Lab 3 Adding Custom IP Lab Micro Blaze

Lab 3 Adding Custom IP Lab: Micro. Blaze for EDK 6. 3 i

Objectives n n n Add a custom IP to your design. Modify the UCF file. Implement the design. for EDK 6. 3 i 1

Procedure n In this lab, you will use the Import Peripheral Wizard of Xilinx Platform Studio (XPS) to create a user peripheral from an HDL module, add an instance of the imported peripheral, and modify the system. ucf file to provide an interface to the on-board 7 segment LED module. n OPB Bus MDM Micro. Blaze LMB BRAM Cntlr INTC LMB BRAM Cntlr Timer BRAM My IP for 7 -segment LEDs 7 Seg LED for EDK 6. 3 i UART My IP GPIO PSB GPIO LEDs GPIO SWs 2

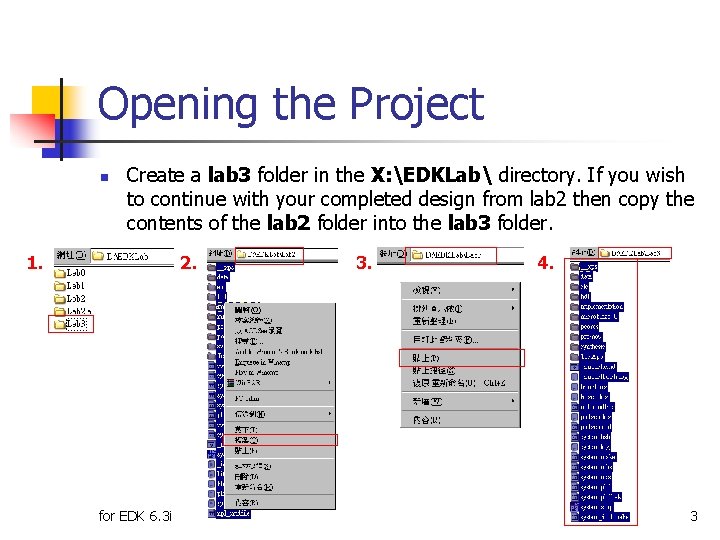

Opening the Project n Create a lab 3 folder in the X: EDKLab directory. If you wish to continue with your completed design from lab 2 then copy the contents of the lab 2 folder into the lab 3 folder. 1. 2. for EDK 6. 3 i 3. 4. 3

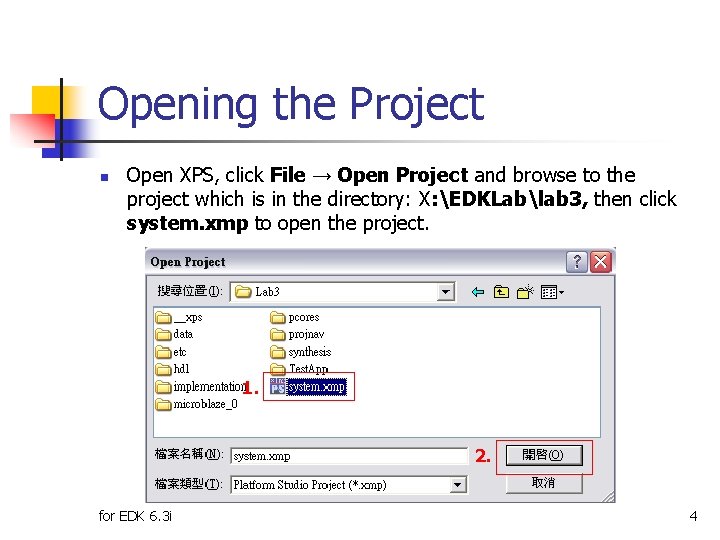

Opening the Project n Open XPS, click File → Open Project and browse to the project which is in the directory: X: EDKLablab 3, then click system. xmp to open the project. 1. 2. for EDK 6. 3 i 4

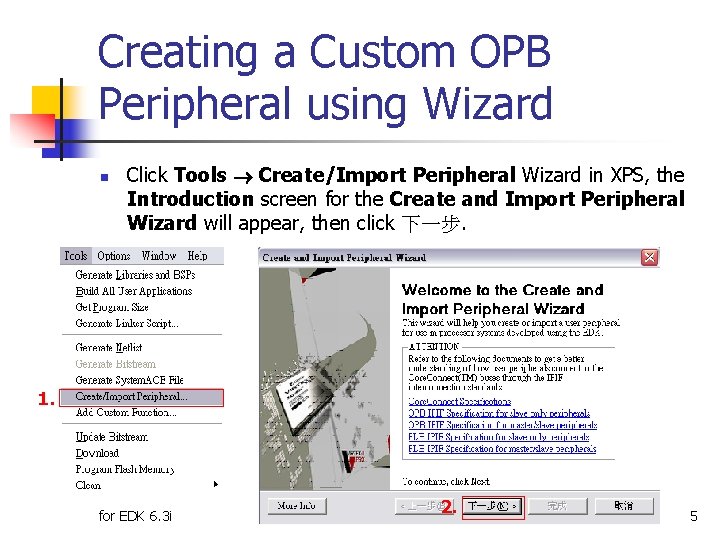

Creating a Custom OPB Peripheral using Wizard n Click Tools Create/Import Peripheral Wizard in XPS, the Introduction screen for the Create and Import Peripheral Wizard will appear, then click 下一步. 1. for EDK 6. 3 i 2. 5

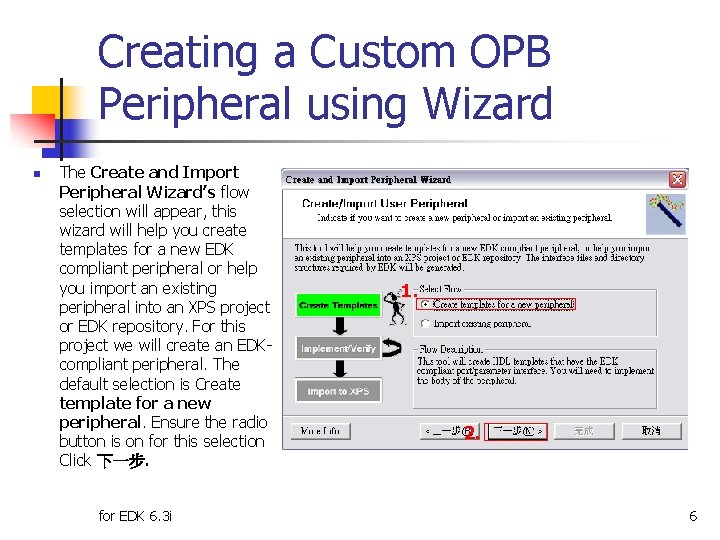

Creating a Custom OPB Peripheral using Wizard n The Create and Import Peripheral Wizard’s flow selection will appear, this wizard will help you create templates for a new EDK compliant peripheral or help you import an existing peripheral into an XPS project or EDK repository. For this project we will create an EDKcompliant peripheral. The default selection is Create template for a new peripheral. Ensure the radio button is on for this selection Click 下一步. for EDK 6. 3 i 1. 2. 6

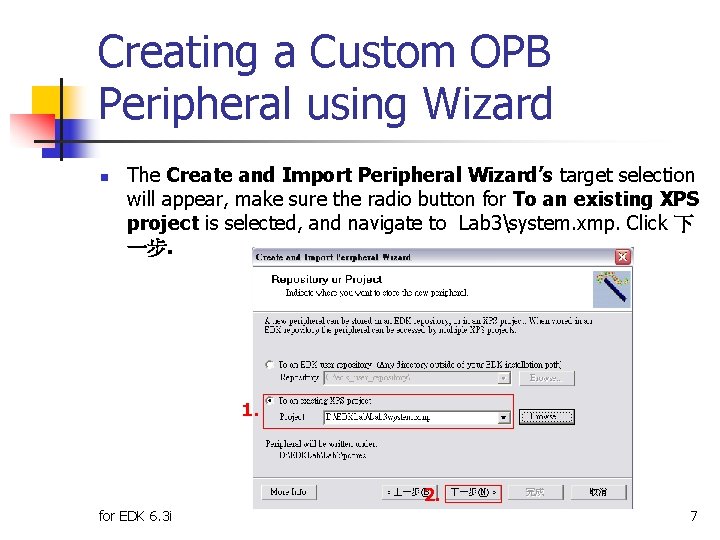

Creating a Custom OPB Peripheral using Wizard n The Create and Import Peripheral Wizard’s target selection will appear, make sure the radio button for To an existing XPS project is selected, and navigate to Lab 3system. xmp. Click 下 一步. 1. 2. for EDK 6. 3 i 7

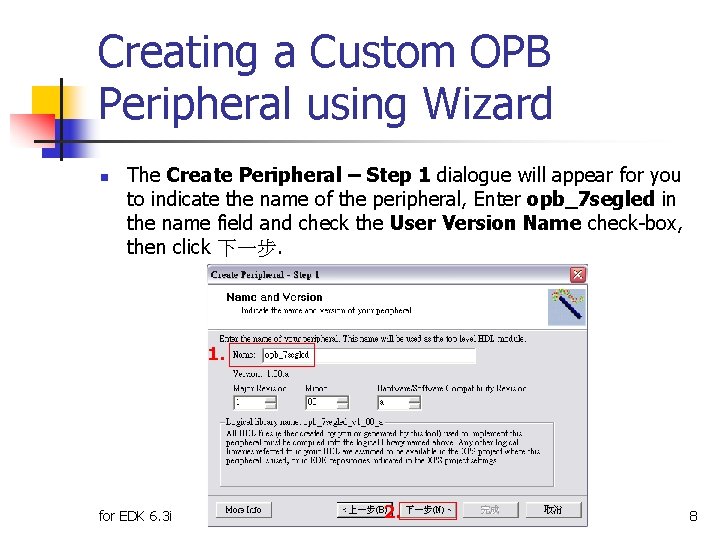

Creating a Custom OPB Peripheral using Wizard n The Create Peripheral – Step 1 dialogue will appear for you to indicate the name of the peripheral, Enter opb_7 segled in the name field and check the User Version Name check-box, then click 下一步. 1. for EDK 6. 3 i 2. 8

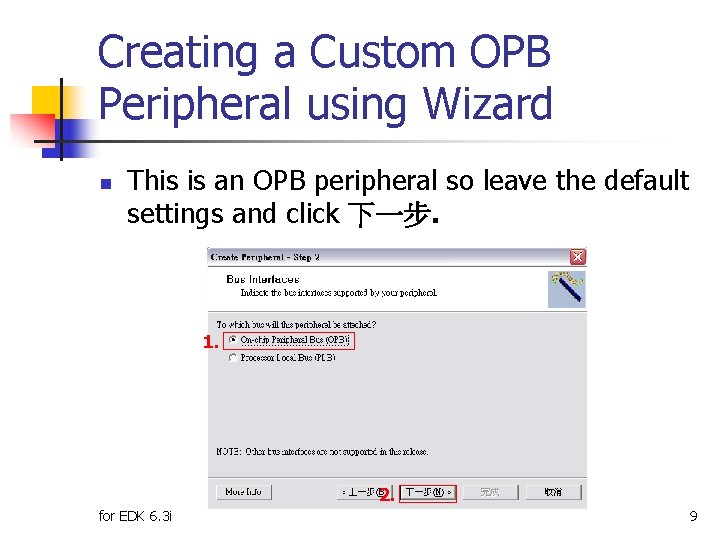

Creating a Custom OPB Peripheral using Wizard n This is an OPB peripheral so leave the default settings and click 下一步. 1. 2. for EDK 6. 3 i 9

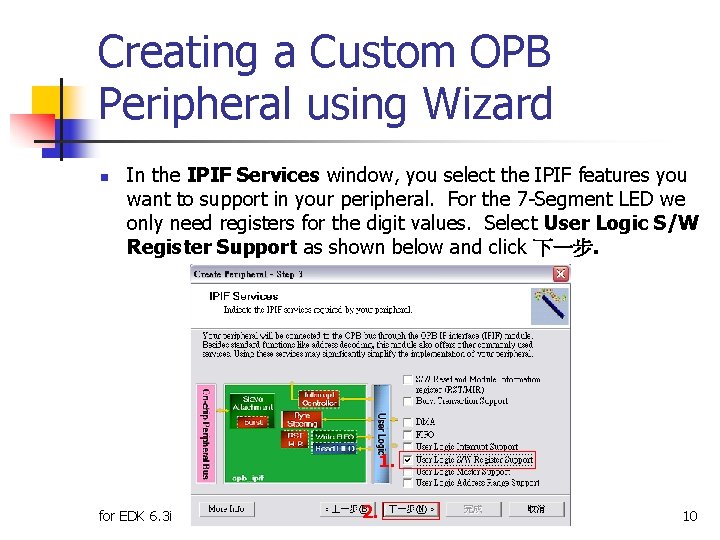

Creating a Custom OPB Peripheral using Wizard n In the IPIF Services window, you select the IPIF features you want to support in your peripheral. For the 7 -Segment LED we only need registers for the digit values. Select User Logic S/W Register Support as shown below and click 下一步. 1. for EDK 6. 3 i 2. 10

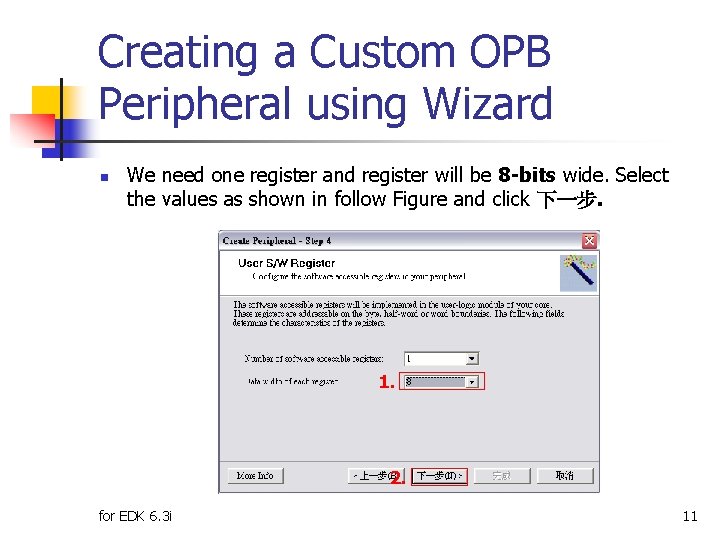

Creating a Custom OPB Peripheral using Wizard n We need one register and register will be 8 -bits wide. Select the values as shown in follow Figure and click 下一步. 1. 2. for EDK 6. 3 i 11

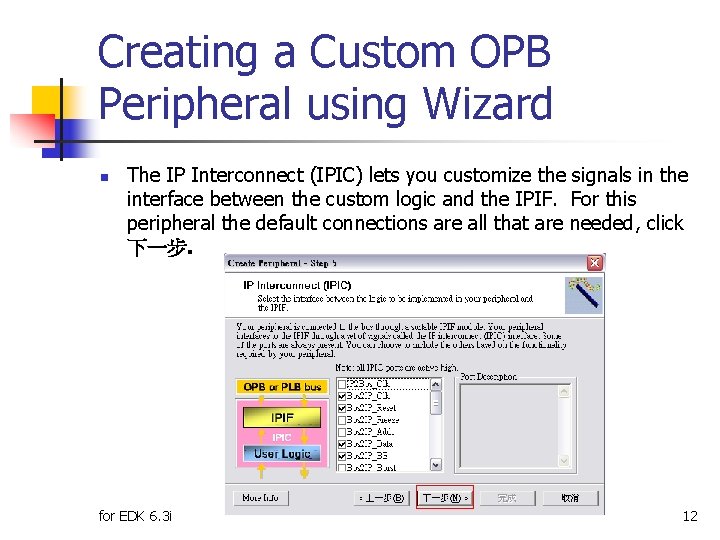

Creating a Custom OPB Peripheral using Wizard n The IP Interconnect (IPIC) lets you customize the signals in the interface between the custom logic and the IPIF. For this peripheral the default connections are all that are needed, click 下一步. for EDK 6. 3 i 12

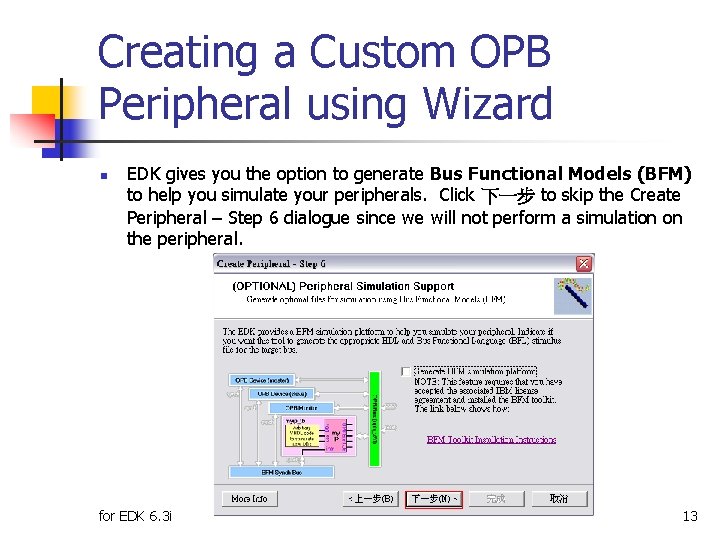

Creating a Custom OPB Peripheral using Wizard n EDK gives you the option to generate Bus Functional Models (BFM) to help you simulate your peripherals. Click 下一步 to skip the Create Peripheral – Step 6 dialogue since we will not perform a simulation on the peripheral. for EDK 6. 3 i 13

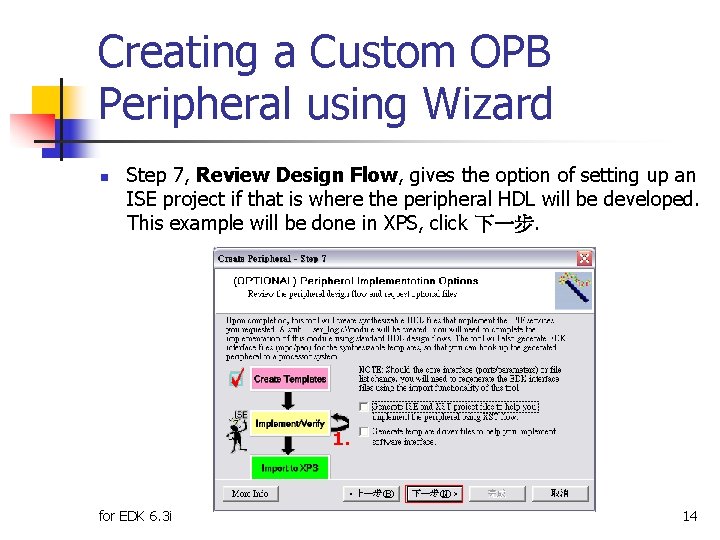

Creating a Custom OPB Peripheral using Wizard n Step 7, Review Design Flow, gives the option of setting up an ISE project if that is where the peripheral HDL will be developed. This example will be done in XPS, click 下一步. 1. for EDK 6. 3 i 14

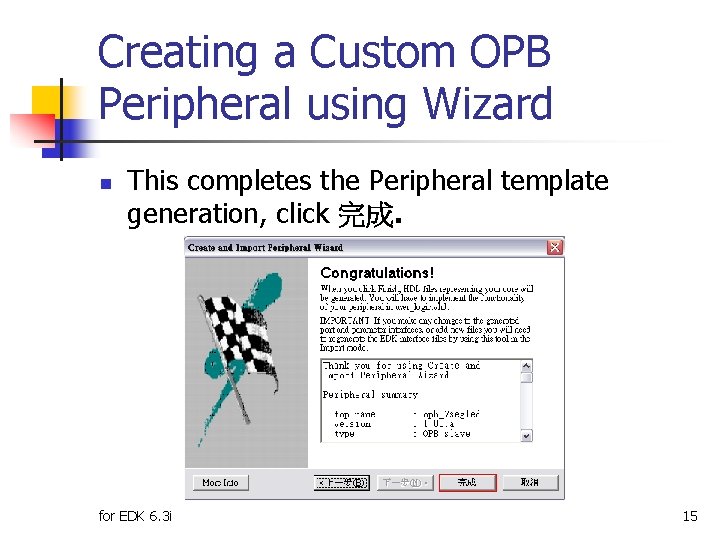

Creating a Custom OPB Peripheral using Wizard n This completes the Peripheral template generation, click 完成. for EDK 6. 3 i 15

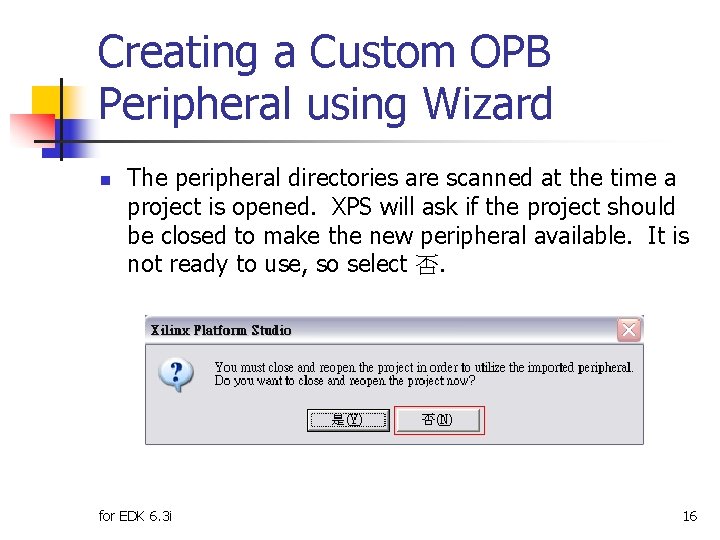

Creating a Custom OPB Peripheral using Wizard n The peripheral directories are scanned at the time a project is opened. XPS will ask if the project should be closed to make the new peripheral available. It is not ready to use, so select 否. for EDK 6. 3 i 16

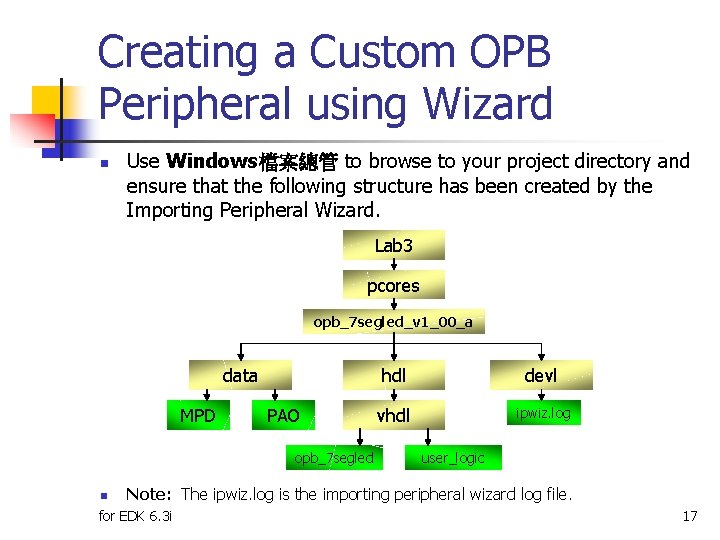

Creating a Custom OPB Peripheral using Wizard n Use Windows檔案總管 to browse to your project directory and ensure that the following structure has been created by the Importing Peripheral Wizard. Lab 3 pcores opb_7 segled_v 1_00_a data MPD PAO opb_7 segled n hdl devl vhdl ipwiz. log user_logic Note: The ipwiz. log is the importing peripheral wizard log file. for EDK 6. 3 i 17

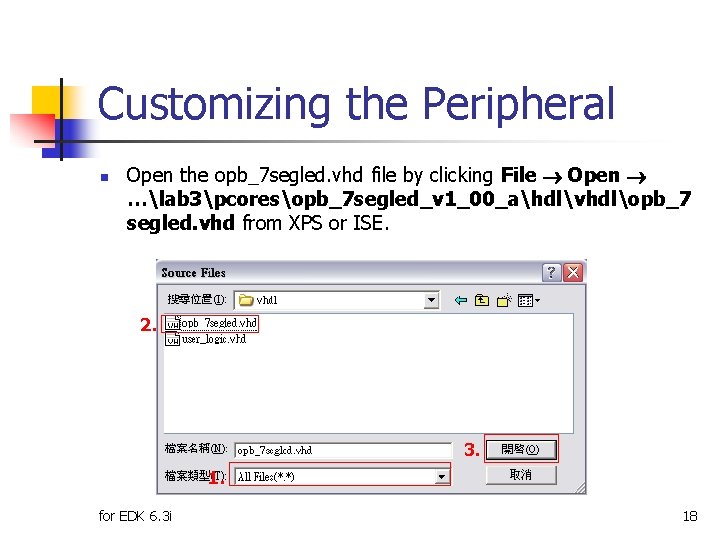

Customizing the Peripheral n Open the opb_7 segled. vhd file by clicking File Open …lab 3pcoresopb_7 segled_v 1_00_ahdlvhdlopb_7 segled. vhd from XPS or ISE. 2. 3. 1. for EDK 6. 3 i 18

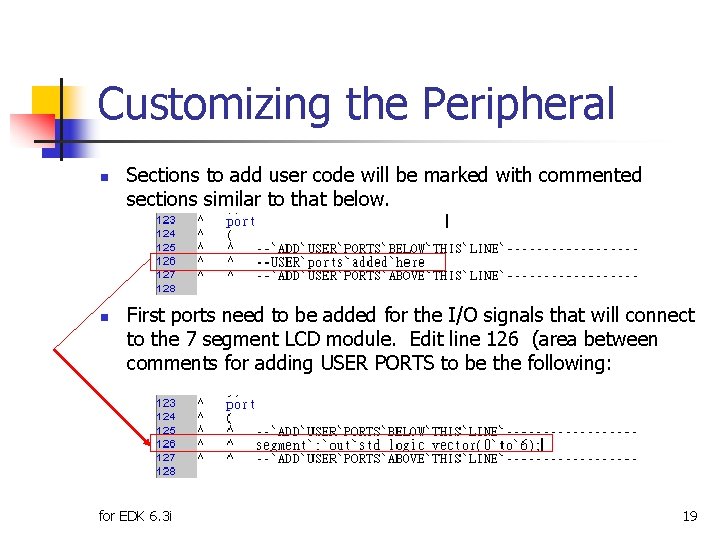

Customizing the Peripheral n n Sections to add user code will be marked with commented sections similar to that below. First ports need to be added for the I/O signals that will connect to the 7 segment LCD module. Edit line 126 (area between comments for adding USER PORTS to be the following: for EDK 6. 3 i 19

Customizing the Peripheral n n Next the ports need to be added to the component instantiation. Edit line 395 (area between comments for mapping USER PORTS to be the following: That completes the changes to the opb_7 segled definition. Save and close the file. for EDK 6. 3 i 20

Customizing the Peripheral n The opb_7 segled. vhd file defines the connectivity of the custom core and includes the OPB and IPIF attachment files. The user_logic. vhd file is where the actual function is implemented. Open the user_logic. vhd file by clicking File Open …lab 3pcoresopb_7 segled_v 1_00_ahdlvhdluser_logic. v hd from XPS or ISE. 2. 3. 1. for EDK 6. 3 i 21

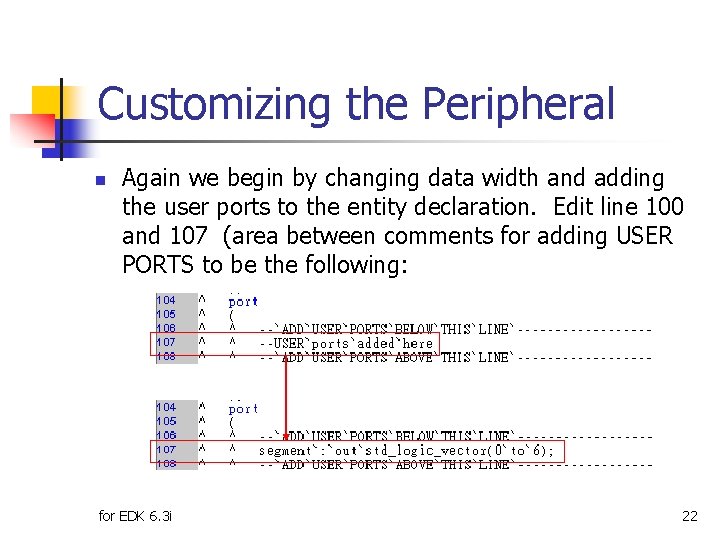

Customizing the Peripheral n Again we begin by changing data width and adding the user ports to the entity declaration. Edit line 100 and 107 (area between comments for adding USER PORTS to be the following: for EDK 6. 3 i 22

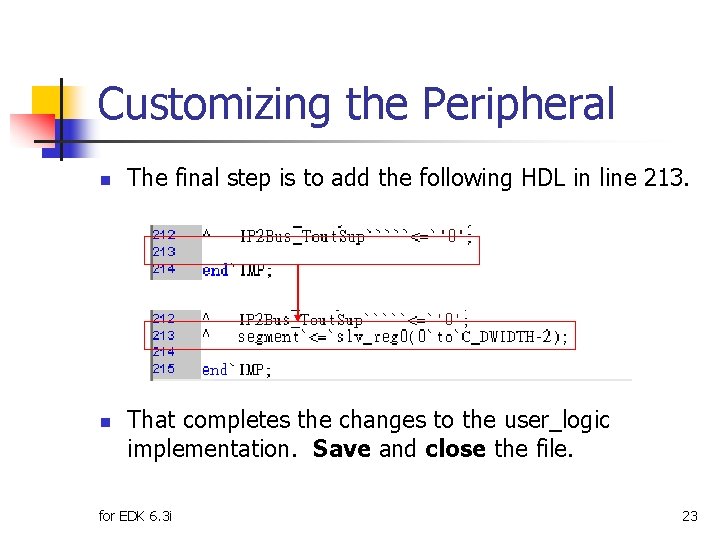

Customizing the Peripheral n n The final step is to add the following HDL in line 213. That completes the changes to the user_logic implementation. Save and close the file. for EDK 6. 3 i 23

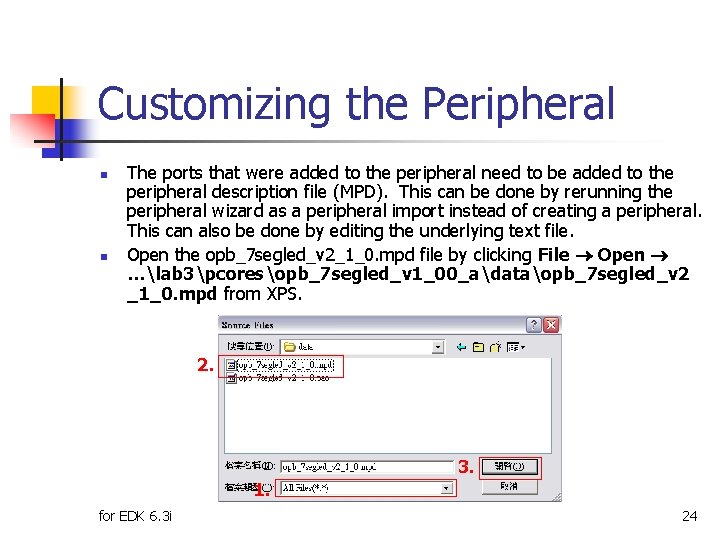

Customizing the Peripheral n n The ports that were added to the peripheral need to be added to the peripheral description file (MPD). This can be done by rerunning the peripheral wizard as a peripheral import instead of creating a peripheral. This can also be done by editing the underlying text file. Open the opb_7 segled_v 2_1_0. mpd file by clicking File Open …lab 3pcoresopb_7 segled_v 1_00_adataopb_7 segled_v 2 _1_0. mpd from XPS. 2. 3. 1. for EDK 6. 3 i 24

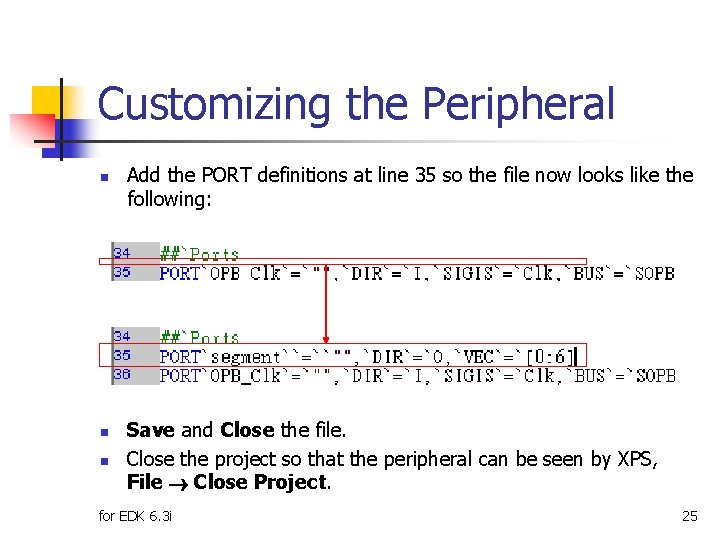

Customizing the Peripheral n n n Add the PORT definitions at line 35 so the file now looks like the following: Save and Close the file. Close the project so that the peripheral can be seen by XPS, File Close Project. for EDK 6. 3 i 25

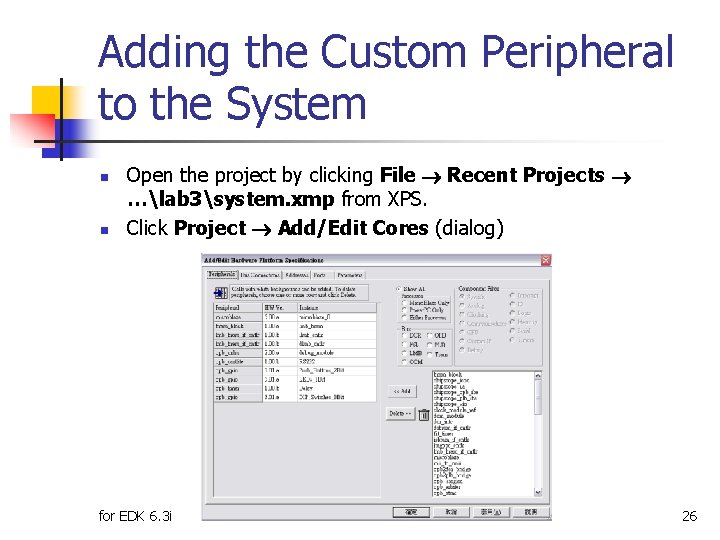

Adding the Custom Peripheral to the System n n Open the project by clicking File Recent Projects …lab 3system. xmp from XPS. Click Project Add/Edit Cores (dialog) for EDK 6. 3 i 26

Adding the Custom Peripheral to the System n In the Peripherals tab, select opb_7 segled from the available IPs list, and click ADD to add the peripheral to the system. 2. 1. 3. for EDK 6. 3 i 27

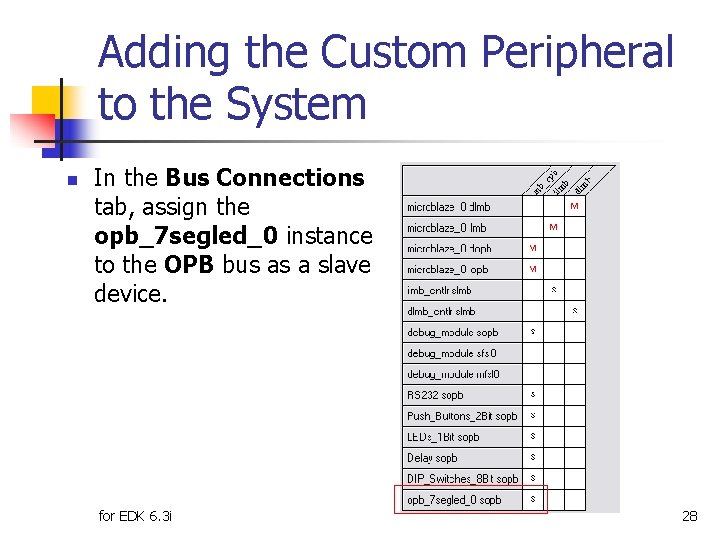

Adding the Custom Peripheral to the System n In the Bus Connections tab, assign the opb_7 segled_0 instance to the OPB bus as a slave device. for EDK 6. 3 i 28

Adding the Custom Peripheral to the System n Change the base address to 0 x 80001 a 00 and the end address to 0 x 80001 a. FF in the Addresses tab. for EDK 6. 3 i 29

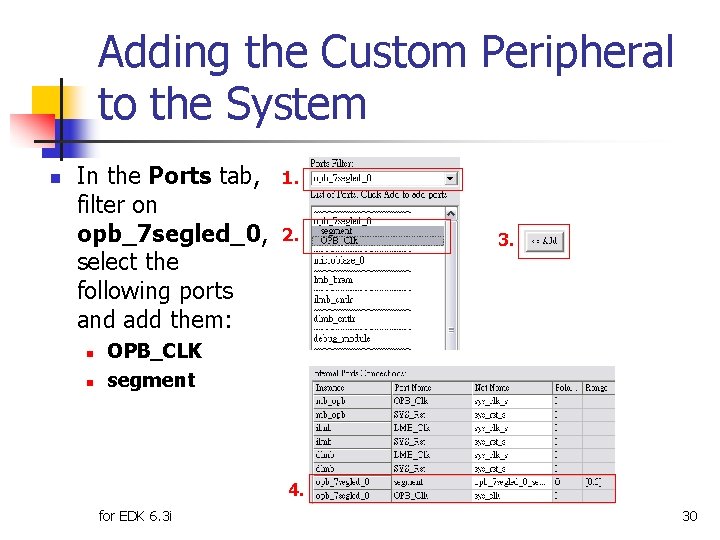

Adding the Custom Peripheral to the System n In the Ports tab, filter on opb_7 segled_0, select the following ports and add them: n n 1. 2. 3. OPB_CLK segment 4. for EDK 6. 3 i 30

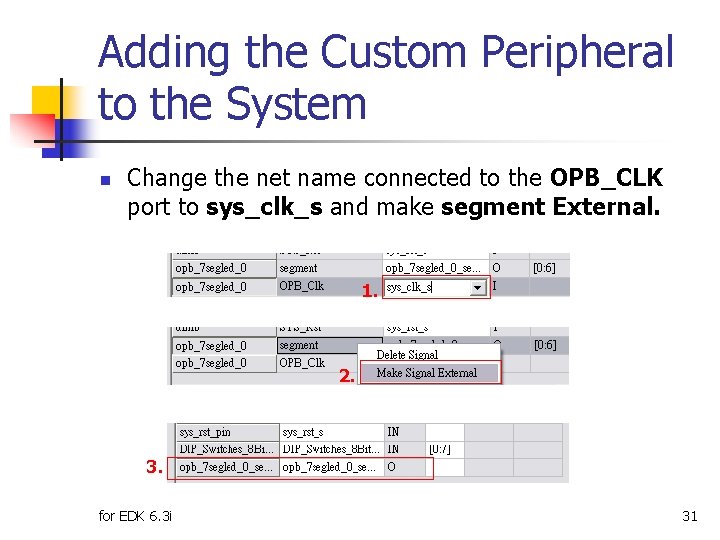

Adding the Custom Peripheral to the System n Change the net name connected to the OPB_CLK port to sys_clk_s and make segment External. 1. 2. 3. for EDK 6. 3 i 31

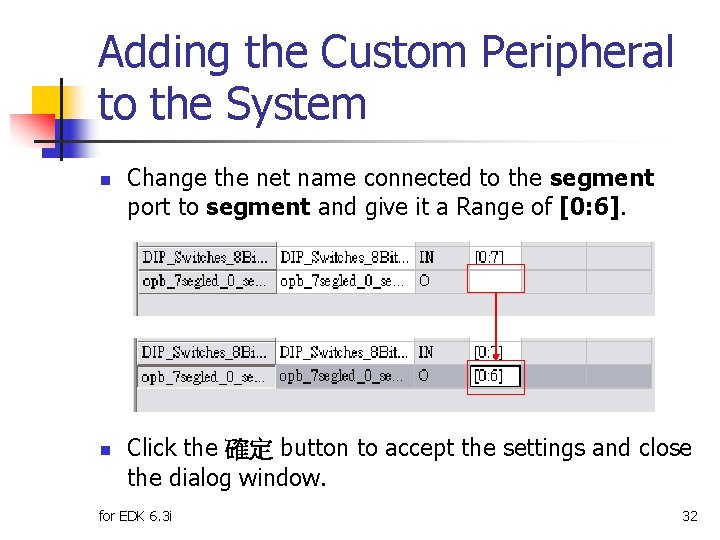

Adding the Custom Peripheral to the System n n Change the net name connected to the segment port to segment and give it a Range of [0: 6]. Click the 確定 button to accept the settings and close the dialog window. for EDK 6. 3 i 32

Modify the UCF file n Open the system. ucf file by double-clicking the UCF File: datasystem. ucf entry under Project Files in the System BSP window. for EDK 6. 3 i 33

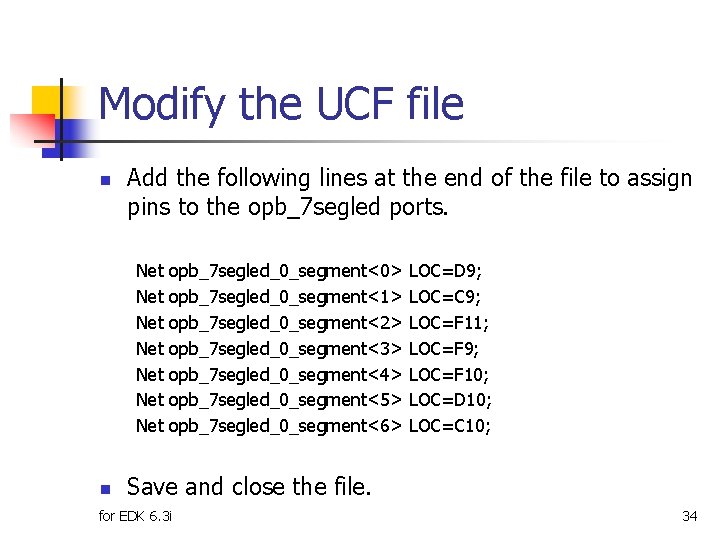

Modify the UCF file n Add the following lines at the end of the file to assign pins to the opb_7 segled ports. Net Net n opb_7 segled_0_segment<0> opb_7 segled_0_segment<1> opb_7 segled_0_segment<2> opb_7 segled_0_segment<3> opb_7 segled_0_segment<4> opb_7 segled_0_segment<5> opb_7 segled_0_segment<6> LOC=D 9; LOC=C 9; LOC=F 11; LOC=F 9; LOC=F 10; LOC=D 10; LOC=C 10; Save and close the file. for EDK 6. 3 i 34

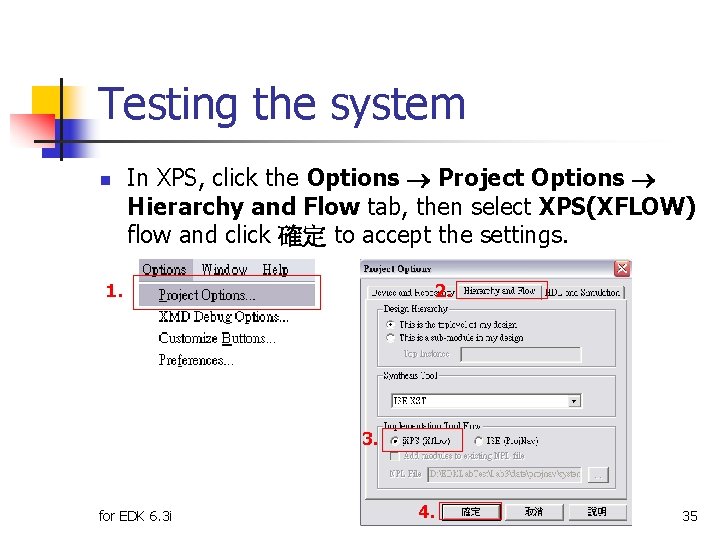

Testing the system n In XPS, click the Options Project Options Hierarchy and Flow tab, then select XPS(XFLOW) flow and click 確定 to accept the settings. 1. 2. 3. for EDK 6. 3 i 4. 35

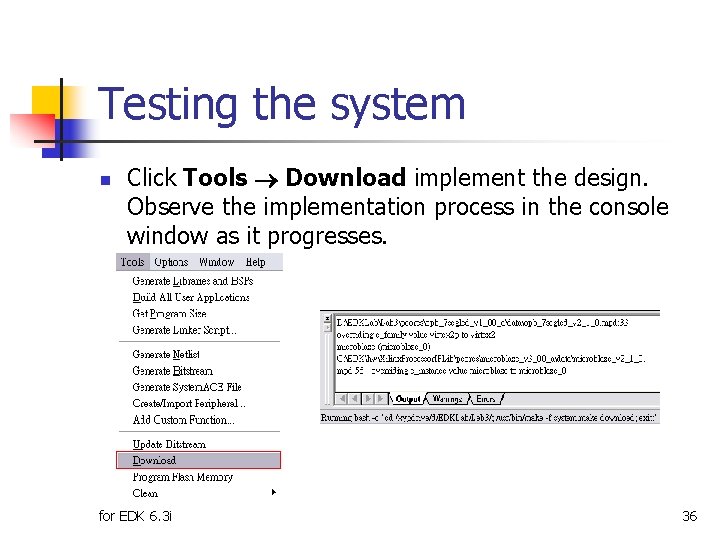

Testing the system n Click Tools Download implement the design. Observe the implementation process in the console window as it progresses. for EDK 6. 3 i 36

Testing the system n n After downloading, the output on the terminal display is still the same and the 7 Segment LEDs still off, but we will use it in lab 5. You can add the other 7 Segment LEDs in this design. for EDK 6. 3 i 37

Conclusion n The Import Peripheral Wizard can be used to integrate your user peripheral into an existing processor system. The wizard creates the necessary directory structure and adds the necessary files (MPD, PAO) to the project directory. After the peripheral is imported, you can use the peripheral in the design by using the same XPS flows that you have seen in previous labs. for EDK 6. 3 i 38

- Slides: 39