Lab 1 and 2 Digital System Design Using

Lab 1 and 2: Digital System Design Using Verilog Ming-Feng Chang CSIE, NCTU

Introduction • Objectives – Understand the design methodologies using Verilog • Target audience – have basic digital circuits design concept – use Verilog to design digital systems – Verilog description for logic synthesis • NOT in the talk – a full coverage of Verilog – use Verilog for quick behavioral modeling 張明峰 交大資 系 Verilog-2

• Contents – Verilog HDL • structured modeling • RTL modeling – Example combinational circuits • structured description (net-list) • RTL – Example sequential circuits • RTL – FSM • combinational circuits • sequential circuits 張明峰 交大資 系 Verilog-3

Verilog history • Gateway Design Automation – Phil Moorby in 1984 and 1985 • Verilog-XL, "XL algorithm", 1986 – a very efficient method for doing gate-level simulation • Verilog logic synthesizer, Synopsys, 1988 – the top-down design methodology is feasible • Cadence Design Systems acquired Gateway – December 1989 – a proprietary HDL 張明峰 交大資 系 Verilog-4

• Open Verilog International (OVI), 1991 – Language Reference Manual (LRM) – making the language specification as vendorindependent as possible. • The IEEE 1364 working group, 1994 – to turn the OVI LRM into an IEEE standard. • Verilog became an IEEE standard – December, 1995. 張明峰 交大資 系 Verilog-5

Hardware Description Languages • The functionality of hardware – concurrency – timing controls • The implementation of hardware – structure – net-list • ISP – C. Gordon Bell and Alan Newell at Carnegie Mellon University, 1972 – RTL (register transfer level) 張明峰 交大資 系 Verilog-6

Different Levels of Abstraction • Algorithmic – the function of the system • RTL – the data flow – the control signals – the storage element and clock • Gate – gate-level net-list • Switch – transistor-level net-list 張明峰 交大資 系 Verilog-7

Verilog for Digital System Design • Structural description – net-list using primitive gates and switches – continuous assignment using Verilog operators • RTL – – functional description timing controls and concurrency specification procedural blocks (always and initial) registers and latches • C + timing controls + concurrency • An HDL to specify your design 張明峰 交大資 系 Verilog-8

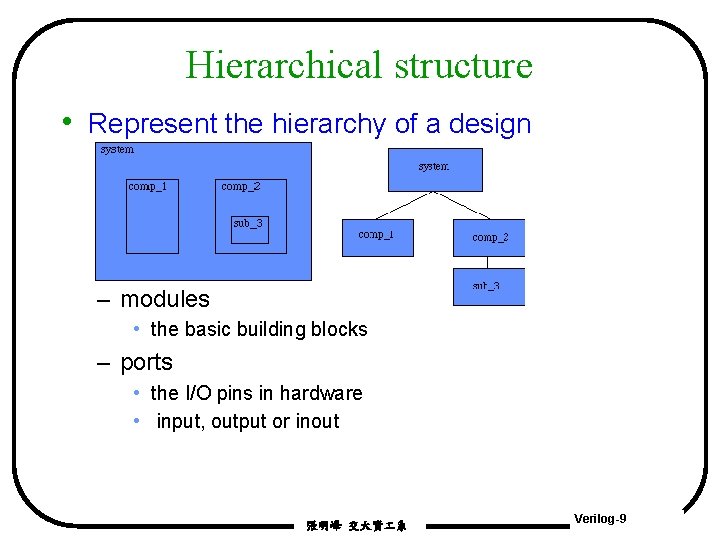

Hierarchical structure • Represent the hierarchy of a design – modules • the basic building blocks – ports • the I/O pins in hardware • input, output or inout 張明峰 交大資 系 Verilog-9

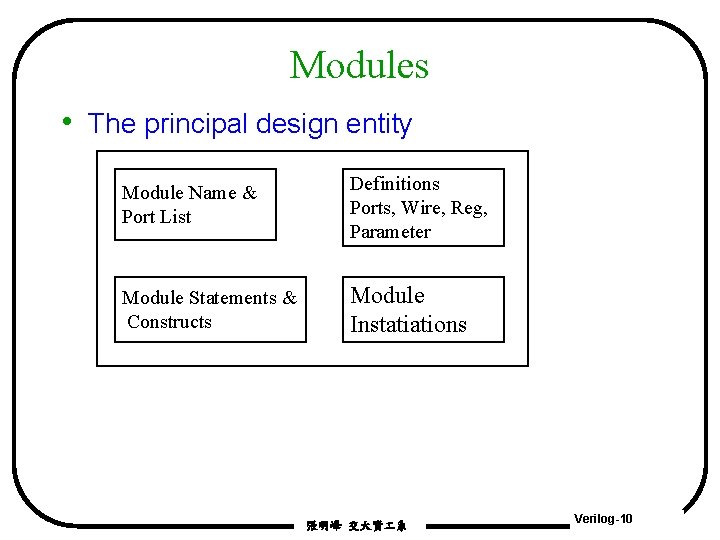

Modules • The principal design entity Module Name & Port List Definitions Ports, Wire, Reg, Parameter Module Statements & Constructs Module Instatiations 張明峰 交大資 系 Verilog-10

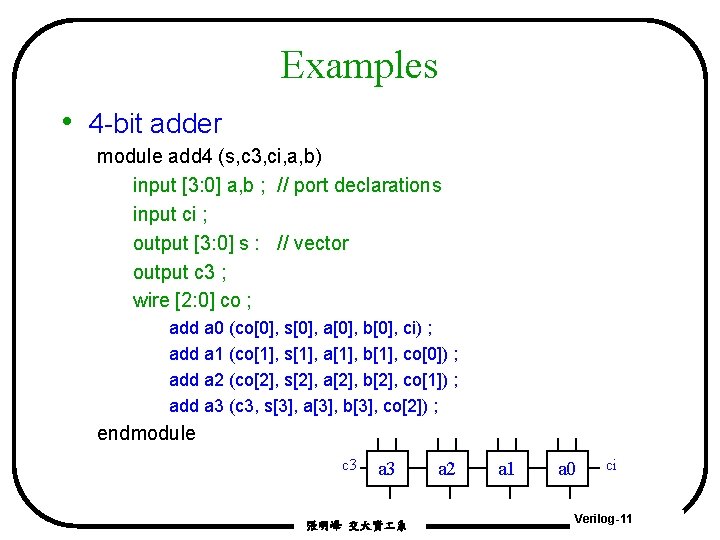

Examples • 4 -bit adder module add 4 (s, c 3, ci, a, b) input [3: 0] a, b ; // port declarations input ci ; output [3: 0] s : // vector output c 3 ; wire [2: 0] co ; add a 0 (co[0], s[0], a[0], b[0], ci) ; add a 1 (co[1], s[1], a[1], b[1], co[0]) ; add a 2 (co[2], s[2], a[2], b[2], co[1]) ; add a 3 (c 3, s[3], a[3], b[3], co[2]) ; endmodule c 3 a 3 張明峰 交大資 系 a 2 a 1 a 0 ci Verilog-11

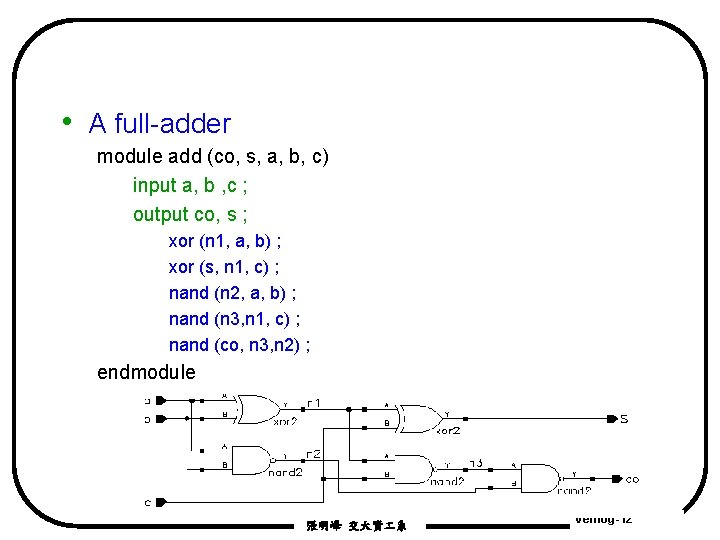

• A full-adder module add (co, s, a, b, c) input a, b , c ; output co, s ; xor (n 1, a, b) ; xor (s, n 1, c) ; nand (n 2, a, b) ; nand (n 3, n 1, c) ; nand (co, n 3, n 2) ; endmodule 張明峰 交大資 系 Verilog-12

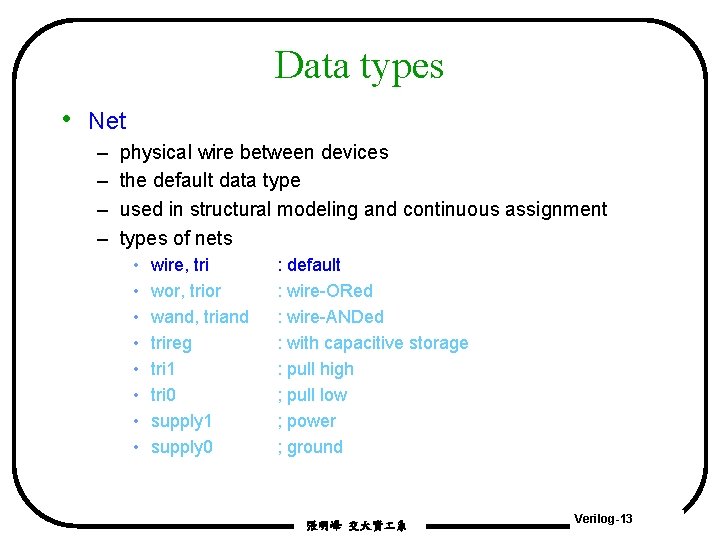

Data types • Net – – physical wire between devices the default data type used in structural modeling and continuous assignment types of nets • • wire, tri wor, trior wand, triand trireg tri 1 tri 0 supply 1 supply 0 : default : wire-ORed : wire-ANDed : with capacitive storage : pull high ; pull low ; power ; ground 張明峰 交大資 系 Verilog-13

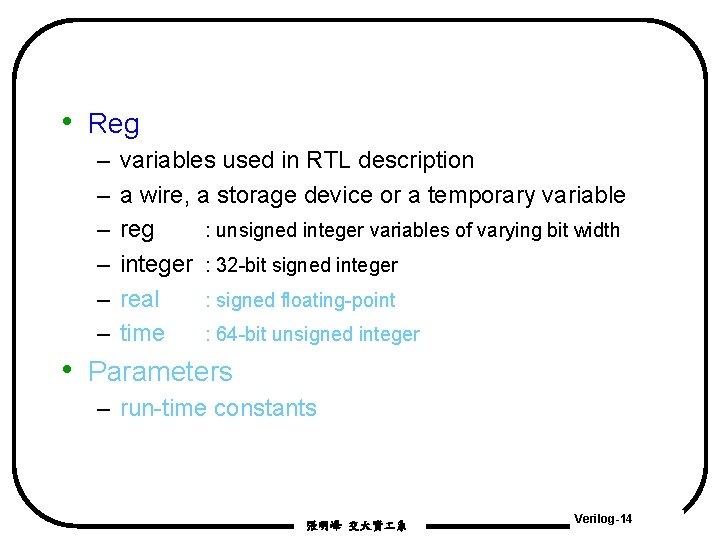

• Reg – – – variables used in RTL description a wire, a storage device or a temporary variable reg : unsigned integer variables of varying bit width integer : 32 -bit signed integer real : signed floating-point time : 64 -bit unsigned integer • Parameters – run-time constants 張明峰 交大資 系 Verilog-14

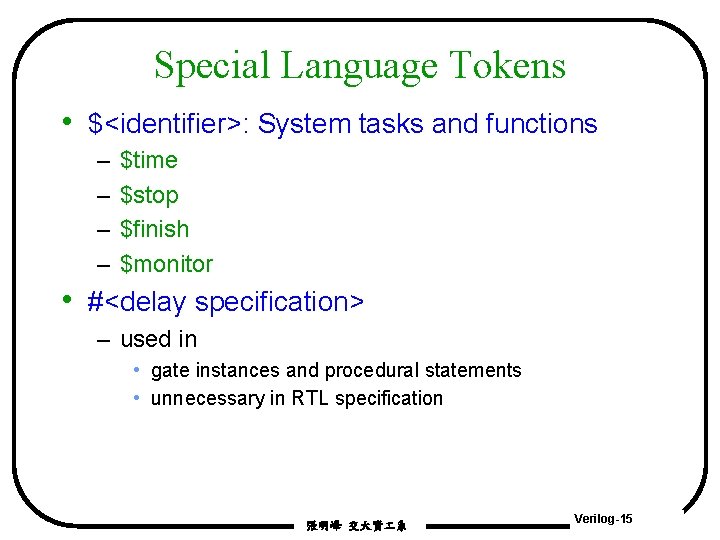

Special Language Tokens • $<identifier>: System tasks and functions – – $time $stop $finish $monitor • #<delay specification> – used in • gate instances and procedural statements • unnecessary in RTL specification 張明峰 交大資 系 Verilog-15

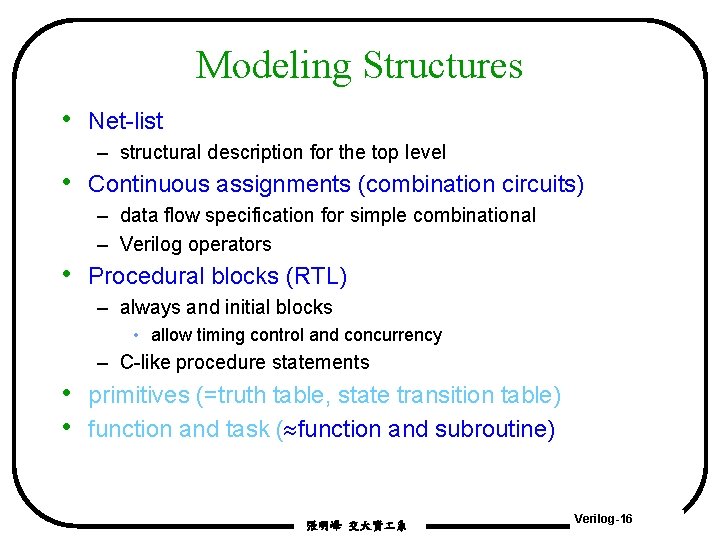

Modeling Structures • Net-list – structural description for the top level • Continuous assignments (combination circuits) – data flow specification for simple combinational – Verilog operators • Procedural blocks (RTL) – always and initial blocks • allow timing control and concurrency – C-like procedure statements • primitives (=truth table, state transition table) • function and task (» function and subroutine) 張明峰 交大資 系 Verilog-16

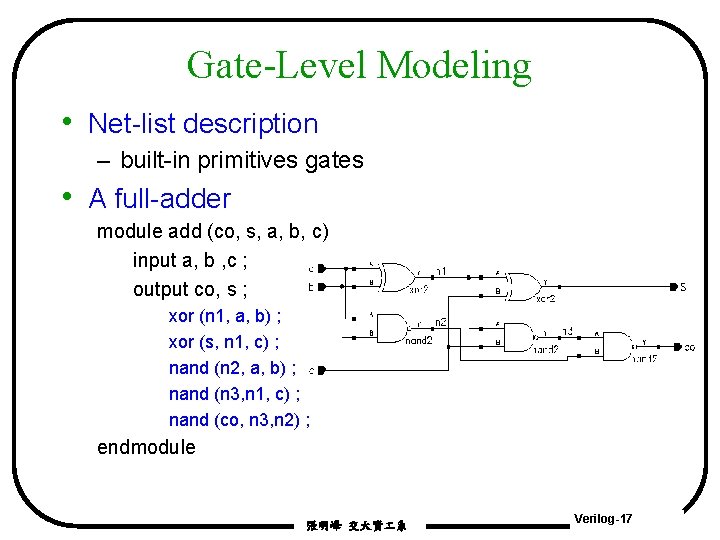

Gate-Level Modeling • Net-list description – built-in primitives gates • A full-adder module add (co, s, a, b, c) input a, b , c ; output co, s ; xor (n 1, a, b) ; xor (s, n 1, c) ; nand (n 2, a, b) ; nand (n 3, n 1, c) ; nand (co, n 3, n 2) ; endmodule 張明峰 交大資 系 Verilog-17

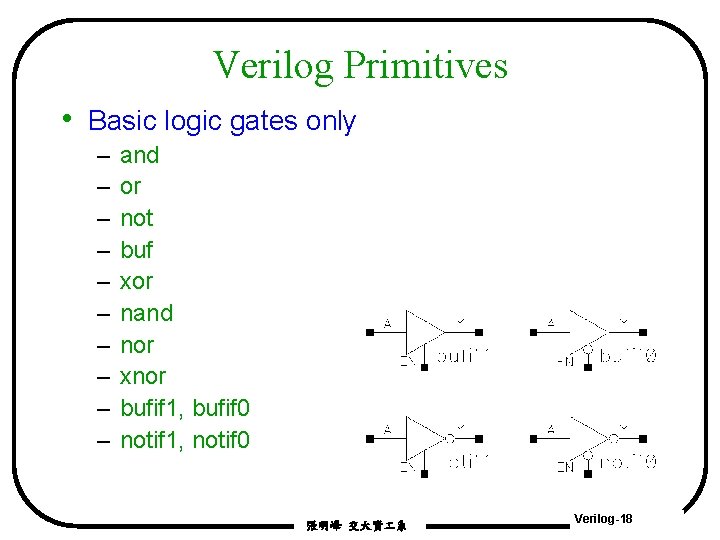

Verilog Primitives • Basic logic gates only – – – – – and or not buf xor nand nor xnor bufif 1, bufif 0 notif 1, notif 0 張明峰 交大資 系 Verilog-18

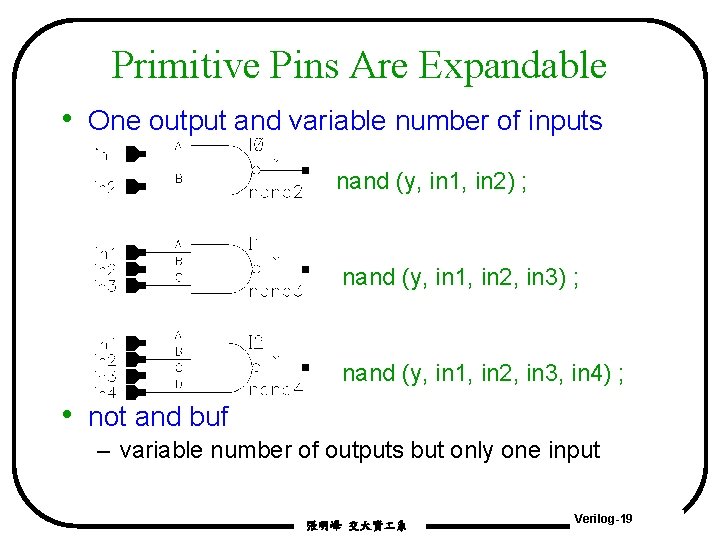

Primitive Pins Are Expandable • One output and variable number of inputs nand (y, in 1, in 2) ; nand (y, in 1, in 2, in 3, in 4) ; • not and buf – variable number of outputs but only one input 張明峰 交大資 系 Verilog-19

Continuous Assignments • Describe combinational logic • Operands + operators • Drive values to a net – – assign out = a&b ; assign eq = (a==b) ; wire #10 inv = ~in ; wire [7: 0] c = a+b ; // and gate // comparator // inverter with delay // 8 -bit adder • Avoid logic loops – assign a = b + a ; – asynchronous design 張明峰 交大資 系 Verilog-20

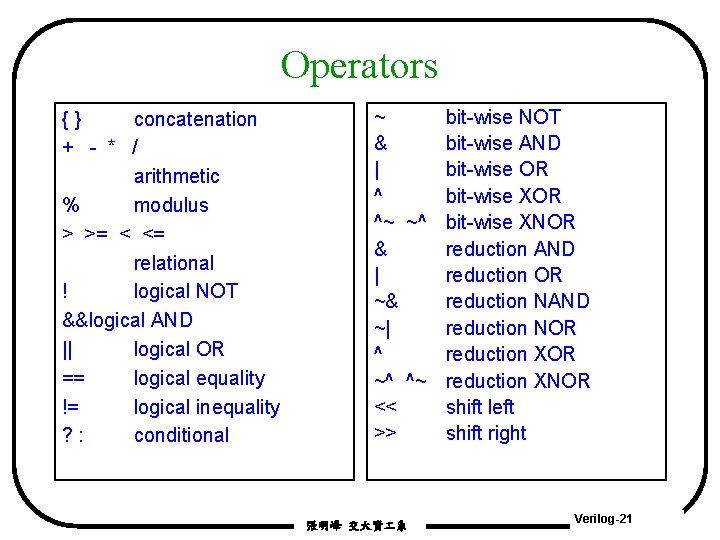

Operators {} concatenation + - * / arithmetic % modulus > >= < <= relational ! logical NOT &&logical AND || logical OR == logical equality != logical inequality ? : conditional ~ bit-wise NOT & bit-wise AND | bit-wise OR ^ bit-wise XOR ^~ ~^ bit-wise XNOR & reduction AND | reduction OR ~& reduction NAND ~| reduction NOR ^ reduction XOR ~^ ^~ reduction XNOR << shift left >> shift right 張明峰 交大資 系 Verilog-21

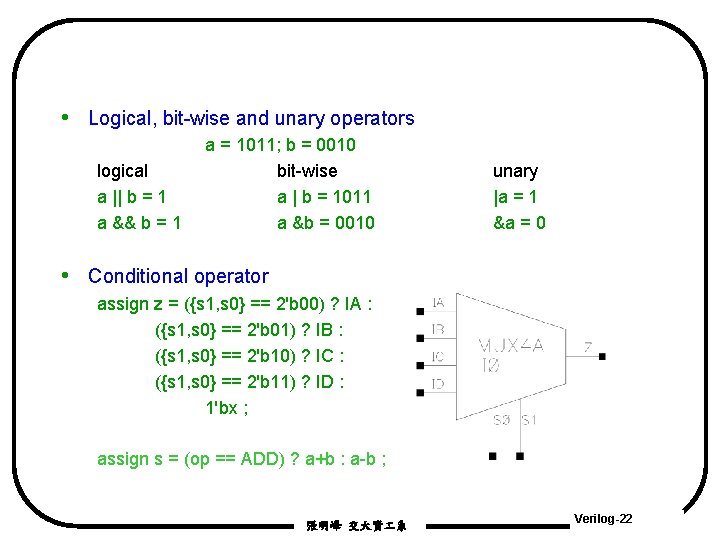

• Logical, bit-wise and unary operators logical a || b = 1 a && b = 1 a = 1011; b = 0010 bit-wise a | b = 1011 a &b = 0010 unary |a = 1 &a = 0 • Conditional operator assign z = ({s 1, s 0} == 2'b 00) ? IA : ({s 1, s 0} == 2'b 01) ? IB : ({s 1, s 0} == 2'b 10) ? IC : ({s 1, s 0} == 2'b 11) ? ID : 1'bx ; assign s = (op == ADD) ? a+b : a-b ; 張明峰 交大資 系 Verilog-22

![Operator Precedence [ ] ( ) !, ~ bit-select or part-select parentheses logical and Operator Precedence [ ] ( ) !, ~ bit-select or part-select parentheses logical and](http://slidetodoc.com/presentation_image_h/e4d9f50839da9da47db52a192533d5f5/image-23.jpg)

Operator Precedence [ ] ( ) !, ~ bit-select or part-select parentheses logical and bit-wise negation &, |, ~&, ~|, ^, ~^, ^~ reduction operators +, unary arithmetic { } concatenation *, /, % arithmetic +, arithmetic <<, >> shift >, >=, <, <= relational ==, != logical equality & bit-wise AND ^, ^~, ~^ bit-wise XOR and XNOR | bit-wise OR &&logical AND || logical OR ? : conditional 張明峰 交大資 系 Verilog-23

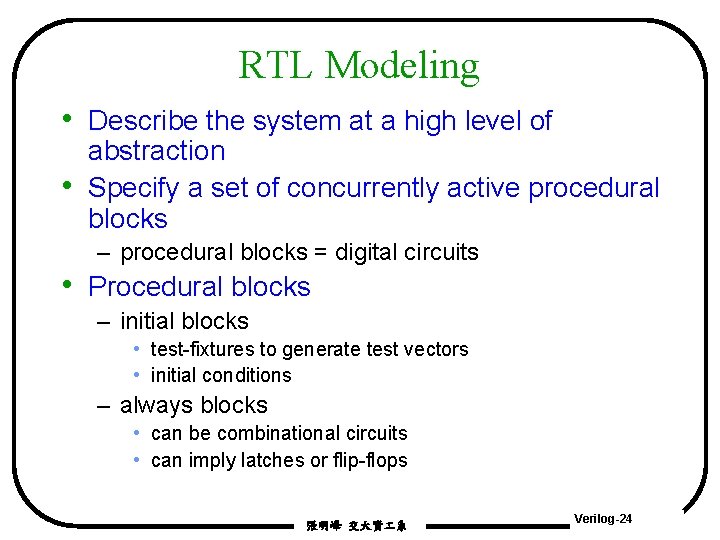

RTL Modeling • Describe the system at a high level of • abstraction Specify a set of concurrently active procedural blocks – procedural blocks = digital circuits • Procedural blocks – initial blocks • test-fixtures to generate test vectors • initial conditions – always blocks • can be combinational circuits • can imply latches or flip-flops 張明峰 交大資 系 Verilog-24

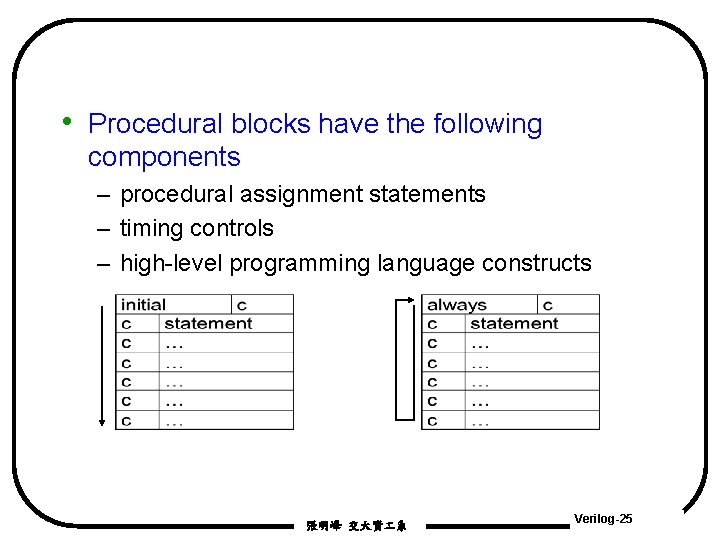

• Procedural blocks have the following components – procedural assignment statements – timing controls – high-level programming language constructs 張明峰 交大資 系 Verilog-25

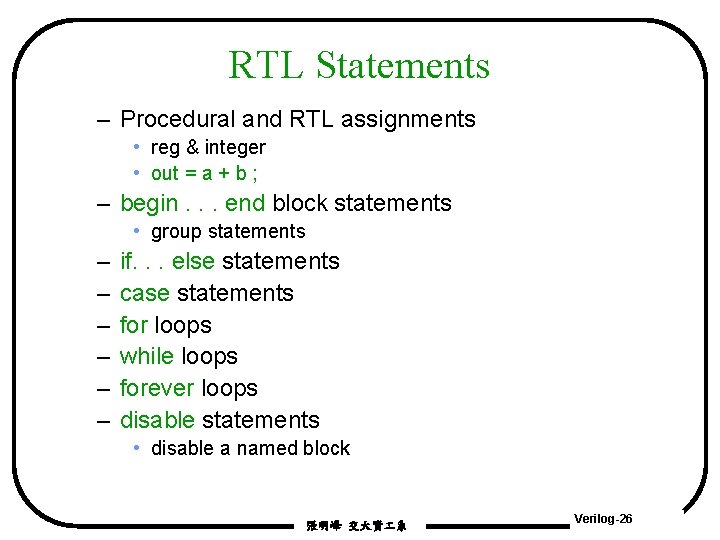

RTL Statements – Procedural and RTL assignments • reg & integer • out = a + b ; – begin. . . end block statements • group statements – – – if. . . else statements case statements for loops while loops forever loops disable statements • disable a named block 張明峰 交大資 系 Verilog-26

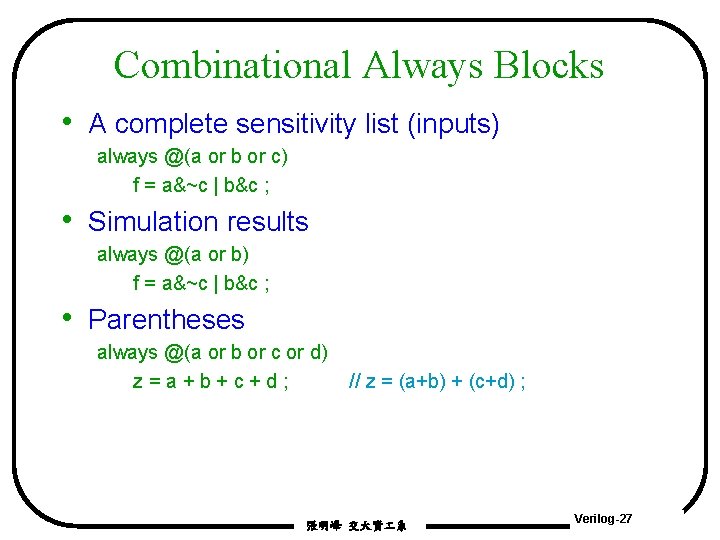

Combinational Always Blocks • A complete sensitivity list (inputs) always @(a or b or c) f = a&~c | b&c ; • Simulation results always @(a or b) f = a&~c | b&c ; • Parentheses always @(a or b or c or d) z=a+b+c+d; // z = (a+b) + (c+d) ; 張明峰 交大資 系 Verilog-27

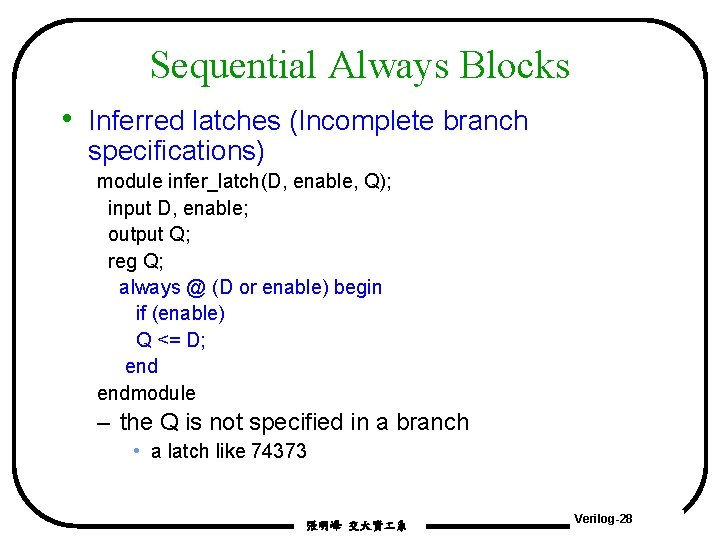

Sequential Always Blocks • Inferred latches (Incomplete branch specifications) module infer_latch(D, enable, Q); input D, enable; output Q; reg Q; always @ (D or enable) begin if (enable) Q <= D; endmodule – the Q is not specified in a branch • a latch like 74373 張明峰 交大資 系 Verilog-28

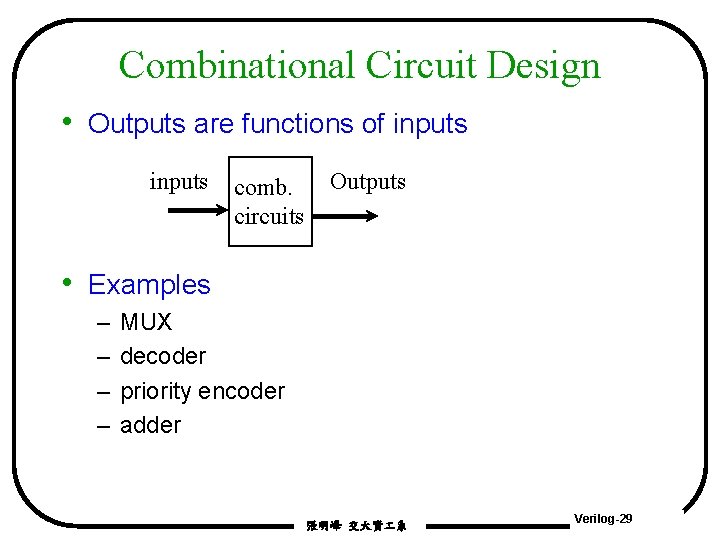

Combinational Circuit Design • Outputs are functions of inputs comb. circuits Outputs • Examples – – MUX decoder priority encoder adder 張明峰 交大資 系 Verilog-29

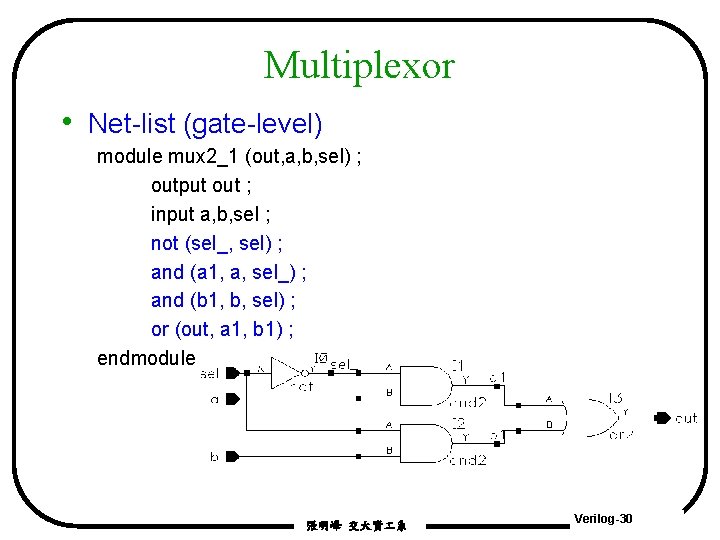

Multiplexor • Net-list (gate-level) module mux 2_1 (out, a, b, sel) ; output out ; input a, b, sel ; not (sel_, sel) ; and (a 1, a, sel_) ; and (b 1, b, sel) ; or (out, a 1, b 1) ; endmodule 張明峰 交大資 系 Verilog-30

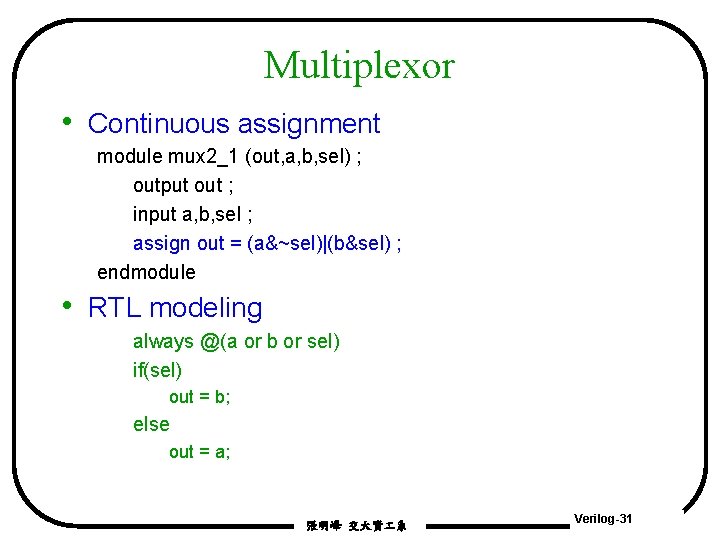

Multiplexor • Continuous assignment module mux 2_1 (out, a, b, sel) ; output out ; input a, b, sel ; assign out = (a&~sel)|(b&sel) ; endmodule • RTL modeling always @(a or b or sel) if(sel) out = b; else out = a; 張明峰 交大資 系 Verilog-31

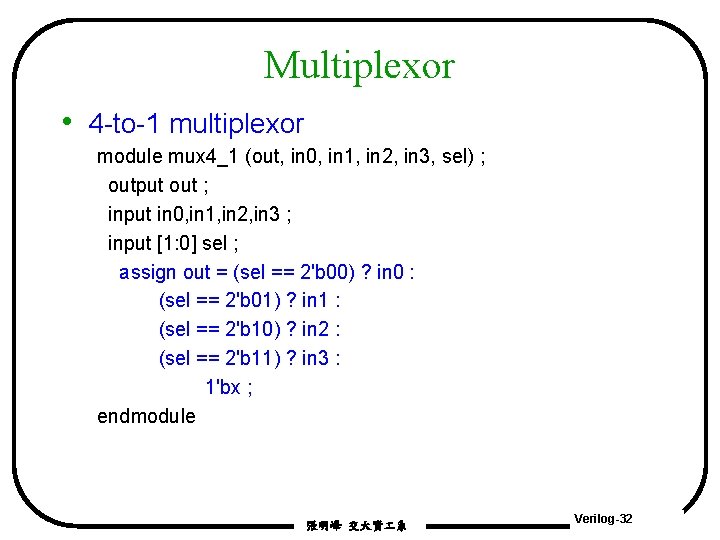

Multiplexor • 4 -to-1 multiplexor module mux 4_1 (out, in 0, in 1, in 2, in 3, sel) ; output out ; input in 0, in 1, in 2, in 3 ; input [1: 0] sel ; assign out = (sel == 2'b 00) ? in 0 : (sel == 2'b 01) ? in 1 : (sel == 2'b 10) ? in 2 : (sel == 2'b 11) ? in 3 : 1'bx ; endmodule 張明峰 交大資 系 Verilog-32

![module mux 4_1 (out, in, sel) ; output out ; input [3: 0] in module mux 4_1 (out, in, sel) ; output out ; input [3: 0] in](http://slidetodoc.com/presentation_image_h/e4d9f50839da9da47db52a192533d5f5/image-33.jpg)

module mux 4_1 (out, in, sel) ; output out ; input [3: 0] in ; input [1: 0] sel ; reg out ; always @(sel or in) begin case(sel) 2’d 0: out = in[0] ; 2’d 1: out = in[1] ; 2’d 2: out = in[2] ; 2’d 3: out = in[3] ; default: 1’bx ; endcase endmodule 張明峰 交大資 系 out = in[sel] ; Verilog-33

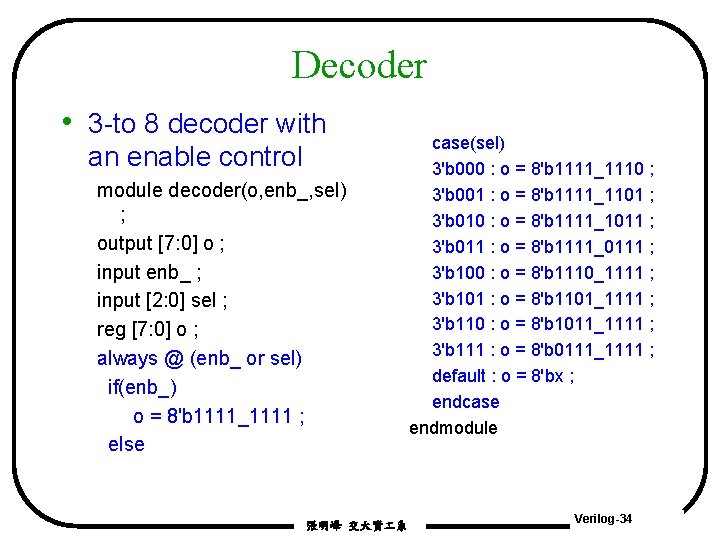

Decoder • 3 -to 8 decoder with an enable control module decoder(o, enb_, sel) ; output [7: 0] o ; input enb_ ; input [2: 0] sel ; reg [7: 0] o ; always @ (enb_ or sel) if(enb_) o = 8'b 1111_1111 ; else 張明峰 交大資 系 case(sel) 3'b 000 : o = 8'b 1111_1110 ; 3'b 001 : o = 8'b 1111_1101 ; 3'b 010 : o = 8'b 1111_1011 ; 3'b 011 : o = 8'b 1111_0111 ; 3'b 100 : o = 8'b 1110_1111 ; 3'b 101 : o = 8'b 1101_1111 ; 3'b 110 : o = 8'b 1011_1111 ; 3'b 111 : o = 8'b 0111_1111 ; default : o = 8'bx ; endcase endmodule Verilog-34

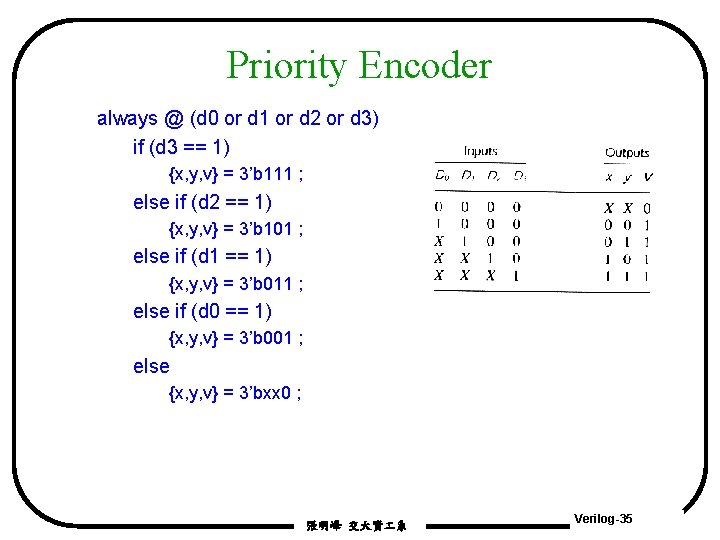

Priority Encoder always @ (d 0 or d 1 or d 2 or d 3) if (d 3 == 1) {x, y, v} = 3’b 111 ; else if (d 2 == 1) {x, y, v} = 3’b 101 ; else if (d 1 == 1) {x, y, v} = 3’b 011 ; else if (d 0 == 1) {x, y, v} = 3’b 001 ; else {x, y, v} = 3’bxx 0 ; 張明峰 交大資 系 Verilog-35

![Parity Checker module parity_chk(data, parity); input [0: 7] data; output parity; reg parity; always Parity Checker module parity_chk(data, parity); input [0: 7] data; output parity; reg parity; always](http://slidetodoc.com/presentation_image_h/e4d9f50839da9da47db52a192533d5f5/image-36.jpg)

Parity Checker module parity_chk(data, parity); input [0: 7] data; output parity; reg parity; always @ (data) begin: check_parity reg partial; integer n; partial = data[0]; for ( n = 0; n <= 7; n = n + 1) begin partial = partial ^ data[n]; end parity <= partial; endmodule 張明峰 交大資 系 Verilog-36

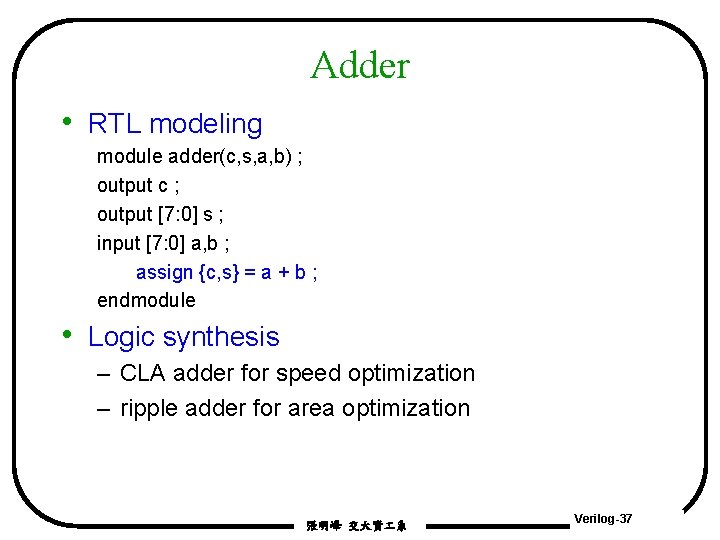

Adder • RTL modeling module adder(c, s, a, b) ; output c ; output [7: 0] s ; input [7: 0] a, b ; assign {c, s} = a + b ; endmodule • Logic synthesis – CLA adder for speed optimization – ripple adder for area optimization 張明峰 交大資 系 Verilog-37

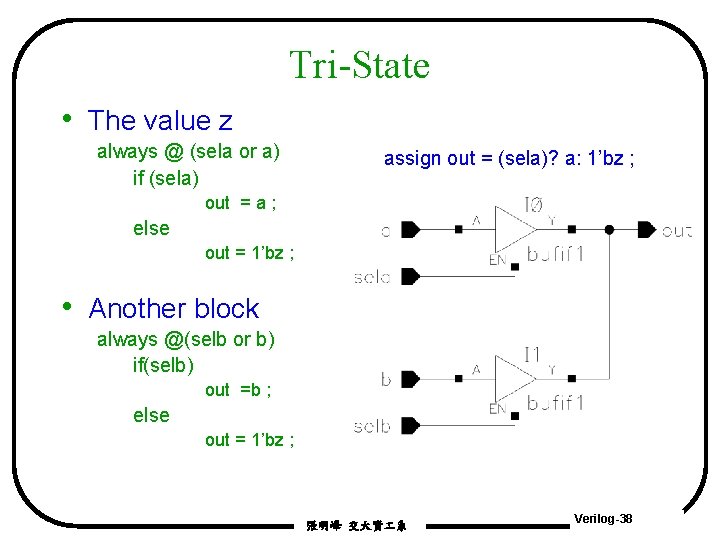

Tri-State • The value z always @ (sela or a) if (sela) assign out = (sela)? a: 1’bz ; out = a ; else out = 1’bz ; • Another block always @(selb or b) if(selb) out =b ; else out = 1’bz ; 張明峰 交大資 系 Verilog-38

• Registers (Flip-flops) are implied – @(posedge clk) or @(negedge clk) – a positive edge-triggered D flip-flop always @ (posedge clk) q=d; 張明峰 交大資 系 Verilog-39

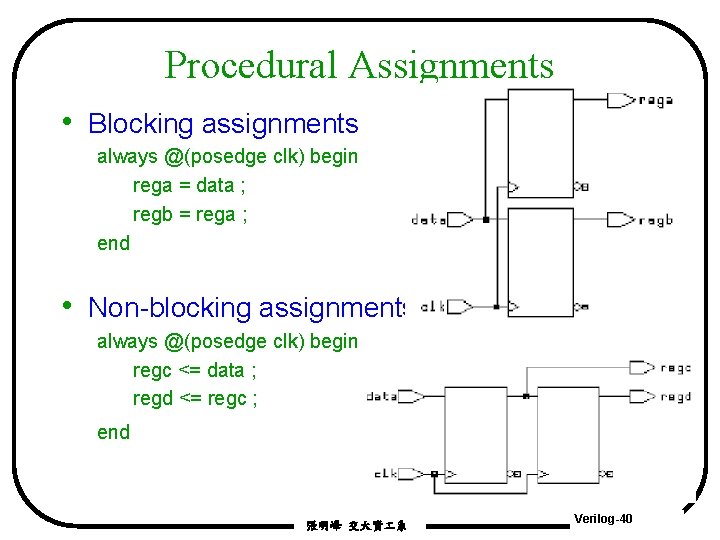

Procedural Assignments • Blocking assignments always @(posedge clk) begin rega = data ; regb = rega ; end • Non-blocking assignments always @(posedge clk) begin regc <= data ; regd <= regc ; end 張明峰 交大資 系 Verilog-40

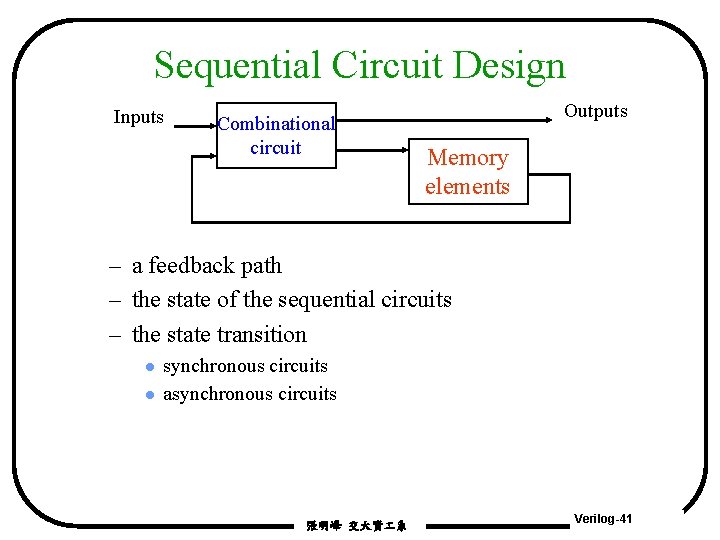

Sequential Circuit Design Inputs Combinational circuit Outputs Memory elements – a feedback path – the state of the sequential circuits – the state transition l l synchronous circuits asynchronous circuits 張明峰 交大資 系 Verilog-41

• Examples – – – – D flip-flop D latch register shifter counter pipeline FSM 張明峰 交大資 系 Verilog-42

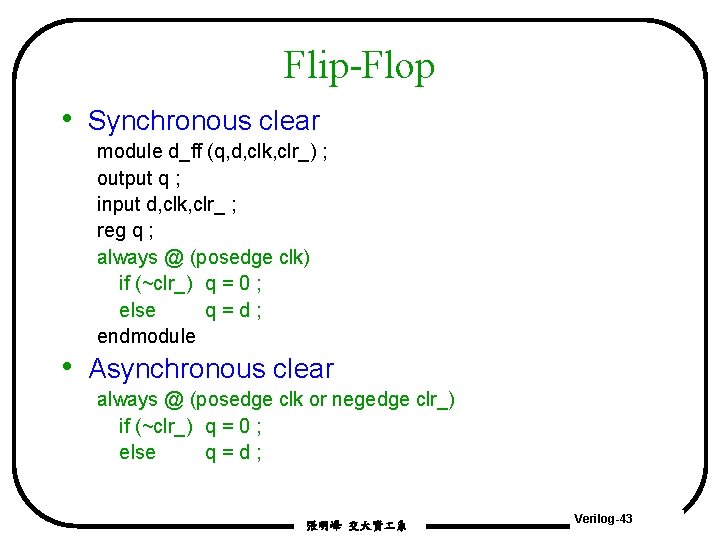

Flip-Flop • Synchronous clear module d_ff (q, d, clk, clr_) ; output q ; input d, clk, clr_ ; reg q ; always @ (posedge clk) if (~clr_) q = 0 ; else q=d; endmodule • Asynchronous clear always @ (posedge clk or negedge clr_) if (~clr_) q = 0 ; else q=d; 張明峰 交大資 系 Verilog-43

![Register module register (q, d, clk, clr_, set_) ; output [7: 0] q ; Register module register (q, d, clk, clr_, set_) ; output [7: 0] q ;](http://slidetodoc.com/presentation_image_h/e4d9f50839da9da47db52a192533d5f5/image-44.jpg)

Register module register (q, d, clk, clr_, set_) ; output [7: 0] q ; input [7: 0] d ; input clk, clr_, set_ ; reg [7: 0] q ; always @ (posedge clk or negedge clr_ or negedge set_) if (~clr_) q=0; else if (~set_) q = 8’b 1111_1111 ; else q=d; endmodule 張明峰 交大資 系 Verilog-44

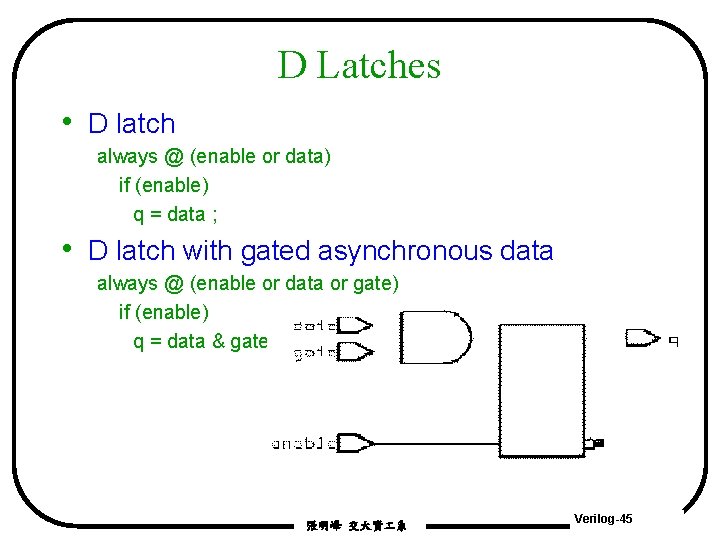

D Latches • D latch always @ (enable or data) if (enable) q = data ; • D latch with gated asynchronous data always @ (enable or data or gate) if (enable) q = data & gate ; 張明峰 交大資 系 Verilog-45

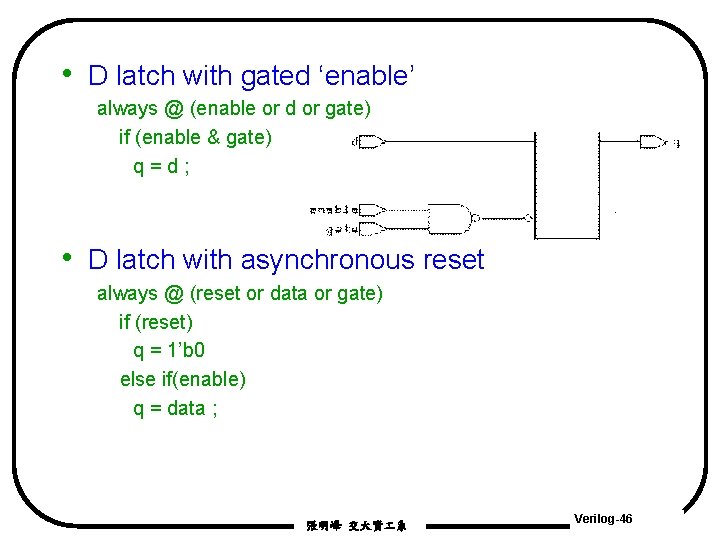

• D latch with gated ‘enable’ always @ (enable or d or gate) if (enable & gate) q=d; • D latch with asynchronous reset always @ (reset or data or gate) if (reset) q = 1’b 0 else if(enable) q = data ; 張明峰 交大資 系 Verilog-46

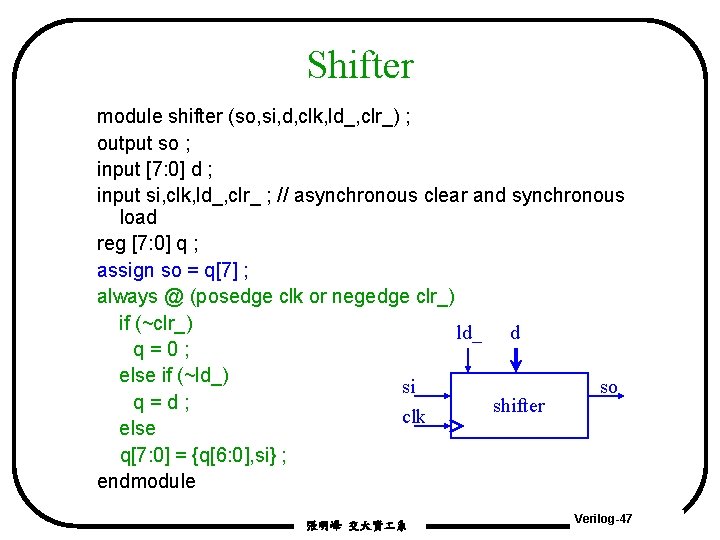

Shifter module shifter (so, si, d, clk, ld_, clr_) ; output so ; input [7: 0] d ; input si, clk, ld_, clr_ ; // asynchronous clear and synchronous load reg [7: 0] q ; assign so = q[7] ; always @ (posedge clk or negedge clr_) if (~clr_) ld_ d q=0; else if (~ld_) si so q=d; shifter clk else q[7: 0] = {q[6: 0], si} ; endmodule 張明峰 交大資 系 Verilog-47

![Counter module bcd_counter(count, ripple_out, clr, clk) ; output [3: 0] count ; output ripple_out Counter module bcd_counter(count, ripple_out, clr, clk) ; output [3: 0] count ; output ripple_out](http://slidetodoc.com/presentation_image_h/e4d9f50839da9da47db52a192533d5f5/image-48.jpg)

Counter module bcd_counter(count, ripple_out, clr, clk) ; output [3: 0] count ; output ripple_out ; reg [3: 0] count ; input clr, clk ; wire ripple_out = (count == 4'b 1001) ? 0: 1 ; // combinational always @ (posedge clk or posedge clr) // combinational + sequential if (clr) ; count = 0 ; else if (count == 4'b 1001) count = 0 ; else count = count + 1 ; endmodule 張明峰 交大資 系 Verilog-48

![Memory module memory (data, addr, read, write); input read, write; input [4: 0] addr; Memory module memory (data, addr, read, write); input read, write; input [4: 0] addr;](http://slidetodoc.com/presentation_image_h/e4d9f50839da9da47db52a192533d5f5/image-49.jpg)

Memory module memory (data, addr, read, write); input read, write; input [4: 0] addr; inout [7: 0] data; reg [7: 0] data_reg; reg [7: 0] memory [0: 8'hff]; parameter load_file = "cput 1. txt"; assign data = (read) ? memory [addr] : 8'hz; always @ (posedge write) memory[addr] = data; initial $readmemb (load_file, memory); endmodule 張明峰 交大資 系 Verilog-49

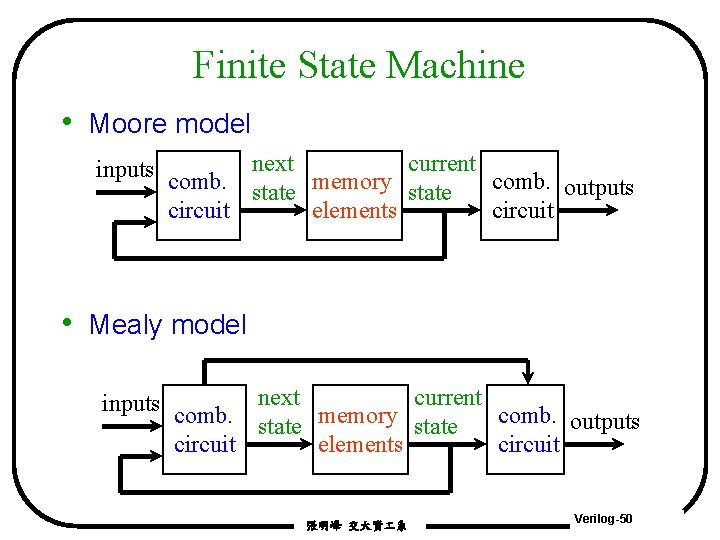

Finite State Machine • Moore model inputs comb. next memory current comb. outputs state circuit elements circuit • Mealy model inputs comb. next memory current comb. outputs state circuit elements circuit 張明峰 交大資 系 Verilog-50

Inefficient Description module count (clock, reset, and_bits, or_bits, xor_bits); input clock, reset; output and_bits, or_bits, xor_bits; reg [2: 0] count; always @(posedge clock) begin if (reset) count = 0; else count = count + 1; and_bits = & count; or_bits = | count; xor_bits = ^ count; endmodule 張明峰 交大資 系 Verilog-51

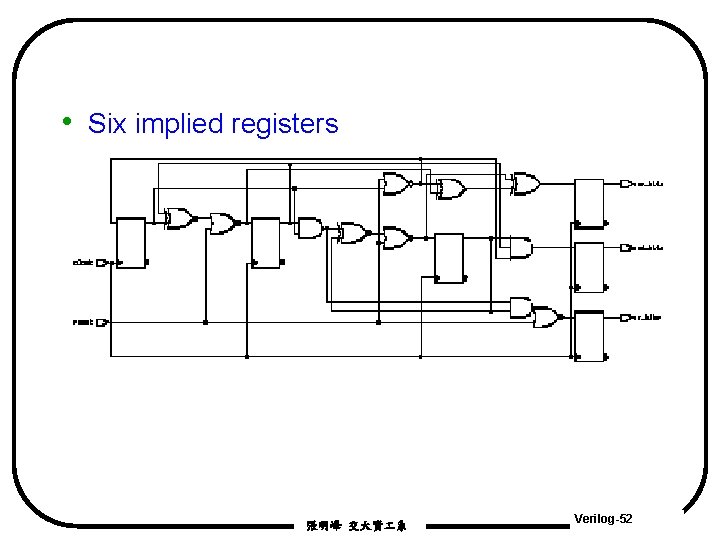

• Six implied registers 張明峰 交大資 系 Verilog-52

Efficient Description l Separate combinational and sequential circuits module count (clock, reset, and_bits, or_bits, xor_bits); input clock, reset; output and_bits, or_bits, xor_bits; reg [2: 0] count; always @(posedge clock) begin if (reset) count = 0; else count = count + 1; end // combinational circuits always @(count) begin and_bits = & count; or_bits = | count; xor_bits = ^ count; endmodule 張明峰 交大資 系 Verilog-53

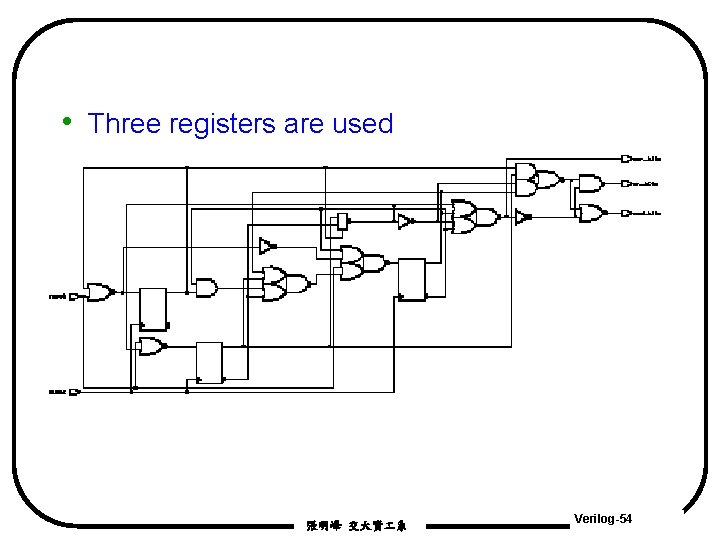

• Three registers are used 張明峰 交大資 系 Verilog-54

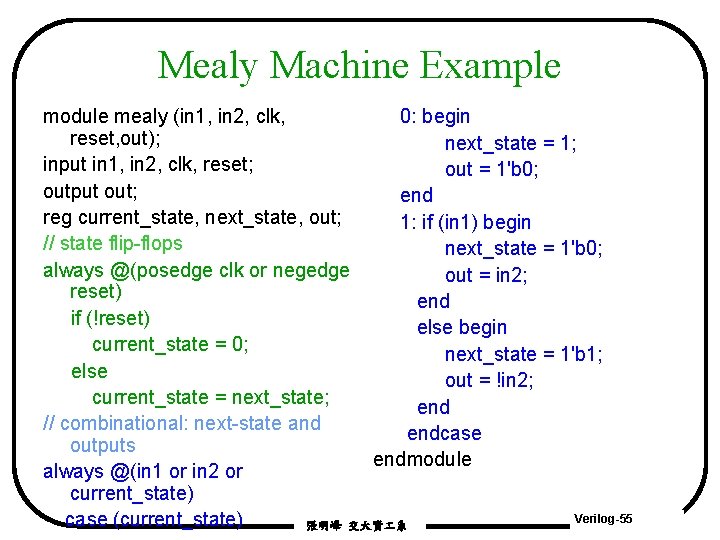

Mealy Machine Example module mealy (in 1, in 2, clk, 0: begin reset, out); next_state = 1; input in 1, in 2, clk, reset; out = 1'b 0; output out; end reg current_state, next_state, out; 1: if (in 1) begin // state flip-flops next_state = 1'b 0; always @(posedge clk or negedge out = in 2; reset) end if (!reset) else begin current_state = 0; next_state = 1'b 1; else out = !in 2; current_state = next_state; end // combinational: next-state and endcase outputs endmodule always @(in 1 or in 2 or current_state) Verilog-55 case (current_state) 張明峰 交大資 系

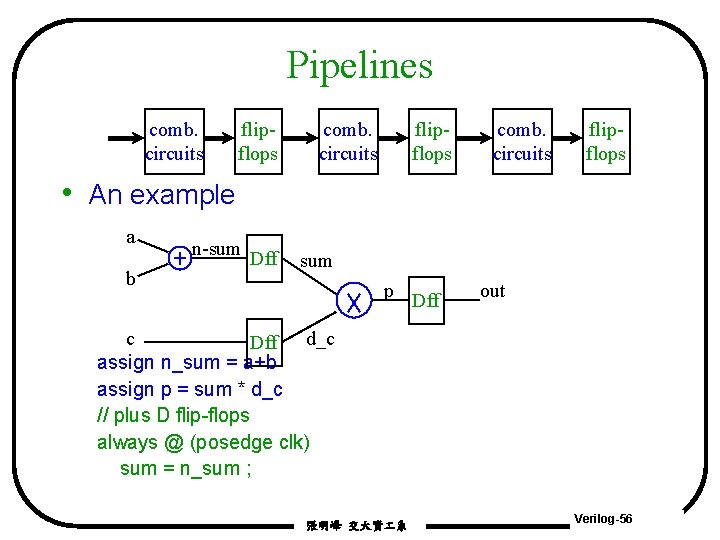

Pipelines comb. circuits flipflops • An example a b n-sum Dff sum p Dff out c Dff d_c assign n_sum = a+b assign p = sum * d_c // plus D flip-flops always @ (posedge clk) sum = n_sum ; 張明峰 交大資 系 Verilog-56

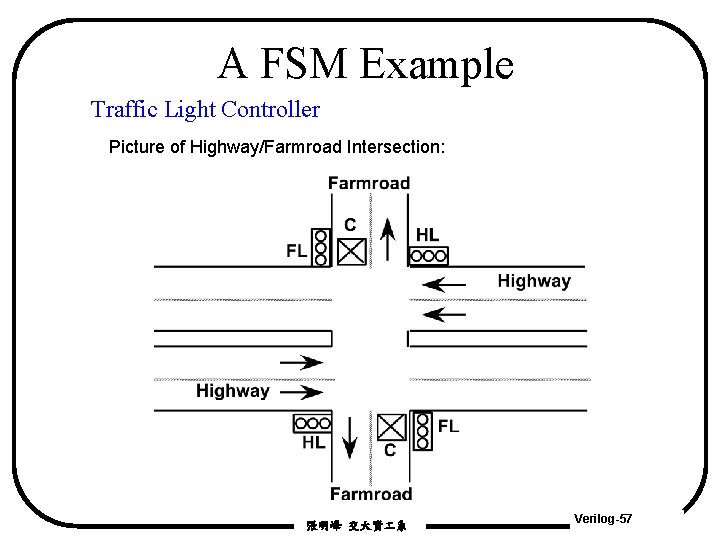

A FSM Example Traffic Light Controller Picture of Highway/Farmroad Intersection: 張明峰 交大資 系 Verilog-57

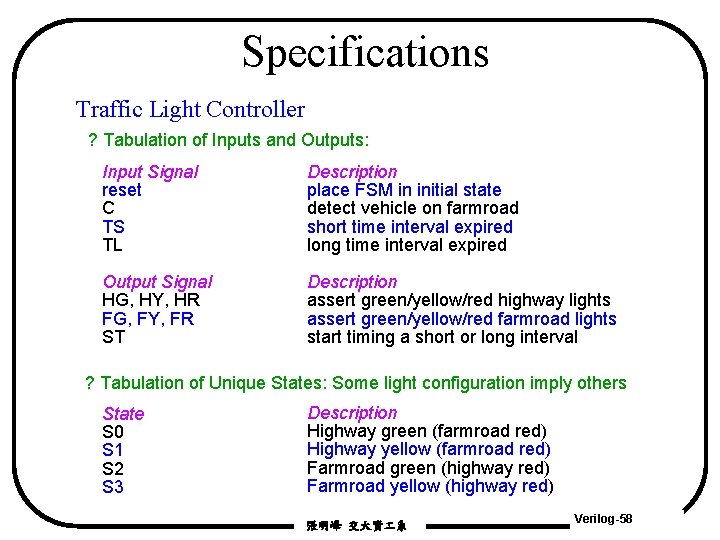

Specifications Traffic Light Controller ? Tabulation of Inputs and Outputs: Input Signal reset C TS TL Description place FSM in initial state detect vehicle on farmroad short time interval expired long time interval expired Output Signal HG, HY, HR FG, FY, FR ST Description assert green/yellow/red highway lights assert green/yellow/red farmroad lights start timing a short or long interval ? Tabulation of Unique States: Some light configuration imply others State S 0 S 1 S 2 S 3 Description Highway green (farmroad red) Highway yellow (farmroad red) Farmroad green (highway red) Farmroad yellow (highway red) 張明峰 交大資 系 Verilog-58

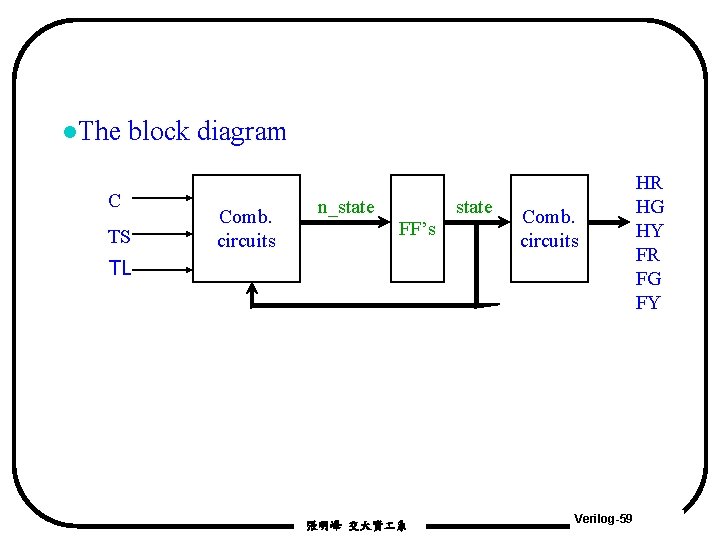

l. The block diagram C TS Comb. circuits n_state FF’s Comb. circuits TL 張明峰 交大資 系 Verilog-59 HR HG HY FR FG FY

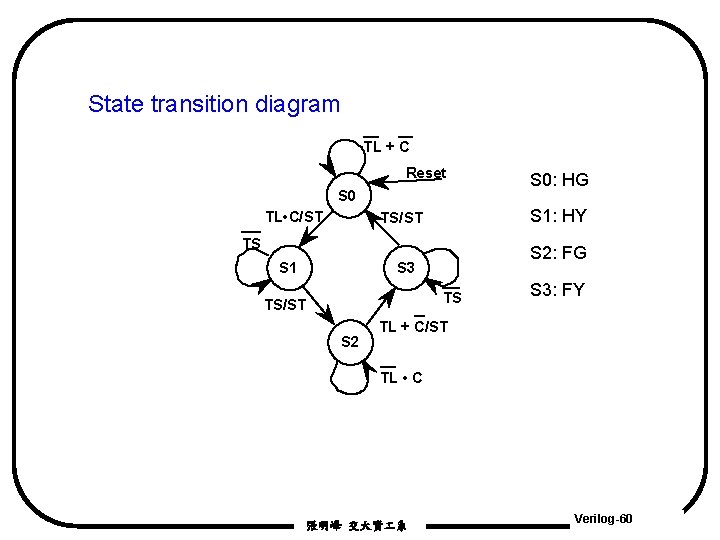

State transition diagram TL + C Reset S 0 TL • C/ST S 1: HY TS/ST TS S 1 S 2: FG S 3 TS TS/ST S 2 S 0: HG S 3: FY TL + C/ST TL • C 張明峰 交大資 系 Verilog-60

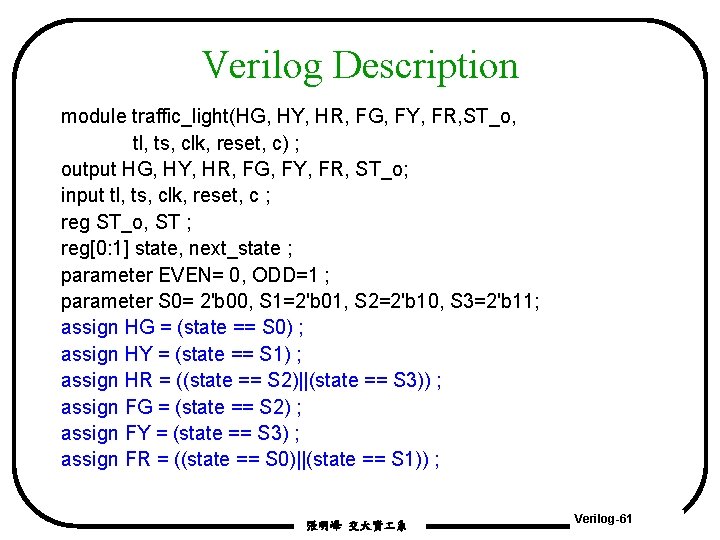

Verilog Description module traffic_light(HG, HY, HR, FG, FY, FR, ST_o, tl, ts, clk, reset, c) ; output HG, HY, HR, FG, FY, FR, ST_o; input tl, ts, clk, reset, c ; reg ST_o, ST ; reg[0: 1] state, next_state ; parameter EVEN= 0, ODD=1 ; parameter S 0= 2'b 00, S 1=2'b 01, S 2=2'b 10, S 3=2'b 11; assign HG = (state == S 0) ; assign HY = (state == S 1) ; assign HR = ((state == S 2)||(state == S 3)) ; assign FG = (state == S 2) ; assign FY = (state == S 3) ; assign FR = ((state == S 0)||(state == S 1)) ; 張明峰 交大資 系 Verilog-61

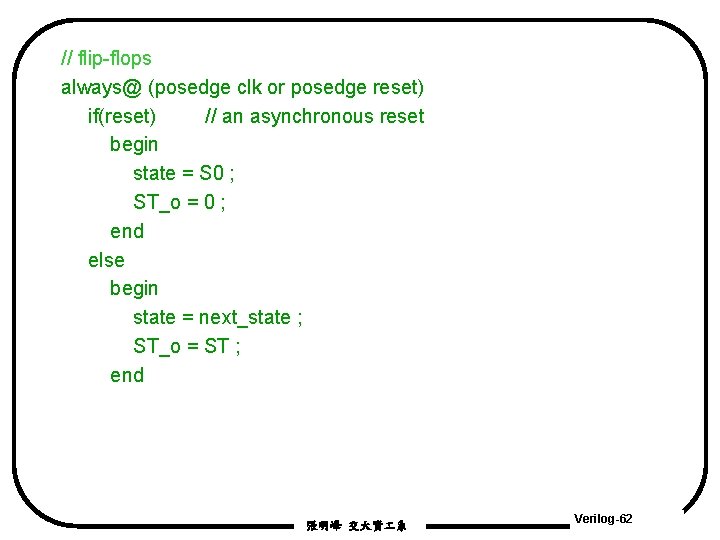

// flip-flops always@ (posedge clk or posedge reset) if(reset) // an asynchronous reset begin state = S 0 ; ST_o = 0 ; end else begin state = next_state ; ST_o = ST ; end 張明峰 交大資 系 Verilog-62

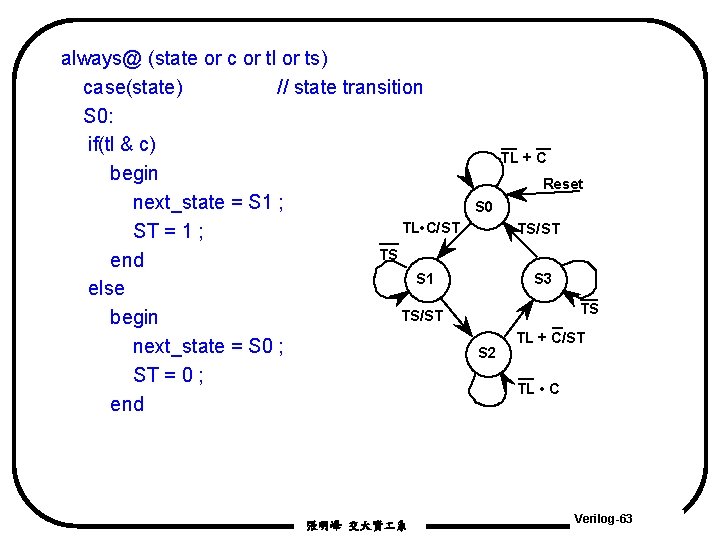

always@ (state or c or tl or ts) case(state) // state transition S 0: if(tl & c) begin next_state = S 1 ; TL • C/ST ST = 1 ; TS end S 1 else TS/ST begin next_state = S 0 ; ST = 0 ; end 張明峰 交大資 系 TL + C Reset S 0 TS/ST S 3 TS S 2 TL + C/ST TL • C Verilog-63

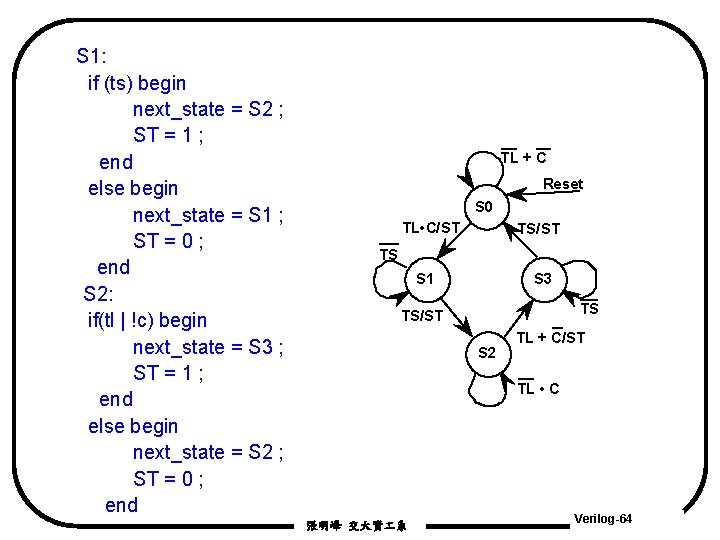

S 1: if (ts) begin next_state = S 2 ; ST = 1 ; end else begin next_state = S 1 ; ST = 0 ; end S 2: if(tl | !c) begin next_state = S 3 ; ST = 1 ; end else begin next_state = S 2 ; ST = 0 ; end TL + C Reset S 0 TL • C/ST TS S 1 S 3 TS TS/ST S 2 TL + C/ST TL • C 張明峰 交大資 系 Verilog-64

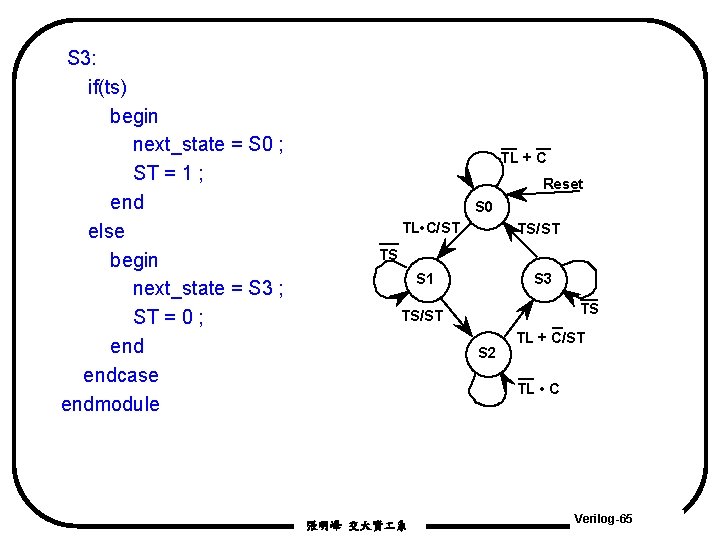

S 3: if(ts) begin next_state = S 0 ; ST = 1 ; end else begin next_state = S 3 ; ST = 0 ; endcase endmodule TL + C Reset S 0 TL • C/ST TS S 1 S 3 TS TS/ST S 2 TL + C/ST TL • C 張明峰 交大資 系 Verilog-65

Efficient Modeling Techniques • Separate combinational and sequential circuits – always know your target circuits • Separate structured circuits and random logic – structured: data path, XORs, MUXs – random logic: control logic, decoder, encoder • Use parentheses control complex structure • . . . 張明峰 交大資 系 Verilog-66

Conclusions • Verilog modeling – structured modeling – continuous assignment – RTL modeling • Design digital systems – separate combinational and sequential description – always keep your target circuits in mind 張明峰 交大資 系 Verilog-67

Reference • Verilog-XL Training Manual, CIC • Logic Synthesis Design Kit, CIC • HDL Compiler for Verilog Reference Manual, • Synopsys Synthesis Application Notes, Synopsys Online Documentation 張明峰 交大資 系 Verilog-68

- Slides: 68