Lab 01 Digital Circuits Design By Xilinx ISE

Lab 01 Digital Circuits Design By Xilinx ISE 1

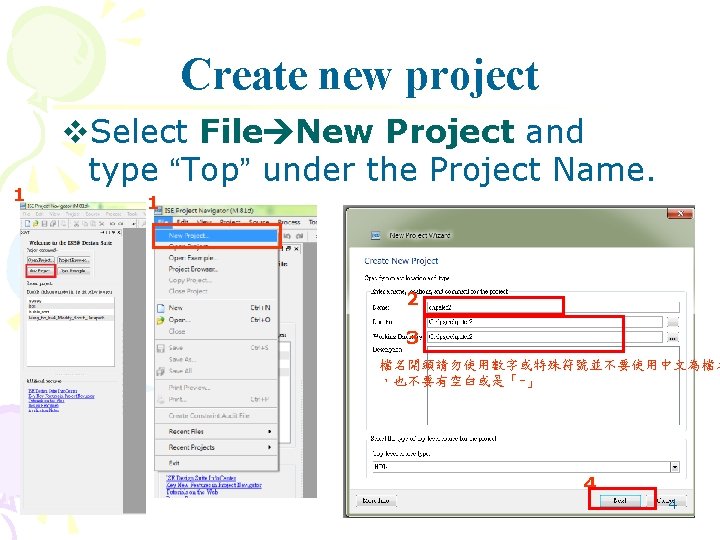

Create new project 1 v. Select File New Project and type “Top” under the Project Name. 1 2 3 檔名開頭請勿使用數字或特殊符號並不要使用中文為檔名 ,也不要有空白或是「-」 4 4

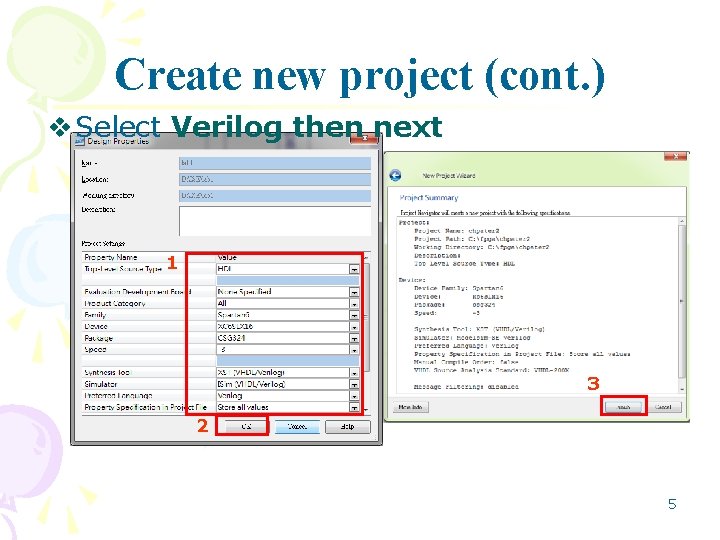

Create new project (cont. ) v Select Verilog then next 1 3 2 5

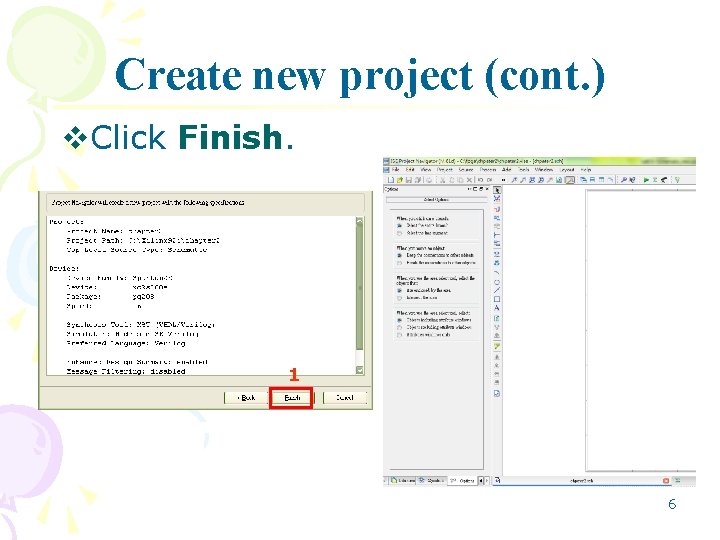

Create new project (cont. ) v. Click Finish. 1 6

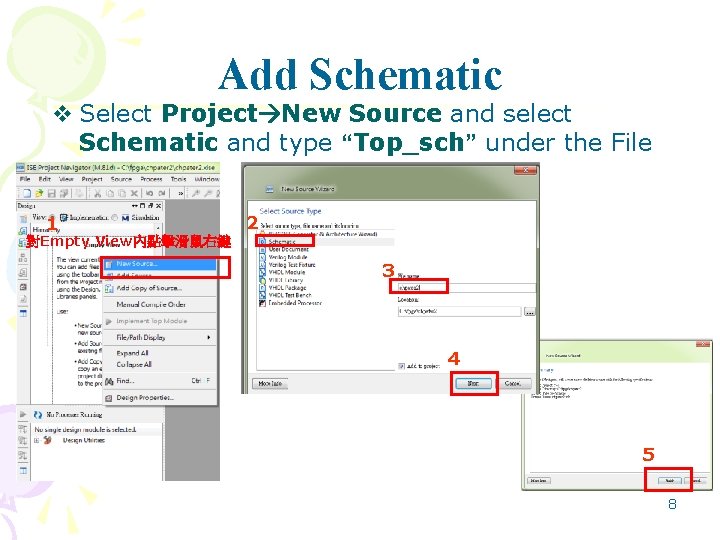

Add Schematic v Select Project New Source and select Schematic and type “Top_sch” under the File Name. 1 對Empty View內點擊滑鼠右鍵 2 3 4 5 8

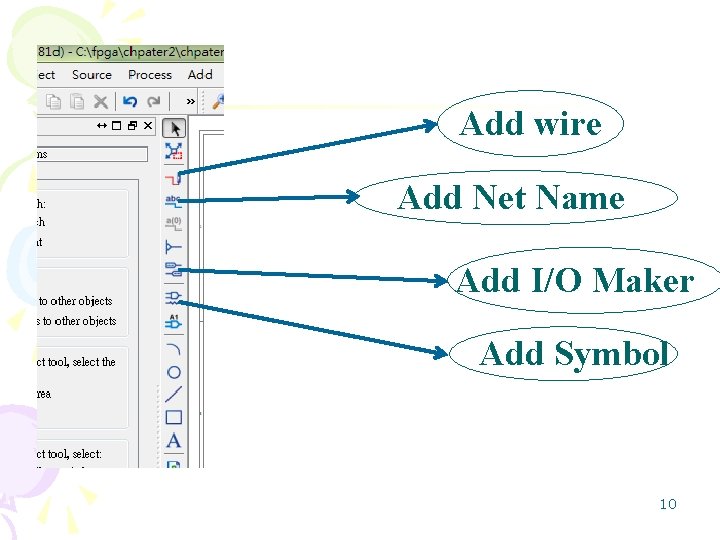

Add wire Add Net Name Add I/O Maker Add Symbol 10

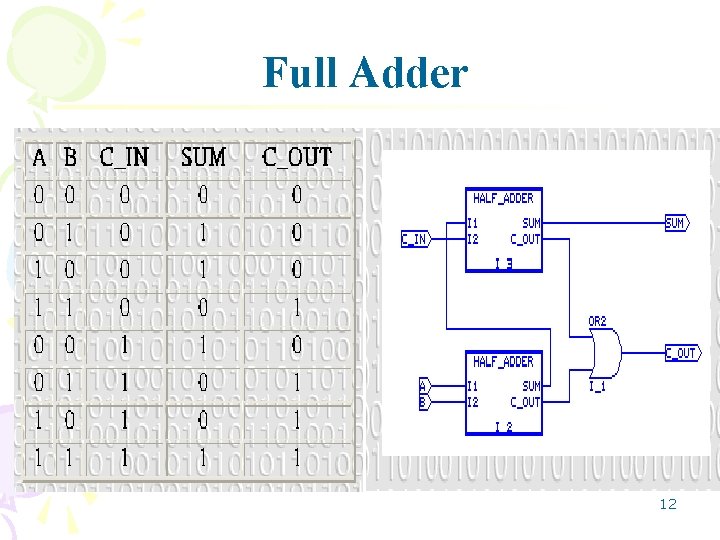

Full Adder 12

Full Adder (cont. ) v Select Symbols and then select symbol that we need AND gate, XOR gate and OR gate. 1 3 5 4 6 2 13

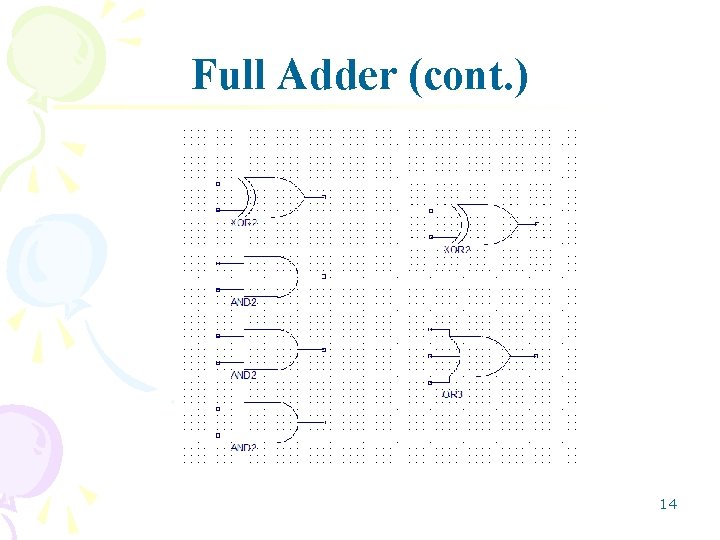

Full Adder (cont. ) 14

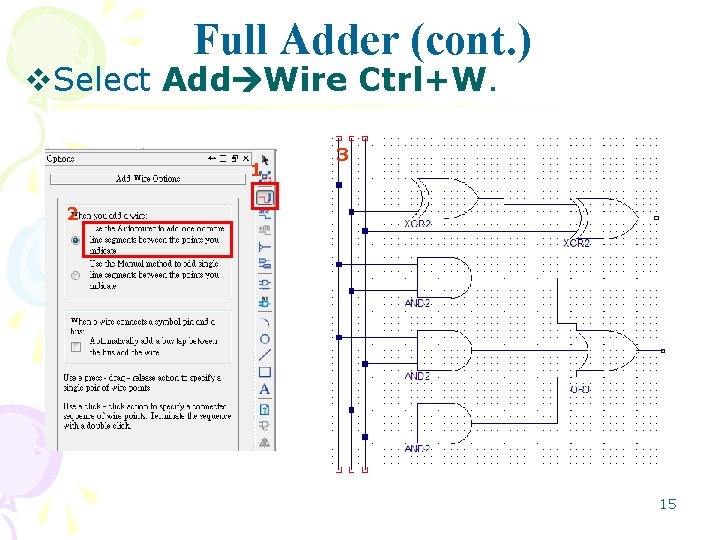

Full Adder (cont. ) v. Select Add Wire Ctrl+W. 1 3 2 15

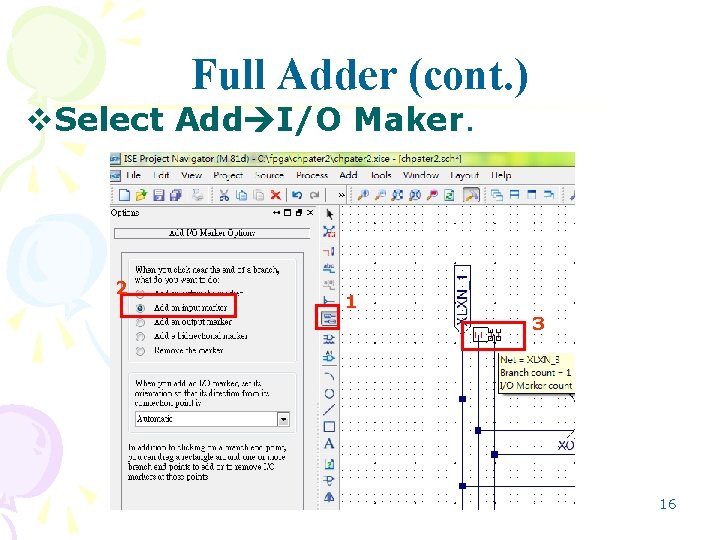

Full Adder (cont. ) v. Select Add I/O Maker. 2 1 3 16

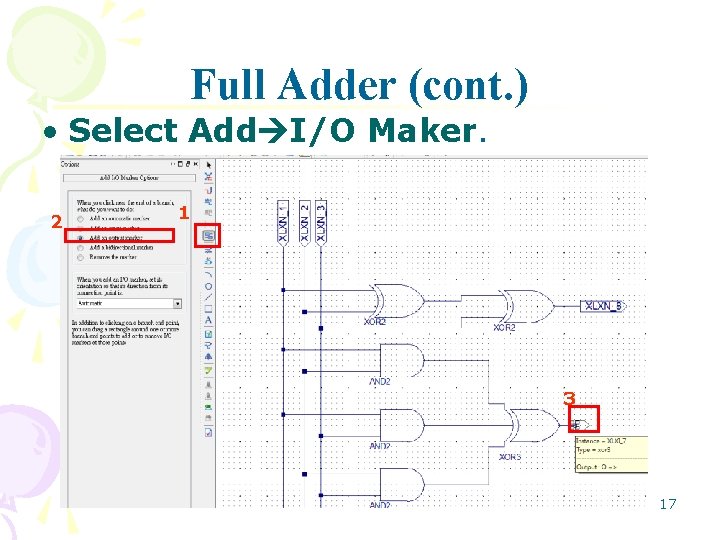

Full Adder (cont. ) • Select Add I/O Maker. 2 1 3 17

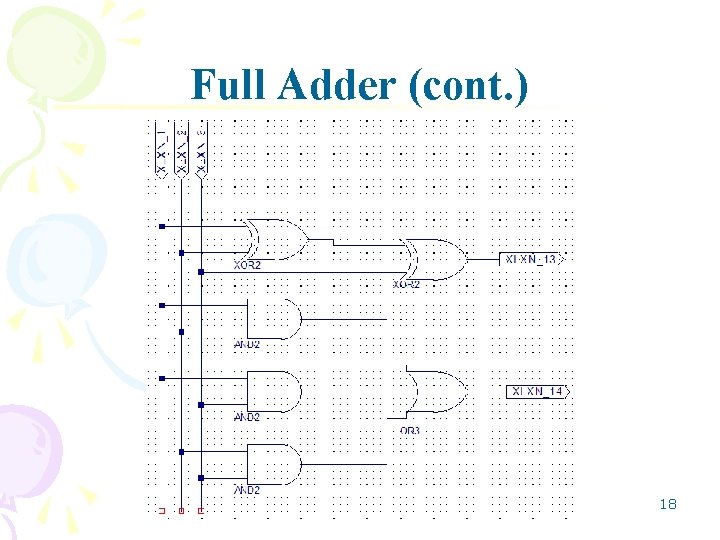

Full Adder (cont. ) 18

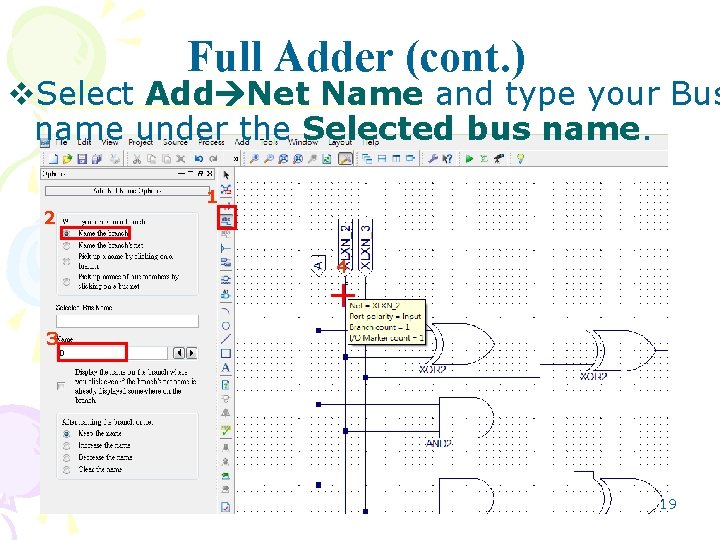

Full Adder (cont. ) v. Select Add Net Name and type your Bus name under the Selected bus name. 2 1 4 3 19

Full Adder (cont. ) 20

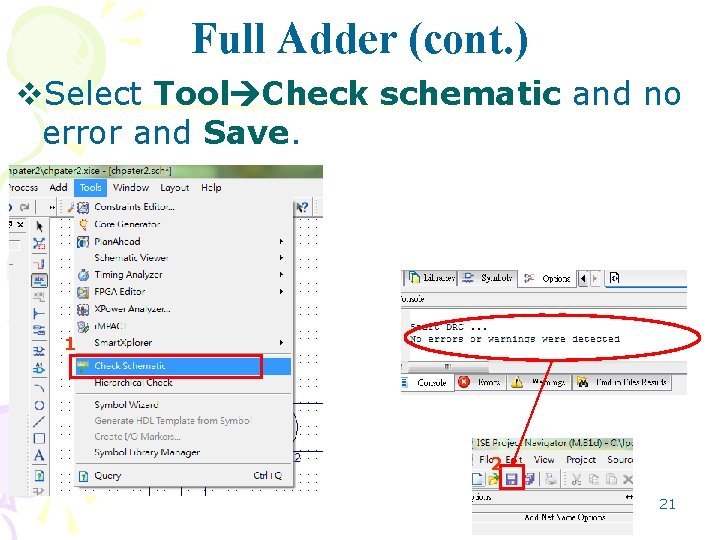

Full Adder (cont. ) v. Select Tool Check schematic and no error and Save. 1 2 21

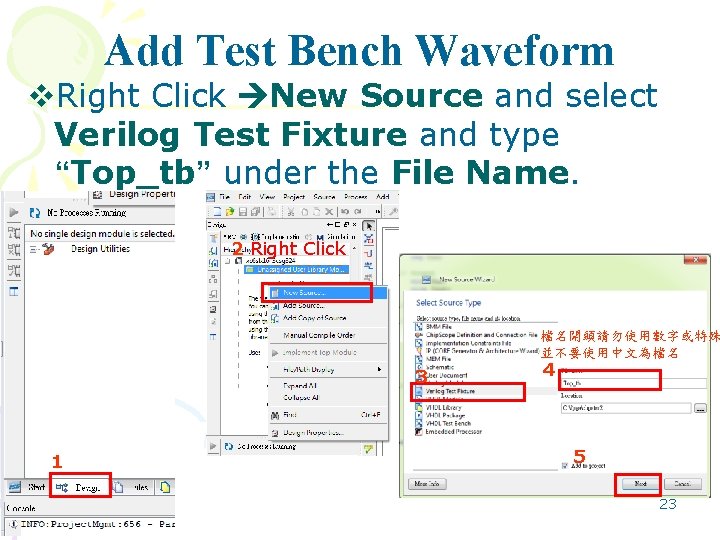

Add Test Bench Waveform v. Right Click New Source and select Verilog Test Fixture and type “Top_tb” under the File Name. 2 Right Click 檔名開頭請勿使用數字或特殊 並不要使用中文為檔名 3 1 4 5 23

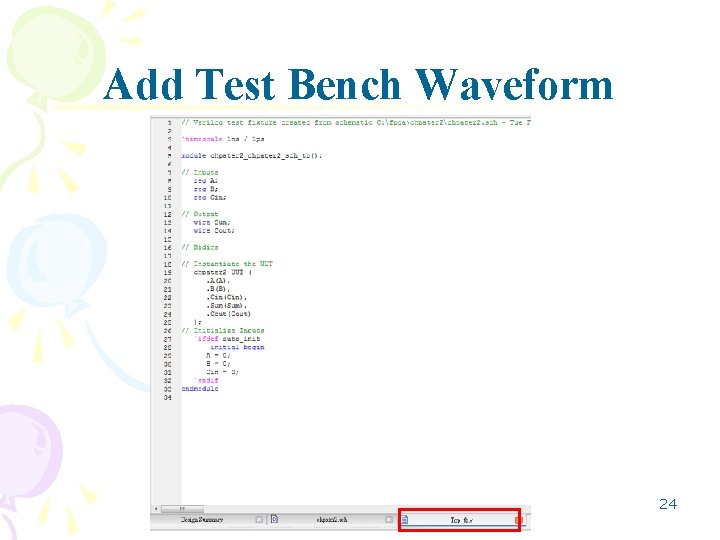

Add Test Bench Waveform 24

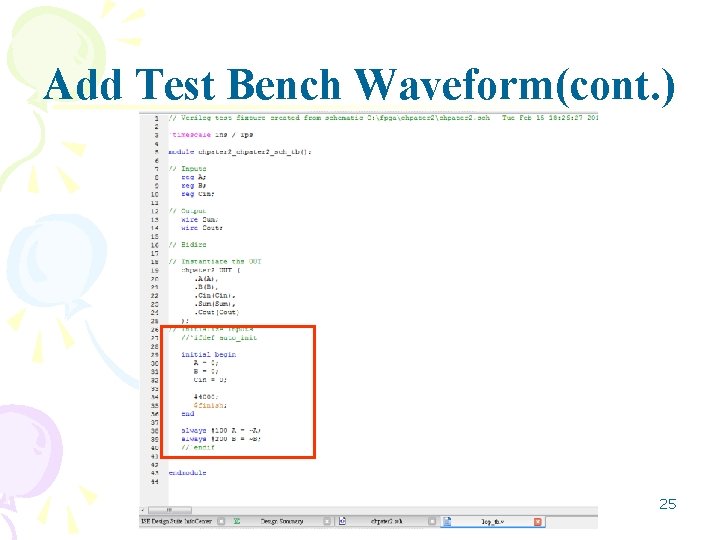

Add Test Bench Waveform(cont. ) 25

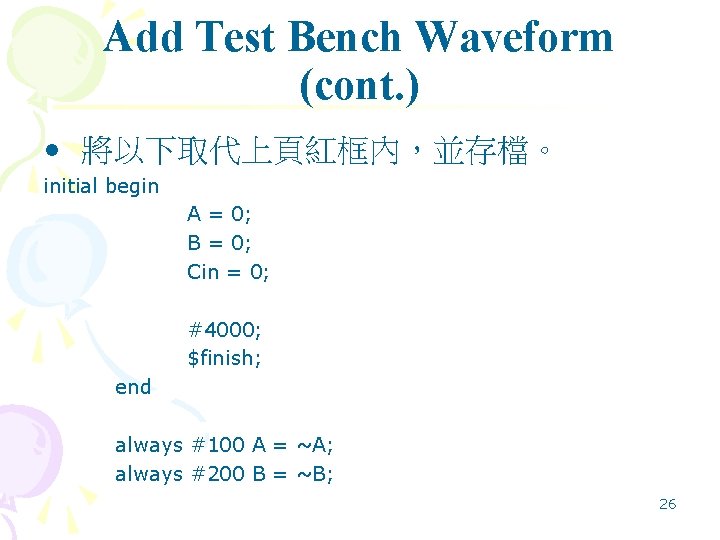

Add Test Bench Waveform (cont. ) • 將以下取代上頁紅框內,並存檔。 initial begin A = 0; B = 0; Cin = 0; #4000; $finish; end always #100 A = ~A; always #200 B = ~B; 26

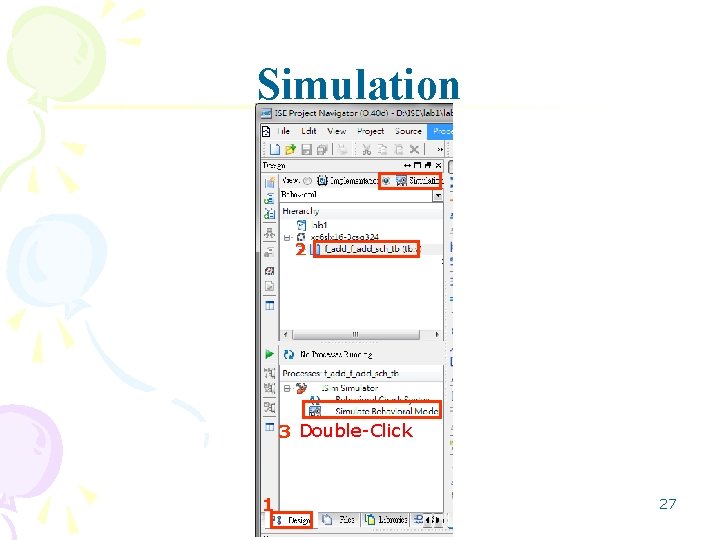

Simulation 2 3 Double-Click 1 27

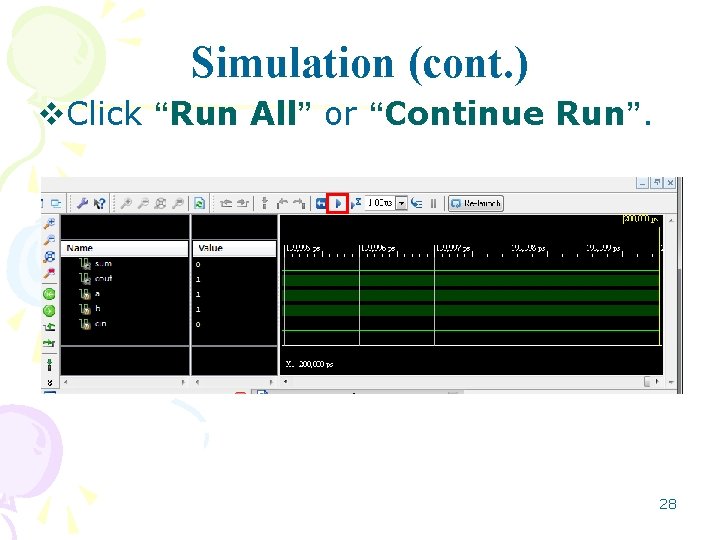

Simulation (cont. ) v. Click “Run All” or “Continue Run”. 28

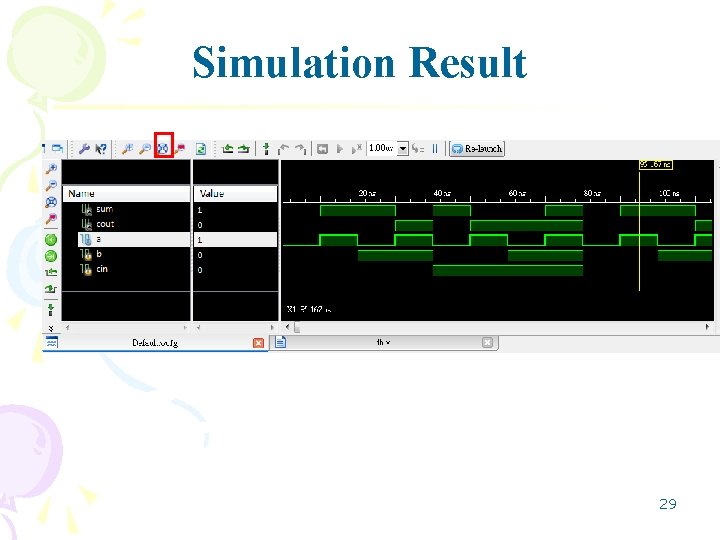

Simulation Result 29

Simulation Result (cont. ) Full Adder truth table A B C_IN SUM C_OUT 0 0 0 1 0 1 0 0 1 1 0 0 1 1 1 1 30

Question & Answer 31

- Slides: 31