La matrice per Apsel VI e per Superpix

- Slides: 23

La matrice per Apsel. VI (e per Superpix 1) Fabio Morsani, 24 -09 -2010 F. Morsani 1

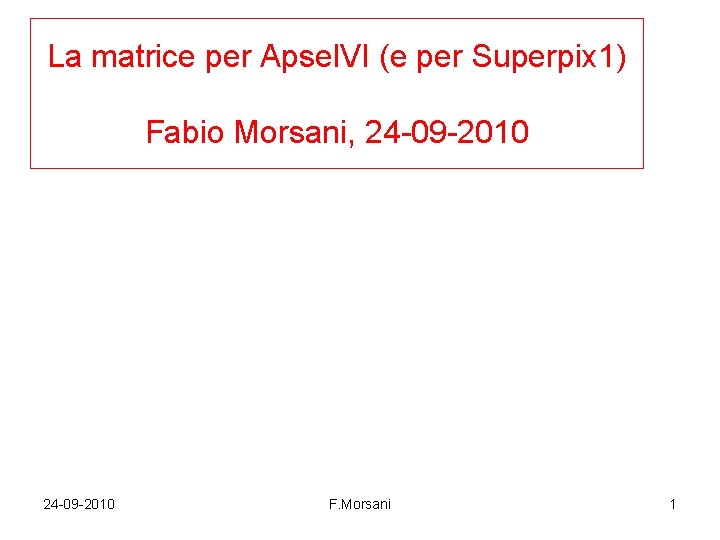

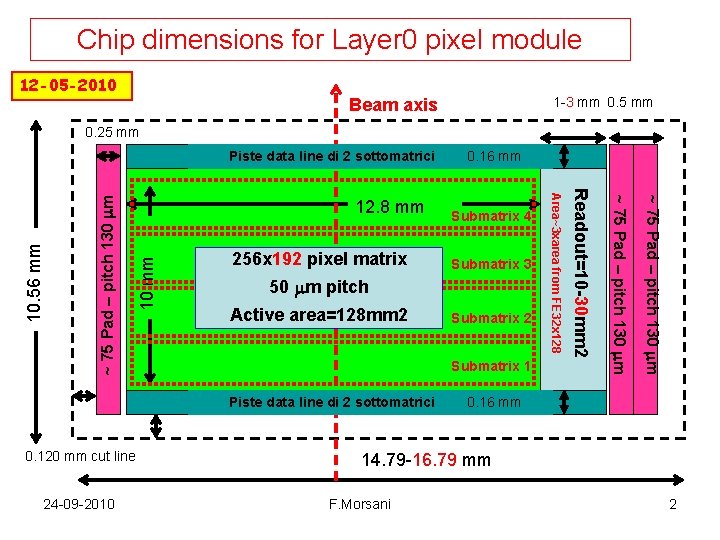

Chip dimensions for Layer 0 pixel module 12 -05 -2010 1 -3 mm 0. 5 mm Beam axis 0. 25 mm 10 mm ~ 75 Pad – pitch 130 mm Active area=128 mm 2 24 -09 -2010 Submatrix 2 Submatrix 1 ~ 75 Pad – pitch 130 mm 50 mm pitch Piste data line di 2 sottomatrici 0. 120 mm cut line Submatrix 3 ~ 75 Pad – pitch 130 mm 256 x 192 pixel matrix Submatrix 4 Readout=10 -30 mm 2 12. 8 mm 0. 16 mm Area~3 xarea from FE 32 x 128 10. 56 mm Piste data line di 2 sottomatrici 0. 16 mm 14. 79 -16. 79 mm F. Morsani 2

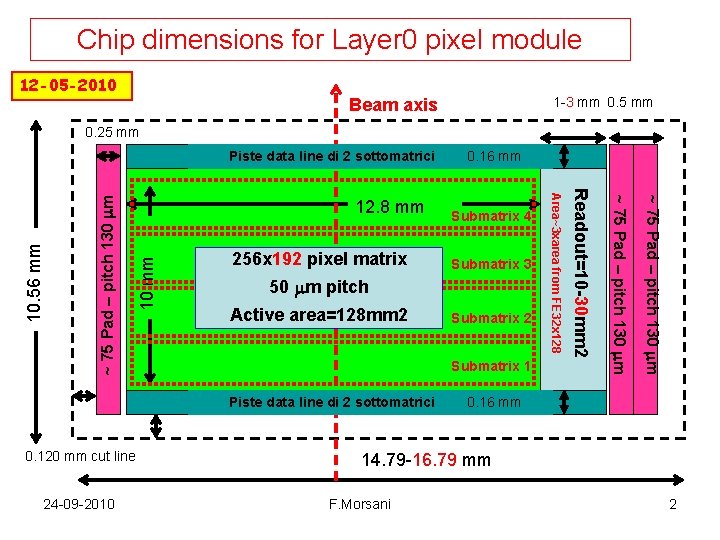

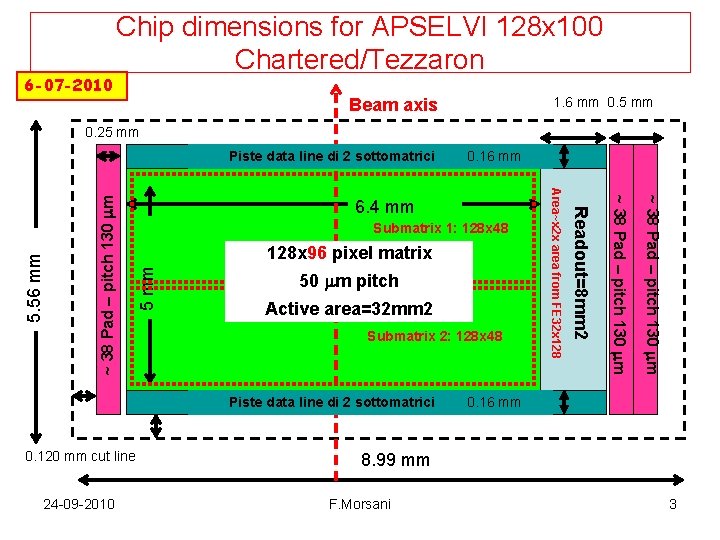

6 -07 -2010 Chip dimensions for APSELVI 128 x 100 Chartered/Tezzaron 1. 6 mm 0. 5 mm Beam axis 0. 25 mm ~ 38 Pad – pitch 130 mm 50 mm pitch Active area=32 mm 2 Submatrix 2: 128 x 48 24 -09 -2010 ~ 38 Pad – pitch 130 mm 128 x 96 pixel matrix ~ 38 Pad – pitch 130 mm Submatrix 1: 128 x 48 Readout=8 mm 2 6. 4 mm Piste data line di 2 sottomatrici 0. 120 mm cut line 0. 16 mm Area~x 2 x area from FE 32 x 128 5. 56 mm Piste data line di 2 sottomatrici 0. 16 mm 8. 99 mm F. Morsani 3

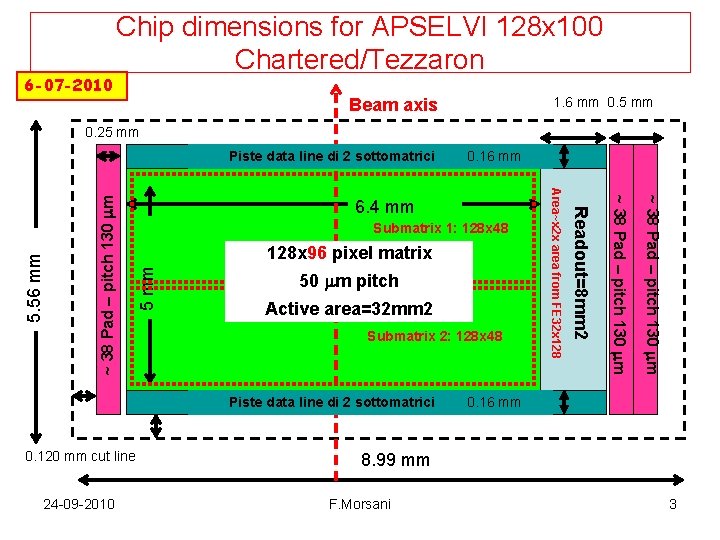

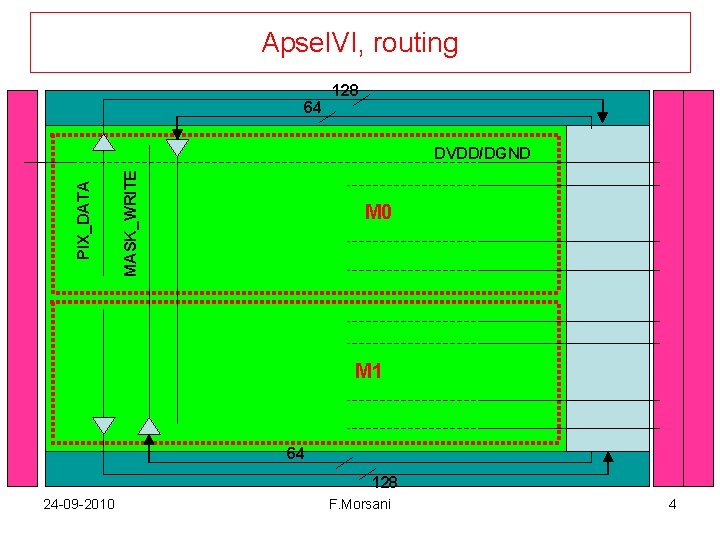

Apsel. VI, routing 64 128 MASK_WRITE PIX_DATA DVDD/DGND M 0 M 1 64 128 24 -09 -2010 F. Morsani 4

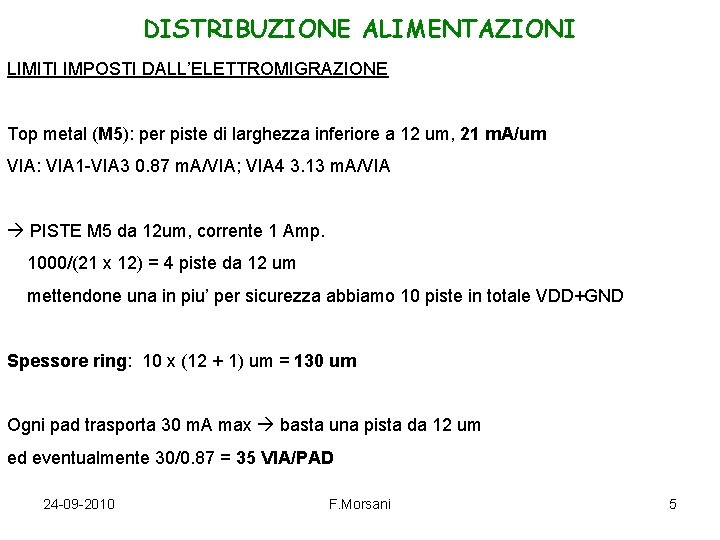

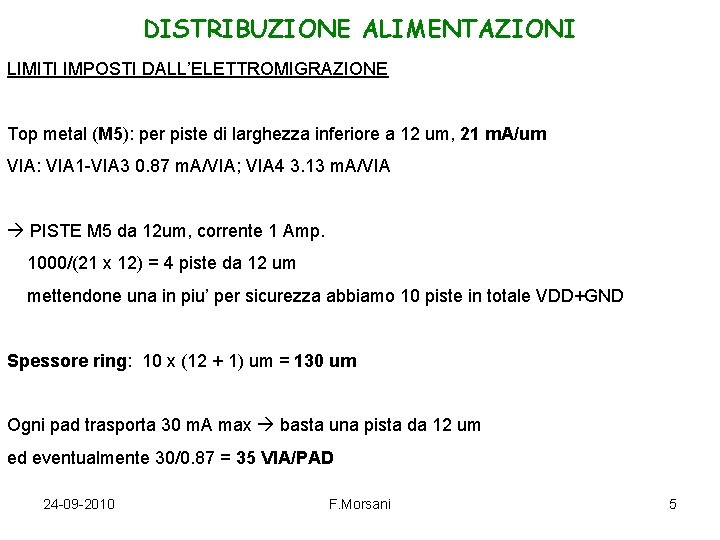

DISTRIBUZIONE ALIMENTAZIONI LIMITI IMPOSTI DALL’ELETTROMIGRAZIONE Top metal (M 5): per piste di larghezza inferiore a 12 um, 21 m. A/um VIA: VIA 1 -VIA 3 0. 87 m. A/VIA; VIA 4 3. 13 m. A/VIA PISTE M 5 da 12 um, corrente 1 Amp. 1000/(21 x 12) = 4 piste da 12 um mettendone una in piu’ per sicurezza abbiamo 10 piste in totale VDD+GND Spessore ring: 10 x (12 + 1) um = 130 um Ogni pad trasporta 30 m. A max basta una pista da 12 um ed eventualmente 30/0. 87 = 35 VIA/PAD 24 -09 -2010 F. Morsani 5

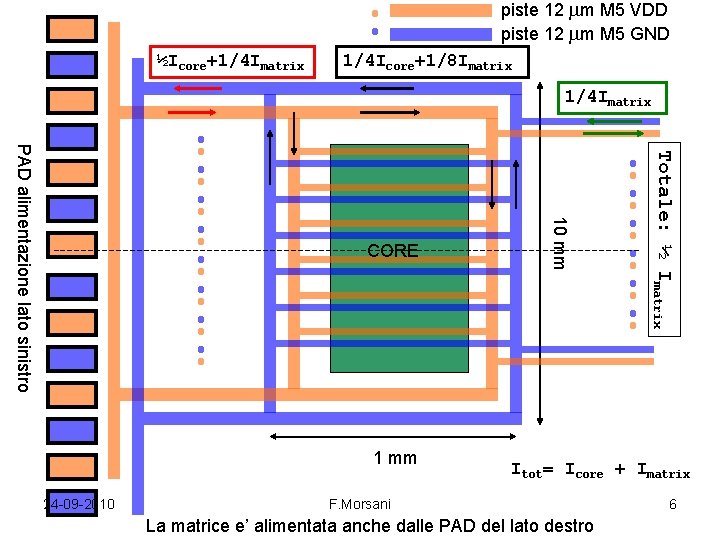

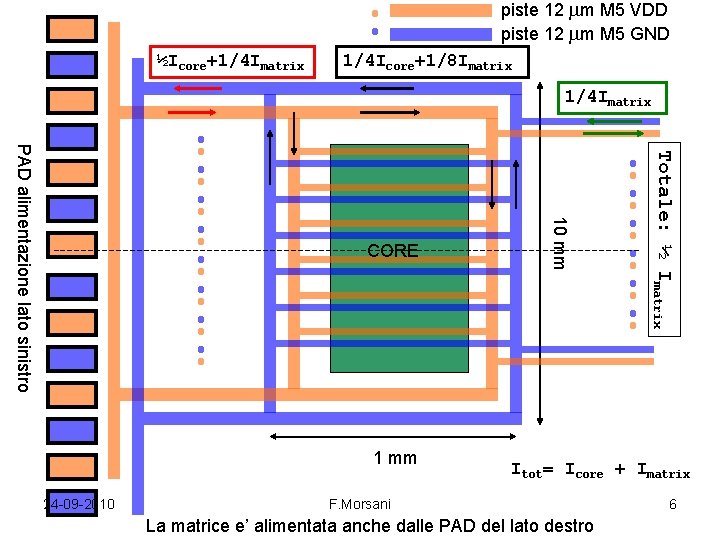

piste 12 mm M 5 VDD piste 12 mm M 5 GND ½Icore+1/4 Imatrix 1/4 Icore+1/8 Imatrix 1/4 Imatrix 24 -09 -2010 Totale: ½ Imatrix 1 mm 10 mm PAD alimentazione lato sinistro CORE Itot= Icore + Imatrix F. Morsani La matrice e’ alimentata anche dalle PAD del lato destro 6

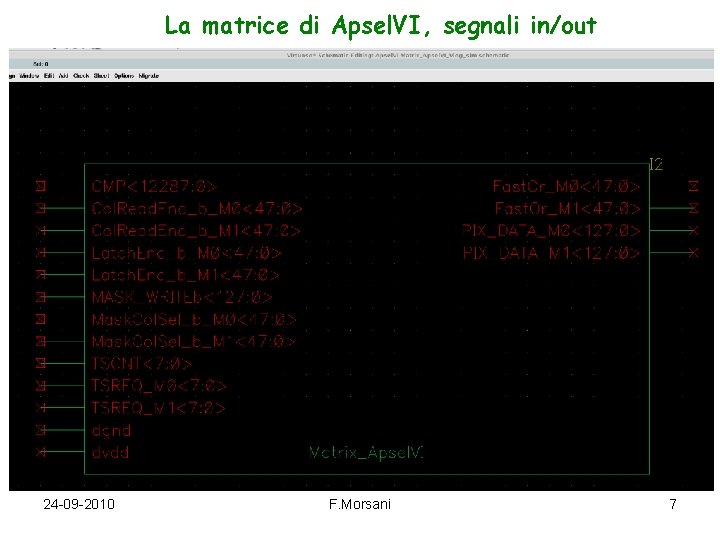

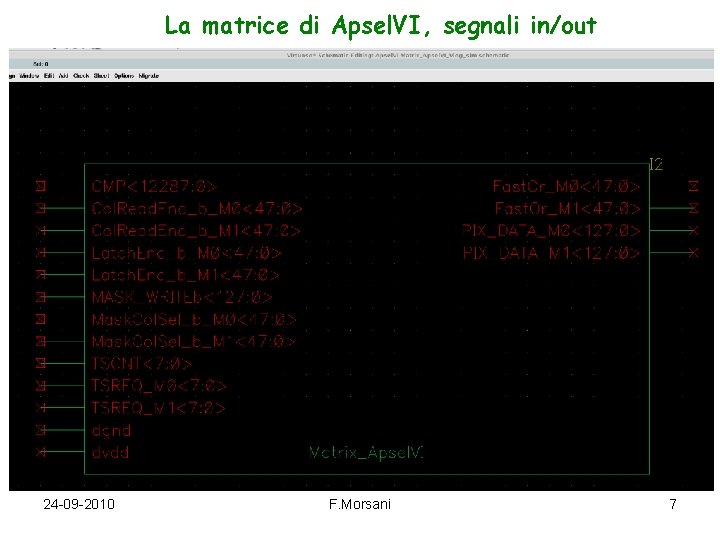

La matrice di Apsel. VI, segnali in/out 24 -09 -2010 F. Morsani 7

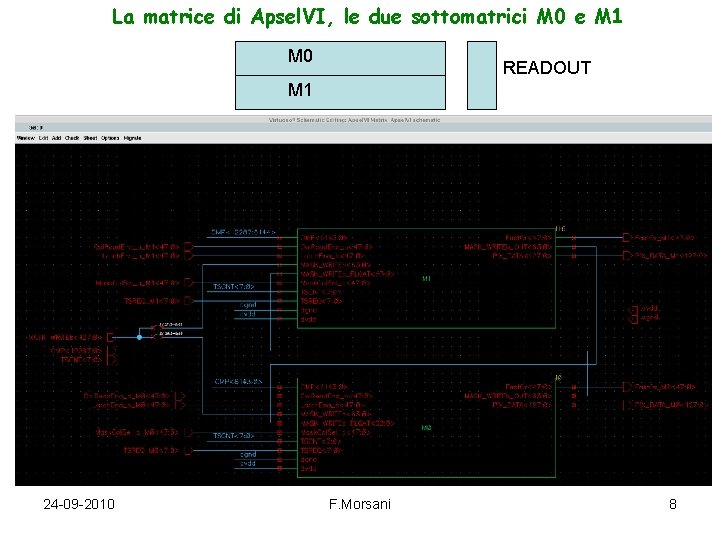

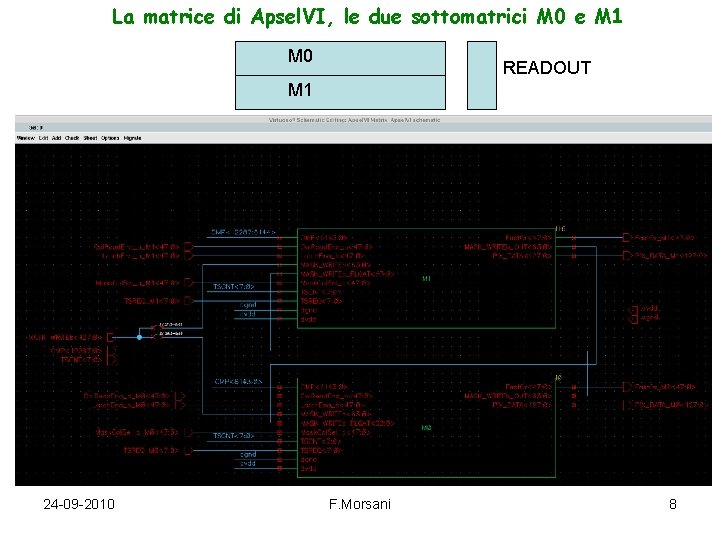

La matrice di Apsel. VI, le due sottomatrici M 0 e M 1 M 0 READOUT M 1 24 -09 -2010 F. Morsani 8

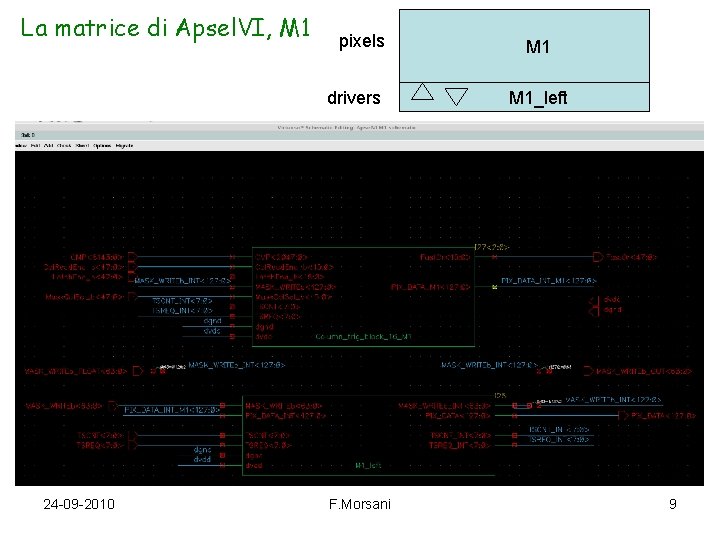

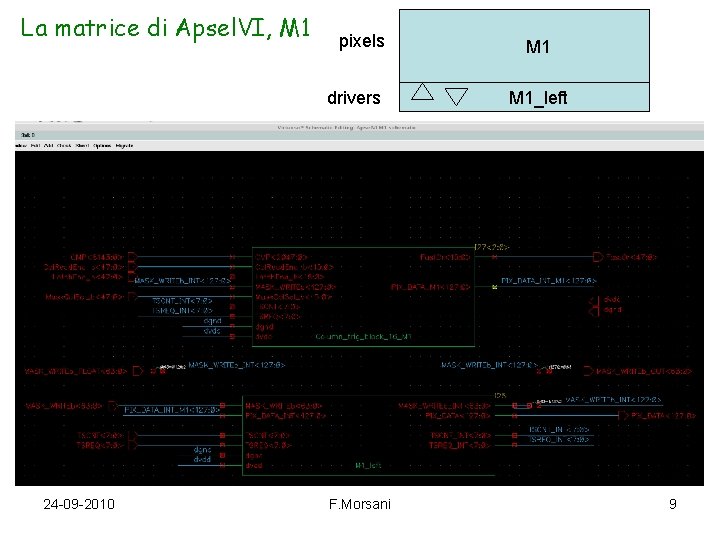

La matrice di Apsel. VI, M 1 pixels drivers 24 -09 -2010 F. Morsani M 1_left 9

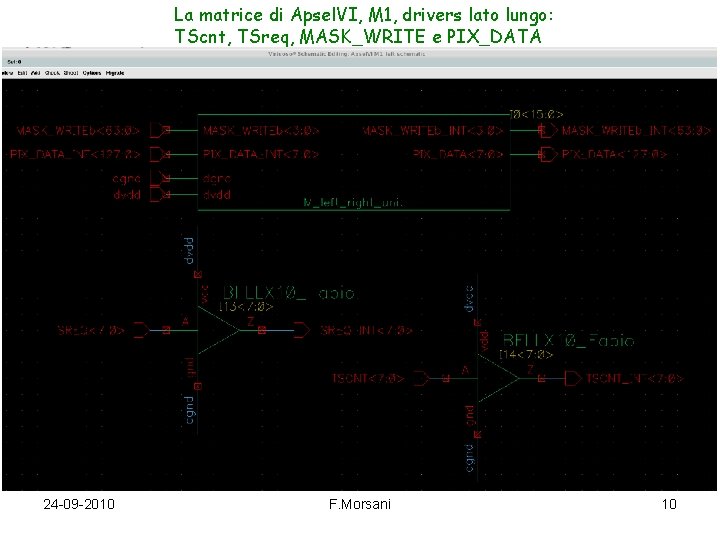

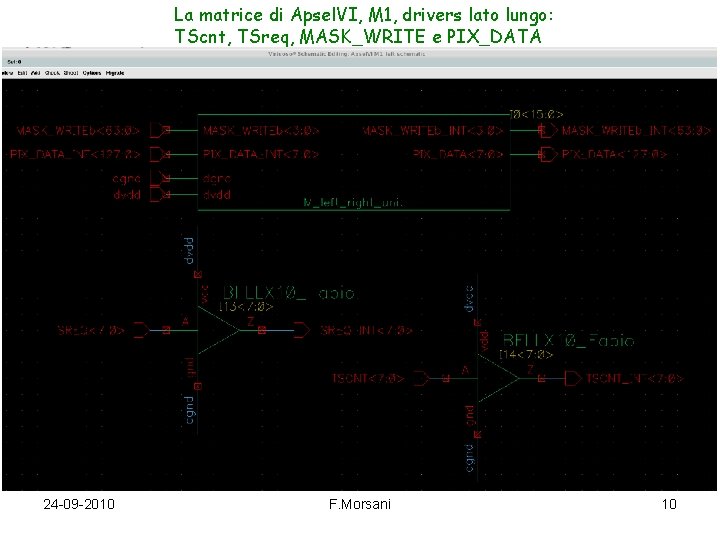

La matrice di Apsel. VI, M 1, drivers lato lungo: TScnt, TSreq, MASK_WRITE e PIX_DATA 24 -09 -2010 F. Morsani 10

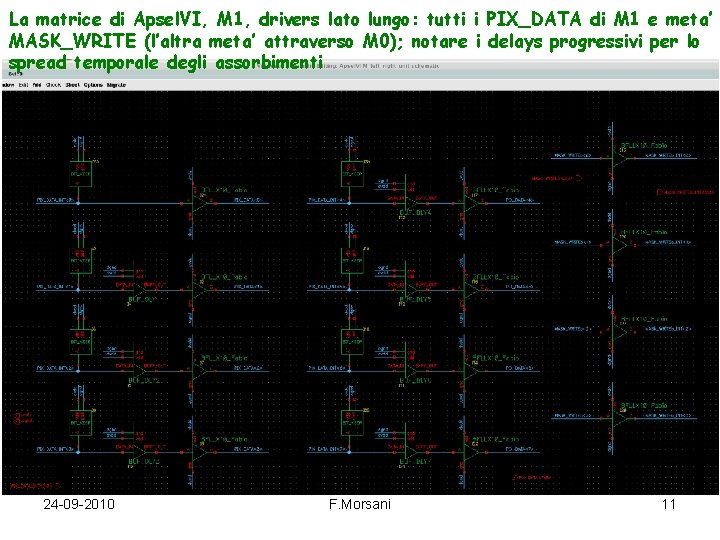

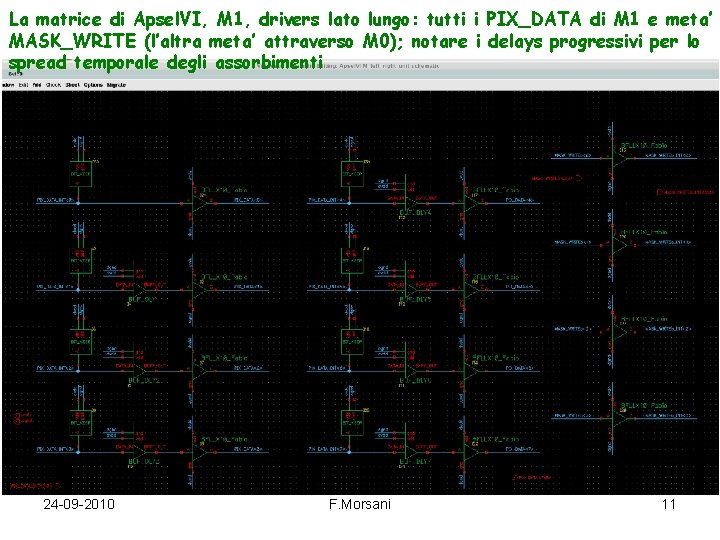

La matrice di Apsel. VI, M 1, drivers lato lungo: tutti i PIX_DATA di M 1 e meta’ MASK_WRITE (l’altra meta’ attraverso M 0); notare i delays progressivi per lo spread temporale degli assorbimenti 24 -09 -2010 F. Morsani 11

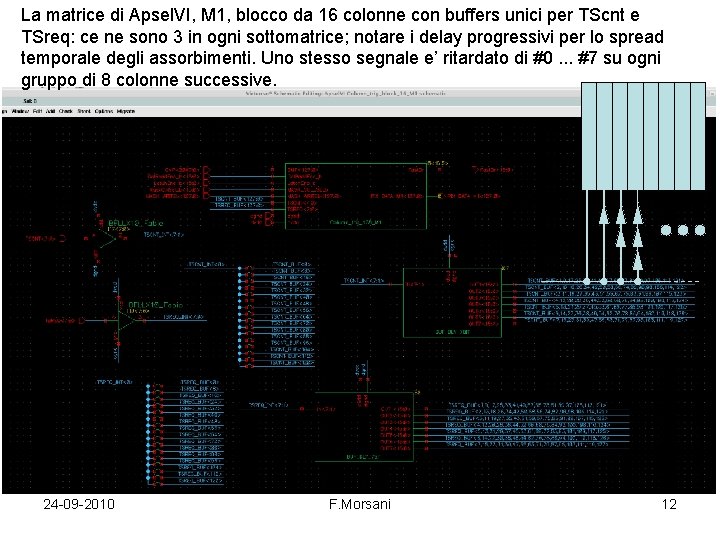

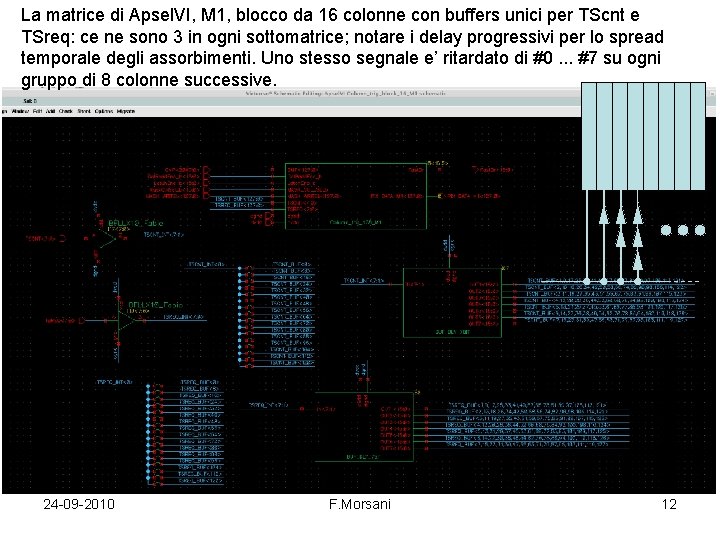

La matrice di Apsel. VI, M 1, blocco da 16 colonne con buffers unici per TScnt e TSreq: ce ne sono 3 in ogni sottomatrice; notare i delay progressivi per lo spread temporale degli assorbimenti. Uno stesso segnale e’ ritardato di #0. . . #7 su ogni gruppo di 8 colonne successive. 24 -09 -2010 F. Morsani 12

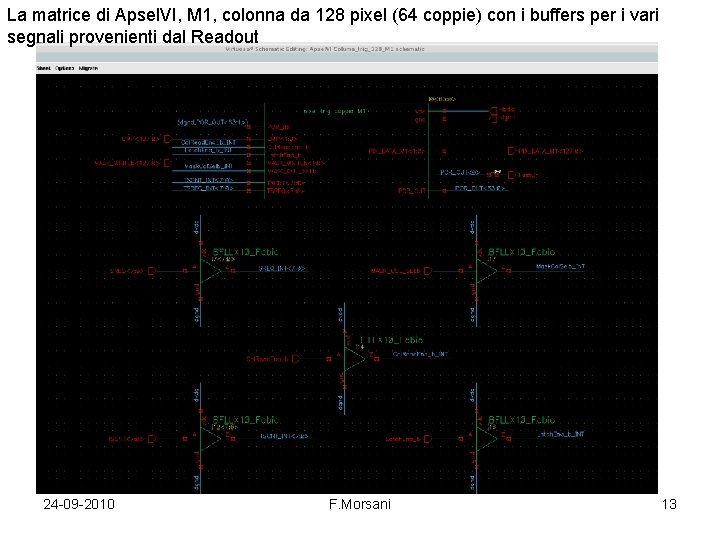

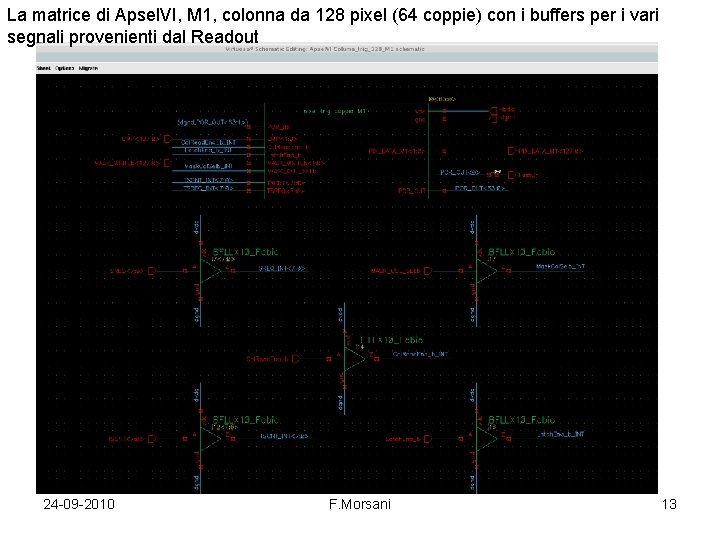

La matrice di Apsel. VI, M 1, colonna da 128 pixel (64 coppie) con i buffers per i vari segnali provenienti dal Readout 24 -09 -2010 F. Morsani 13

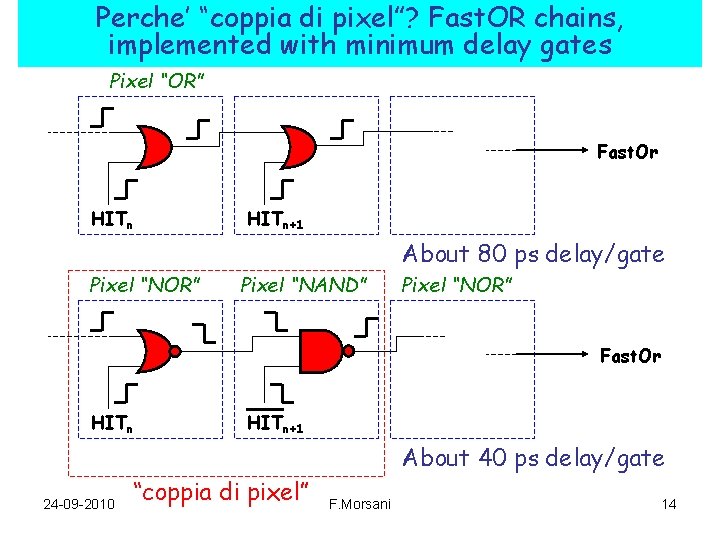

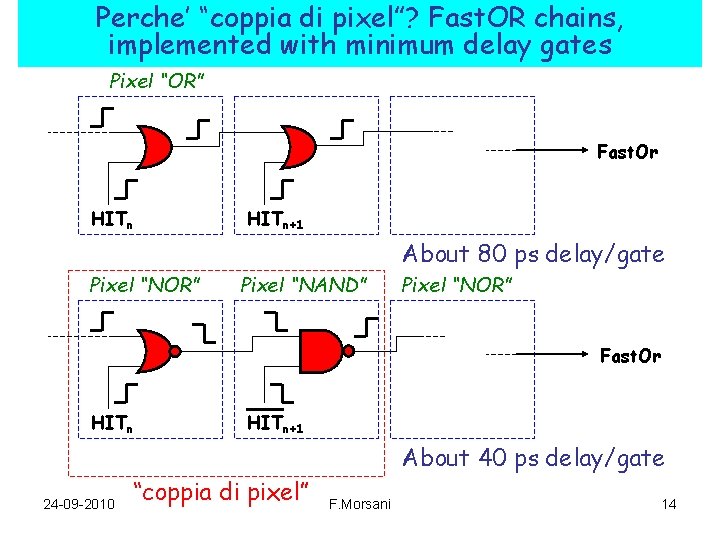

Perche’ “coppia di pixel”? Fast. OR chains, implemented with minimum delay gates Pixel “OR” Fast. Or HITn+1 About 80 ps delay/gate Pixel “NOR” Pixel “NAND” Pixel “NOR” Fast. Or HITn+1 About 40 ps delay/gate 24 -09 -2010 “coppia di pixel” F. Morsani 14

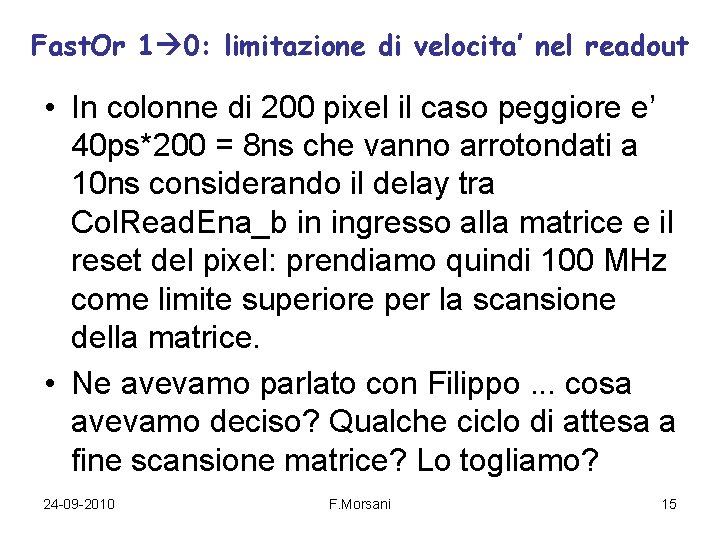

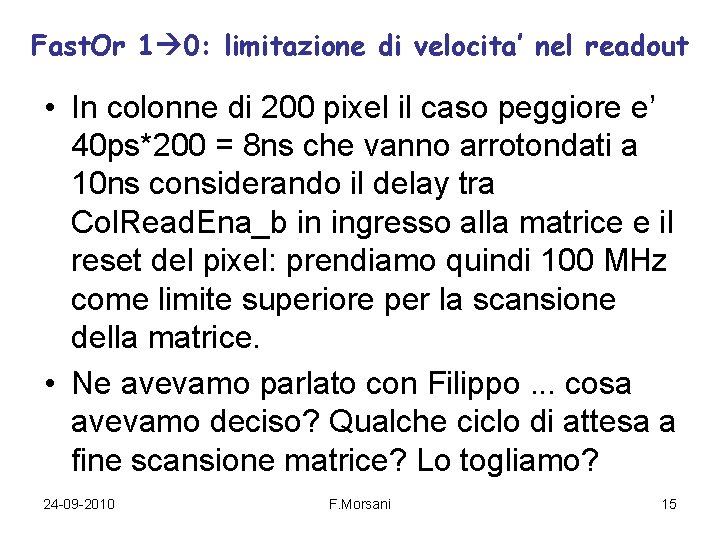

Fast. Or 1 0: limitazione di velocita’ nel readout • In colonne di 200 pixel il caso peggiore e’ 40 ps*200 = 8 ns che vanno arrotondati a 10 ns considerando il delay tra Col. Read. Ena_b in ingresso alla matrice e il reset del pixel: prendiamo quindi 100 MHz come limite superiore per la scansione della matrice. • Ne avevamo parlato con Filippo. . . cosa avevamo deciso? Qualche ciclo di attesa a fine scansione matrice? Lo togliamo? 24 -09 -2010 F. Morsani 15

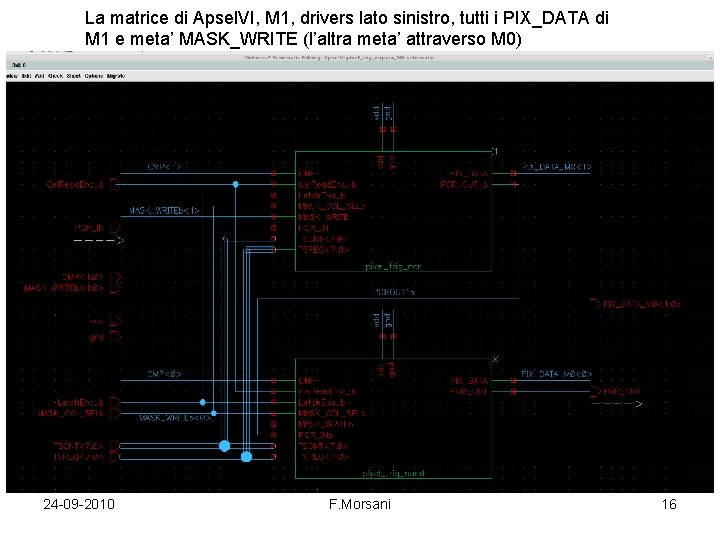

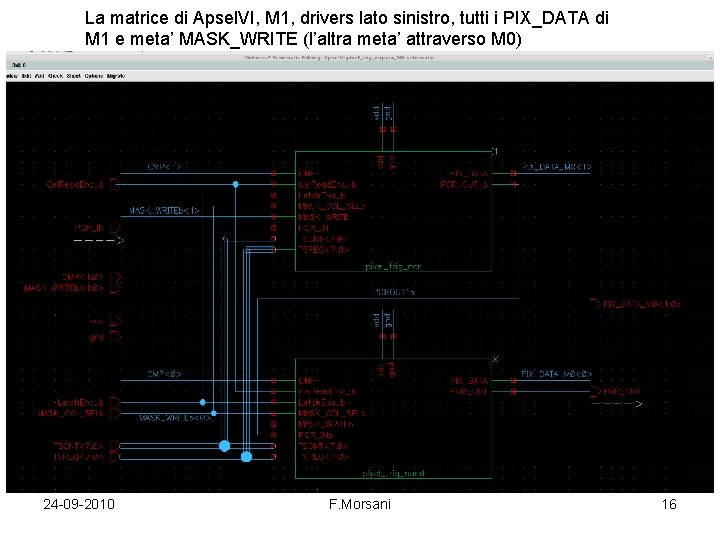

La matrice di Apsel. VI, M 1, drivers lato sinistro, tutti i PIX_DATA di M 1 e meta’ MASK_WRITE (l’altra meta’ attraverso M 0) 24 -09 -2010 F. Morsani 16

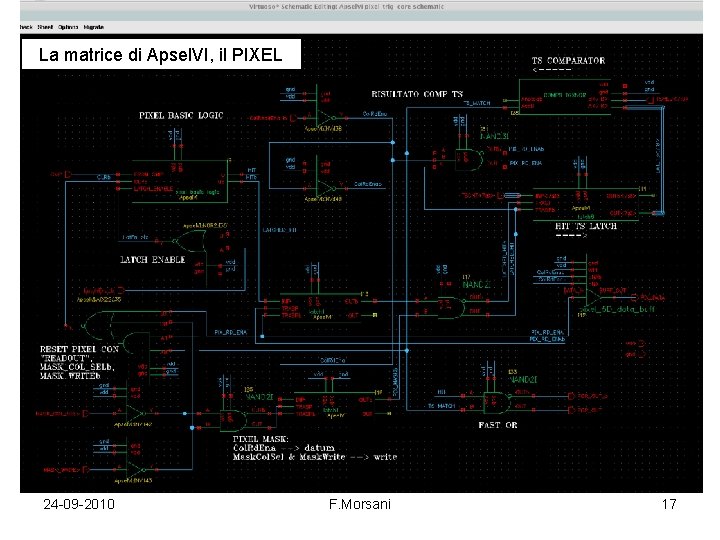

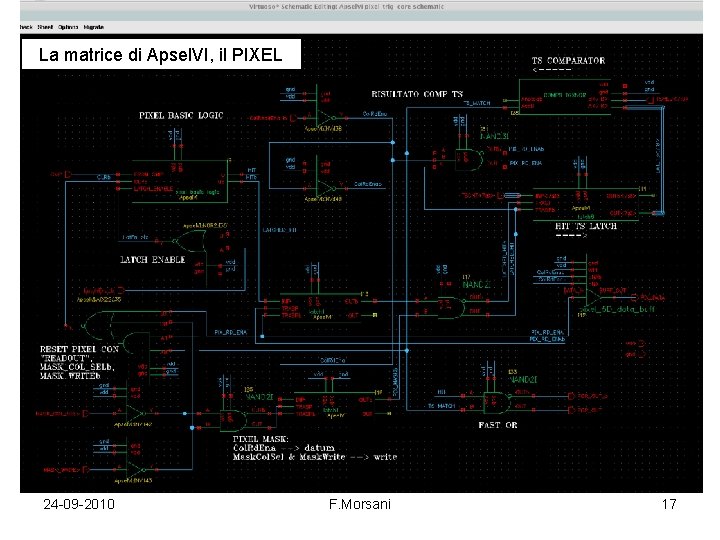

La matrice di Apsel. VI, il PIXEL 24 -09 -2010 F. Morsani 17

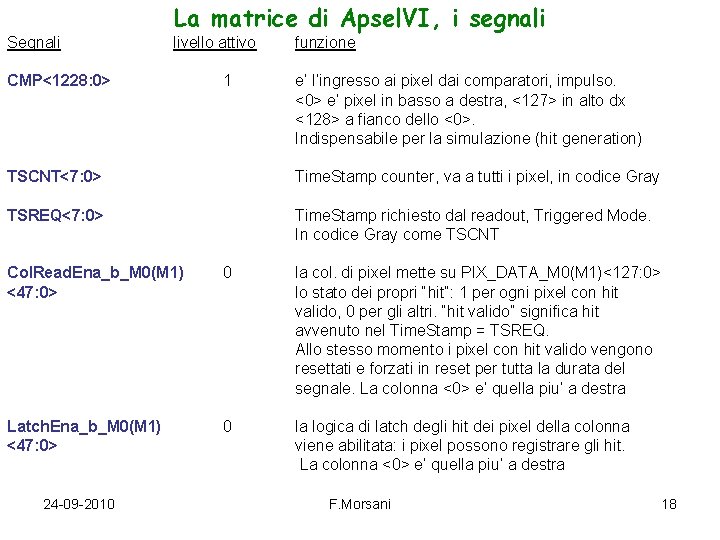

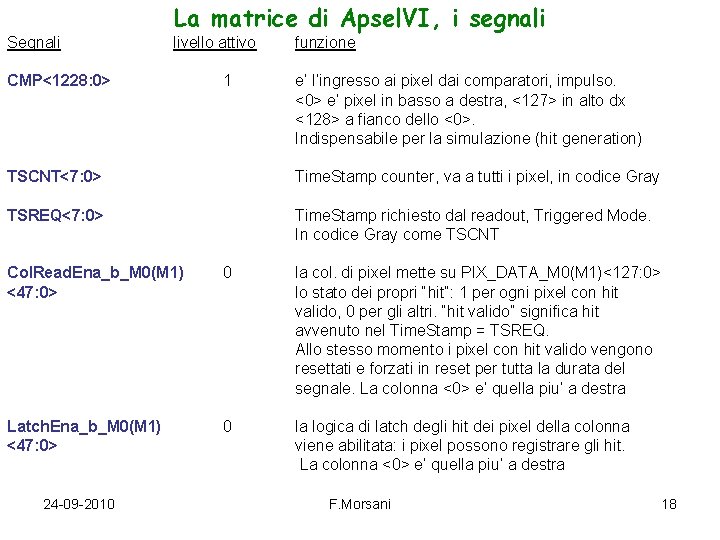

La matrice di Apsel. VI, i segnali Segnali livello attivo CMP<1228: 0> 1 funzione e’ l’ingresso ai pixel dai comparatori, impulso. <0> e’ pixel in basso a destra, <127> in alto dx <128> a fianco dello <0>. Indispensabile per la simulazione (hit generation) TSCNT<7: 0> Time. Stamp counter, va a tutti i pixel, in codice Gray TSREQ<7: 0> Time. Stamp richiesto dal readout, Triggered Mode. In codice Gray come TSCNT Col. Read. Ena_b_M 0(M 1) <47: 0> 0 la col. di pixel mette su PIX_DATA_M 0(M 1)<127: 0> lo stato dei propri “hit”: 1 per ogni pixel con hit valido, 0 per gli altri. “hit valido” significa hit avvenuto nel Time. Stamp = TSREQ. Allo stesso momento i pixel con hit valido vengono resettati e forzati in reset per tutta la durata del segnale. La colonna <0> e’ quella piu’ a destra Latch. Ena_b_M 0(M 1) <47: 0> 0 la logica di latch degli hit dei pixel della colonna viene abilitata: i pixel possono registrare gli hit. La colonna <0> e’ quella piu’ a destra 24 -09 -2010 F. Morsani 18

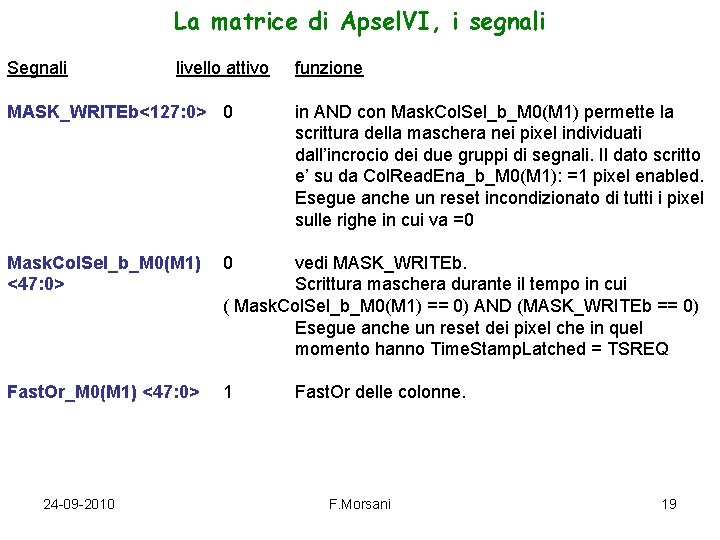

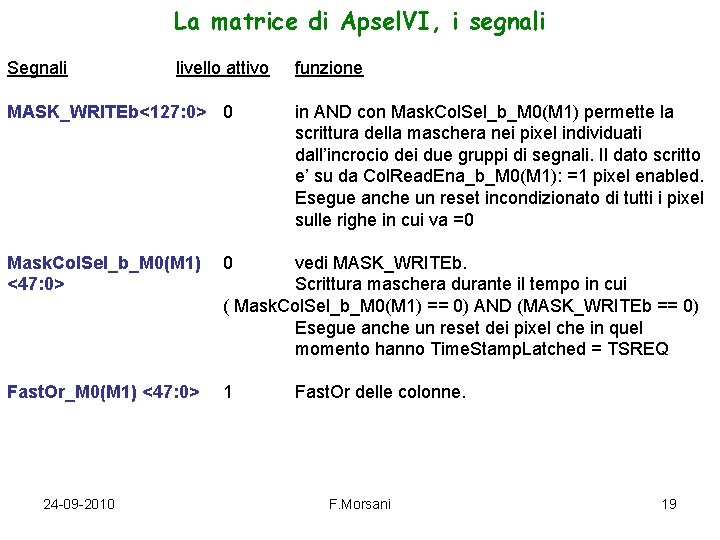

La matrice di Apsel. VI, i segnali Segnali livello attivo MASK_WRITEb<127: 0> 0 Mask. Col. Sel_b_M 0(M 1) <47: 0> 0 Fast. Or_M 0(M 1) <47: 0> 1 24 -09 -2010 funzione in AND con Mask. Col. Sel_b_M 0(M 1) permette la scrittura della maschera nei pixel individuati dall’incrocio dei due gruppi di segnali. Il dato scritto e’ su da Col. Read. Ena_b_M 0(M 1): =1 pixel enabled. Esegue anche un reset incondizionato di tutti i pixel sulle righe in cui va =0 vedi MASK_WRITEb. Scrittura maschera durante il tempo in cui ( Mask. Col. Sel_b_M 0(M 1) == 0) AND (MASK_WRITEb == 0) Esegue anche un reset dei pixel che in quel momento hanno Time. Stamp. Latched = TSREQ Fast. Or delle colonne. F. Morsani 19

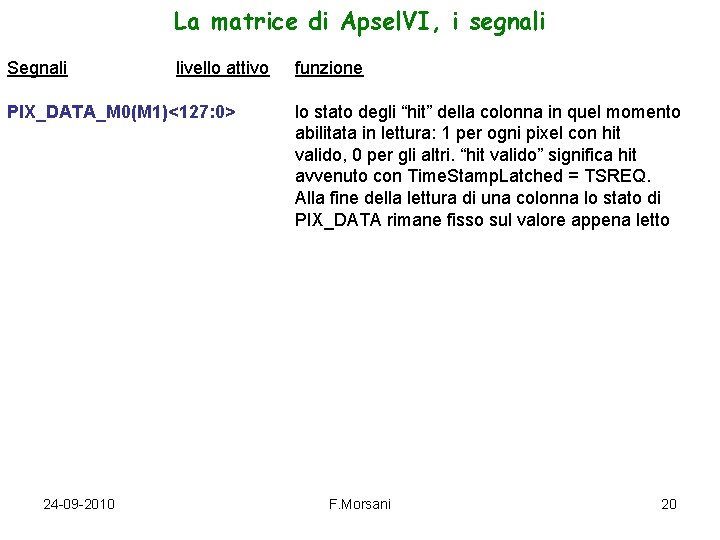

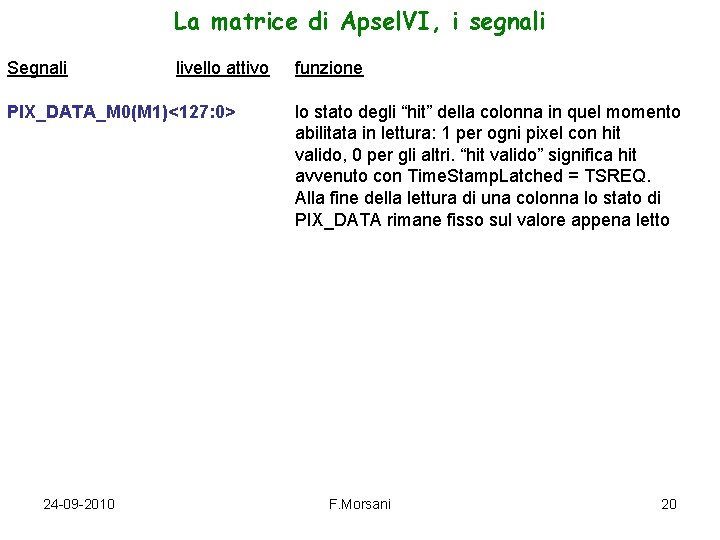

La matrice di Apsel. VI, i segnali Segnali livello attivo PIX_DATA_M 0(M 1)<127: 0> 24 -09 -2010 funzione lo stato degli “hit” della colonna in quel momento abilitata in lettura: 1 per ogni pixel con hit valido, 0 per gli altri. “hit valido” significa hit avvenuto con Time. Stamp. Latched = TSREQ. Alla fine della lettura di una colonna lo stato di PIX_DATA rimane fisso sul valore appena letto F. Morsani 20

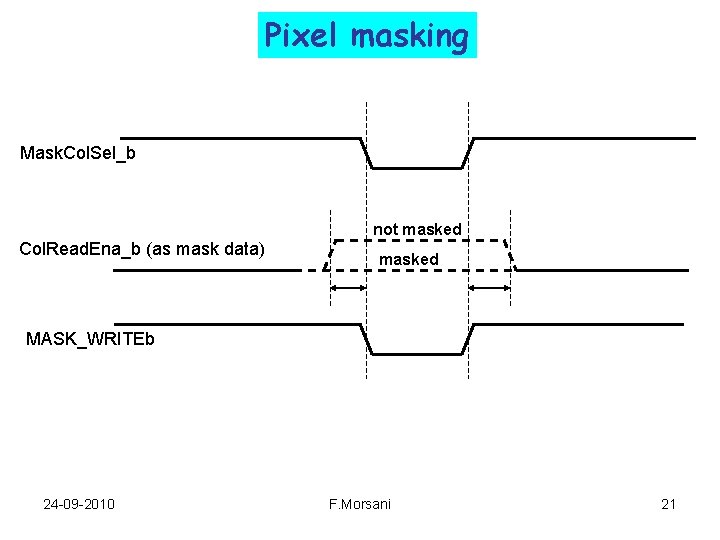

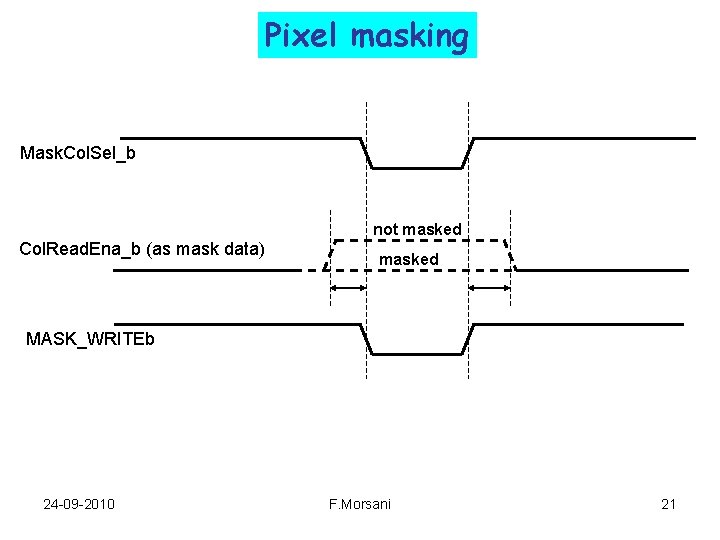

Pixel masking Mask. Col. Sel_b not masked Col. Read. Ena_b (as mask data) masked MASK_WRITEb 24 -09 -2010 F. Morsani 21

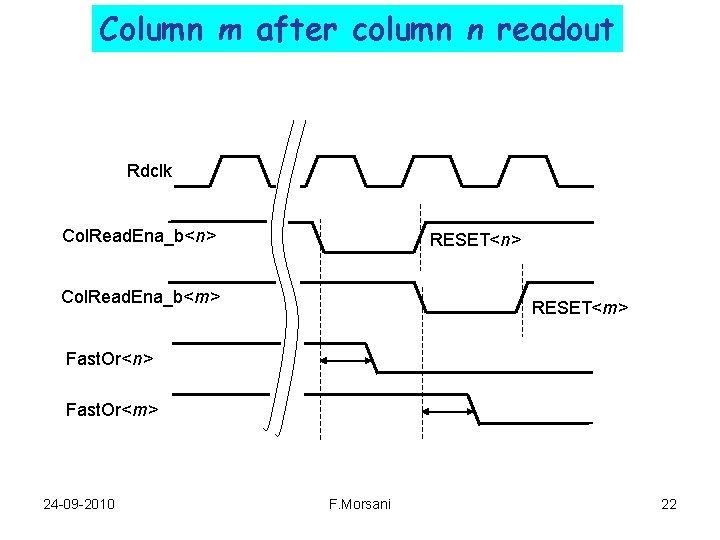

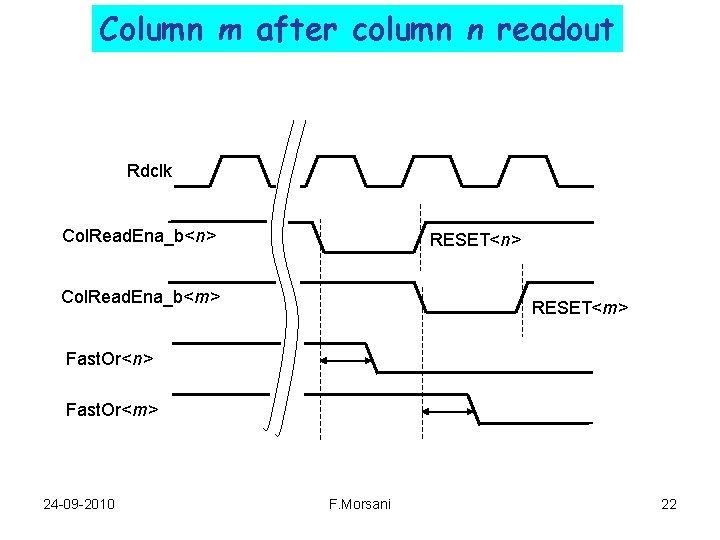

Column m after column n readout Rdclk Col. Read. Ena_b<n> RESET<n> Col. Read. Ena_b<m> RESET<m> Fast. Or<n> Fast. Or<m> 24 -09 -2010 F. Morsani 22

Da fare per la matrice • Schemi: – quasi finiti Apsel. VI, a seguire quelli di Superpix 1; tutto da validare con simulazione – sarebbe bello simulare tutto a switch-level (Ultrasim); chiesto a CMP nessuna risposta = non sanno nulla; chiedero’ a Cadence Italy sperando nell’aiuto di Oddone • Layout: – da finire i vari blocchi, DRC+LVS – produzione cella per P&R (come si fa senza salti mortali? ) 24 -09 -2010 F. Morsani 23