L Transistortransistor Logic ECL Emitter Coupled Logic MOS

- Slides: 57

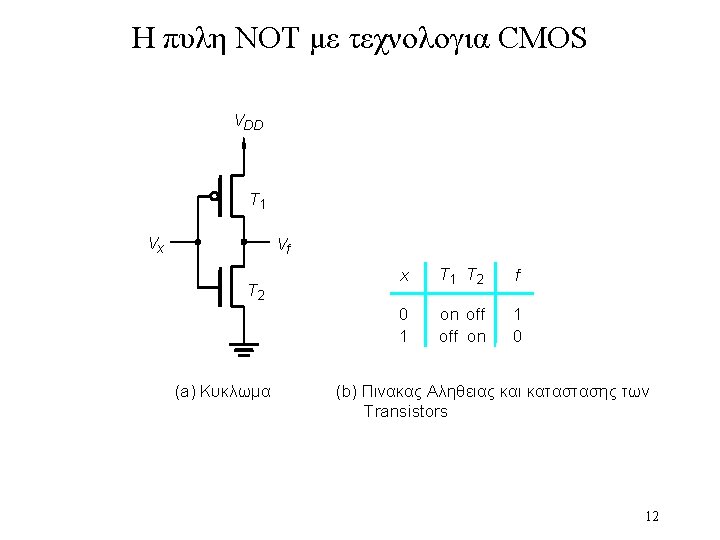

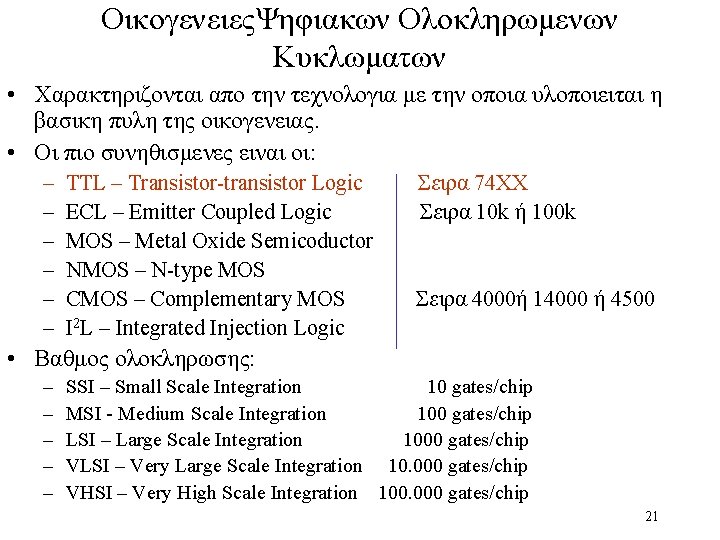

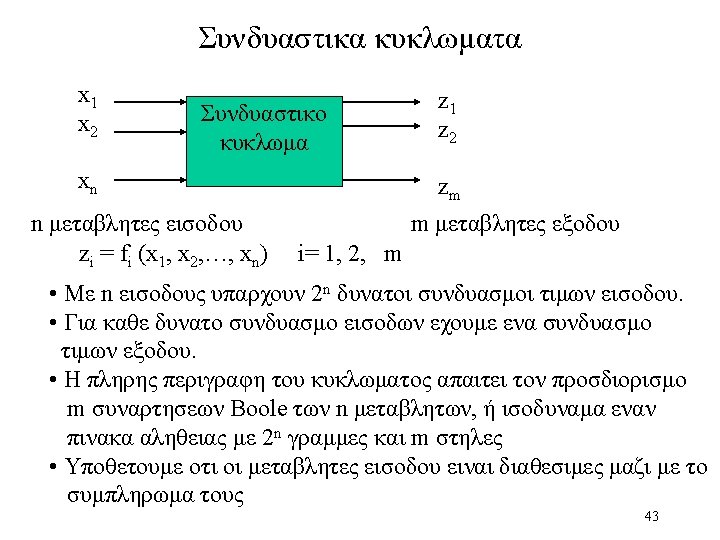

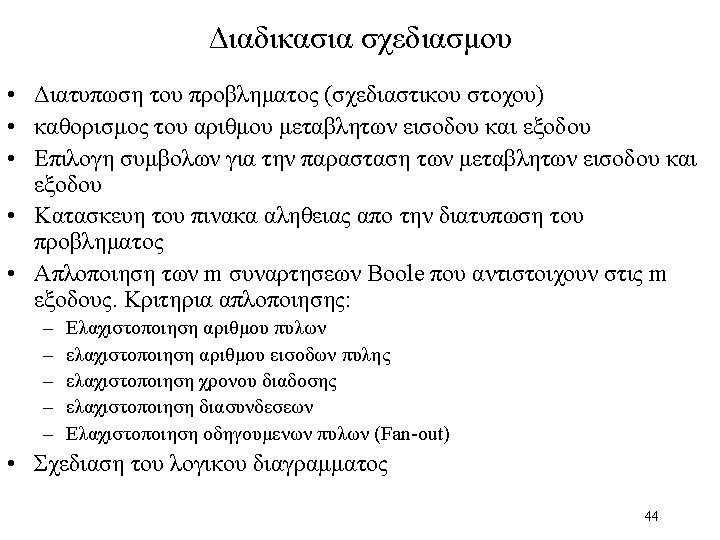

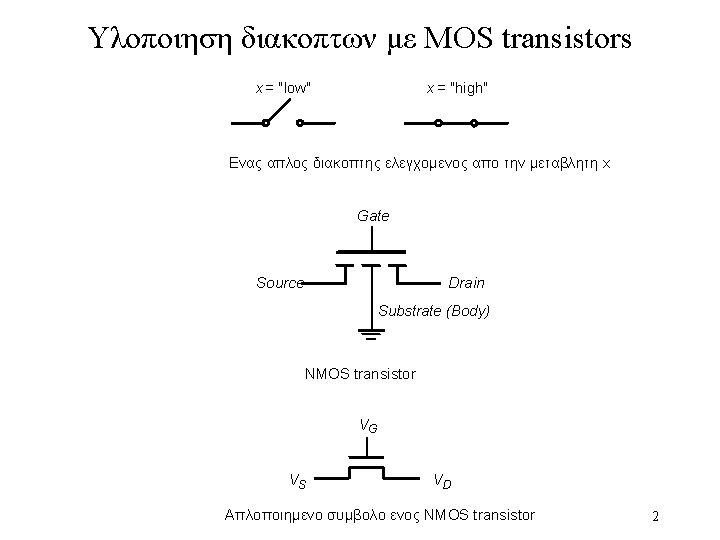

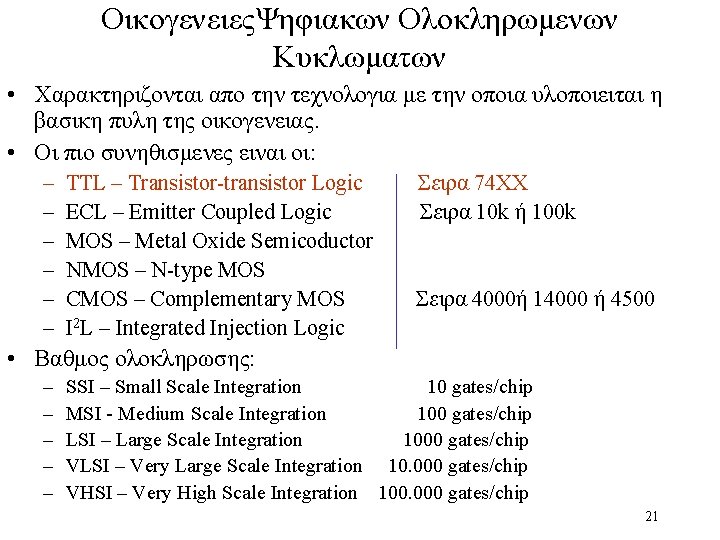

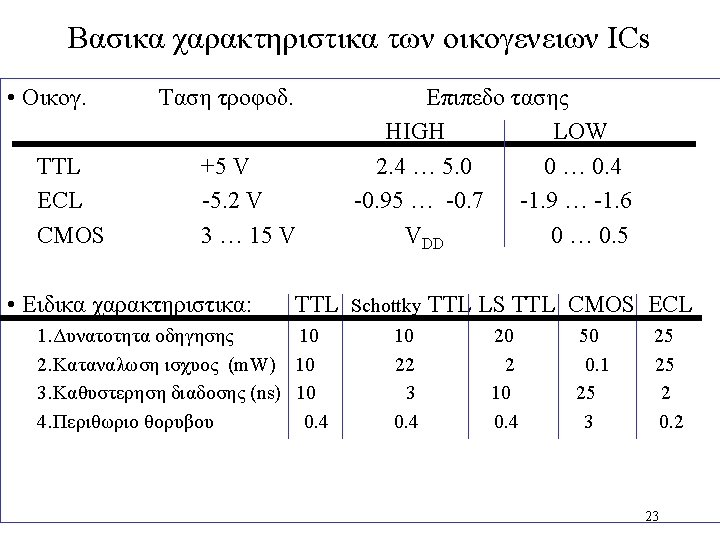

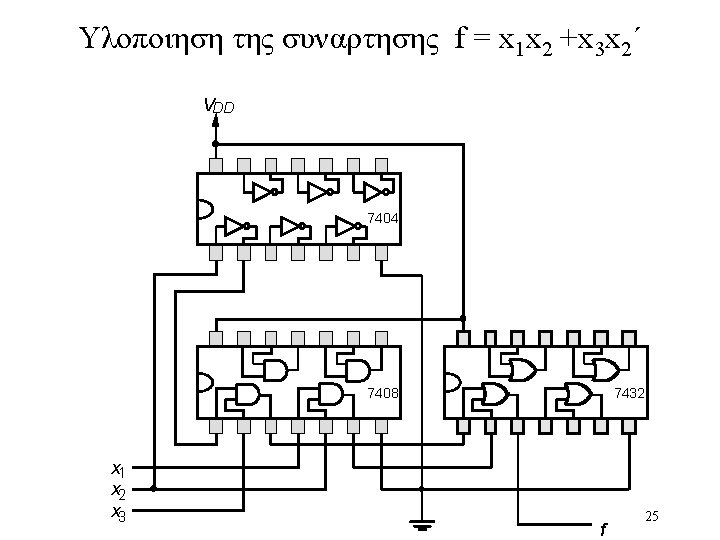

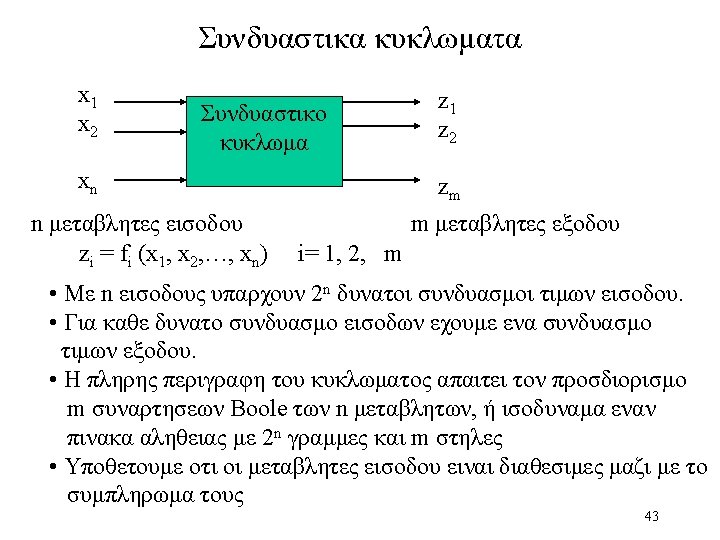

ΟικογενειεςΨηφιακων Ολοκληρωμενων Κυκλωματων • Χαρακτηριζονται απο την τεχνολογια με την οποια υλοποιειται η βασικη πυλη της οικογενειας. • Οι πιο συνηθισμενες ειναι οι: – – – ΤΤL – Transistor-transistor Logic ECL – Emitter Coupled Logic MOS – Metal Oxide Semicoductor NMOS – N-type MOS CMOS – Complementary MOS I 2 L – Integrated Injection Logic Σειρα 74ΧΧ Σειρα 10 k ή 100 k Σειρα 4000ή 14000 ή 4500 • Βαθμος ολοκληρωσης: – – – SSI – Small Scale Integration 10 gates/chip MSI - Medium Scale Integration 100 gates/chip LSI – Large Scale Integration 1000 gates/chip VLSI – Very Large Scale Integration 10. 000 gates/chip VHSI – Very High Scale Integration 100. 000 gates/chip 21

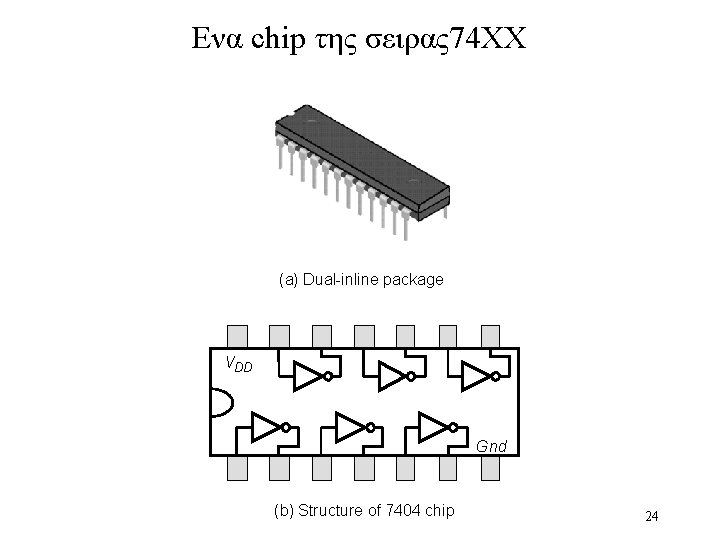

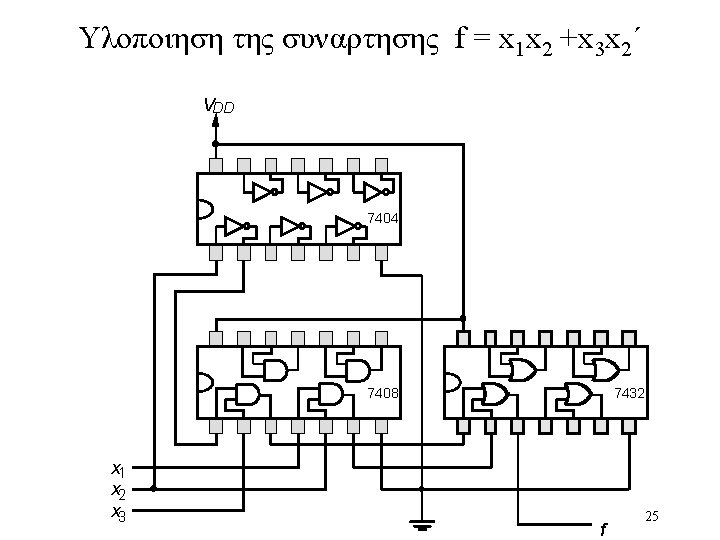

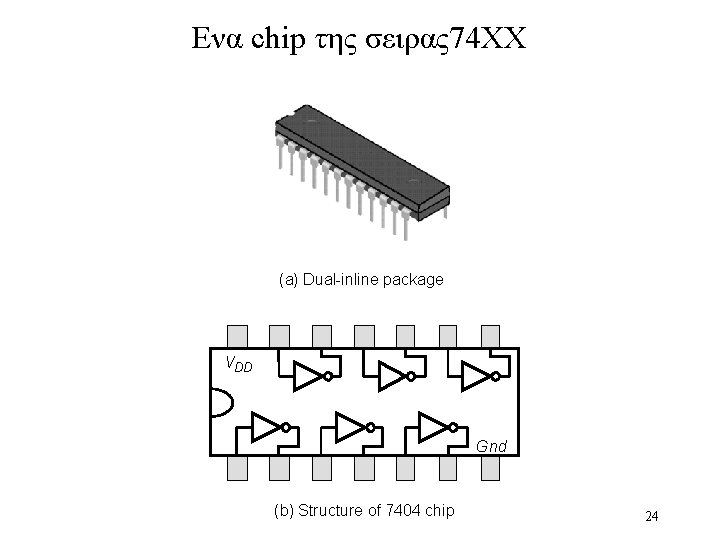

Ενα chip της σειρας74ΧΧ (a) Dual-inline package VDD Gnd (b) Structure of 7404 chip 24

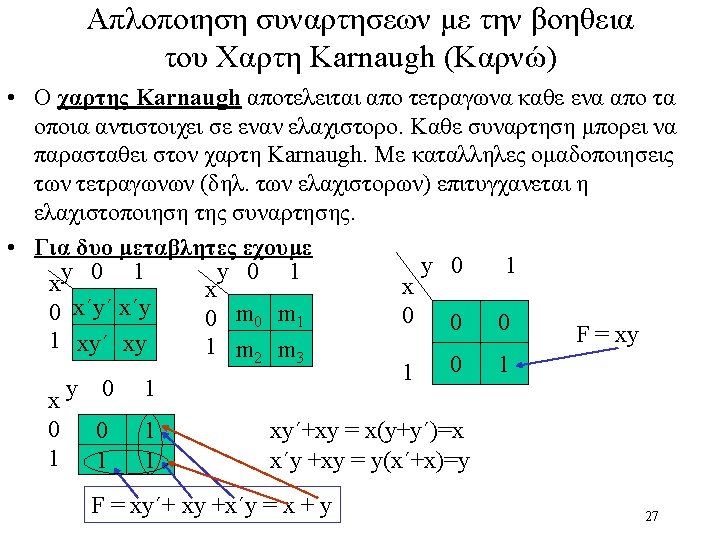

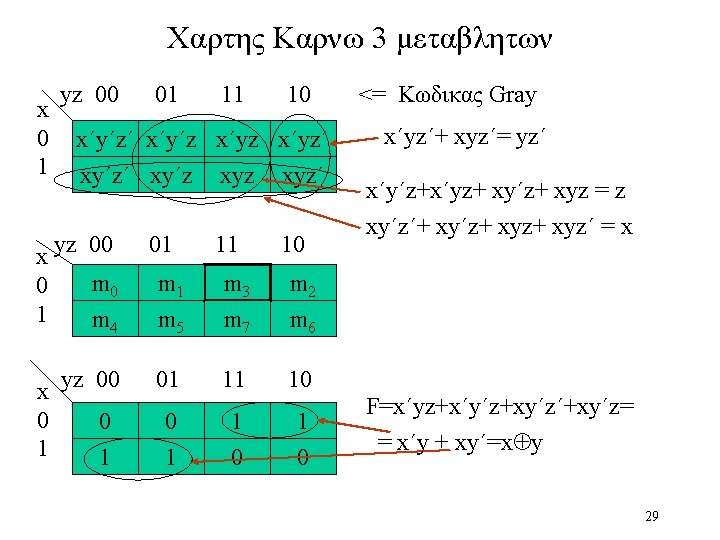

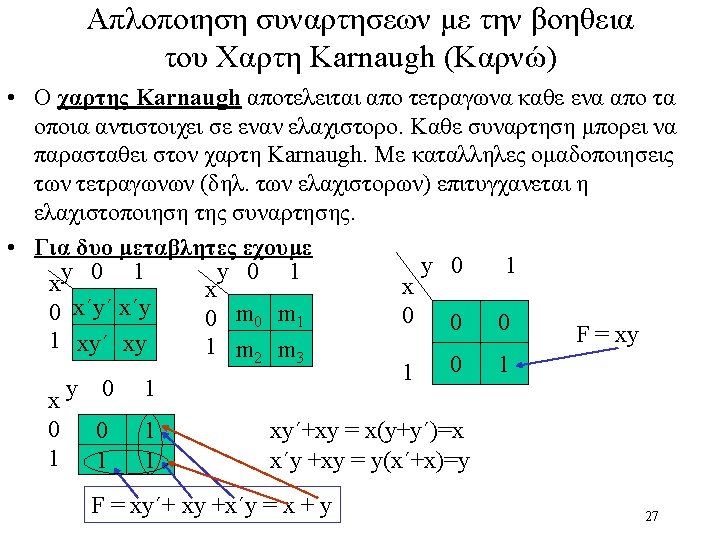

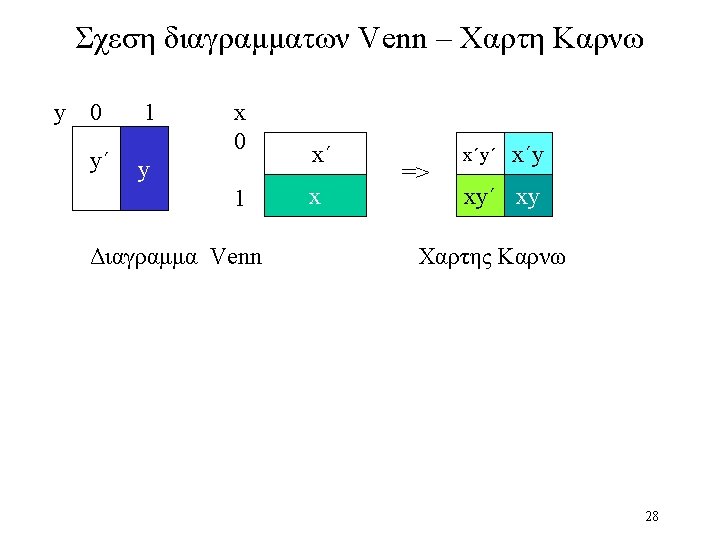

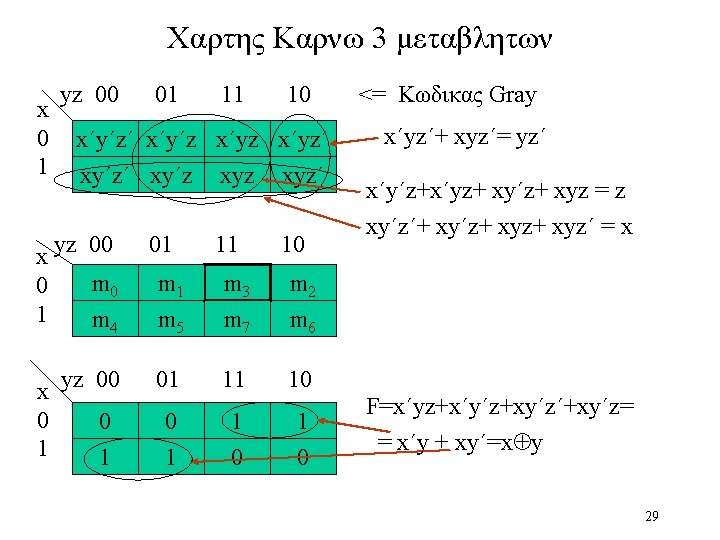

Χαρτης Καρνω 3 μεταβλητων x 0 1 yz 00 01 11 10 x´y´z´ x´y´z x´yz´ xy´z x yz 00 m 0 0 1 m 4 x yz 00 0 0 1 1 01 xyz´ 11 10 m 1 m 5 m 3 m 7 m 2 m 6 01 11 10 0 1 1 0 <= Κωδικας Gray x´yz´+ xyz´= yz´ x´y´z+x´yz+ xy´z+ xyz = z xy´z´+ xy´z+ xyz´ = x F=x´yz+x´y´z+xy´z´+xy´z= = x´y + xy´=x y 29

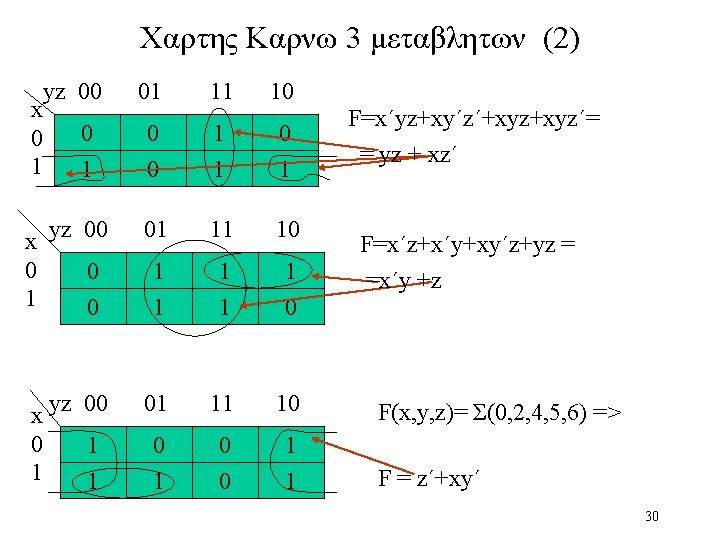

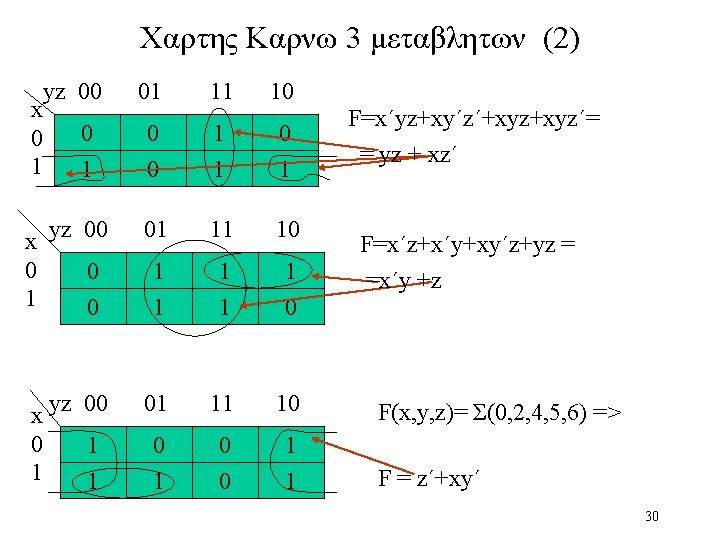

Χαρτης Καρνω 3 μεταβλητων (2) yz 00 x 0 0 1 1 01 11 10 0 1 1 x yz 00 0 0 1 0 01 11 10 1 1 1 0 x yz 00 0 1 1 1 01 11 10 0 1 1 F=x´yz+xy´z´+xyz´= = yz + xz´ F=x´z+x´y+xy´z+yz = =x´y +z F(x, y, z)= Σ(0, 2, 4, 5, 6) => F = z´+xy´ 30

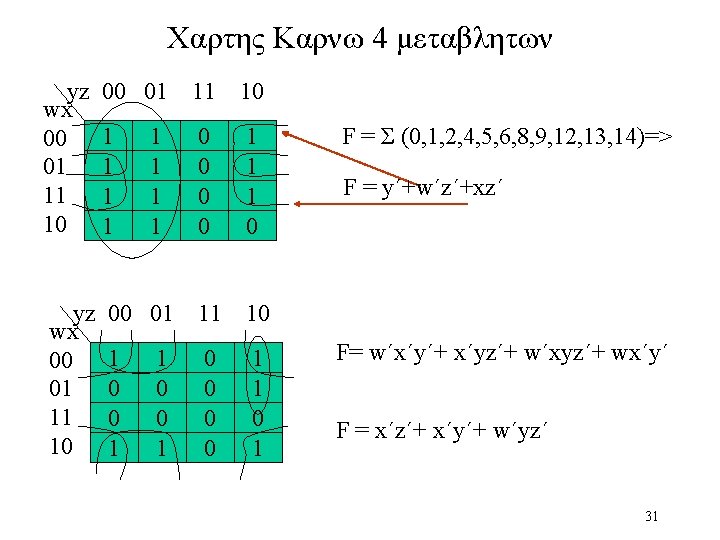

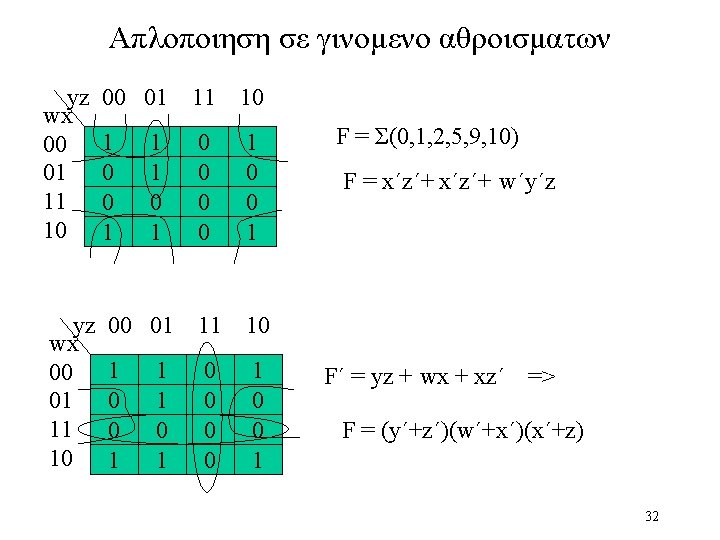

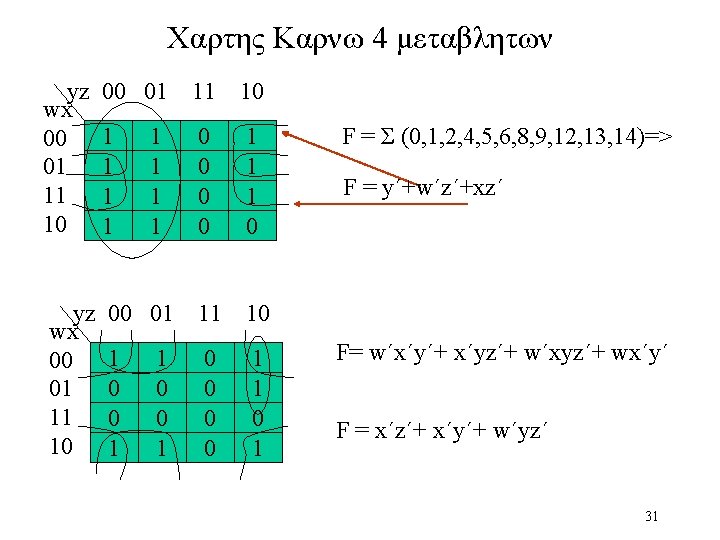

Χαρτης Καρνω 4 μεταβλητων yz wx 00 01 11 10 1 1 0 0 1 1 1 0 yz wx 00 01 11 10 1 0 0 0 0 1 1 1 1 0 0 1 F = Σ (0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)=> F = y´+w´z´+xz´ F= w´x´y´+ x´yz´+ w´xyz´+ wx´y´ F = x´z´+ x´y´+ w´yz´ 31

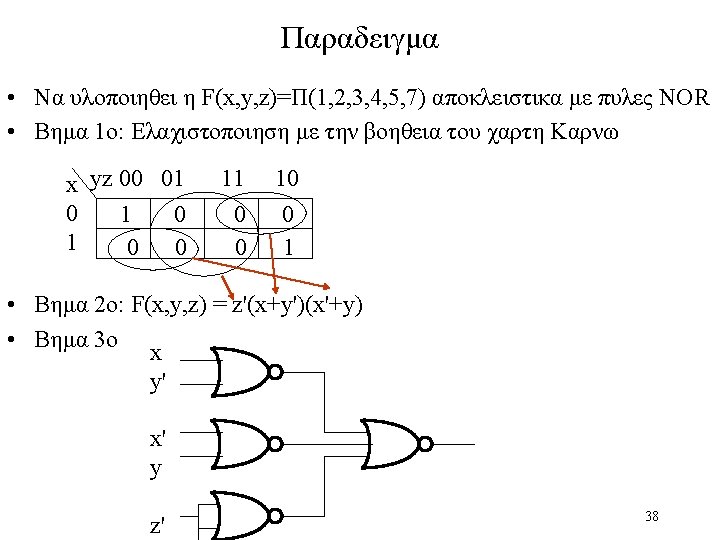

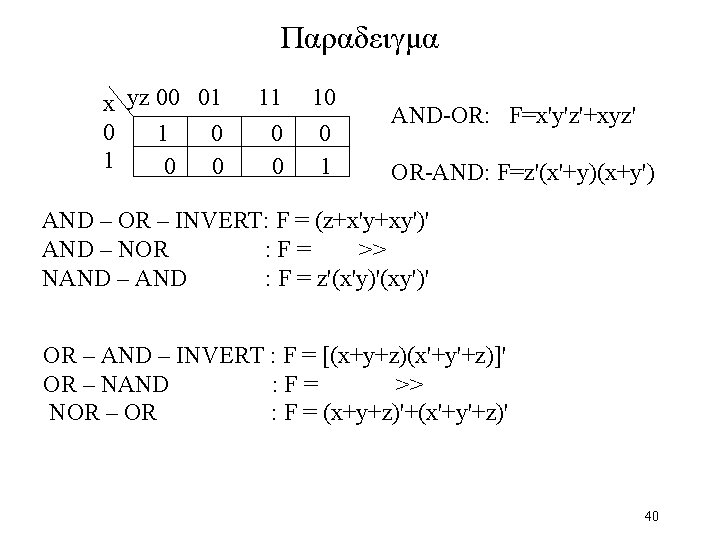

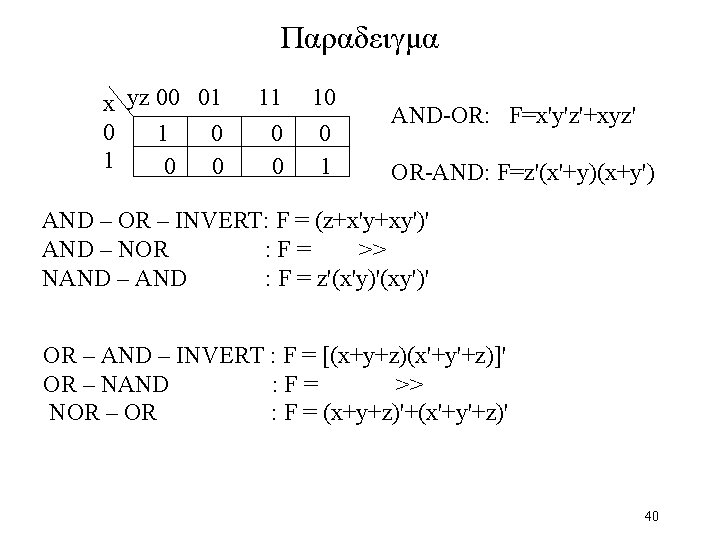

Παραδειγμα x yz 00 01 0 1 0 0 10 0 1 AND-OR: F=x'y'z'+xyz' OR-AND: F=z'(x'+y)(x+y') AND – OR – INVERT: F = (z+x'y+xy')' AND – NOR : F= >> NAND – AND : F = z'(x'y)'(xy')' OR – AND – INVERT : F = [(x+y+z)(x'+y'+z)]' OR – NAND : F= >> NOR – OR : F = (x+y+z)'+(x'+y'+z)' 40

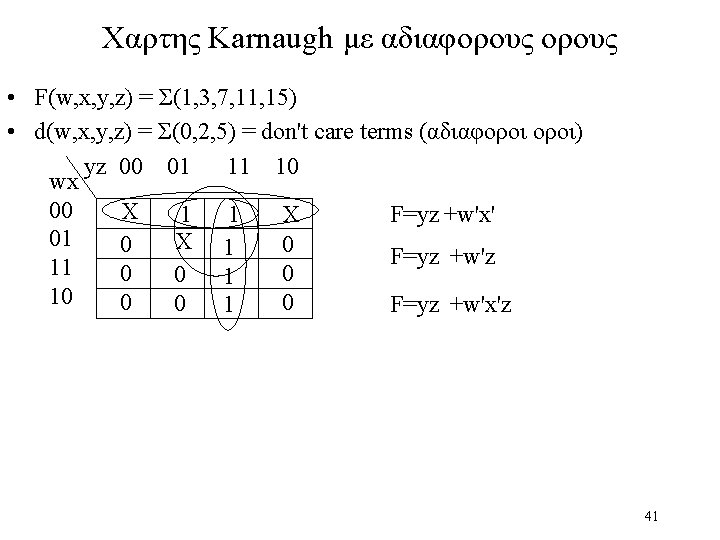

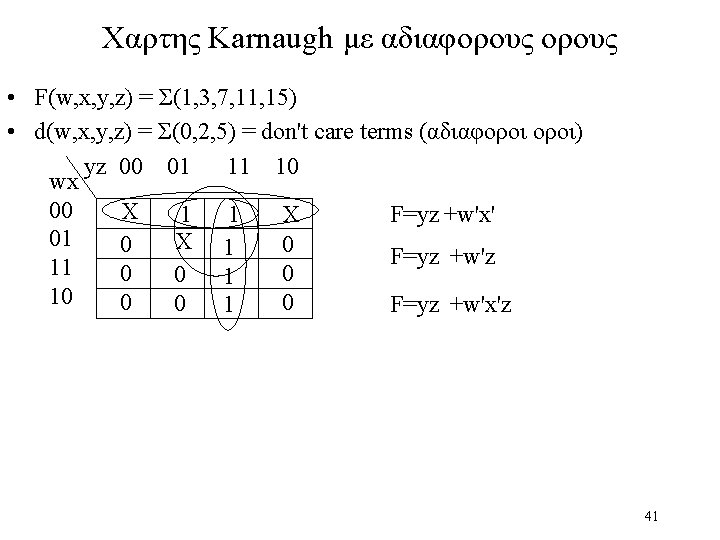

Χαρτης Karnaugh με αδιαφορους • F(w, x, y, z) = Σ(1, 3, 7, 11, 15) • d(w, x, y, z) = Σ(0, 2, 5) = don't care terms (αδιαφοροι) yz 00 01 11 10 wx 00 X 1 1 X F=yz +w'x' 01 X 1 0 0 F=yz +w'z 11 0 0 0 1 10 0 F=yz +w'x'z 1 41

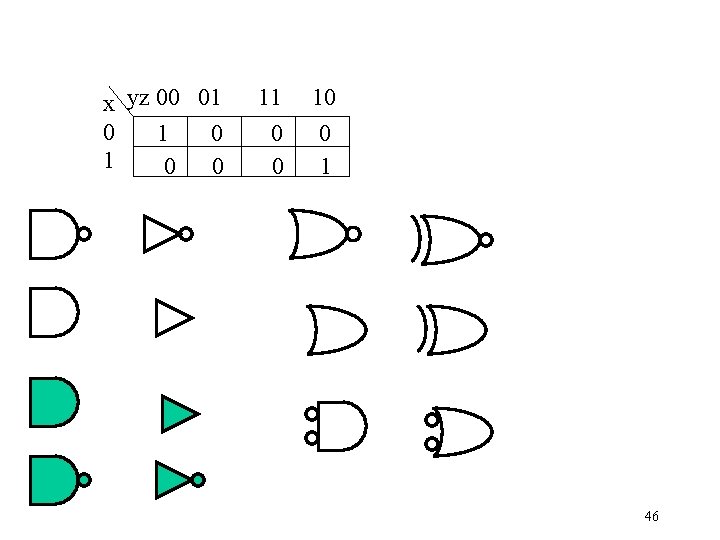

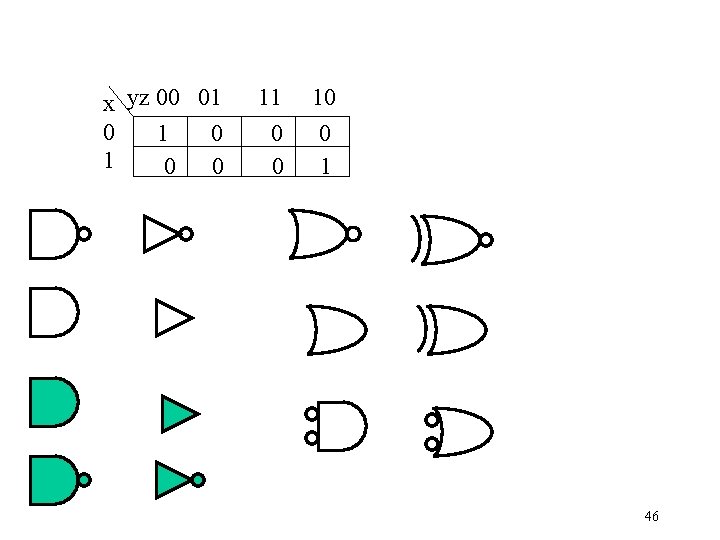

x yz 00 01 0 1 0 0 10 0 1 46

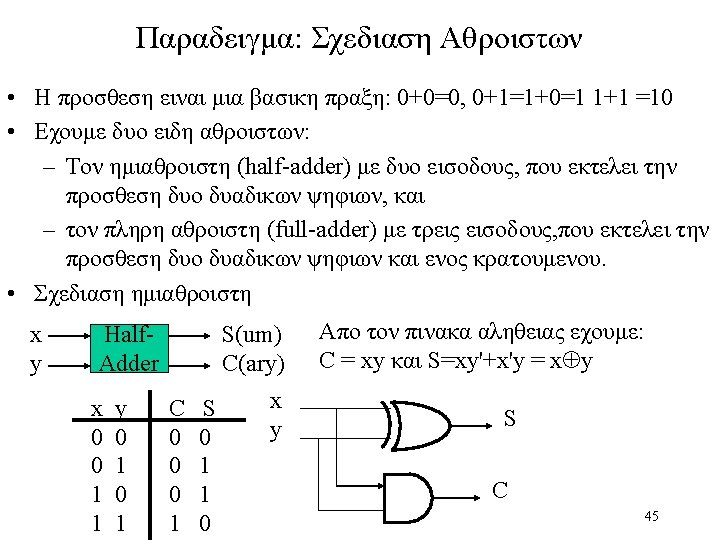

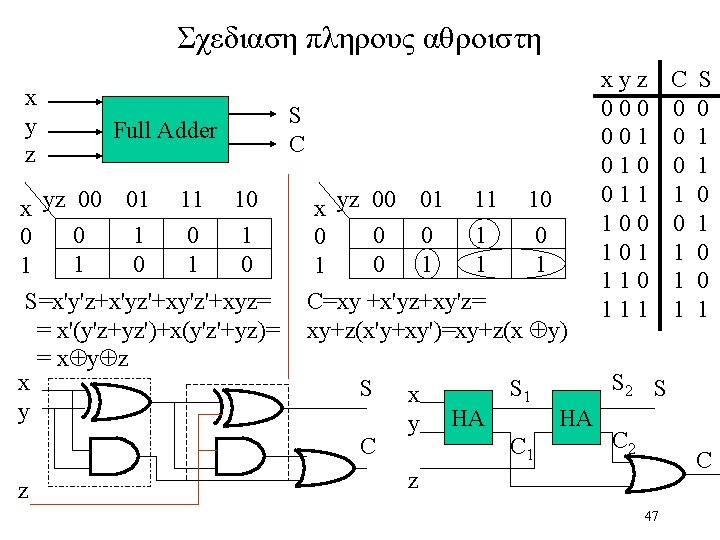

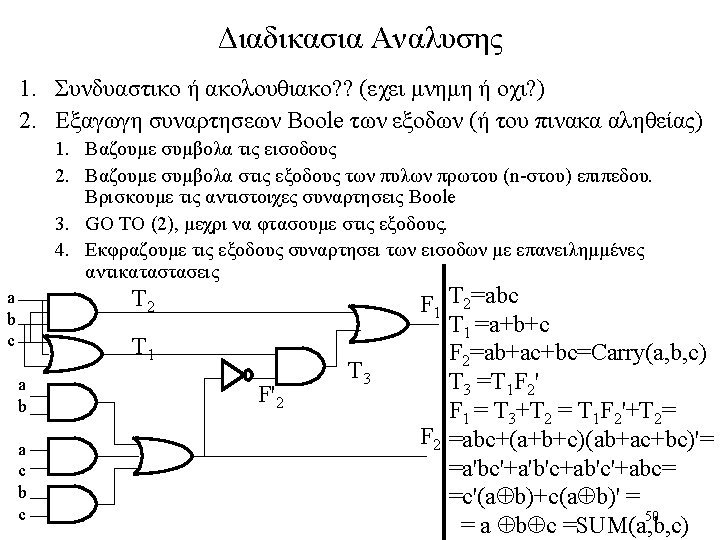

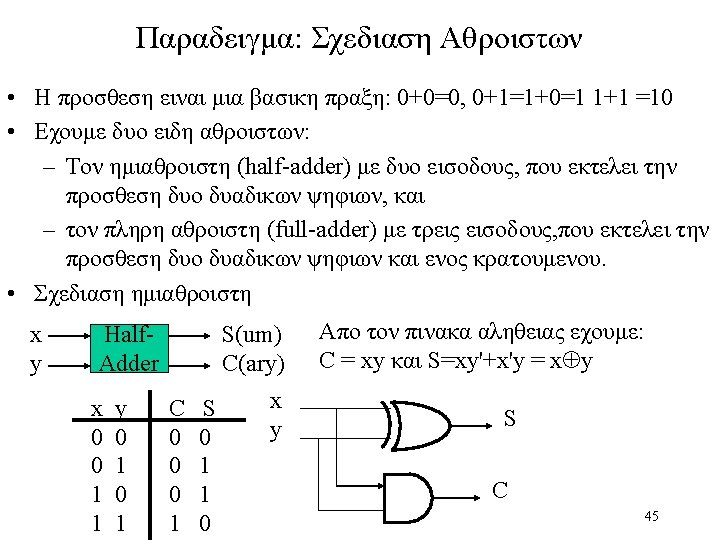

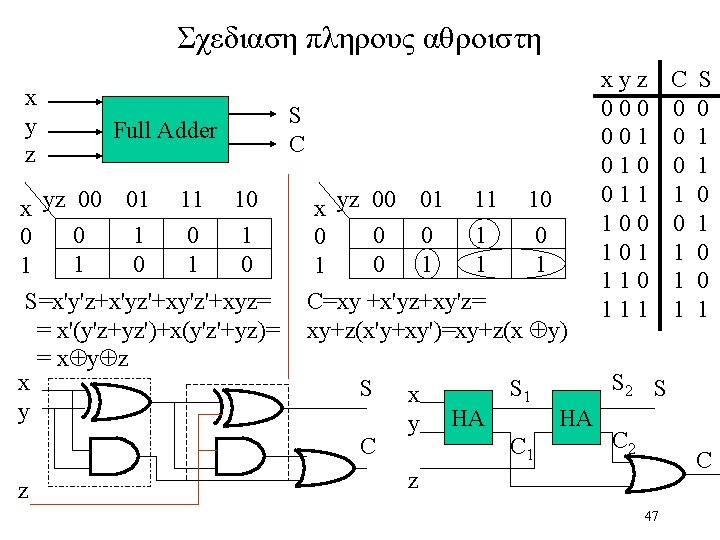

Σχεδιαση πληρους αθροιστη x y z Full Adder x yz 00 01 11 10 0 1 0 1 0 1 S=x'y'z+x'yz'+xy'z'+xyz= = x'(y'z+yz')+x(y'z'+yz)= = x y z x y S C x yz 00 01 11 10 0 0 1 1 1 1 C=xy +x'yz+xy'z= xy+z(x'y+xy')=xy+z(x y) S C z x y HA S 1 C 1 xyz C S 000 0 0 001 0 1 010 0 1 011 1 0 100 0 1 101 1 0 110 1 0 111 1 1 S 2 S HA C 2 C z 47

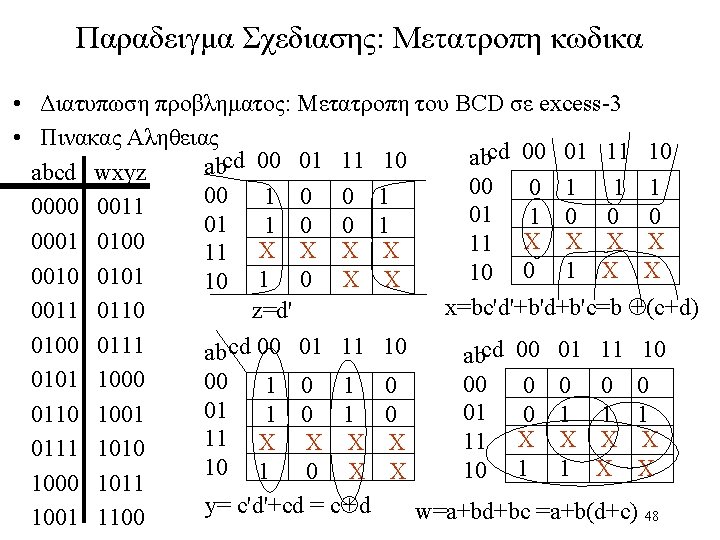

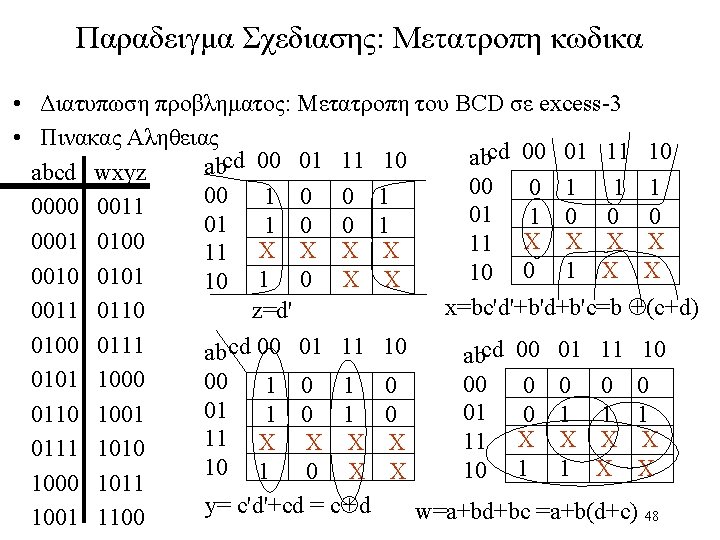

Παραδειγμα Σχεδιασης: Μετατροπη κωδικα • Διατυπωση προβληματος: Μετατροπη του BCD σε excess-3 • Πινακας Αληθειας cd 00 01 11 10 ab abcd wxyz 00 0 1 1 1 00 1 0000 0011 01 1 0 0 1 0001 0100 11 X X X X 10 0 1 X X 0010 0101 10 1 0 X X x=bc'd'+b'd+b'c=b (c+d) z=d' 0011 0110 0100 0111 ab cd 00 01 11 10 abcd 00 01 11 10 0101 1000 00 00 1 0 0 0 01 01 1 0 0 1 1 1 0110 1001 11 X X X X 0111 1010 10 1 1 X X 0 X X 1000 1011 y= c'd'+cd = c d w=a+bd+bc =a+b(d+c) 48 1001 1100

51

52

53

54

55

56

57