L 23 Arithmetic Logic Units Arithmetic Logic Units

- Slides: 25

L 23 – Arithmetic Logic Units

Arithmetic Logic Units (ALU) o Modern ALU design ALU is heart of datapath o Ref: text Unit 15 o 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

Design of ALUs and Data Paths o o Objective: Design a General Purpose Data Path such as the datapath found in a typical computer. A Data Path Contains: n n o Registers – general purpose, special purpose Execution Units capable of multiple functions Have completed design of a dual ported register set. Objective: Design ALU and integrate with registers. 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 3

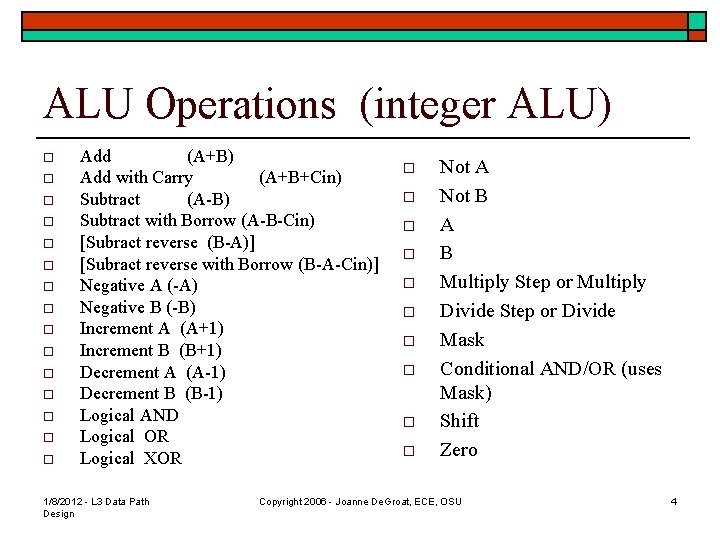

ALU Operations (integer ALU) o o o o Add (A+B) Add with Carry (A+B+Cin) Subtract (A-B) Subtract with Borrow (A-B-Cin) [Subract reverse (B-A)] [Subract reverse with Borrow (B-A-Cin)] Negative A (-A) Negative B (-B) Increment A (A+1) Increment B (B+1) Decrement A (A-1) Decrement B (B-1) Logical AND Logical OR Logical XOR 1/8/2012 - L 3 Data Path Design o o o o o Not A Not B A B Multiply Step or Multiply Divide Step or Divide Mask Conditional AND/OR (uses Mask) Shift Zero Copyright 2006 - Joanne De. Groat, ECE, OSU 4

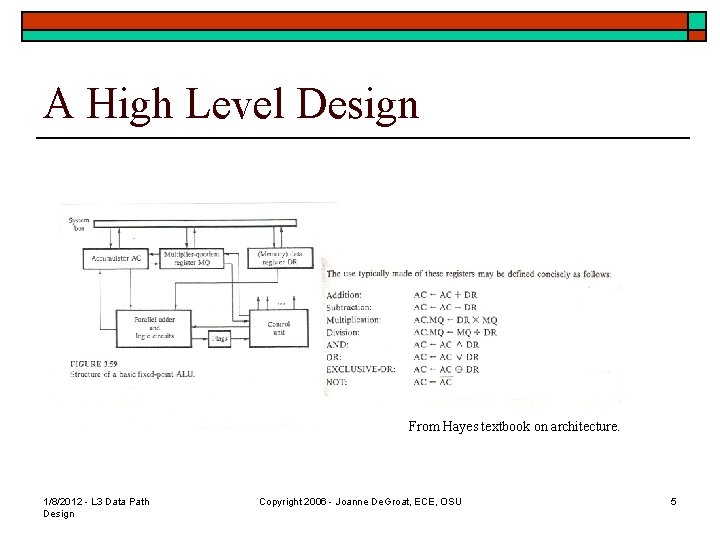

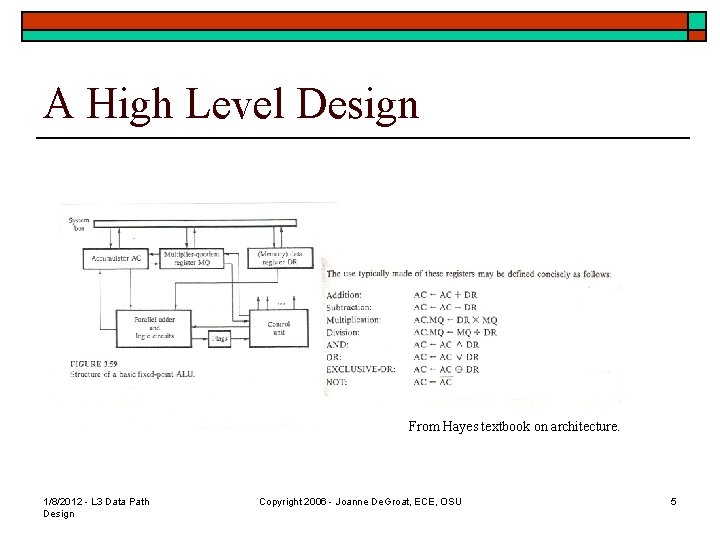

A High Level Design From Hayes textbook on architecture. 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 5

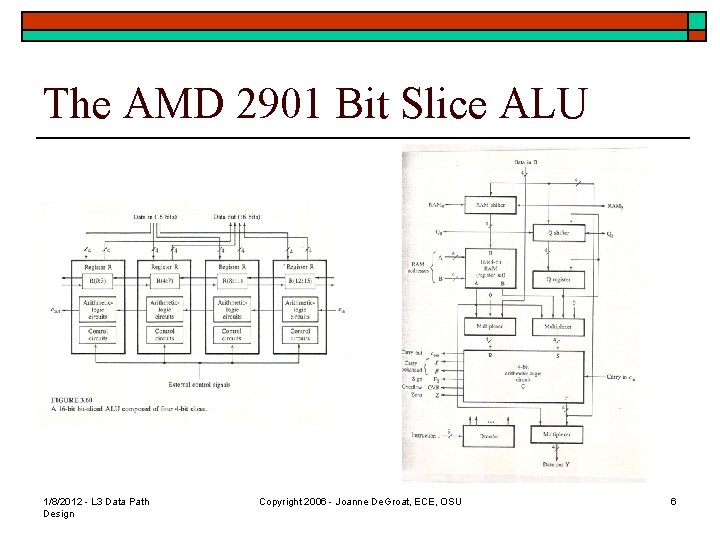

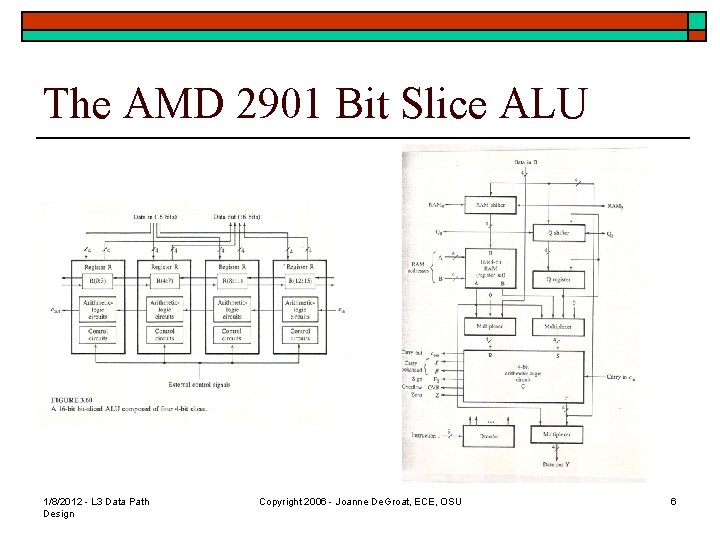

The AMD 2901 Bit Slice ALU 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 6

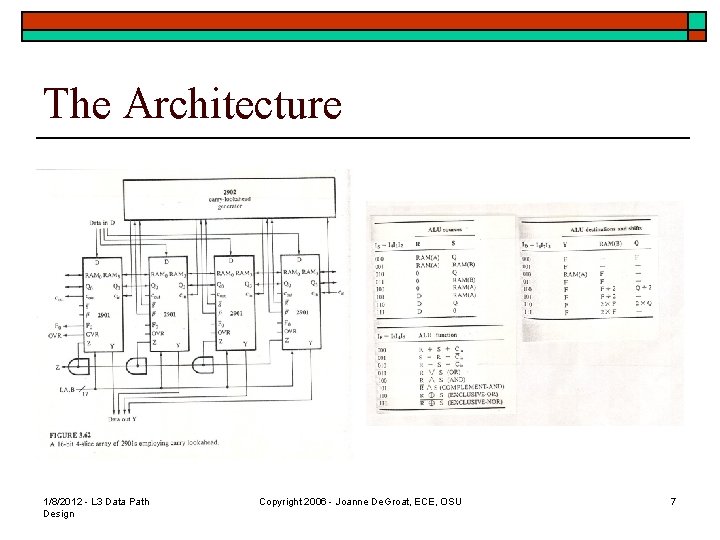

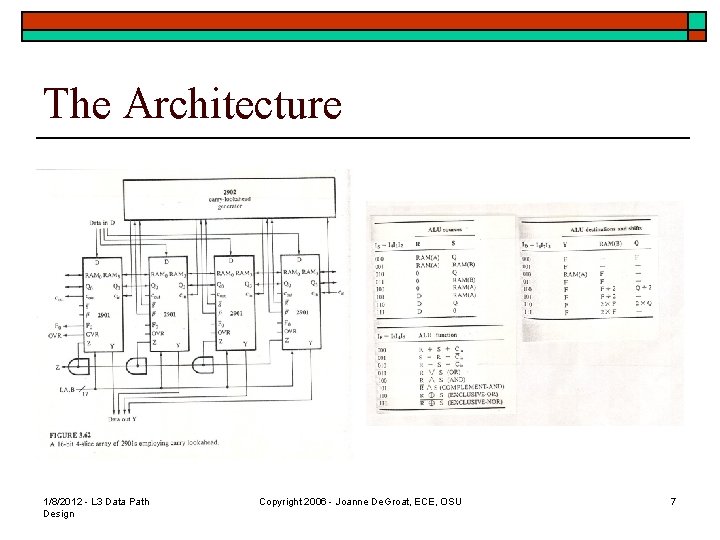

The Architecture 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 7

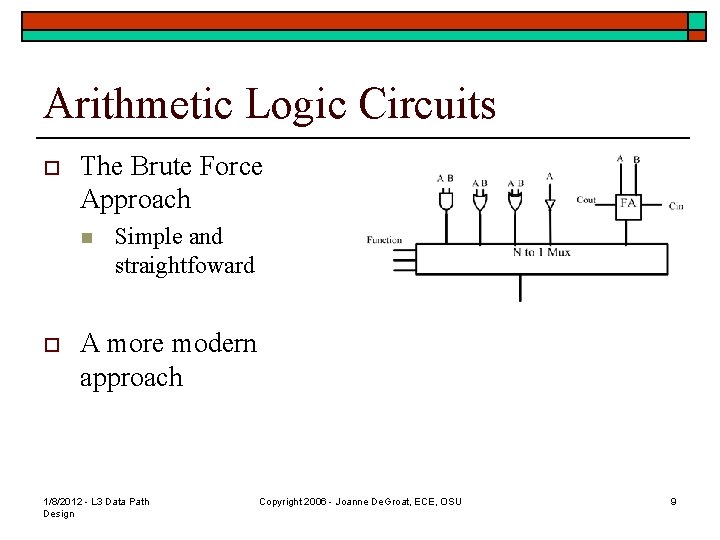

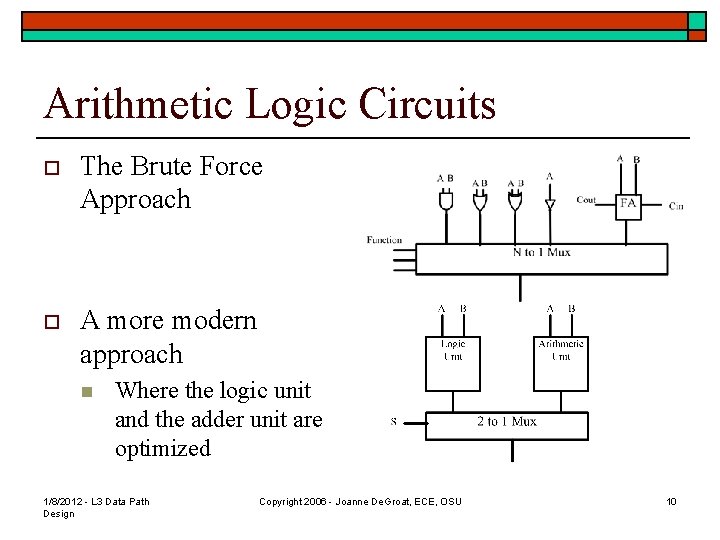

Arithmetic Logic Circuits o The Brute Force Approach o A more modern approach 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 8

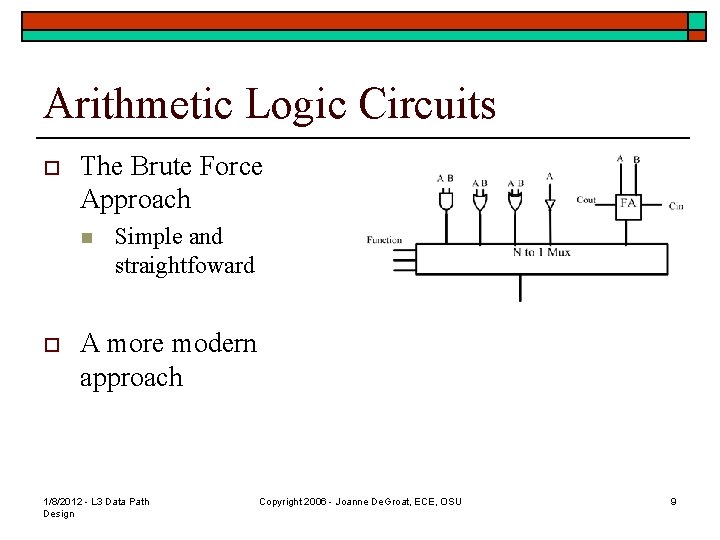

Arithmetic Logic Circuits o The Brute Force Approach n o Simple and straightfoward A more modern approach 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 9

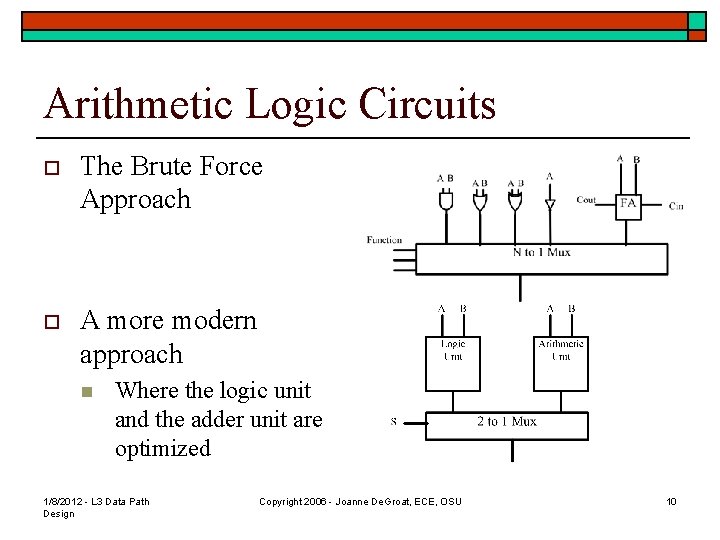

Arithmetic Logic Circuits o The Brute Force Approach o A more modern approach n Where the logic unit and the adder unit are optimized 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 10

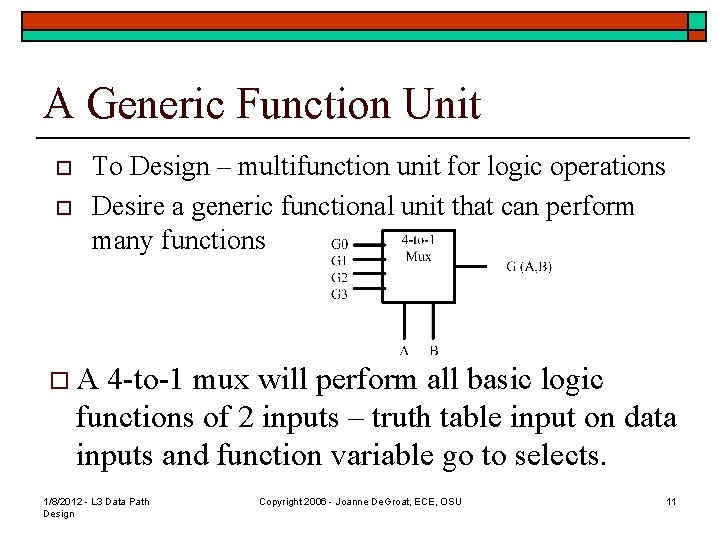

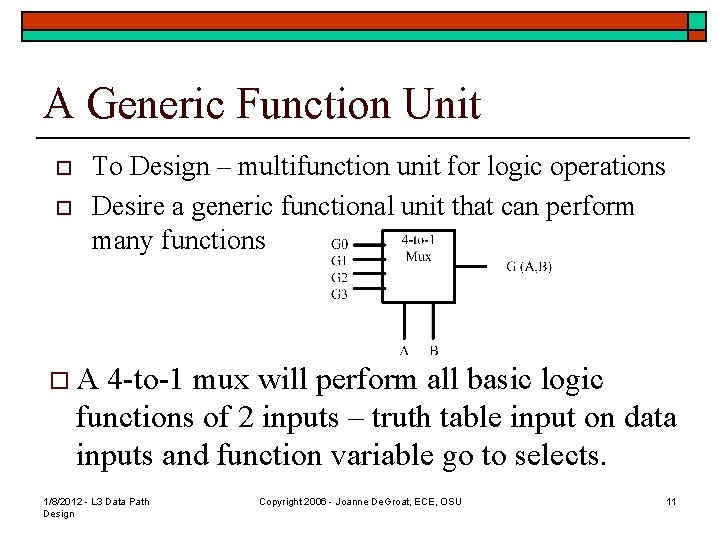

A Generic Function Unit o o To Design – multifunction unit for logic operations Desire a generic functional unit that can perform many functions o. A 4 -to-1 mux will perform all basic logic functions of 2 inputs – truth table input on data inputs and function variable go to selects. 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 11

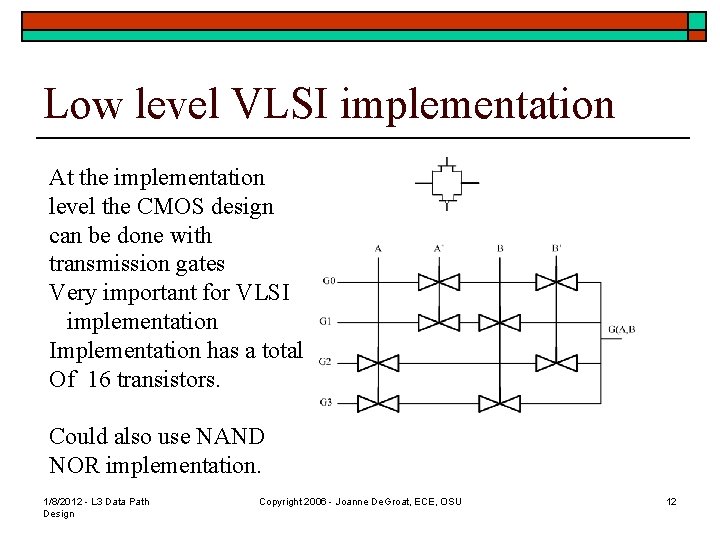

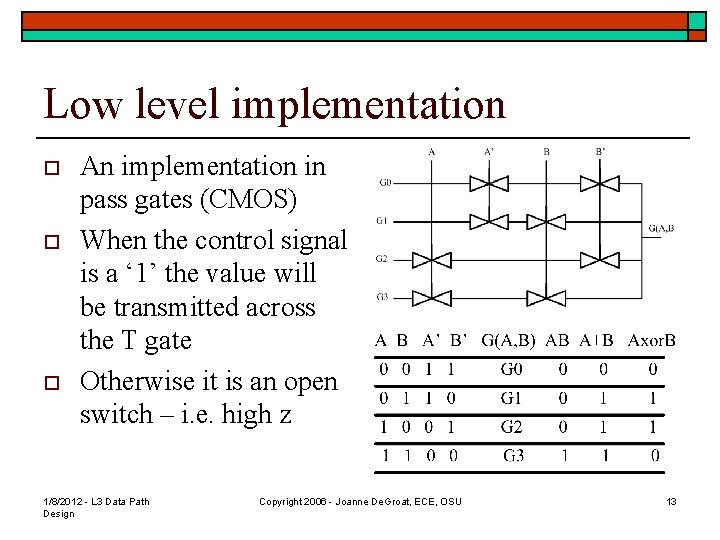

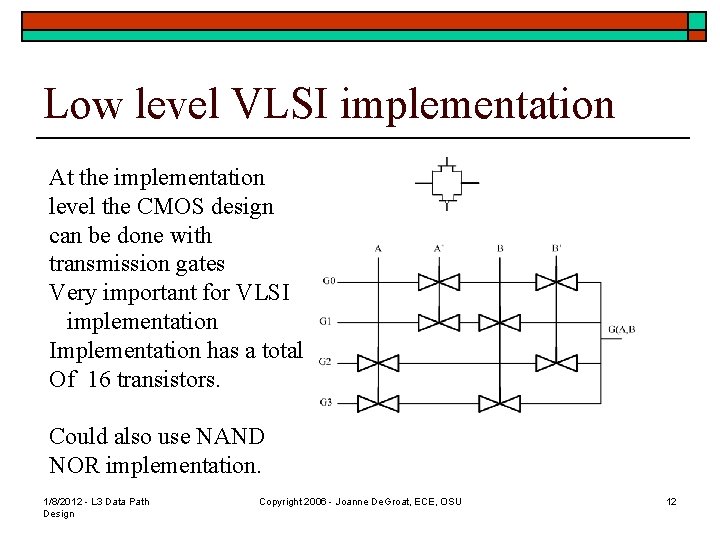

Low level VLSI implementation At the implementation level the CMOS design can be done with transmission gates Very important for VLSI implementation Implementation has a total Of 16 transistors. Could also use NAND NOR implementation. 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 12

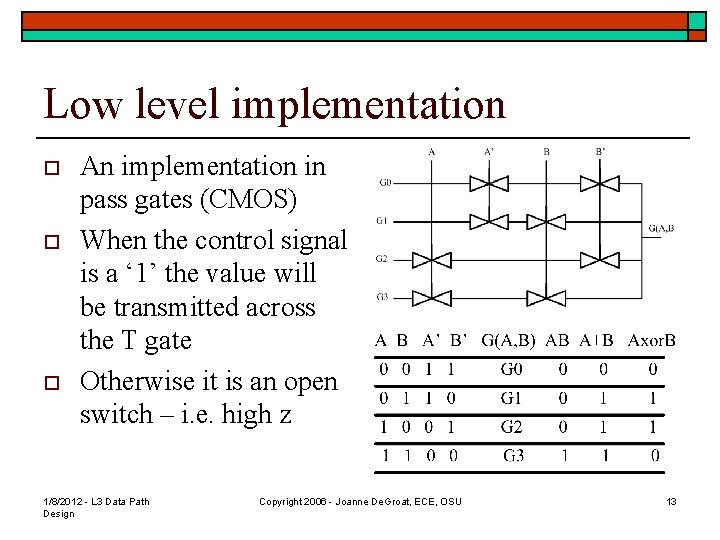

Low level implementation o o o An implementation in pass gates (CMOS) When the control signal is a ‘ 1’ the value will be transmitted across the T gate Otherwise it is an open switch – i. e. high z 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 13

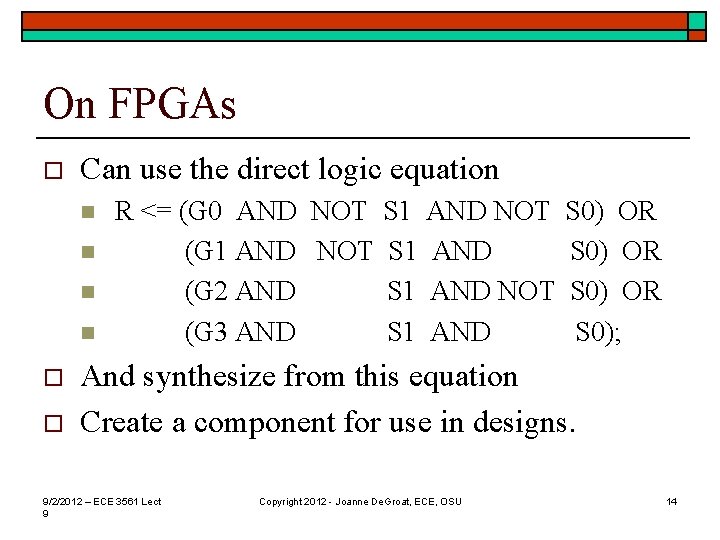

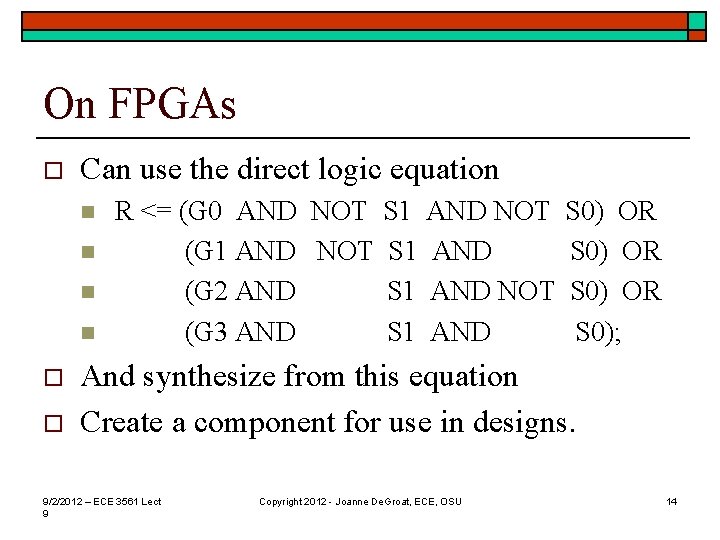

On FPGAs o Can use the direct logic equation n n o o R <= (G 0 AND NOT S 1 AND NOT (G 1 AND NOT S 1 AND (G 2 AND S 1 AND NOT (G 3 AND S 1 AND S 0) OR S 0); And synthesize from this equation Create a component for use in designs. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 14

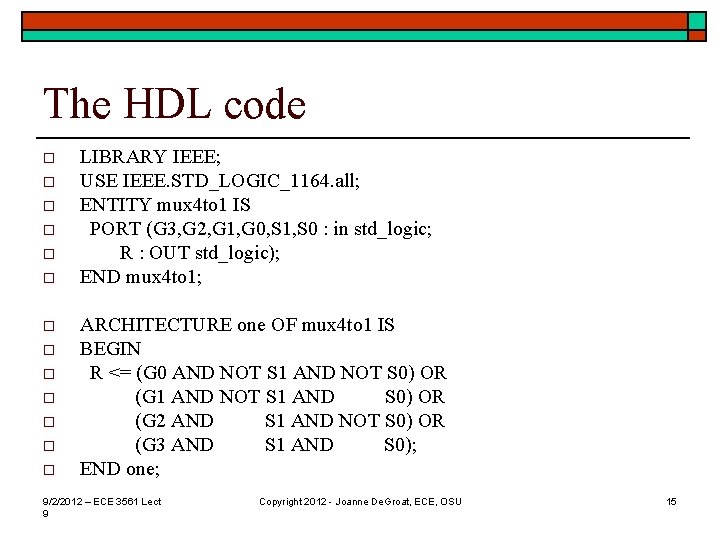

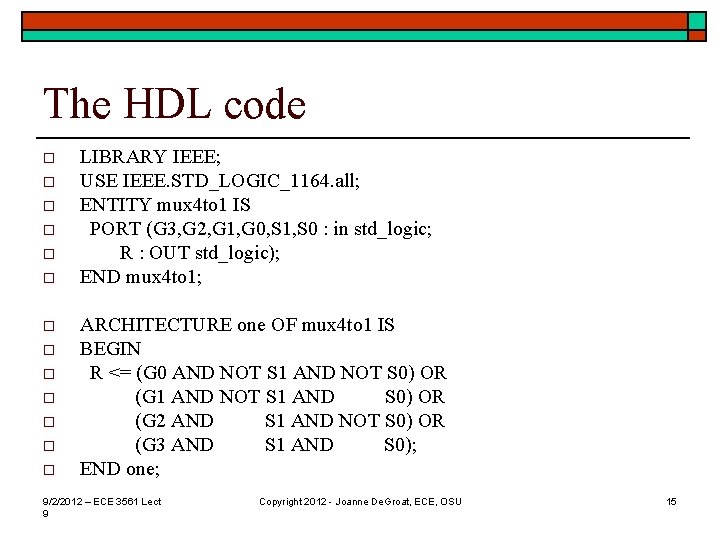

The HDL code o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY mux 4 to 1 IS PORT (G 3, G 2, G 1, G 0, S 1, S 0 : in std_logic; R : OUT std_logic); END mux 4 to 1; ARCHITECTURE one OF mux 4 to 1 IS BEGIN R <= (G 0 AND NOT S 1 AND NOT S 0) OR (G 1 AND NOT S 1 AND S 0) OR (G 2 AND S 1 AND NOT S 0) OR (G 3 AND S 1 AND S 0); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 15

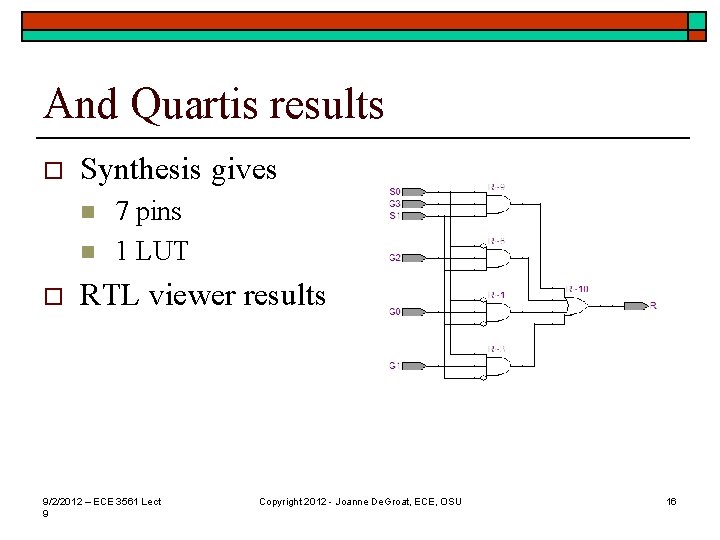

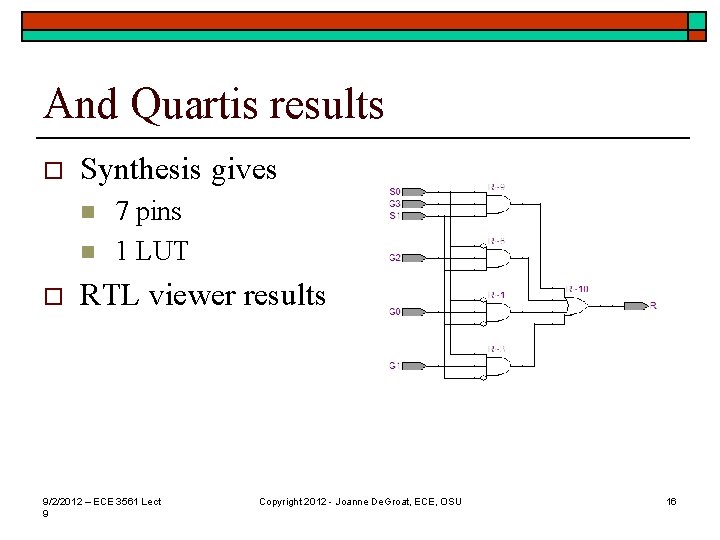

And Quartis results o Synthesis gives n n o 7 pins 1 LUT RTL viewer results 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 16

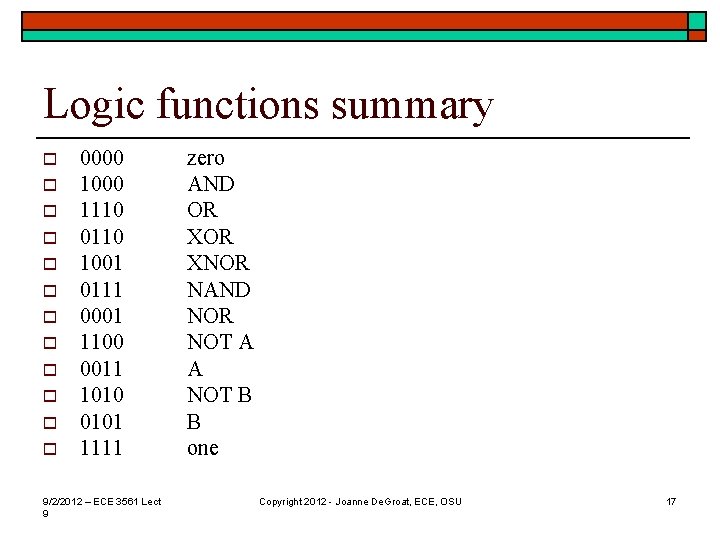

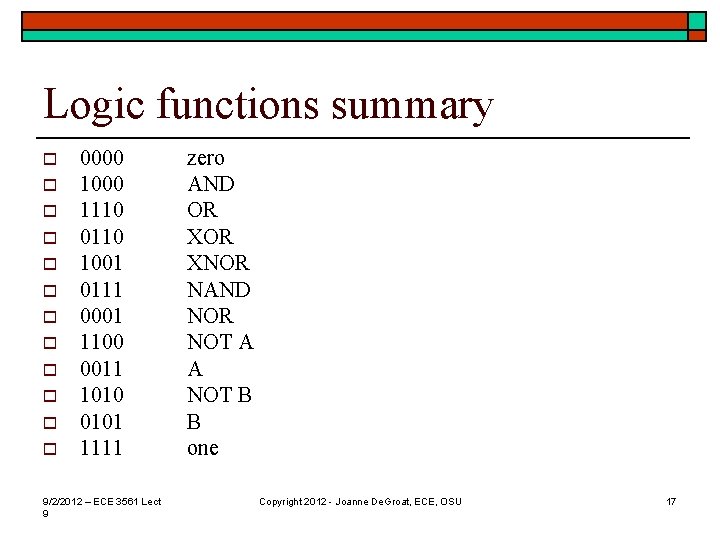

Logic functions summary o o o 0000 1110 0110 1001 0111 0001 1100 0011 1010 0101 1111 9/2/2012 – ECE 3561 Lect 9 zero AND OR XNOR NAND NOR NOT A A NOT B B one Copyright 2012 - Joanne De. Groat, ECE, OSU 17

Now - the arithmetic unit o o Typically integer add/subtract 2’s complement Can be simple – A ripple carry adder Could also be a carry lookahead Start with a simple ripple carry adder 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 18

Do component based design o Full adder n n o Sum = a XOR b XOR c Carry = ab + ac + bc Create the HDL code and synthesize 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 19

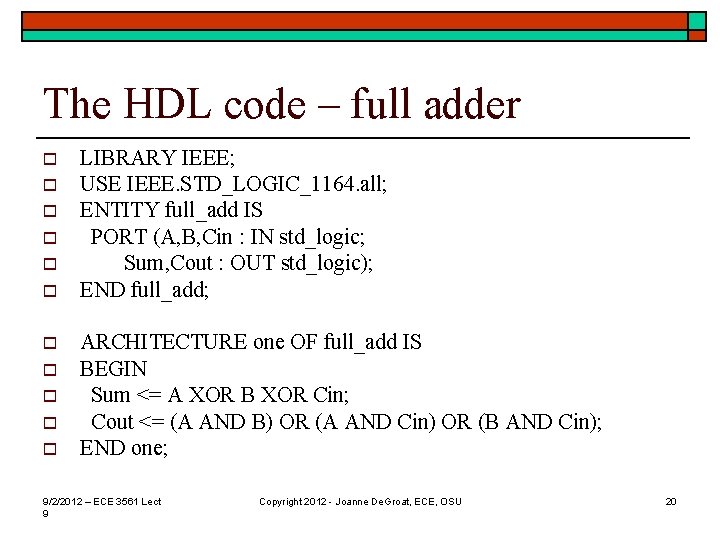

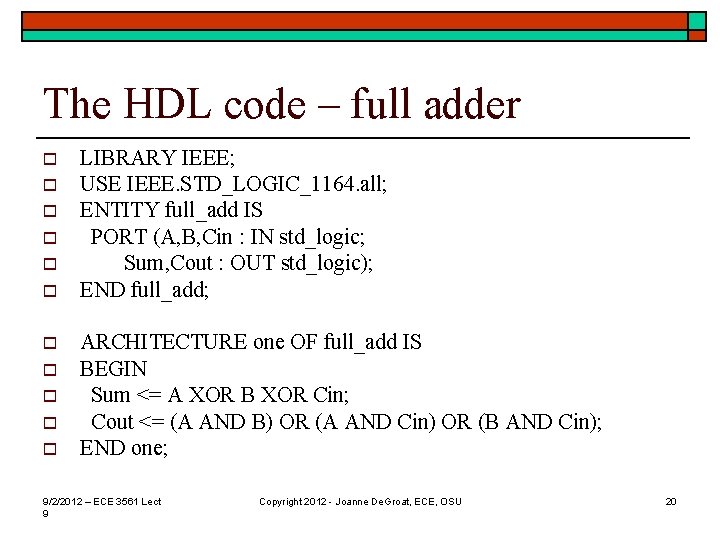

The HDL code – full adder o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY full_add IS PORT (A, B, Cin : IN std_logic; Sum, Cout : OUT std_logic); END full_add; ARCHITECTURE one OF full_add IS BEGIN Sum <= A XOR B XOR Cin; Cout <= (A AND B) OR (A AND Cin) OR (B AND Cin); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 20

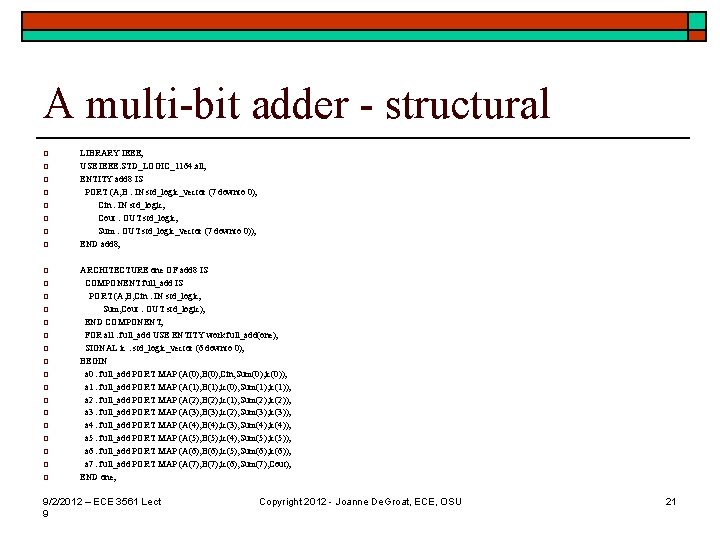

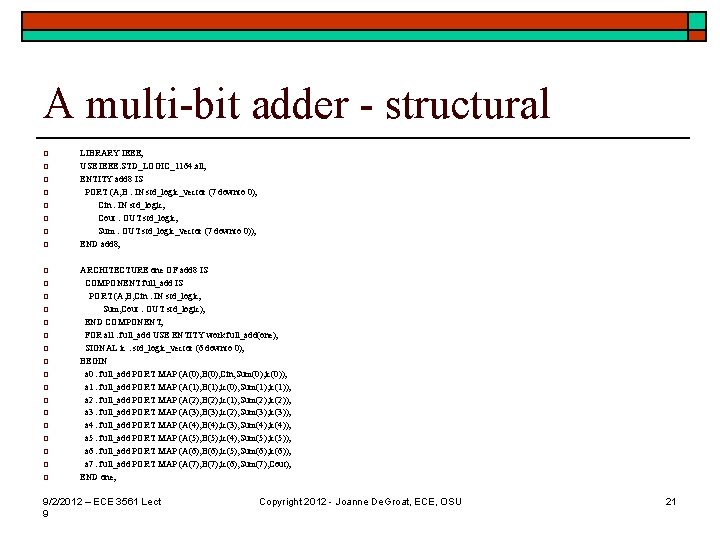

A multi-bit adder - structural o o o o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY add 8 IS PORT (A, B : IN std_logic_vector (7 downto 0); Cin : IN std_logic; Cout : OUT std_logic; Sum : OUT std_logic_vector (7 downto 0)); END add 8; ARCHITECTURE one OF add 8 IS COMPONENT full_add IS PORT (A, B, Cin : IN std_logic; Sum, Cout : OUT std_logic); END COMPONENT; FOR all : full_add USE ENTITY work. full_add(one); SIGNAL ic : std_logic_vector (6 downto 0); BEGIN a 0 : full_add PORT MAP (A(0), B(0), Cin, Sum(0), ic(0)); a 1 : full_add PORT MAP (A(1), B(1), ic(0), Sum(1), ic(1)); a 2 : full_add PORT MAP (A(2), B(2), ic(1), Sum(2), ic(2)); a 3 : full_add PORT MAP (A(3), B(3), ic(2), Sum(3), ic(3)); a 4 : full_add PORT MAP (A(4), B(4), ic(3), Sum(4), ic(4)); a 5 : full_add PORT MAP (A(5), B(5), ic(4), Sum(5), ic(5)); a 6 : full_add PORT MAP (A(6), B(6), ic(5), Sum(6), ic(6)); a 7 : full_add PORT MAP (A(7), B(7), ic(6), Sum(7), Cout); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 21

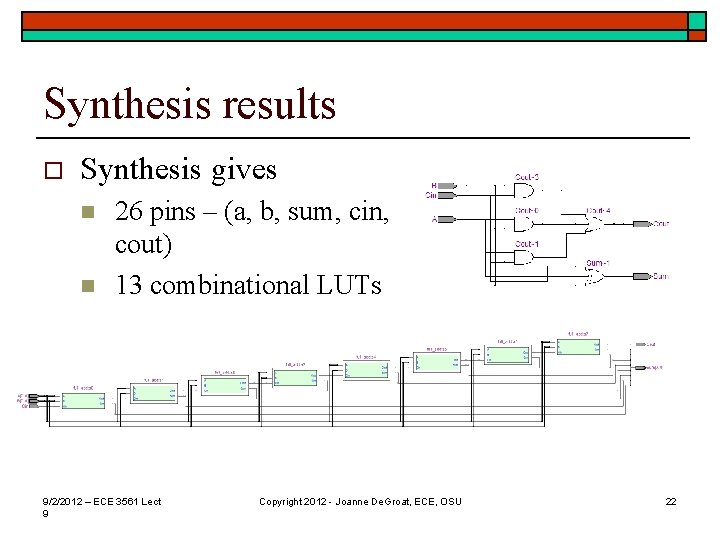

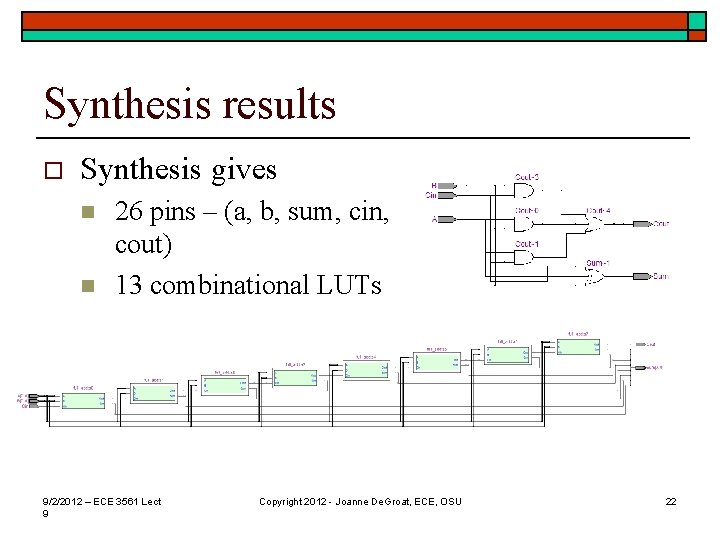

Synthesis results o Synthesis gives n n 26 pins – (a, b, sum, cin, cout) 13 combinational LUTs 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 22

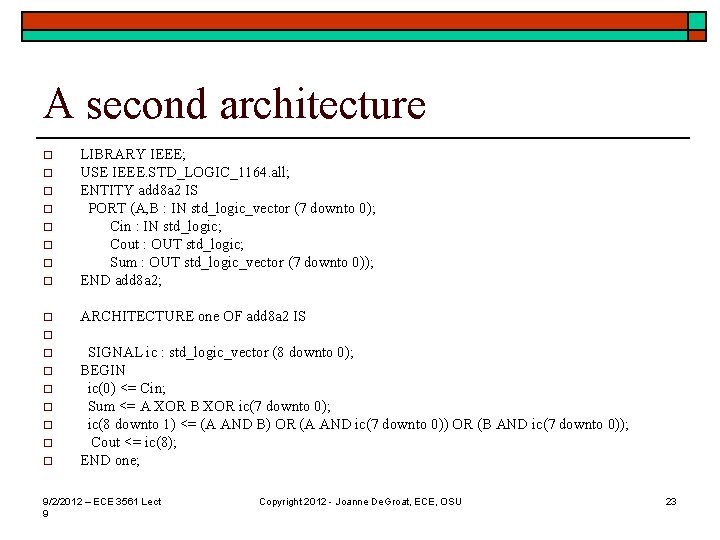

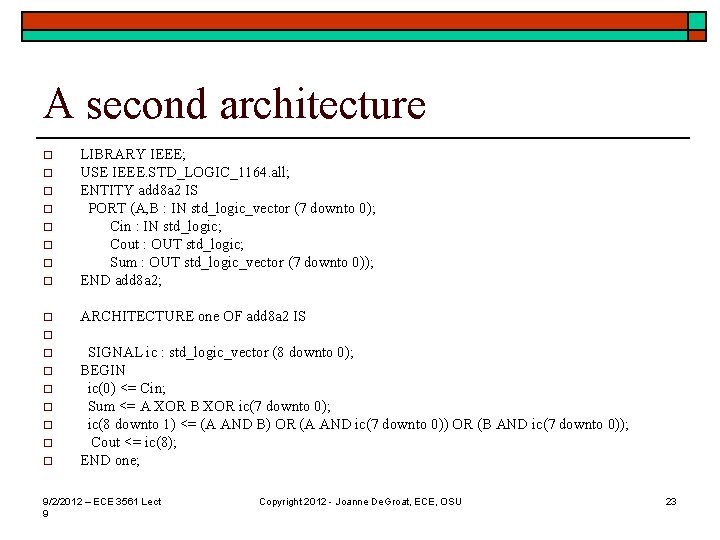

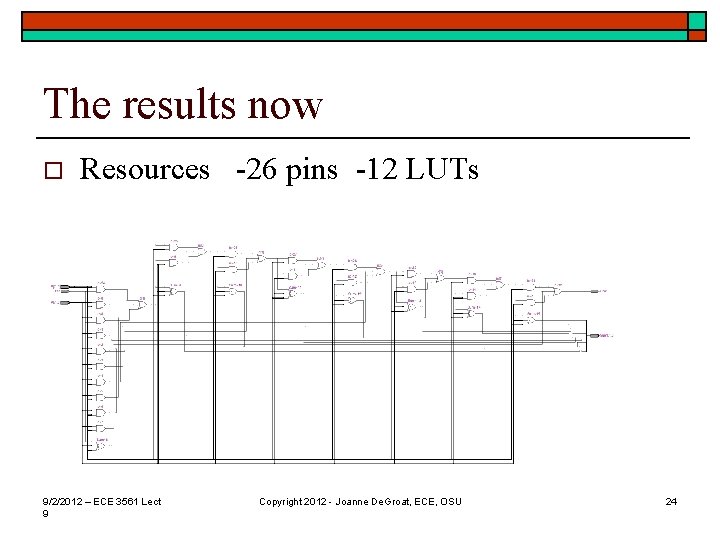

A second architecture o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY add 8 a 2 IS PORT (A, B : IN std_logic_vector (7 downto 0); Cin : IN std_logic; Cout : OUT std_logic; Sum : OUT std_logic_vector (7 downto 0)); END add 8 a 2; o ARCHITECTURE one OF add 8 a 2 IS o o o o SIGNAL ic : std_logic_vector (8 downto 0); BEGIN ic(0) <= Cin; Sum <= A XOR B XOR ic(7 downto 0); ic(8 downto 1) <= (A AND B) OR (A AND ic(7 downto 0)) OR (B AND ic(7 downto 0)); Cout <= ic(8); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 23

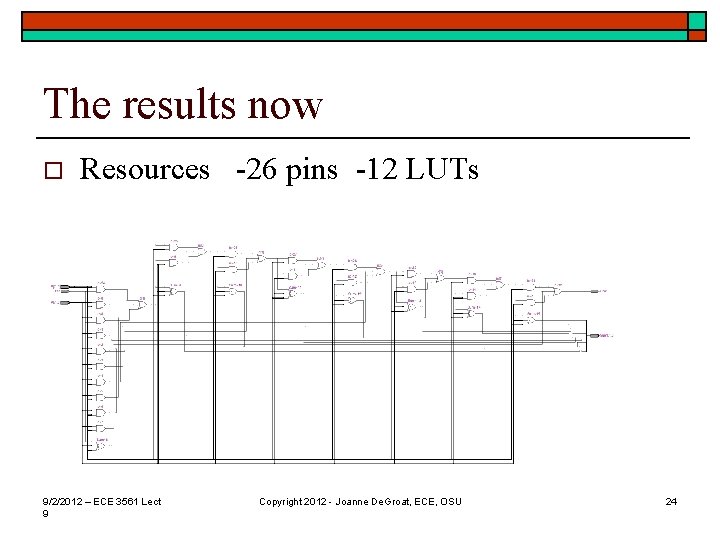

The results now o Resources -26 pins -12 LUTs 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 24

Lecture summary o The adder was a simple ripple carry adder. o Other Architectures n n n Carry Lookahead Carry select Carry multiplexed 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 25