L 22 Register Set Debugging Dual Ported Register

L 22 – Register Set Debugging

Dual Ported Register Set o Narrowed the problem to the input data from the multiplexers o Ref: text Unit 10, 17, 20 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

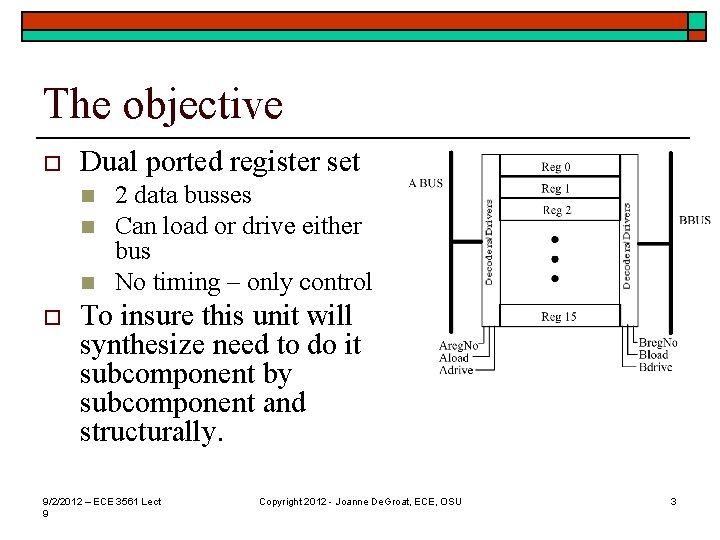

The objective o Dual ported register set n n n o 2 data busses Can load or drive either bus No timing – only control To insure this unit will synthesize need to do it subcomponent by subcomponent and structurally. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 3

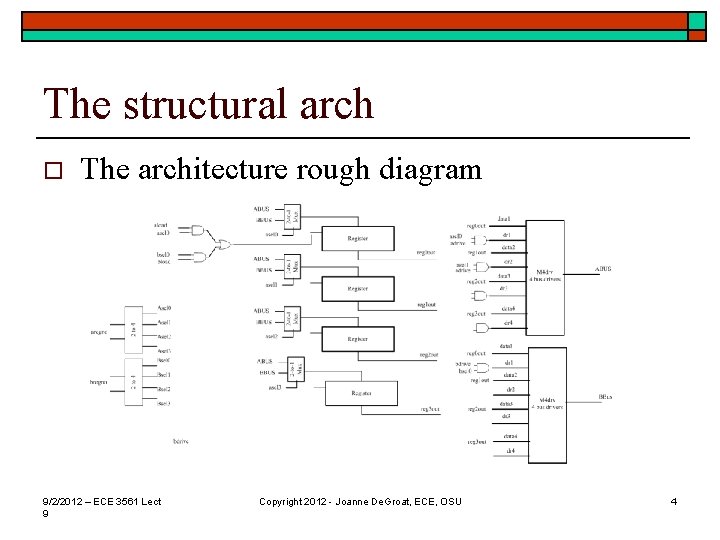

The structural arch o The architecture rough diagram 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 4

From last time o o Narrowed the problem that it was input into the register, i. e. , the output of the muxes. The problem was in the control equation. Comment out all but the input decoders and the input muxes. Add to the waveform the control and output from unit m 0, the mux that supplies data to register 0. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 5

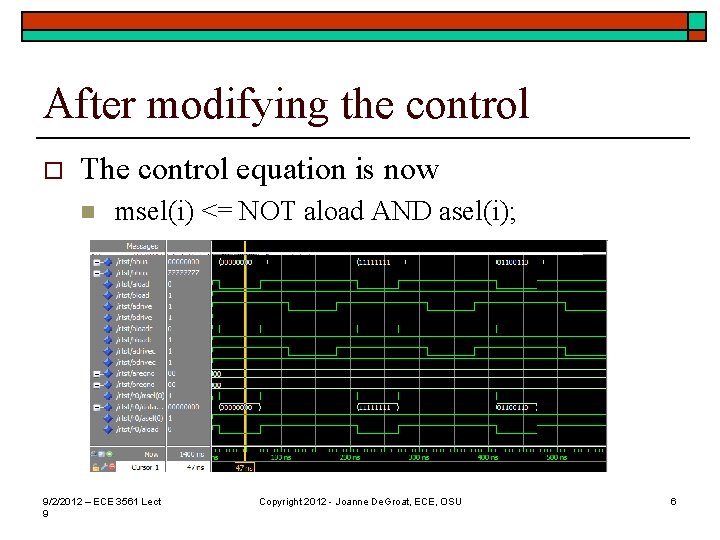

After modifying the control o The control equation is now n msel(i) <= NOT aload AND asel(i); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 6

For the BBUS input selection o Also working when a BBUS input 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 7

One thought o o Could it be that the equation used in the mux was part of the problem? Orig equation n o Tried generating an 8 bit version of sel n n o o dataout <= linput when sel=‘ 1’ ELSE rinput; Isel <= sel&sel& sel&sel; dataout <= (linput AND isel) OR (rinput AND NOT isel); First version was muxing the ‘Z’, 2 nd version resulted in ‘X’. Problem was the control equation so orig used. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 8

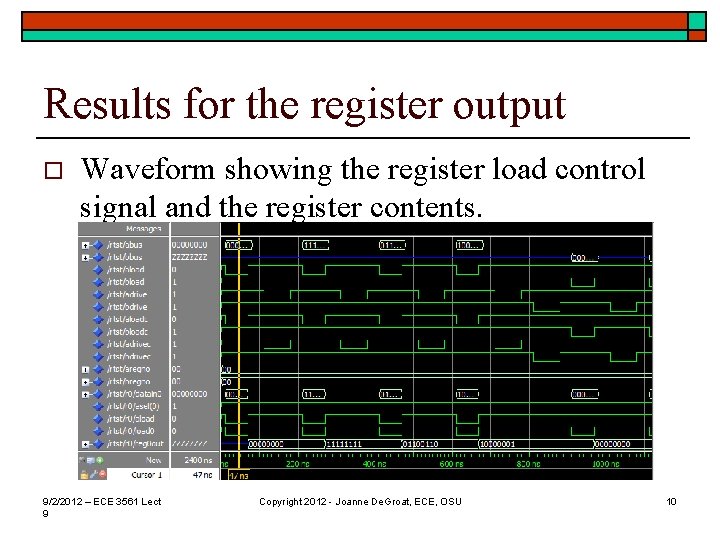

Now the register load signal o o Also found a polarity error. Had a falling edge when you desired the rising edge. Fixed Now can add back the registers and run 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 9

Results for the register output o Waveform showing the register load control signal and the register contents. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 10

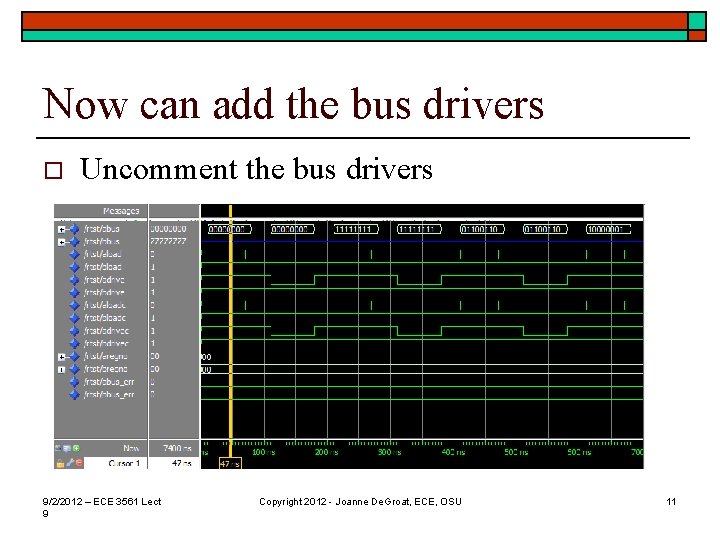

Now can add the bus drivers o Uncomment the bus drivers 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 11

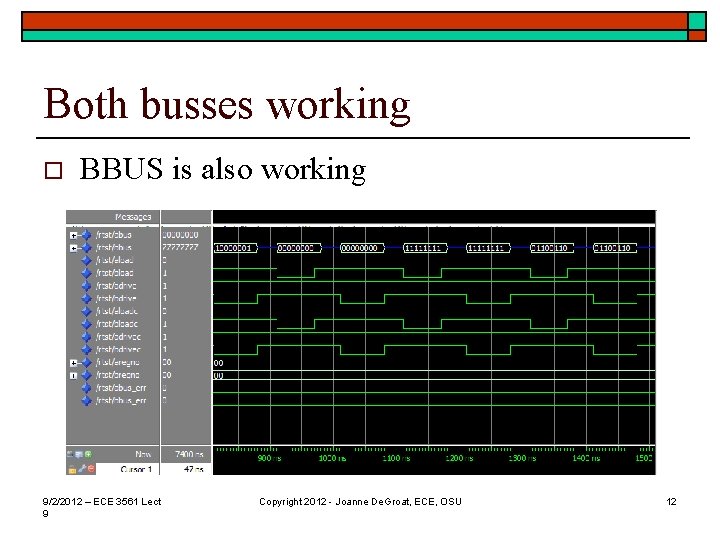

Both busses working o BBUS is also working 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 12

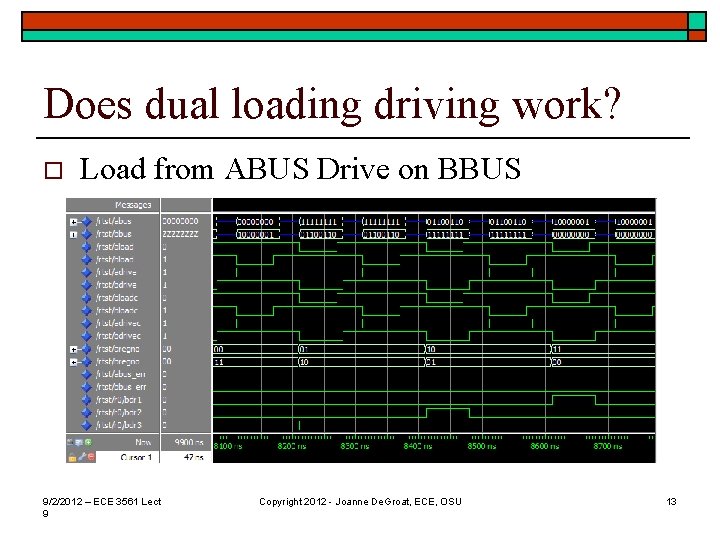

Does dual loading driving work? o Load from ABUS Drive on BBUS 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 13

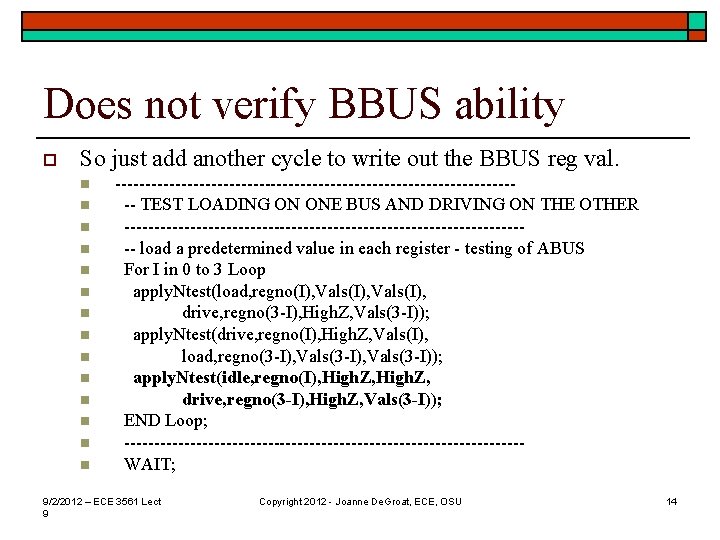

Does not verify BBUS ability o So just add another cycle to write out the BBUS reg val. n n n n ---------------------------------- TEST LOADING ON ONE BUS AND DRIVING ON THE OTHER ---------------------------------- load a predetermined value in each register - testing of ABUS For I in 0 to 3 Loop apply. Ntest(load, regno(I), Vals(I), drive, regno(3 -I), High. Z, Vals(3 -I)); apply. Ntest(drive, regno(I), High. Z, Vals(I), load, regno(3 -I), Vals(3 -I)); apply. Ntest(idle, regno(I), High. Z, drive, regno(3 -I), High. Z, Vals(3 -I)); END Loop; ---------------------------------WAIT; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 14

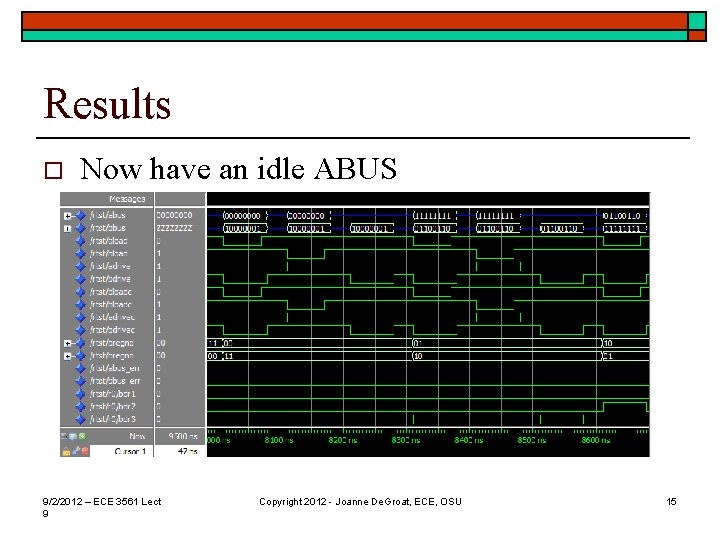

Results o Now have an idle ABUS 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 15

YEAH o o DEMO TIME. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 16

And it still synthesizes!! o Synthesis results 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 17

Synthesis statistics o o o Registers – 32 Pins – 24 LUTs – 60 (even though control equations are a bit more complex – why the same? ) Average Fan Out – 3. 6 (higher) Timing results from Quartis n n Set up time –from ABUS to register dataout 2. 2 ns Time from adrive to ABUS – 10. 67 ns 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 18

Lecture summary o o Have seen how to debug a 4 register location dual ported register-set. Also some information on resolved signals and units for resolved signals. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 19

- Slides: 19