L 20 Register Set The 430 Register Set

- Slides: 52

L 20 – Register Set

The 430 Register Set o Not exactly a dual ported register set, but a dual drive register set. o Ref: text Unit 10, 17, 20 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

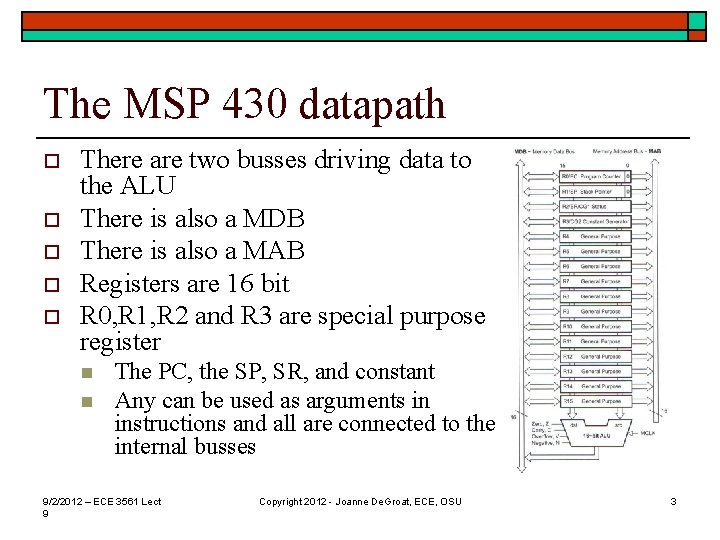

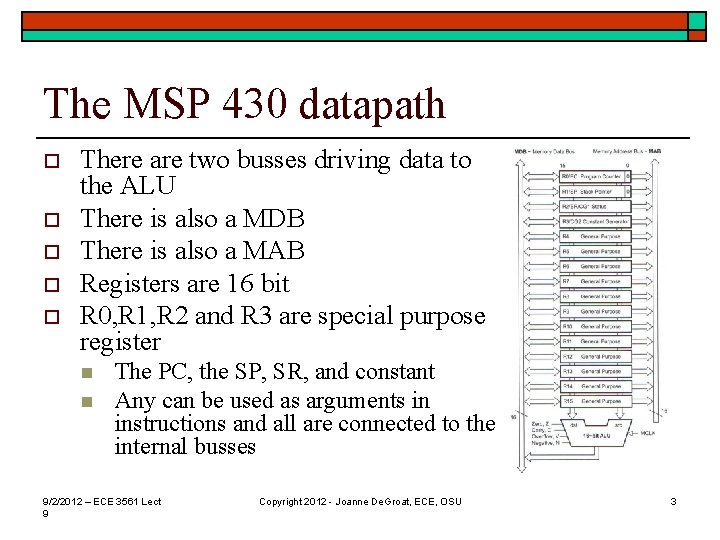

The MSP 430 datapath o o o There are two busses driving data to the ALU There is also a MDB There is also a MAB Registers are 16 bit R 0, R 1, R 2 and R 3 are special purpose register n n The PC, the SP, SR, and constant Any can be used as arguments in instructions and all are connected to the internal busses 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 3

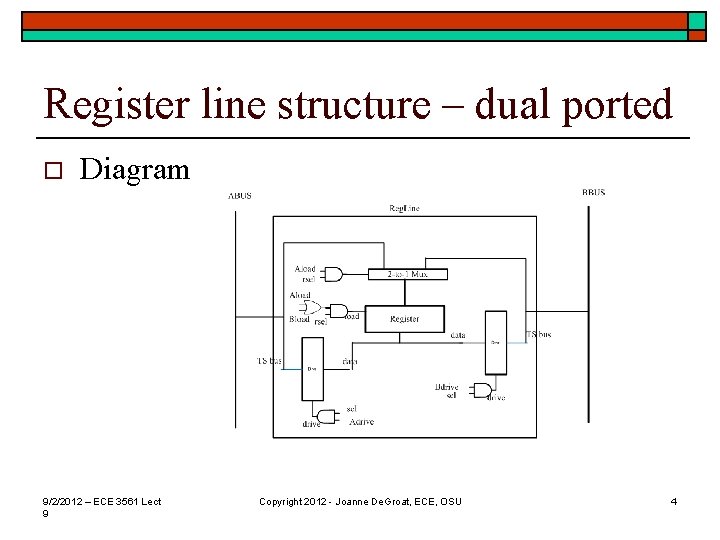

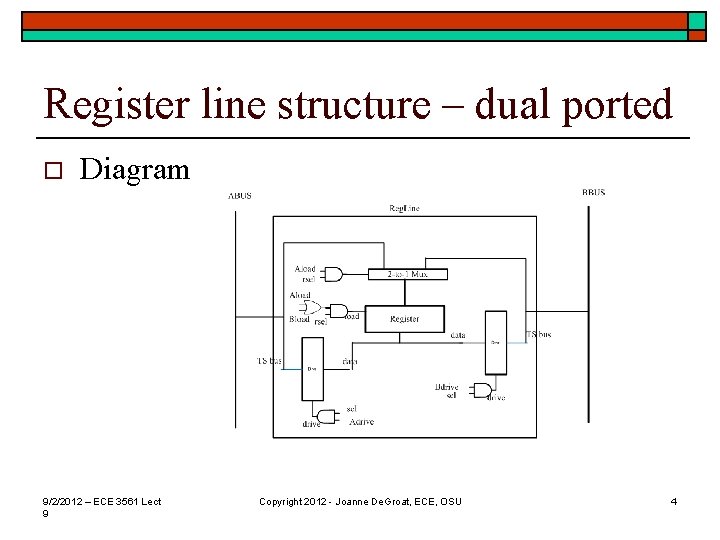

Register line structure – dual ported o Diagram 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 4

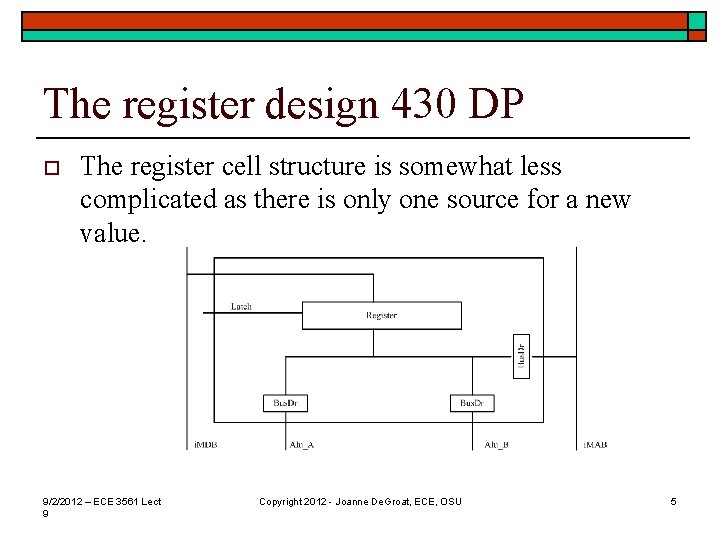

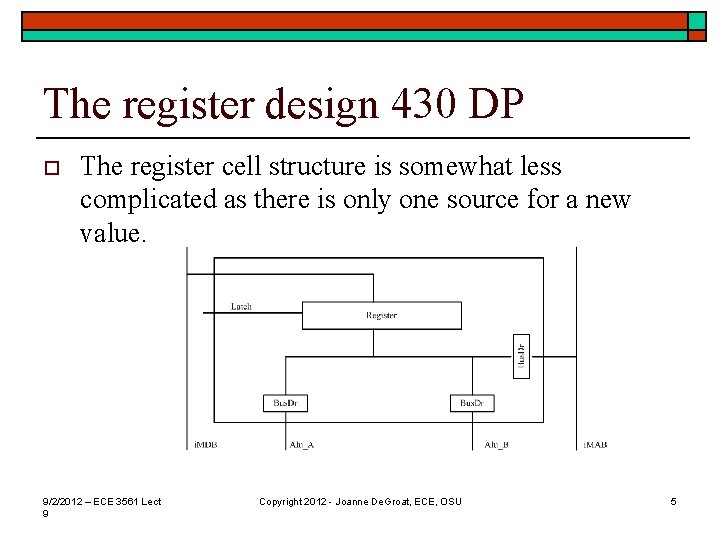

The register design 430 DP o The register cell structure is somewhat less complicated as there is only one source for a new value. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 5

Still need the bus driver o o The bus driver is still needed to drive the bus. They are the same as before, but they are now 16 bits each. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 6

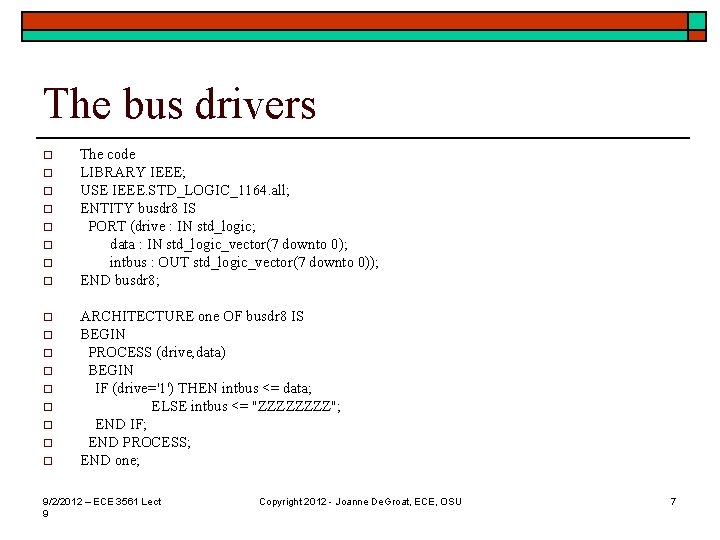

The bus drivers o o o o o The code LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY busdr 8 IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END busdr 8; ARCHITECTURE one OF busdr 8 IS BEGIN PROCESS (drive, data) BEGIN IF (drive='1') THEN intbus <= data; ELSE intbus <= "ZZZZ"; END IF; END PROCESS; END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 7

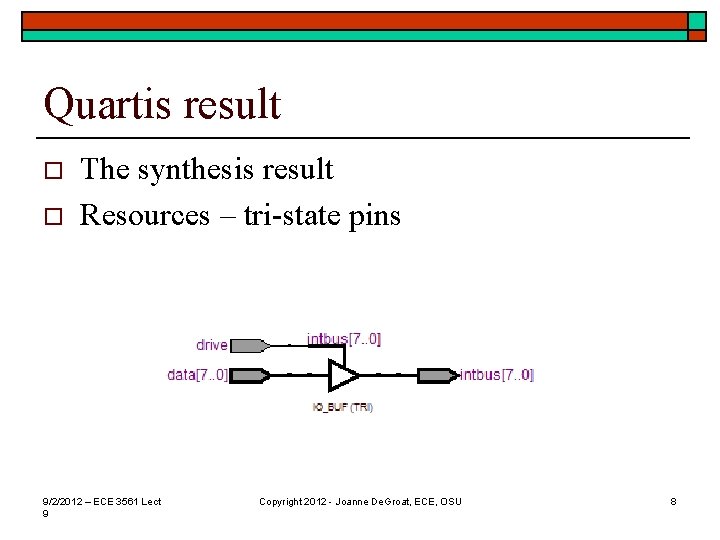

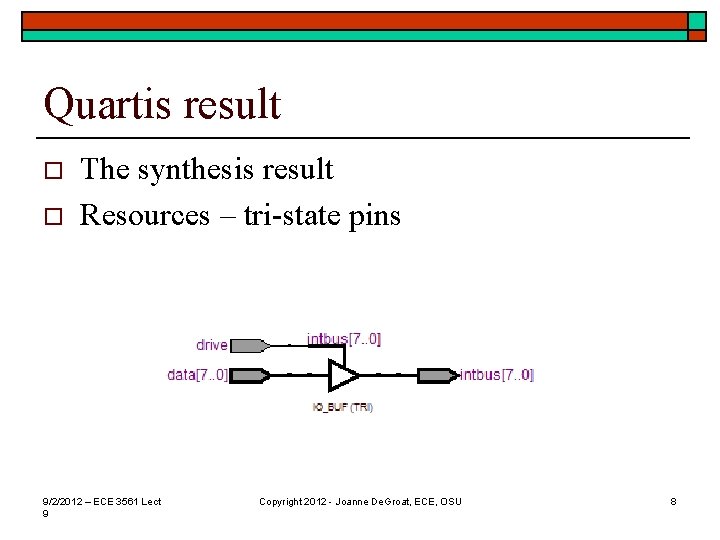

Quartis result o o The synthesis result Resources – tri-state pins 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 8

Next assignment o o o The next assignment is to create a bus driver, a 4 -to-16 demultiplexer, and a 16 -bit register cell. Write the VHDL code for it. You can write a simple test bench to test it logically it you want, but most likely will wait until the register set is done to do the logic simulation. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 9

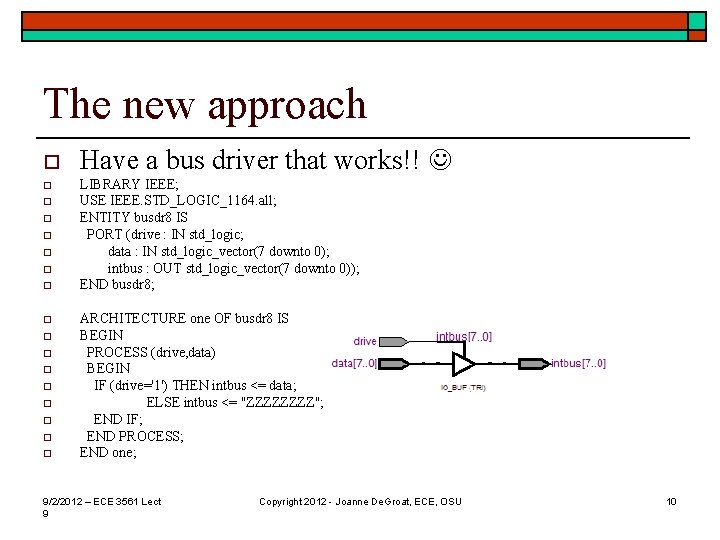

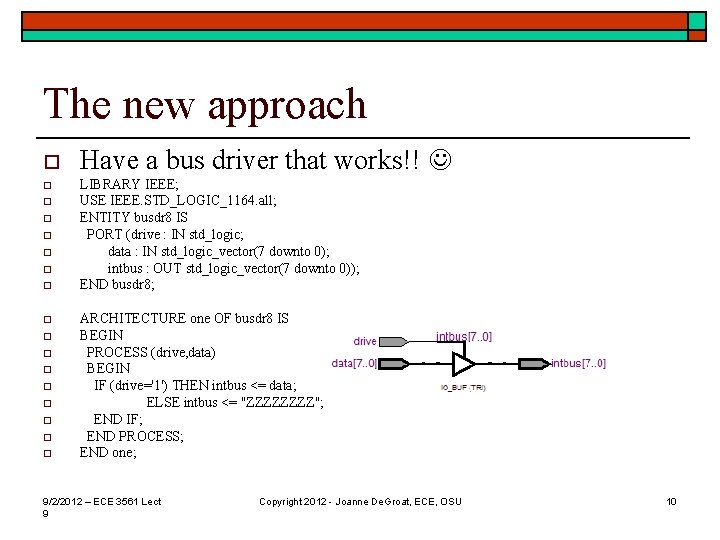

The new approach o o o o o Have a bus driver that works!! LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY busdr 8 IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END busdr 8; ARCHITECTURE one OF busdr 8 IS BEGIN PROCESS (drive, data) BEGIN IF (drive='1') THEN intbus <= data; ELSE intbus <= "ZZZZ"; END IF; END PROCESS; END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 10

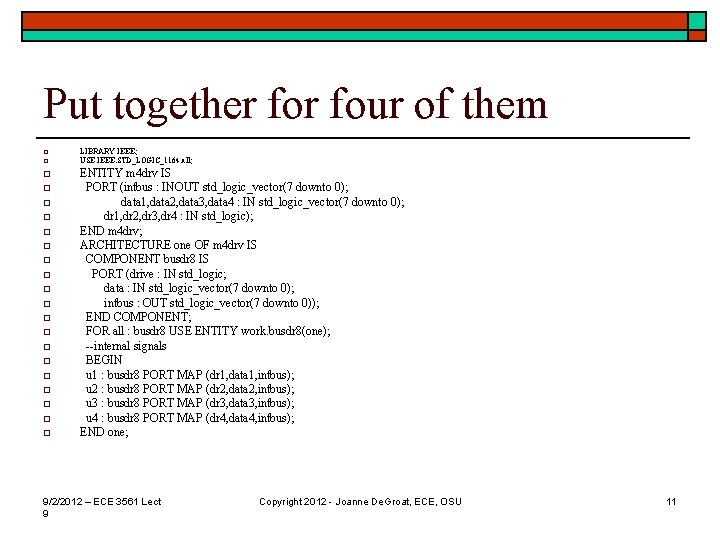

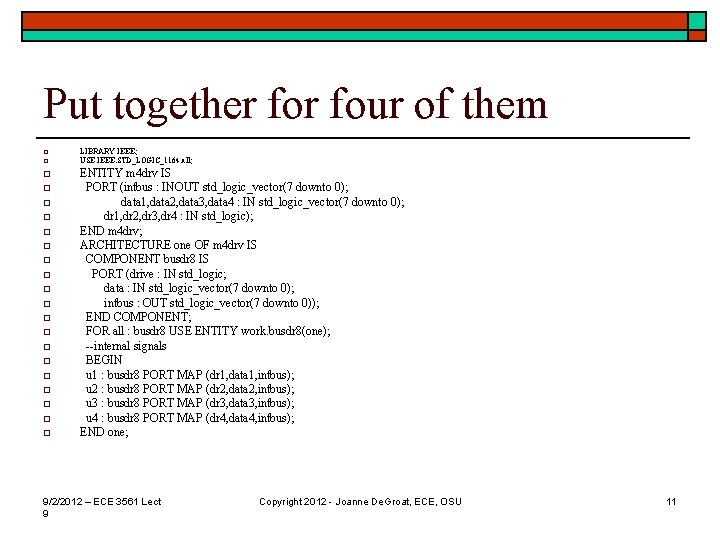

Put together four of them o o o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY m 4 drv IS PORT (intbus : INOUT std_logic_vector(7 downto 0); data 1, data 2, data 3, data 4 : IN std_logic_vector(7 downto 0); dr 1, dr 2, dr 3, dr 4 : IN std_logic); END m 4 drv; ARCHITECTURE one OF m 4 drv IS COMPONENT busdr 8 IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END COMPONENT; FOR all : busdr 8 USE ENTITY work. busdr 8(one); --internal signals BEGIN u 1 : busdr 8 PORT MAP (dr 1, data 1, intbus); u 2 : busdr 8 PORT MAP (dr 2, data 2, intbus); u 3 : busdr 8 PORT MAP (dr 3, data 3, intbus); u 4 : busdr 8 PORT MAP (dr 4, data 4, intbus); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 11

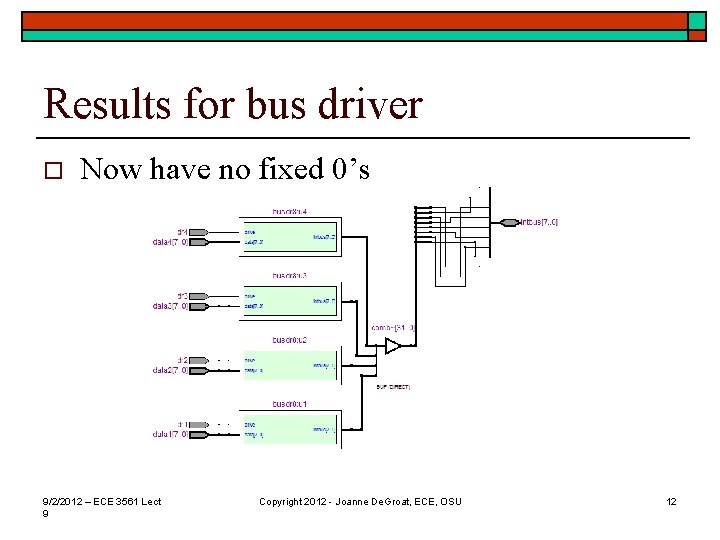

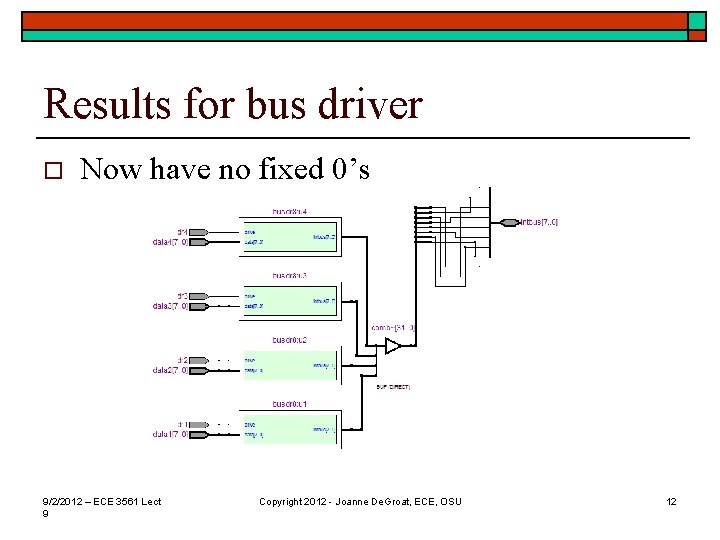

Results for bus driver o Now have no fixed 0’s 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 12

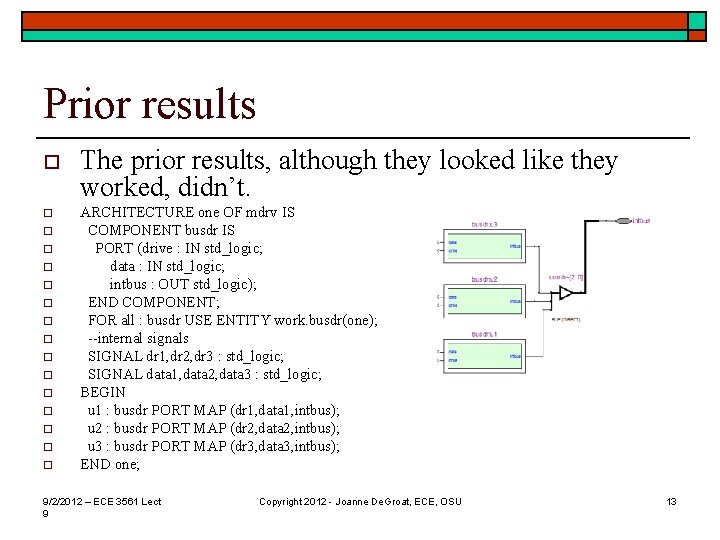

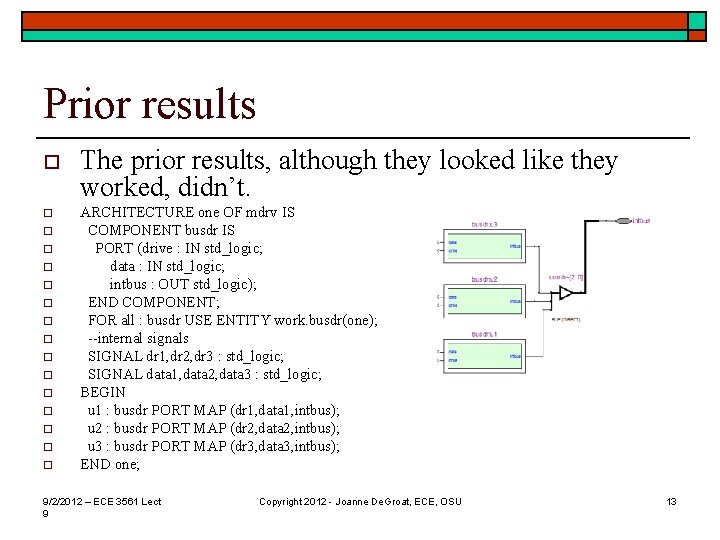

Prior results o o o o The prior results, although they looked like they worked, didn’t. ARCHITECTURE one OF mdrv IS COMPONENT busdr IS PORT (drive : IN std_logic; data : IN std_logic; intbus : OUT std_logic); END COMPONENT; FOR all : busdr USE ENTITY work. busdr(one); --internal signals SIGNAL dr 1, dr 2, dr 3 : std_logic; SIGNAL data 1, data 2, data 3 : std_logic; BEGIN u 1 : busdr PORT MAP (dr 1, data 1, intbus); u 2 : busdr PORT MAP (dr 2, data 2, intbus); u 3 : busdr PORT MAP (dr 3, data 3, intbus); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 13

The 4 -to-16 multiplexer o Specification n n Input – 4 bit binary number Output – 16 lines numbered o 0 to o 15 operation is such that only 1 of the outputs is active, indicating the value of the 4 -bit binary input. Input and output type – can be std_logic or std_logic_vector. Recommend using direct output generation by writing the logic equation for each output line directly from the 4 -bit input. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 14

The 16 -bit register cell o o Write a VHDL ENTITY and ARCHITECTURE for a 16 -bit register unit. Inputs – latch – std_logic din – std_logic_vector Output dout – std_logic-vector 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 15

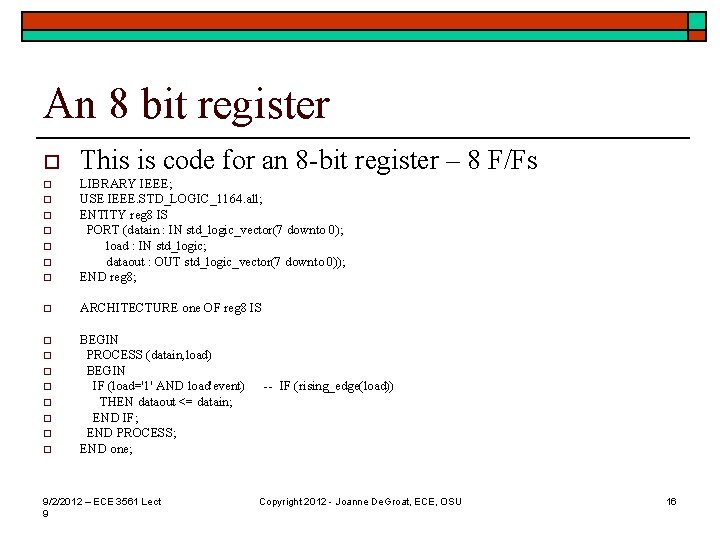

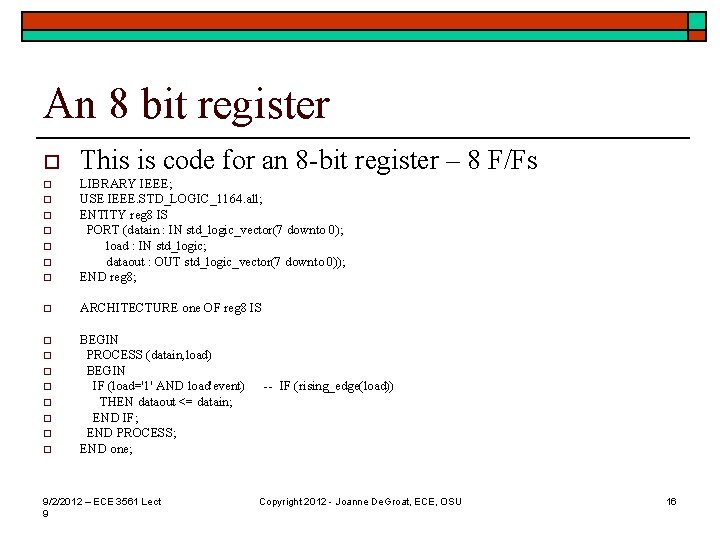

An 8 bit register o This is code for an 8 -bit register – 8 F/Fs o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY reg 8 IS PORT (datain : IN std_logic_vector(7 downto 0); load : IN std_logic; dataout : OUT std_logic_vector(7 downto 0)); END reg 8; o ARCHITECTURE one OF reg 8 IS o BEGIN PROCESS (datain, load) BEGIN IF (load='1' AND load'event) THEN dataout <= datain; END IF; END PROCESS; END one; o o o o 9/2/2012 – ECE 3561 Lect 9 -- IF (rising_edge(load)) Copyright 2012 - Joanne De. Groat, ECE, OSU 16

Another use of the register cell o o The register cell will also be used for the input latching for the inputs to the ALU. The bus driver will also be used for the output driver of the ALU result onto its bus. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 17

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 18

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 19

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 20

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 21

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 22

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 23

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 24

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 25

The objective o Dual ported register set n n n o 2 data busses Can load or drive either bus No timing – only control To insure this unit will synthesize need to do it subcomponent by subcomponent and structurally. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 26

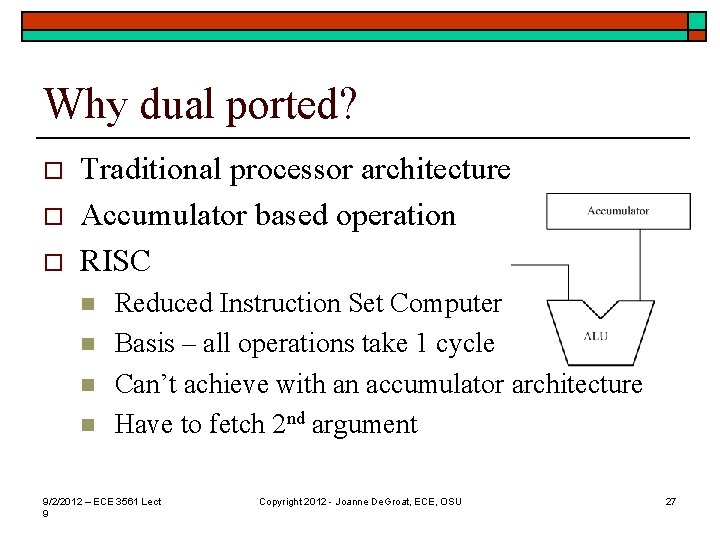

Why dual ported? o o o Traditional processor architecture Accumulator based operation RISC n n Reduced Instruction Set Computer Basis – all operations take 1 cycle Can’t achieve with an accumulator architecture Have to fetch 2 nd argument 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 27

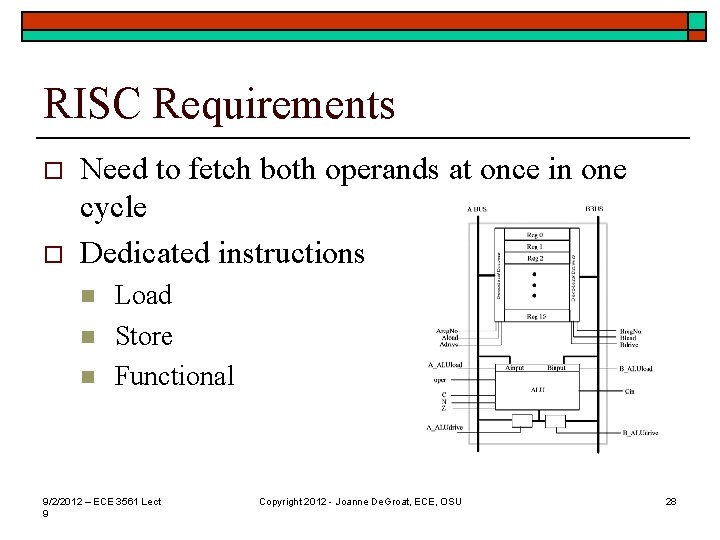

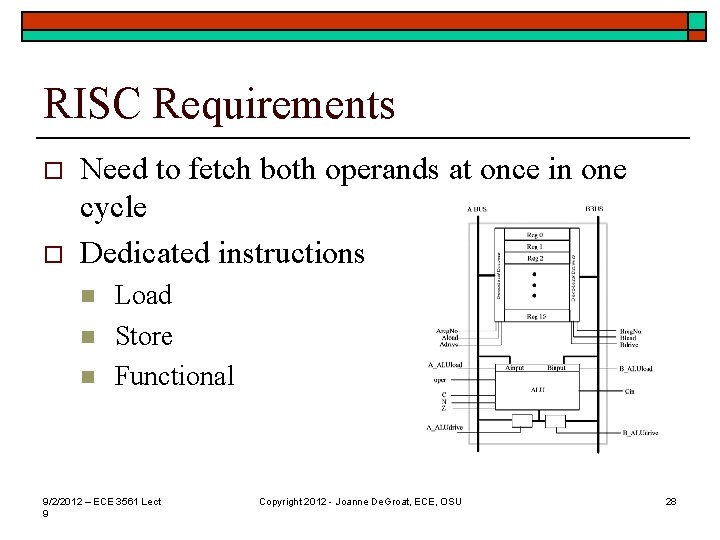

RISC Requirements o o Need to fetch both operands at once in one cycle Dedicated instructions n n n Load Store Functional 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 28

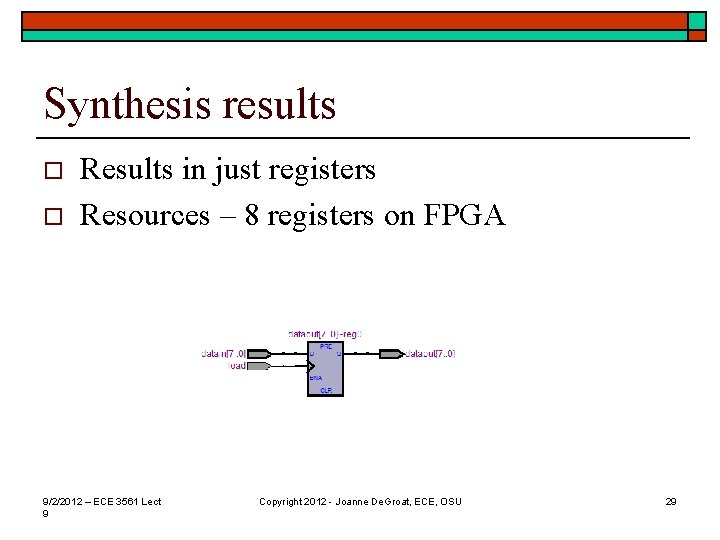

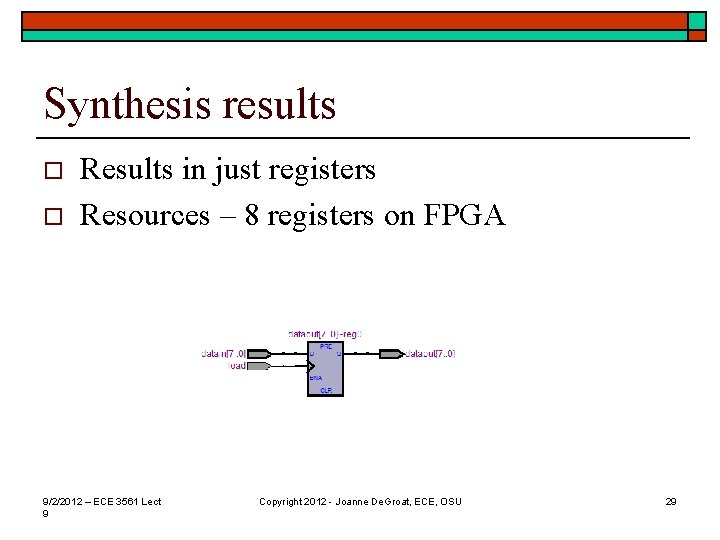

Synthesis results o o Results in just registers Resources – 8 registers on FPGA 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 29

2 -to-1 multiplexer 8 -bit o The code o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY mux 2 to 1 x 8 IS PORT (linput, rinput : IN std_logic_vector(7 downto 0); sel : IN std_logic; dataout : OUT std_logic_vector(7 downto 0)); END mux 2 to 1 x 8; o o o o o ARCHITECTURE one OF mux 2 to 1 x 8 IS BEGIN dataout <= linput when sel='0' ELSE rinput; END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 30

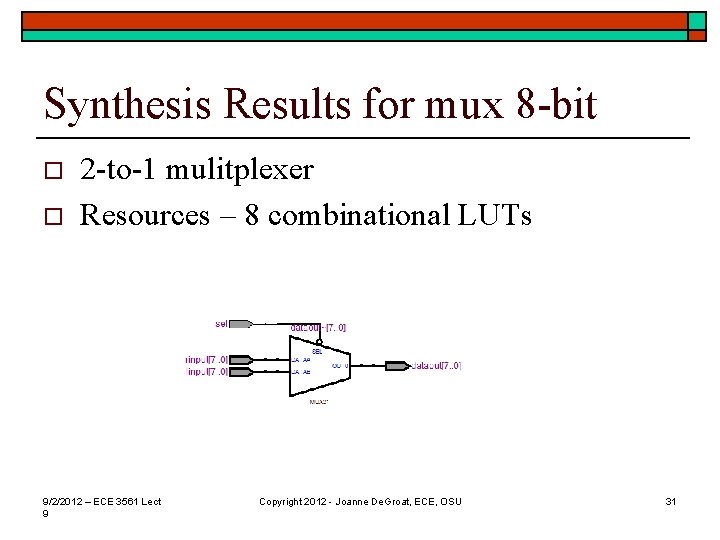

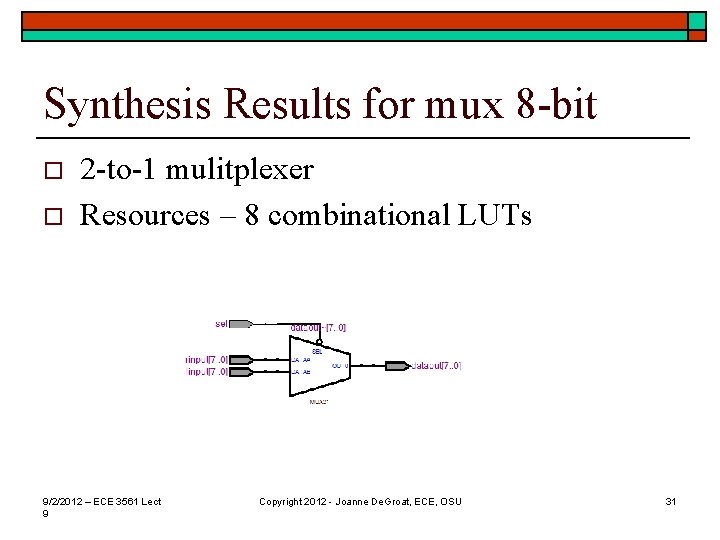

Synthesis Results for mux 8 -bit o o 2 -to-1 mulitplexer Resources – 8 combinational LUTs 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 31

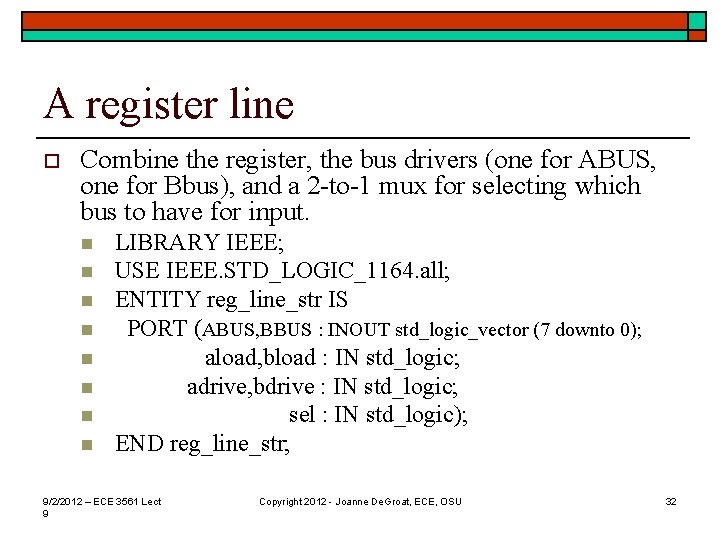

A register line o Combine the register, the bus drivers (one for ABUS, one for Bbus), and a 2 -to-1 mux for selecting which bus to have for input. n n n n LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY reg_line_str IS PORT (ABUS, BBUS : INOUT std_logic_vector (7 downto 0); aload, bload : IN std_logic; adrive, bdrive : IN std_logic; sel : IN std_logic); END reg_line_str; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 32

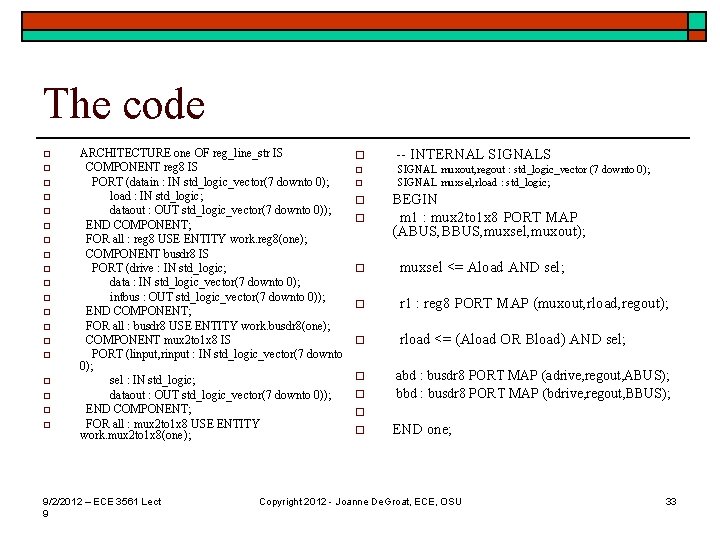

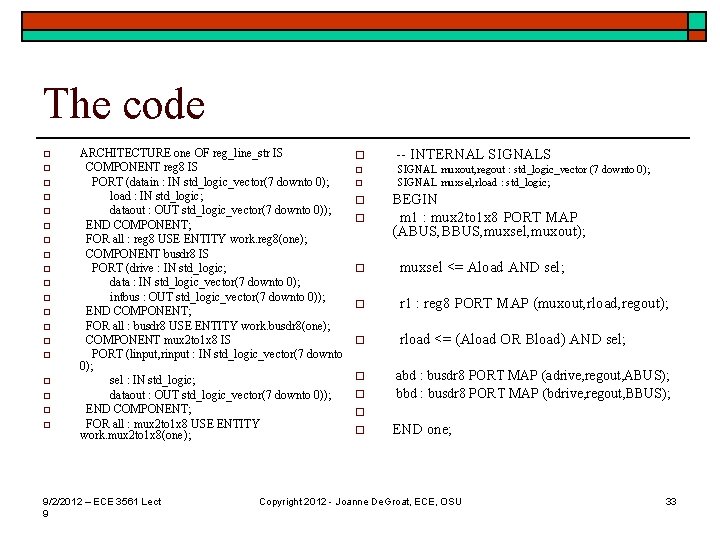

The code o o o o o ARCHITECTURE one OF reg_line_str IS COMPONENT reg 8 IS PORT (datain : IN std_logic_vector(7 downto 0); load : IN std_logic; dataout : OUT std_logic_vector(7 downto 0)); END COMPONENT; FOR all : reg 8 USE ENTITY work. reg 8(one); COMPONENT busdr 8 IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END COMPONENT; FOR all : busdr 8 USE ENTITY work. busdr 8(one); COMPONENT mux 2 to 1 x 8 IS PORT (linput, rinput : IN std_logic_vector(7 downto 0); sel : IN std_logic; dataout : OUT std_logic_vector(7 downto 0)); END COMPONENT; FOR all : mux 2 to 1 x 8 USE ENTITY work. mux 2 to 1 x 8(one); 9/2/2012 – ECE 3561 Lect 9 o -- INTERNAL SIGNALS o SIGNAL muxout, regout : std_logic_vector (7 downto 0); SIGNAL muxsel, rload : std_logic; o o o BEGIN m 1 : mux 2 to 1 x 8 PORT MAP (ABUS, BBUS, muxsel, muxout); o muxsel <= Aload AND sel; o r 1 : reg 8 PORT MAP (muxout, rload, regout); o rload <= (Aload OR Bload) AND sel; o o abd : busdr 8 PORT MAP (adrive, regout, ABUS); bbd : busdr 8 PORT MAP (bdrive, regout, BBUS); o o END one; Copyright 2012 - Joanne De. Groat, ECE, OSU 33

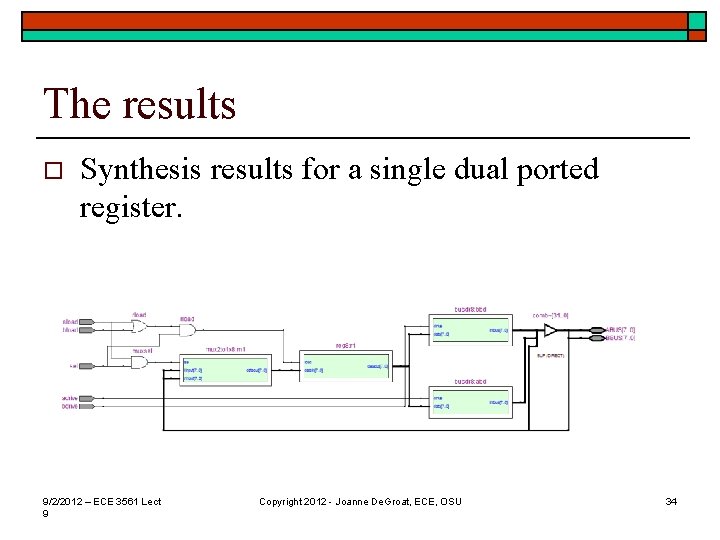

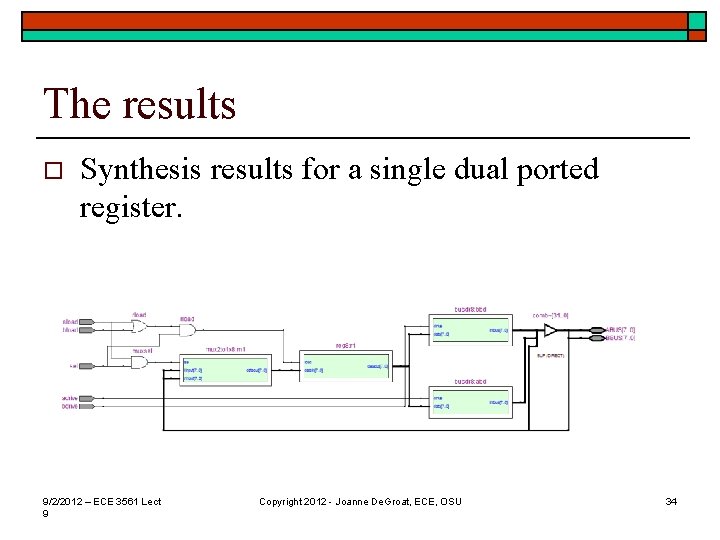

The results o Synthesis results for a single dual ported register. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 34

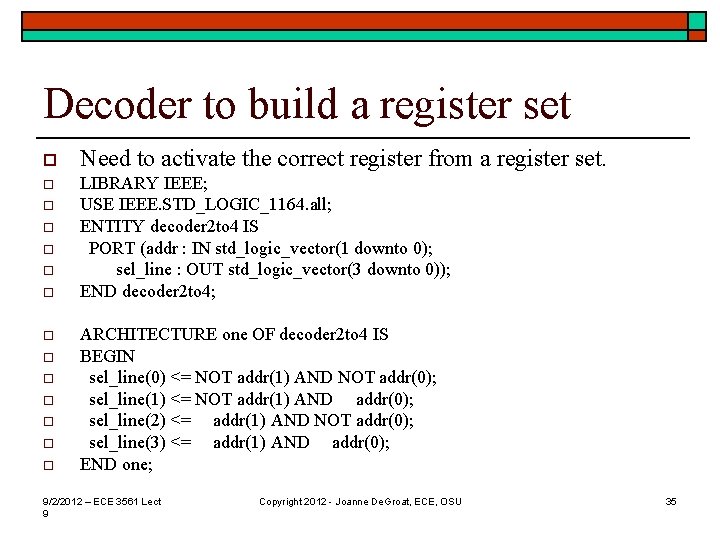

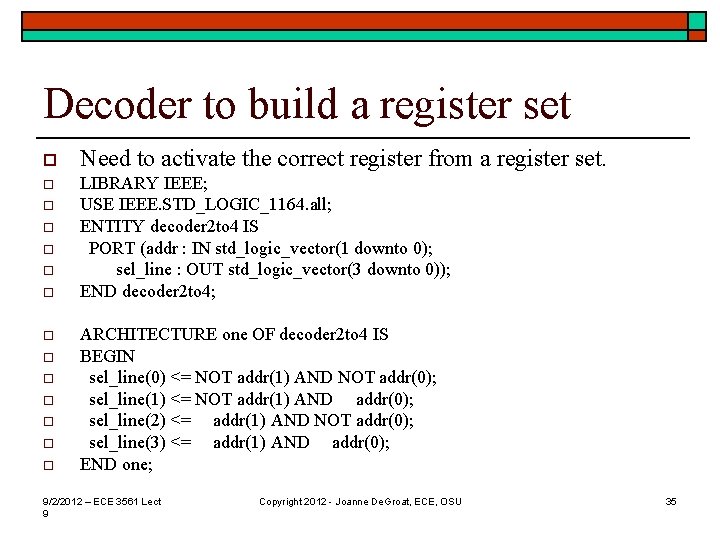

Decoder to build a register set o Need to activate the correct register from a register set. o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY decoder 2 to 4 IS PORT (addr : IN std_logic_vector(1 downto 0); sel_line : OUT std_logic_vector(3 downto 0)); END decoder 2 to 4; o o o ARCHITECTURE one OF decoder 2 to 4 IS BEGIN sel_line(0) <= NOT addr(1) AND NOT addr(0); sel_line(1) <= NOT addr(1) AND addr(0); sel_line(2) <= addr(1) AND NOT addr(0); sel_line(3) <= addr(1) AND addr(0); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 35

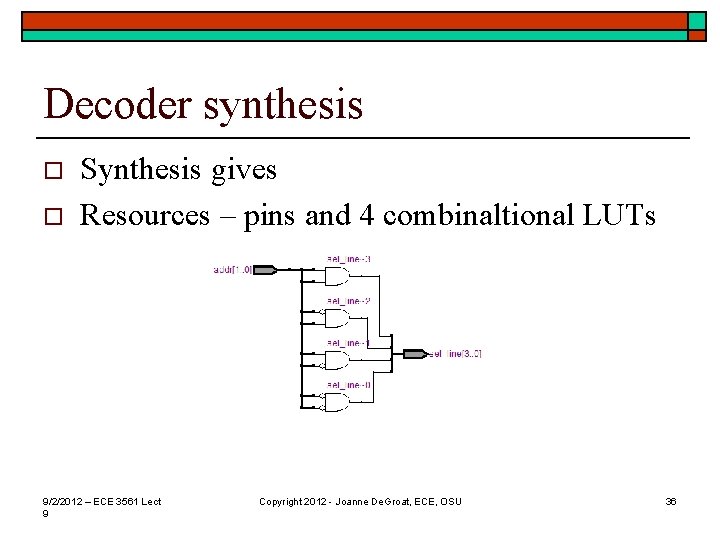

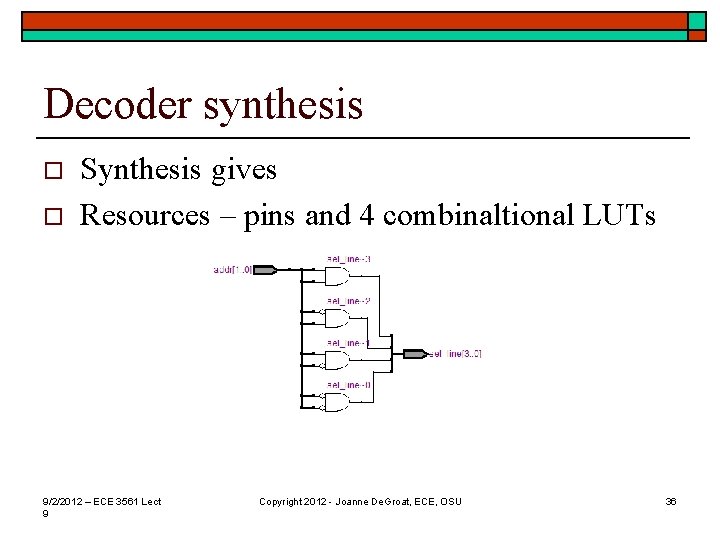

Decoder synthesis o o Synthesis gives Resources – pins and 4 combinaltional LUTs 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 36

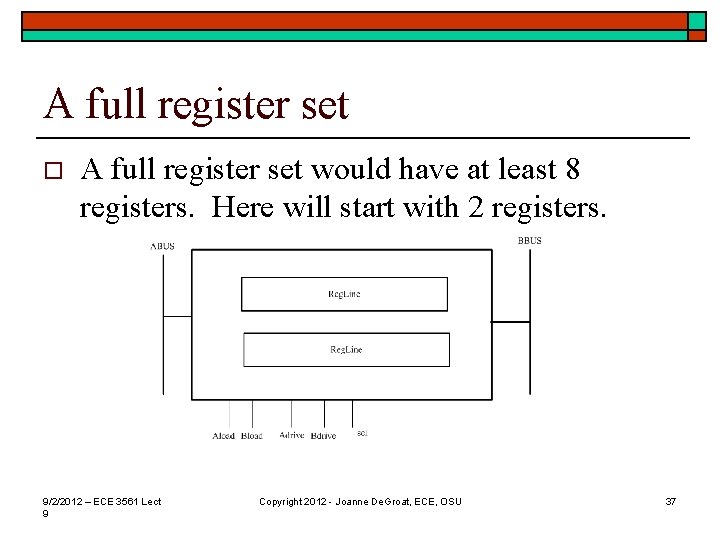

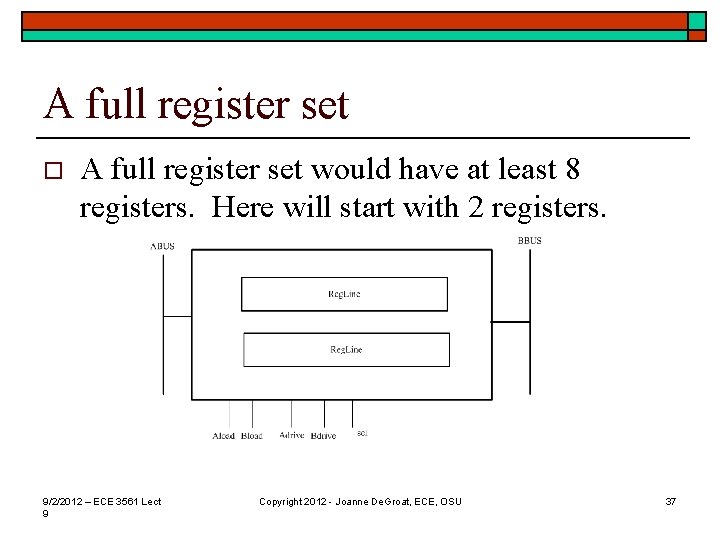

A full register set o A full register set would have at least 8 registers. Here will start with 2 registers. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 37

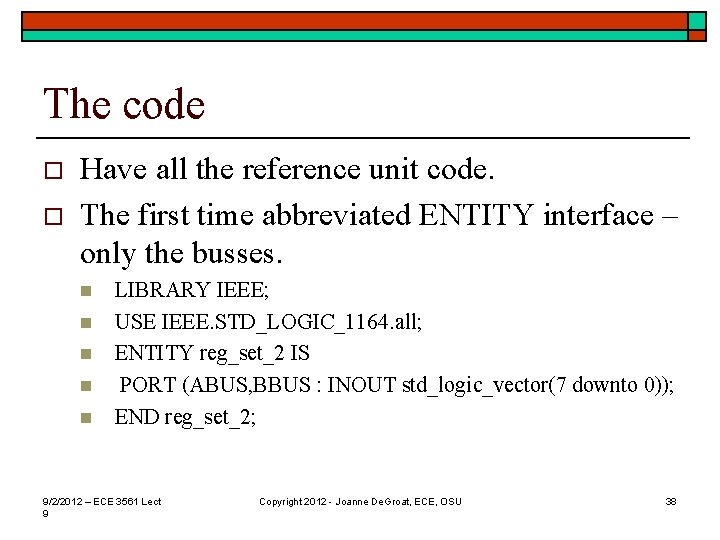

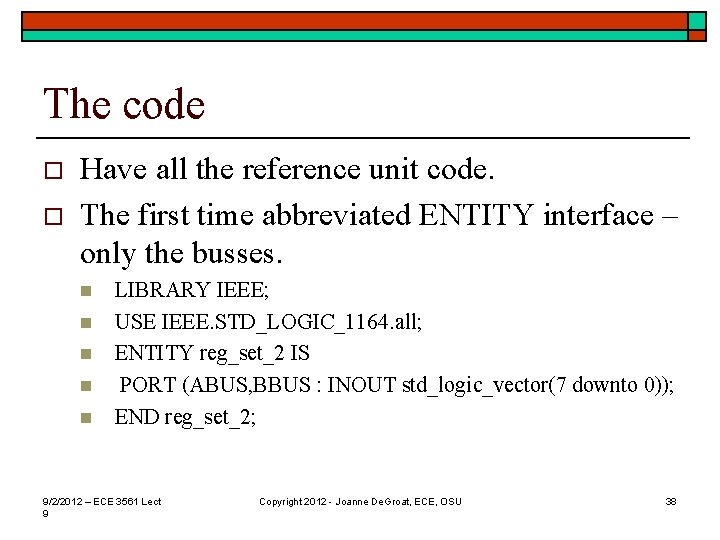

The code o o Have all the reference unit code. The first time abbreviated ENTITY interface – only the busses. n n n LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY reg_set_2 IS PORT (ABUS, BBUS : INOUT std_logic_vector(7 downto 0)); END reg_set_2; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 38

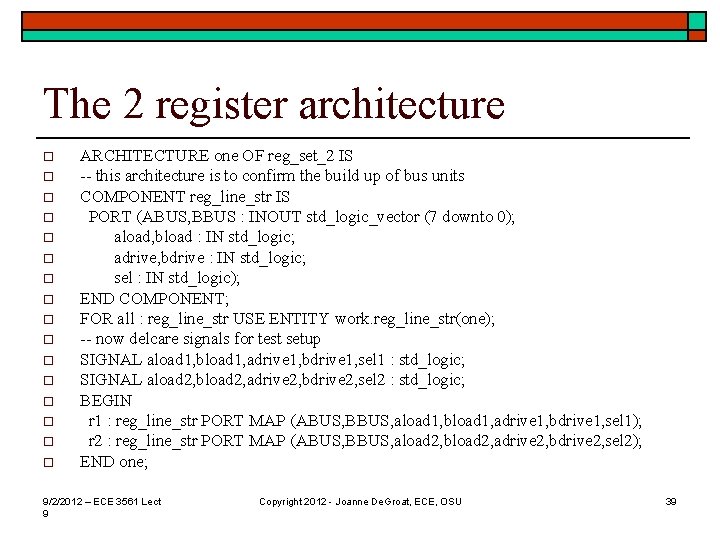

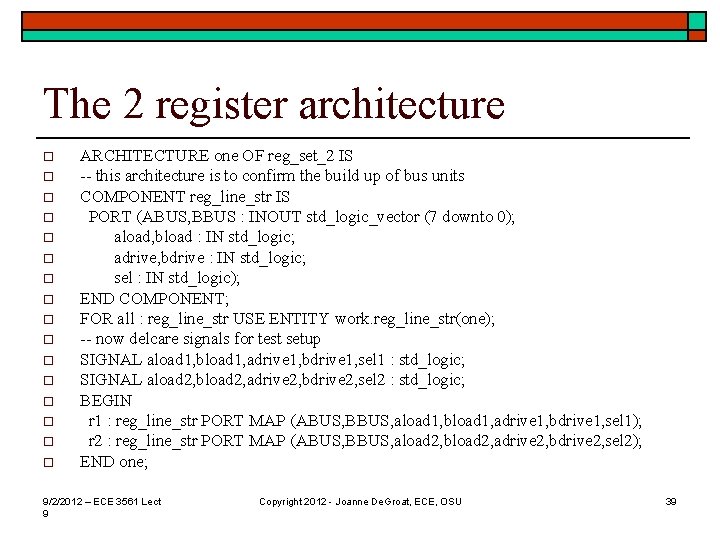

The 2 register architecture o o o o ARCHITECTURE one OF reg_set_2 IS -- this architecture is to confirm the build up of bus units COMPONENT reg_line_str IS PORT (ABUS, BBUS : INOUT std_logic_vector (7 downto 0); aload, bload : IN std_logic; adrive, bdrive : IN std_logic; sel : IN std_logic); END COMPONENT; FOR all : reg_line_str USE ENTITY work. reg_line_str(one); -- now delcare signals for test setup SIGNAL aload 1, bload 1, adrive 1, bdrive 1, sel 1 : std_logic; SIGNAL aload 2, bload 2, adrive 2, bdrive 2, sel 2 : std_logic; BEGIN r 1 : reg_line_str PORT MAP (ABUS, BBUS, aload 1, bload 1, adrive 1, bdrive 1, sel 1); r 2 : reg_line_str PORT MAP (ABUS, BBUS, aload 2, bload 2, adrive 2, bdrive 2, sel 2); END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 39

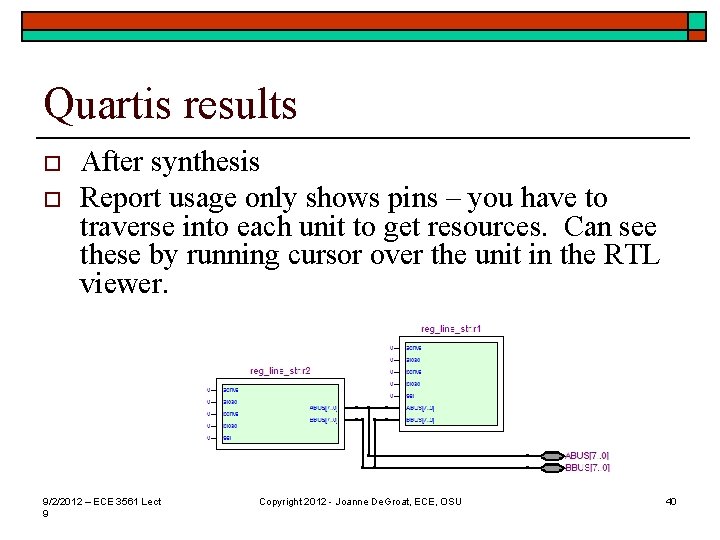

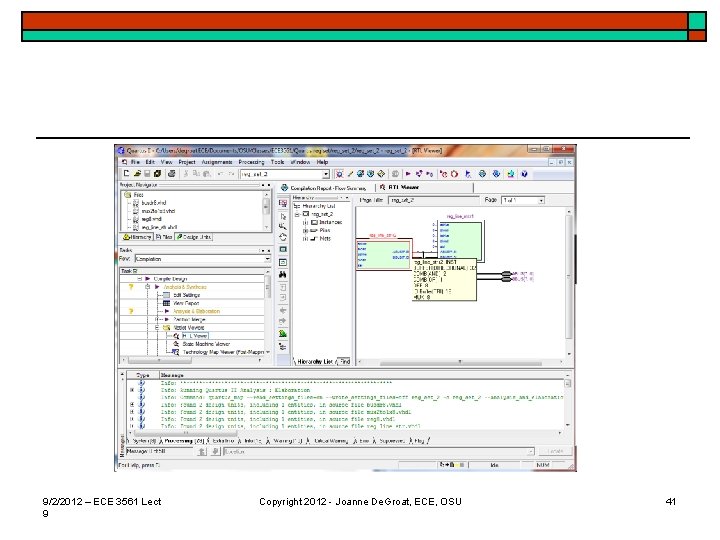

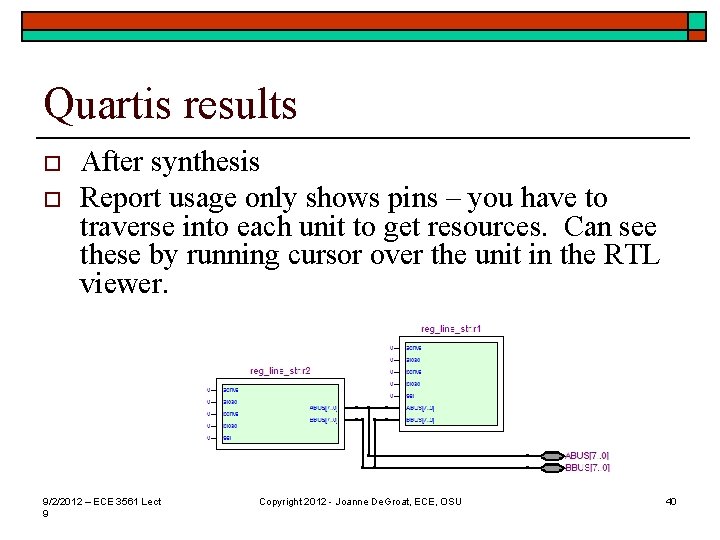

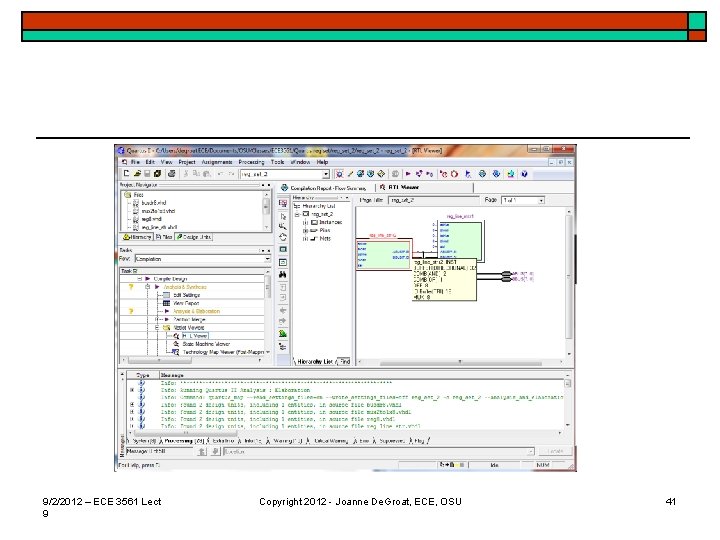

Quartis results o o After synthesis Report usage only shows pins – you have to traverse into each unit to get resources. Can see these by running cursor over the unit in the RTL viewer. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 40

9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 41

Usage summary by using cursor o For each register line n n n 32 buffers (regular) 2 combination ANDs 1 combination OR 8 DFF 16 Tri-state buffers 8 muxes 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 42

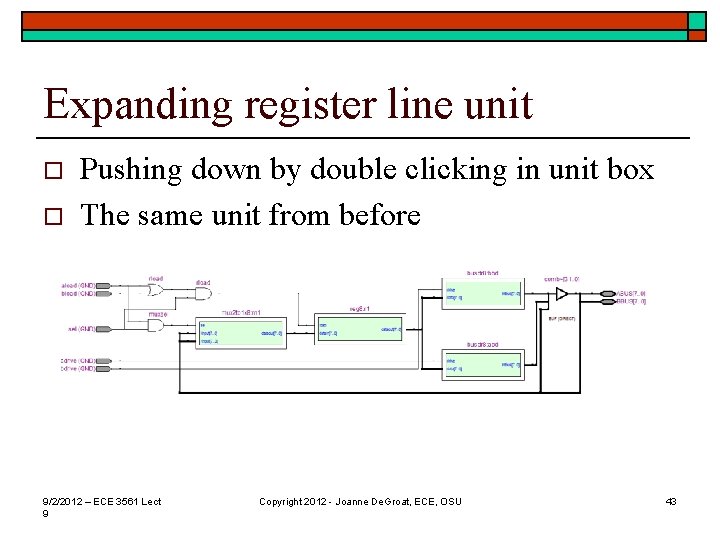

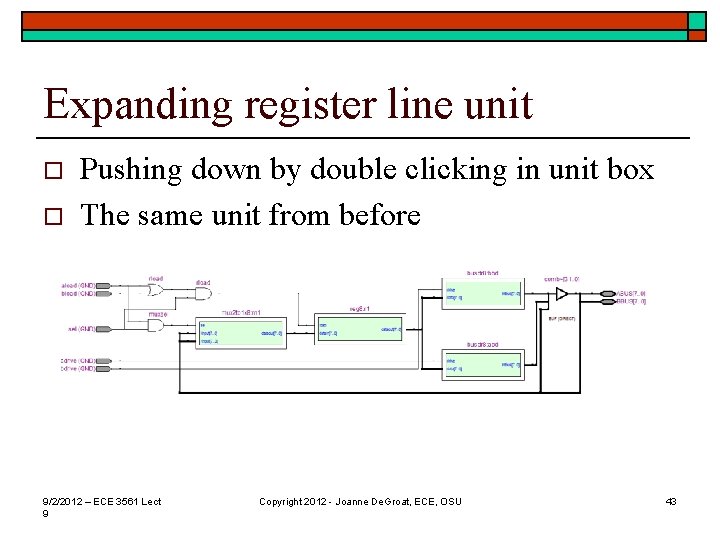

Expanding register line unit o o Pushing down by double clicking in unit box The same unit from before 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 43

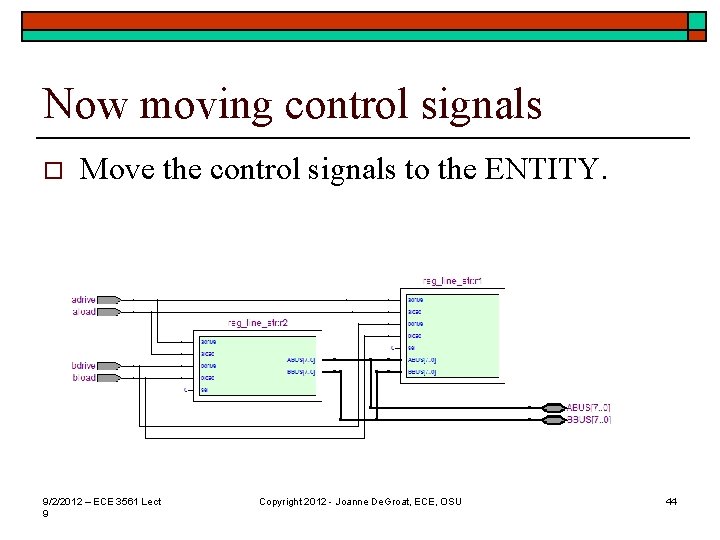

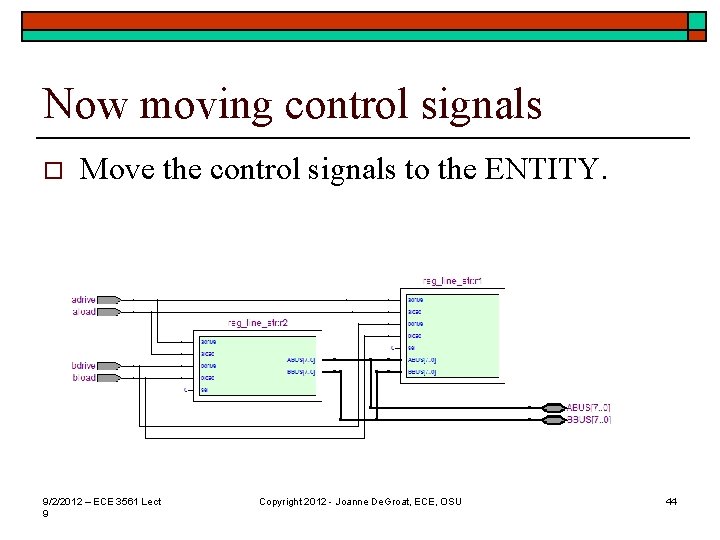

Now moving control signals o Move the control signals to the ENTITY. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 44

The last step o o o Adding a decoder to generate the selects This time a 1 -to-2 decoder Then a bunch of errors popped up so back up. n n Do the implementation one step at a time Add the regno signal to the ENTITY o n Add the decoder COMPONENT – re-synthesize o n WORKED FINE Add and instantiation for the decoder o n WORKED FINE Finally link the decoder output to the select lines with concurrent signal assignment statements. It then started generating errors so starting a new approach. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 45

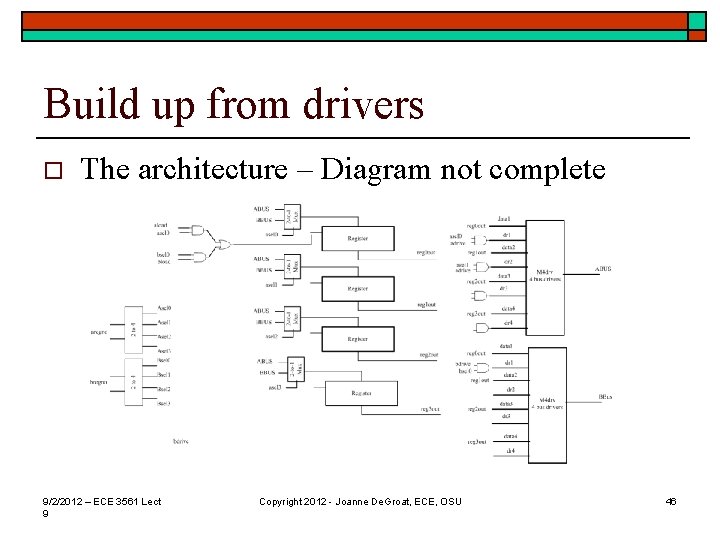

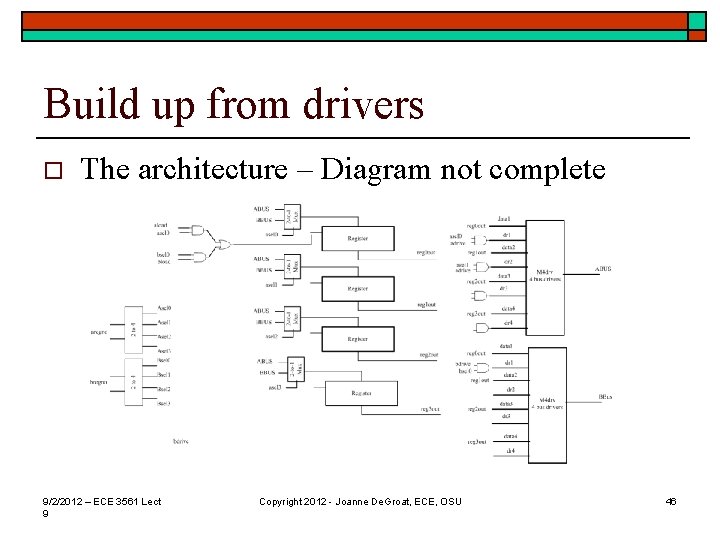

Build up from drivers o The architecture – Diagram not complete 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 46

The units o The tri-state bus drivers n o The registers n o o o 4 of them 8 -bits each in a hierarchical unit 4 of them as instantiated units Mux 2 to 1 x 8 – a byte width 2 to 1 multiplexer used to select which input to have available to load into register, the ABUS or the BBUS Decoders 2 to 4 – takes the 2 bit register number and generates the correct select line – used for selecting which register to load from the ABUS or BBUS and which register to drive. Note that the system can drive just register. It is capable of two operations each cycle. Glue logic – generated the load and drive signals. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 47

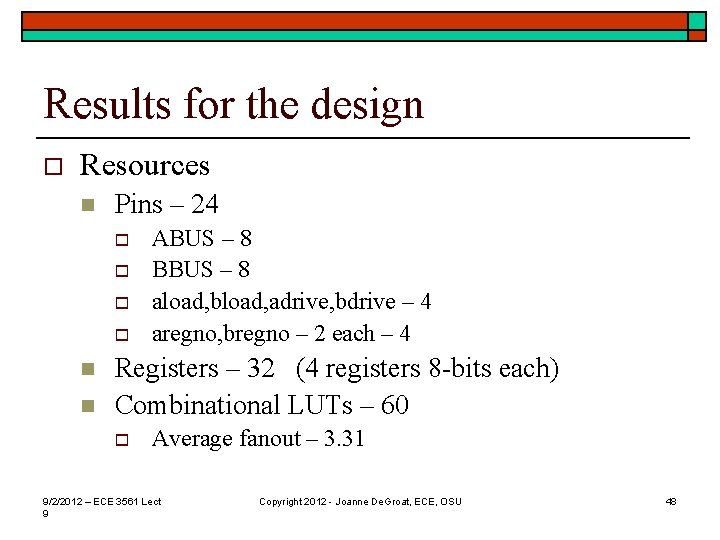

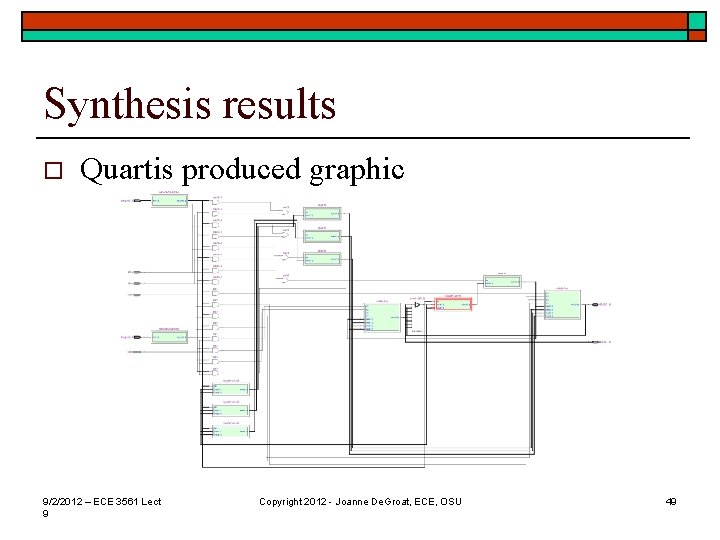

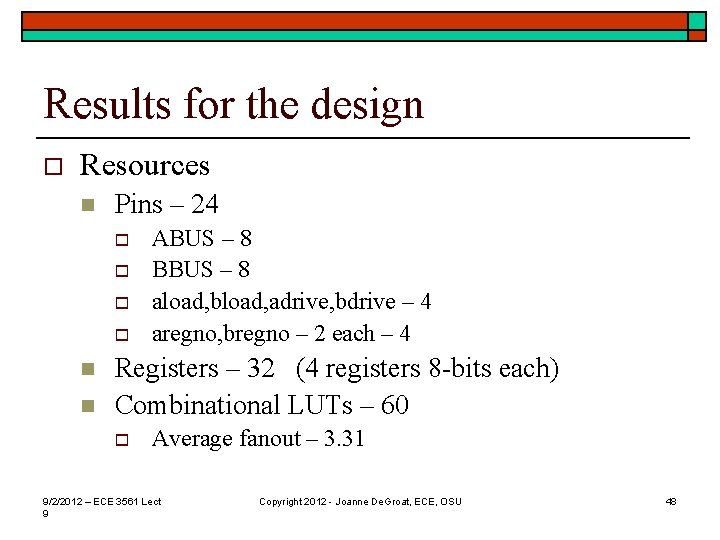

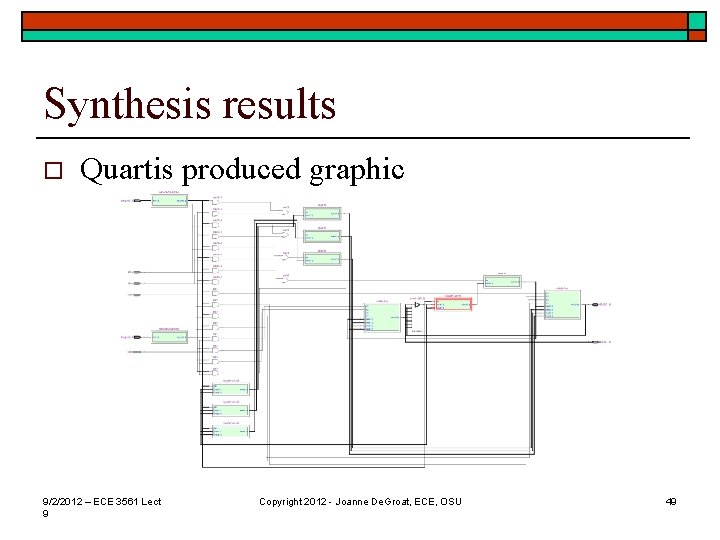

Results for the design o Resources n Pins – 24 o o n n ABUS – 8 BBUS – 8 aload, bload, adrive, bdrive – 4 aregno, bregno – 2 each – 4 Registers – 32 (4 registers 8 -bits each) Combinational LUTs – 60 o Average fanout – 3. 31 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 48

Synthesis results o Quartis produced graphic 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 49

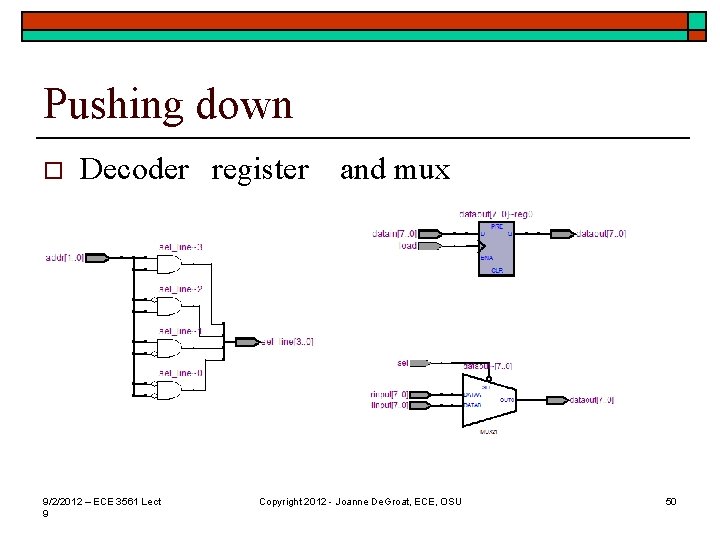

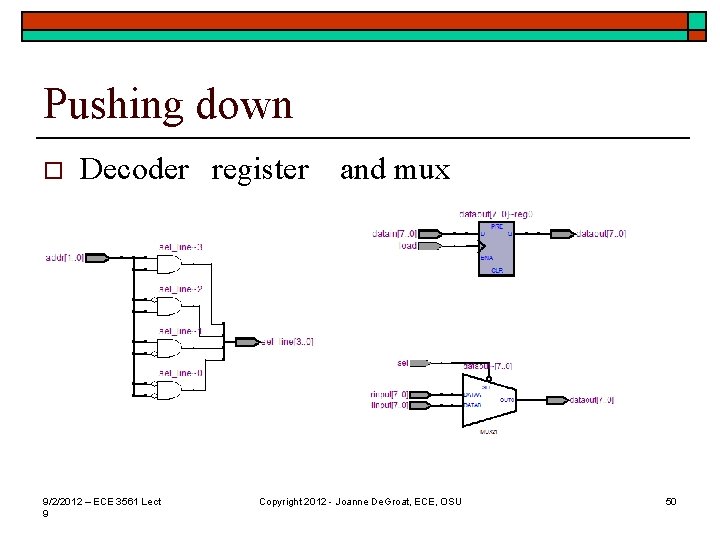

Pushing down o Decoder register and mux 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 50

Next step o The next step is the VHDL simulation of the register set to be sure its behavior is as desired. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 51

Lecture summary o Have seen how to create a 4 register location register-set. o The next assignment is to use the code here (which is also on the web page) to generate a 8 location register. Simply build upon this code. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 52