L 19 Resolved Signals Resolved Signals o What

- Slides: 38

L 19 – Resolved Signals

Resolved Signals o What are resolved signals n n n o In systems In VHDL Resolution – Isn’t that for resolving conflicts? Ref: text Unit 10, 17, 20 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

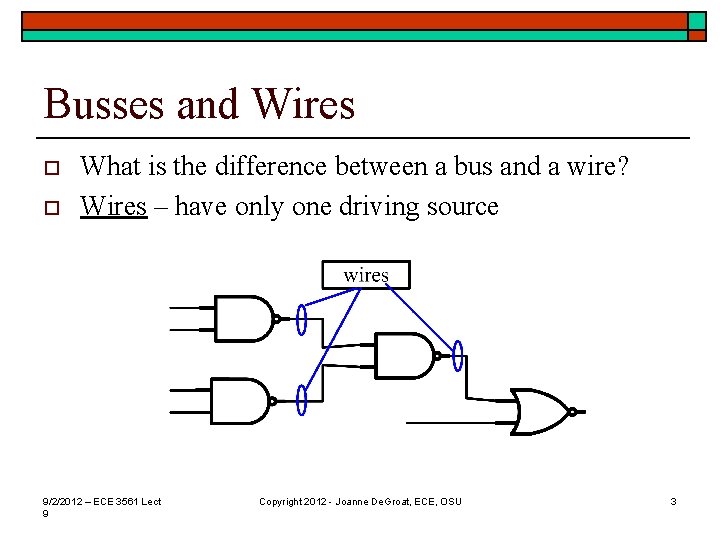

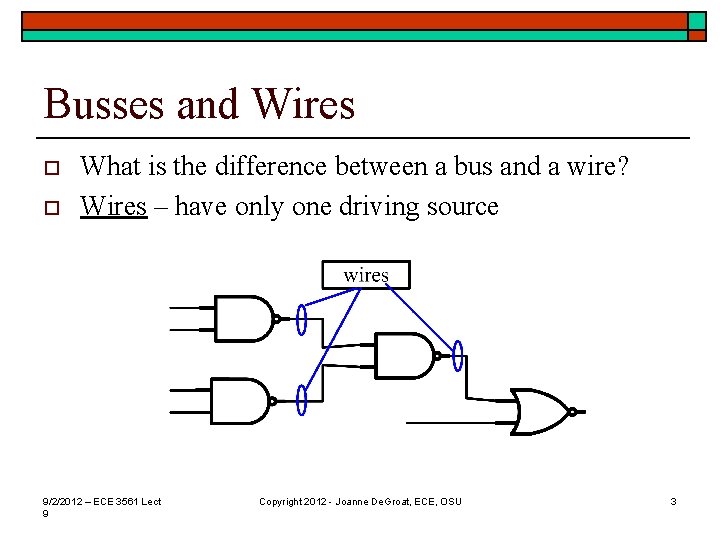

Busses and Wires o o What is the difference between a bus and a wire? Wires – have only one driving source 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 3

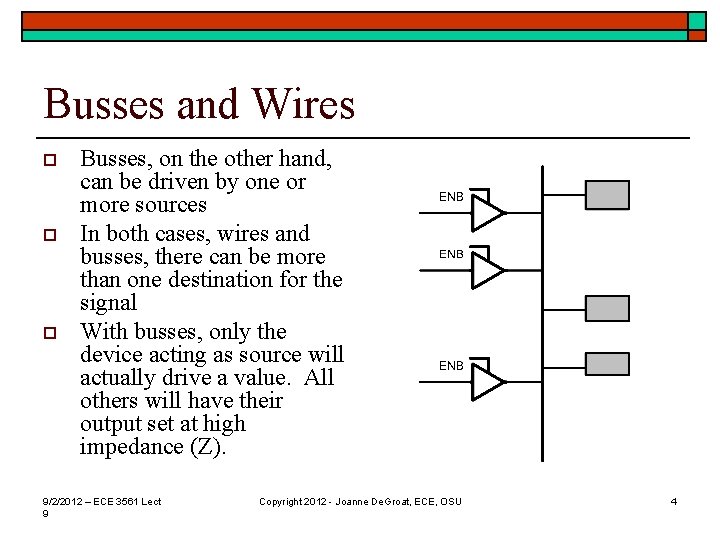

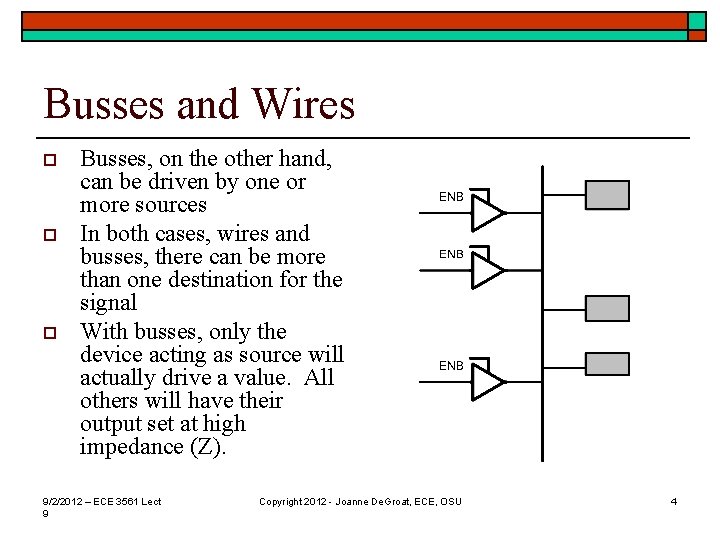

Busses and Wires o o o Busses, on the other hand, can be driven by one or more sources In both cases, wires and busses, there can be more than one destination for the signal With busses, only the device acting as source will actually drive a value. All others will have their output set at high impedance (Z). 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 4

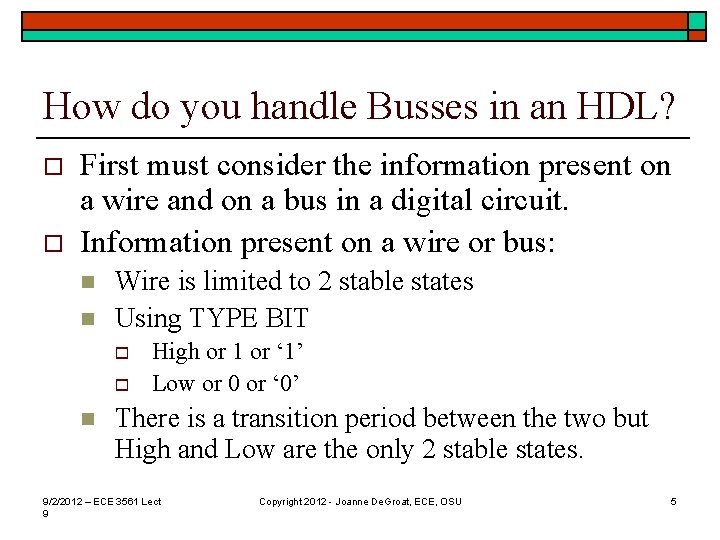

How do you handle Busses in an HDL? o o First must consider the information present on a wire and on a bus in a digital circuit. Information present on a wire or bus: n n Wire is limited to 2 stable states Using TYPE BIT o o n High or 1 or ‘ 1’ Low or 0 or ‘ 0’ There is a transition period between the two but High and Low are the only 2 stable states. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 5

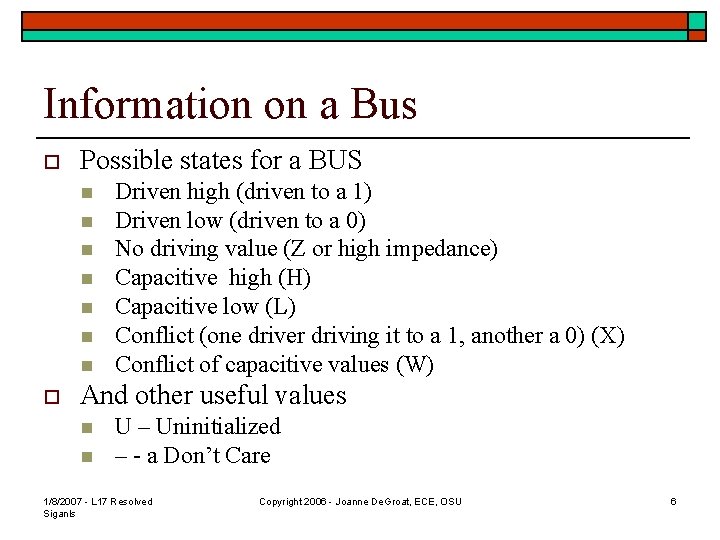

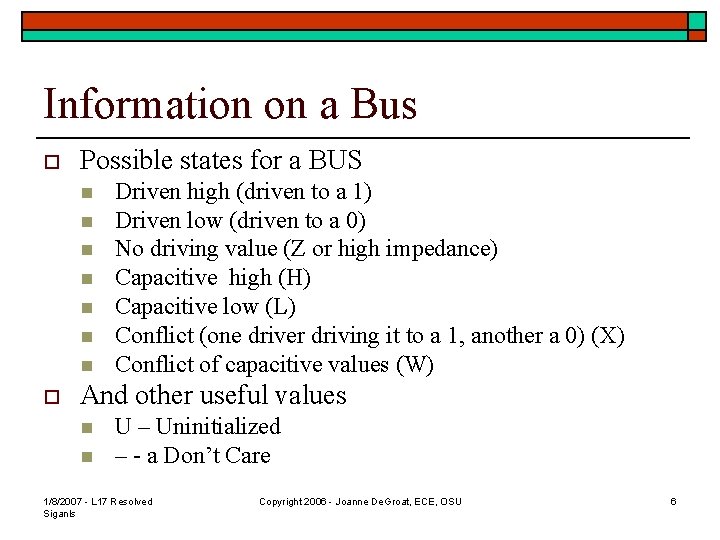

Information on a Bus o Possible states for a BUS n n n n o Driven high (driven to a 1) Driven low (driven to a 0) No driving value (Z or high impedance) Capacitive high (H) Capacitive low (L) Conflict (one driver driving it to a 1, another a 0) (X) Conflict of capacitive values (W) And other useful values n n U – Uninitialized – - a Don’t Care 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 6

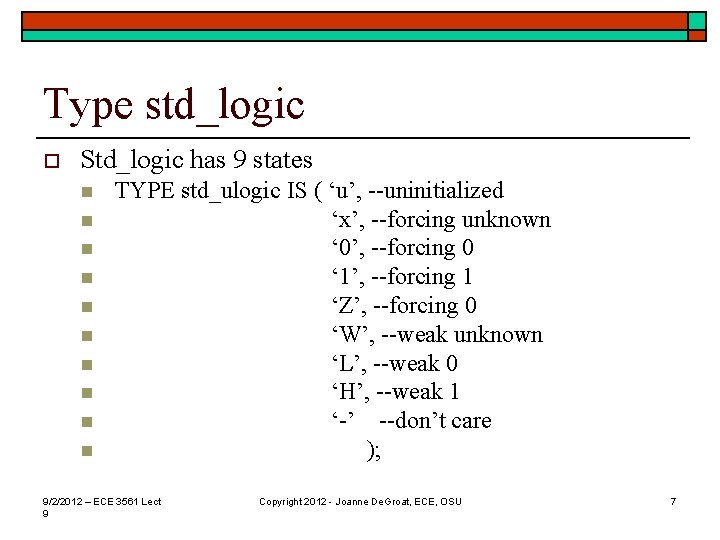

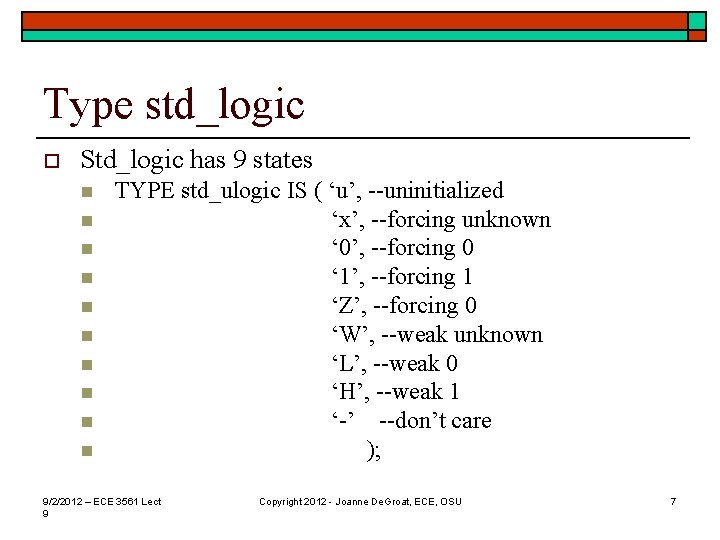

Type std_logic o Std_logic has 9 states n n n n n TYPE std_ulogic IS ( ‘u’, --uninitialized ‘x’, --forcing unknown ‘ 0’, --forcing 0 ‘ 1’, --forcing 1 ‘Z’, --forcing 0 ‘W’, --weak unknown ‘L’, --weak 0 ‘H’, --weak 1 ‘-’ --don’t care ); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 7

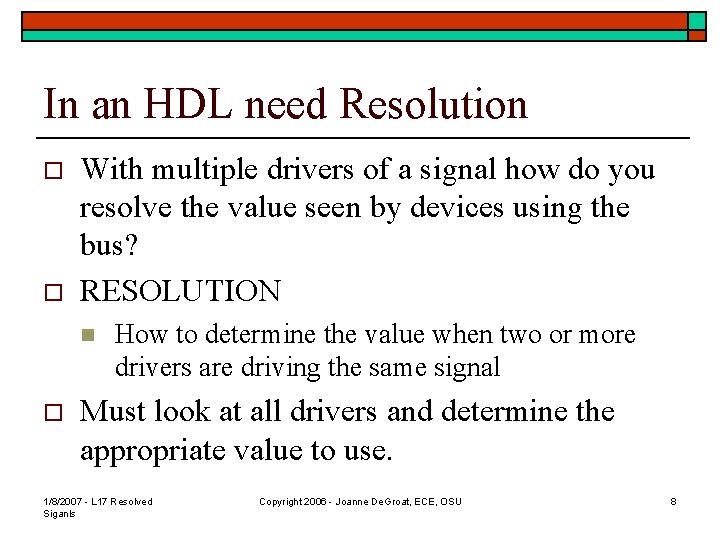

In an HDL need Resolution o o With multiple drivers of a signal how do you resolve the value seen by devices using the bus? RESOLUTION n o How to determine the value when two or more drivers are driving the same signal Must look at all drivers and determine the appropriate value to use. 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 8

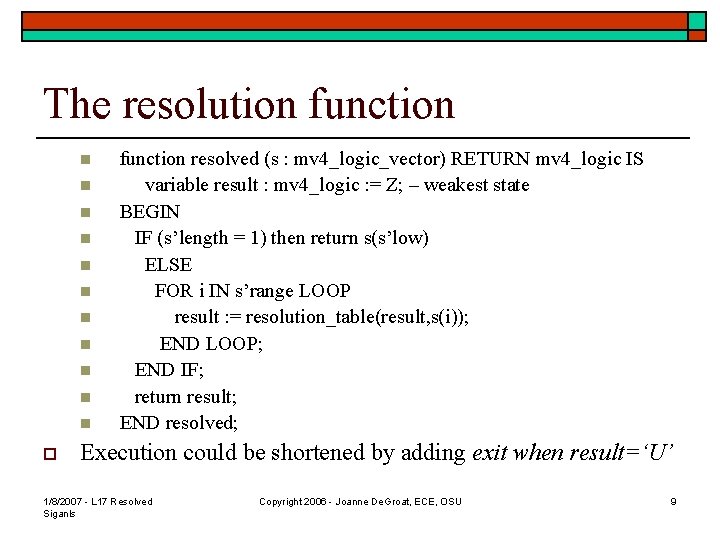

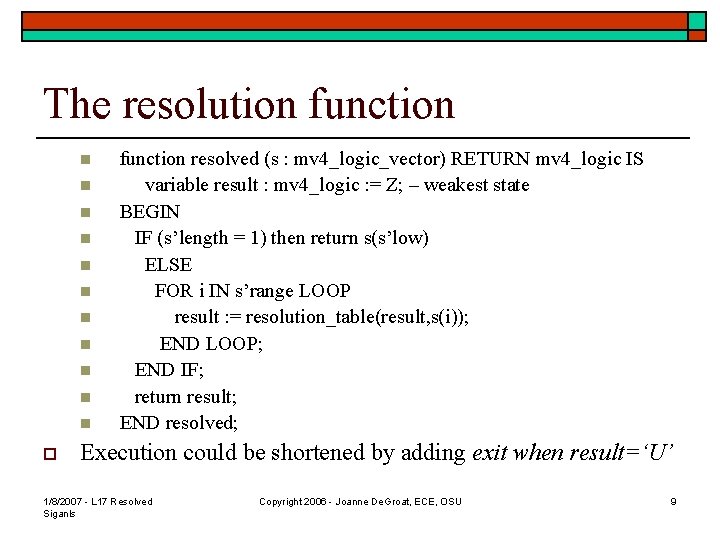

The resolution function n n o function resolved (s : mv 4_logic_vector) RETURN mv 4_logic IS variable result : mv 4_logic : = Z; – weakest state BEGIN IF (s’length = 1) then return s(s’low) ELSE FOR i IN s’range LOOP result : = resolution_table(result, s(i)); END LOOP; END IF; return result; END resolved; Execution could be shortened by adding exit when result=‘U’ 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 9

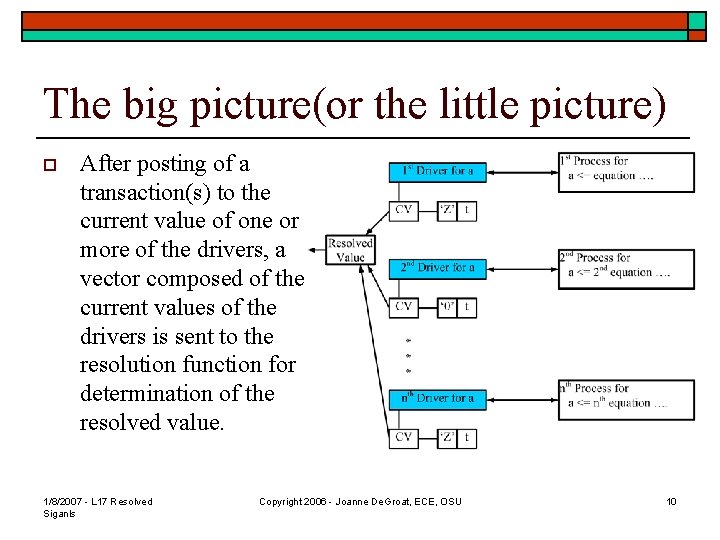

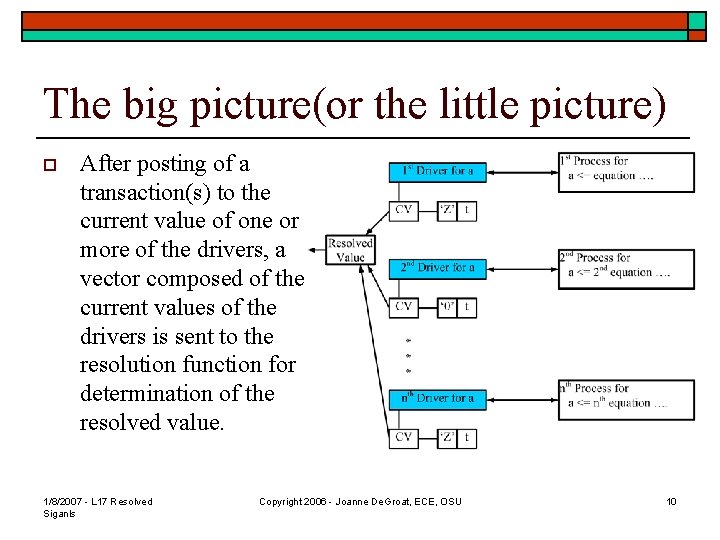

The big picture(or the little picture) o After posting of a transaction(s) to the current value of one or more of the drivers, a vector composed of the current values of the drivers is sent to the resolution function for determination of the resolved value. 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 10

Completeness of a MVL package o o Having a MVL type with resolution is only part of creating a MVL system. ALSO need n n o Overloaded function for standard operators Type conversion functions to convert from other type to this type and the reverse ieee_1164 standard MVL package is a standard package for a multi-value logic system and contains all of these. 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 11

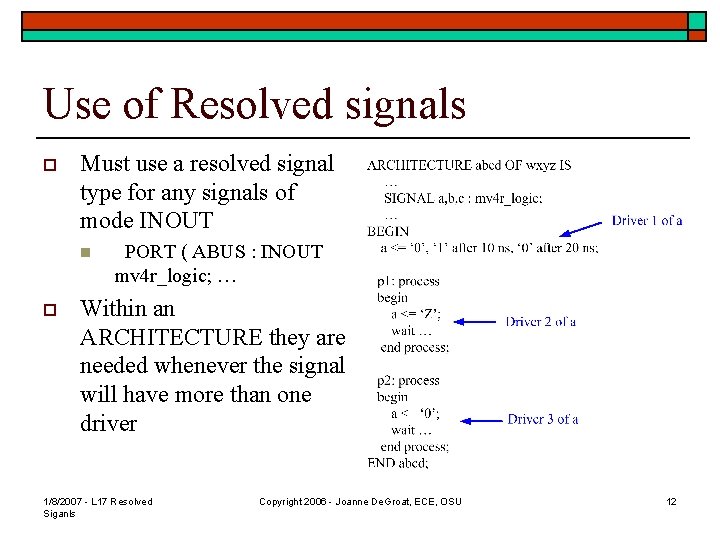

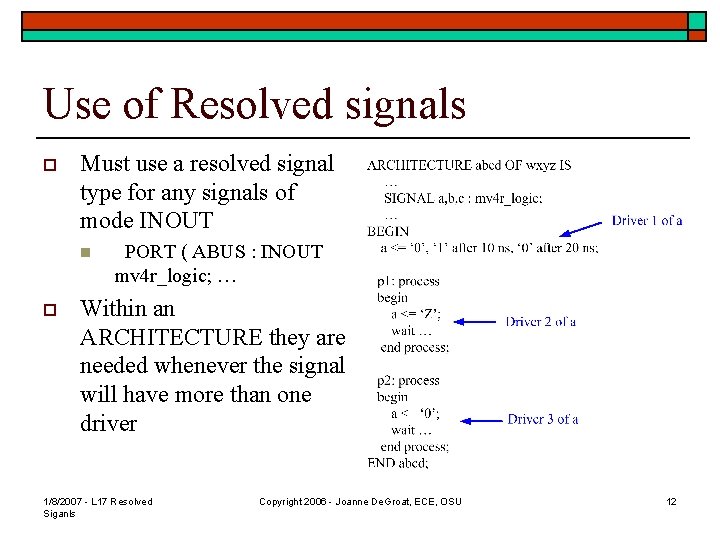

Use of Resolved signals o Must use a resolved signal type for any signals of mode INOUT n o PORT ( ABUS : INOUT mv 4 r_logic; … Within an ARCHITECTURE they are needed whenever the signal will have more than one driver 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 12

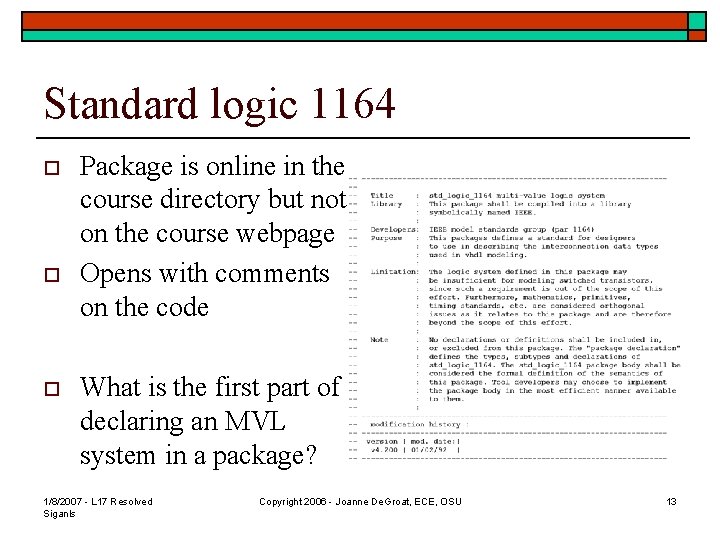

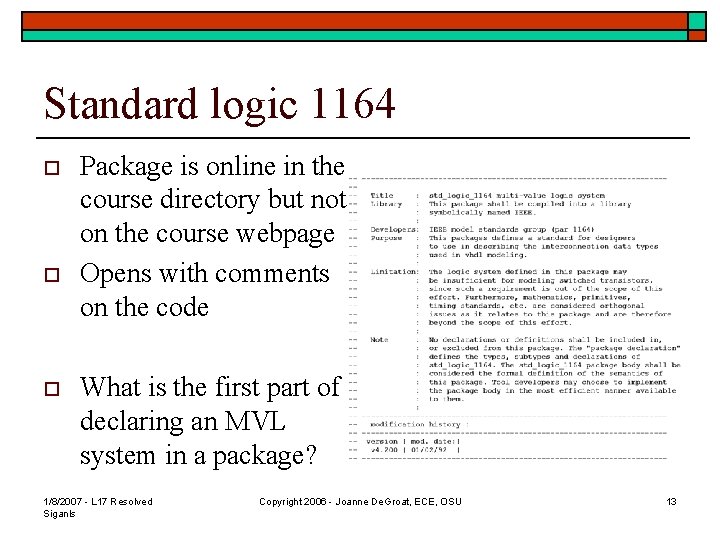

Standard logic 1164 o o o Package is online in the course directory but not on the course webpage Opens with comments on the code What is the first part of declaring an MVL system in a package? 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 13

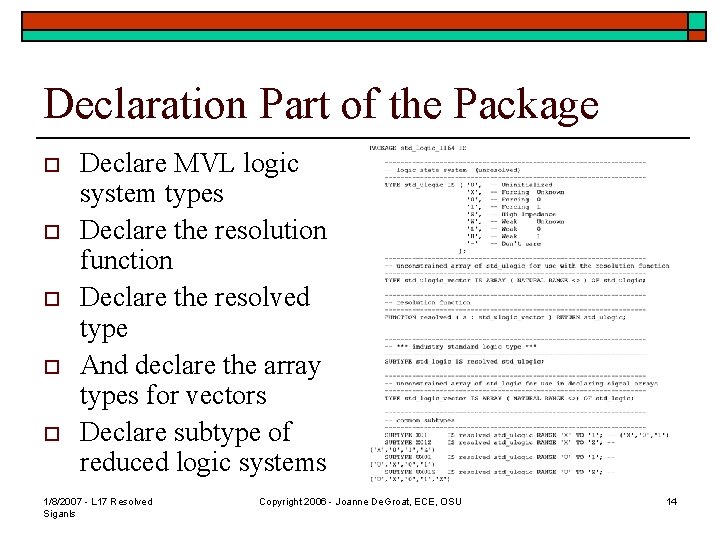

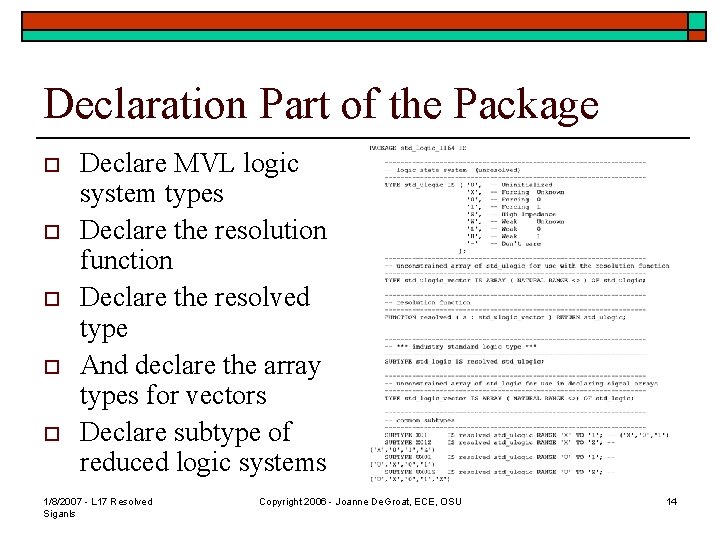

Declaration Part of the Package o o o Declare MVL logic system types Declare the resolution function Declare the resolved type And declare the array types for vectors Declare subtype of reduced logic systems 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 14

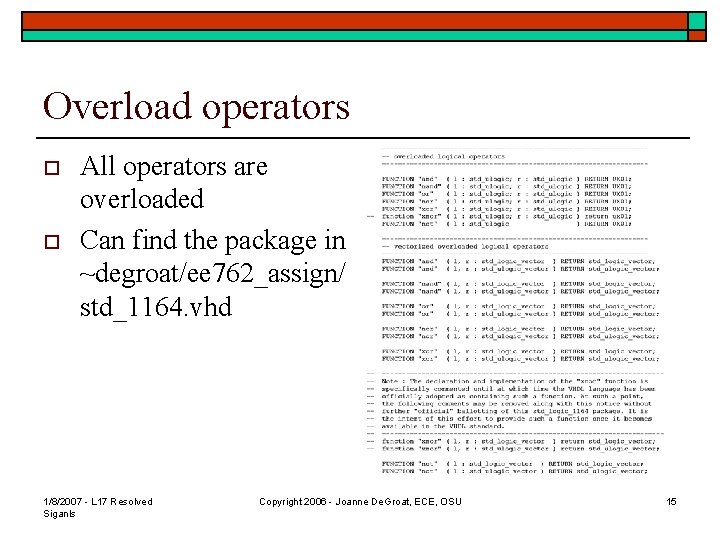

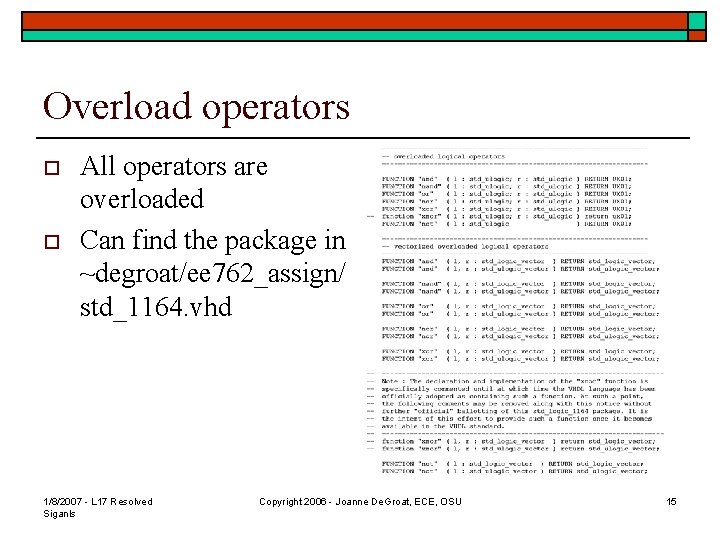

Overload operators o o All operators are overloaded Can find the package in ~degroat/ee 762_assign/ std_1164. vhd 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 15

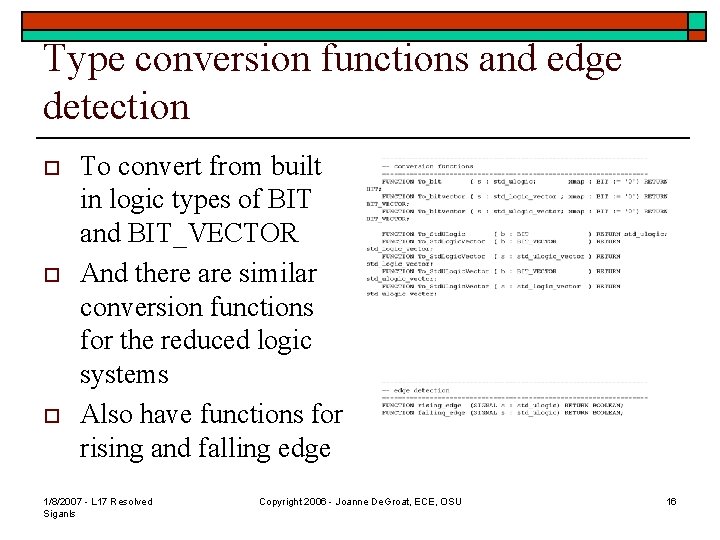

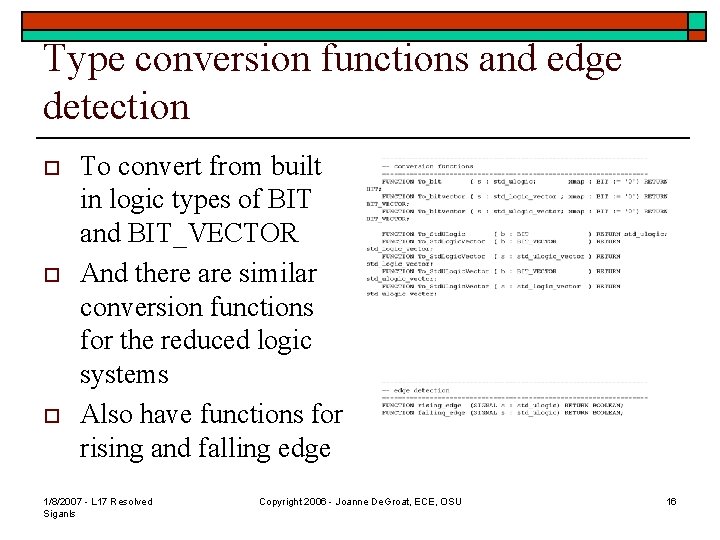

Type conversion functions and edge detection o o o To convert from built in logic types of BIT and BIT_VECTOR And there are similar conversion functions for the reduced logic systems Also have functions for rising and falling edge 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 16

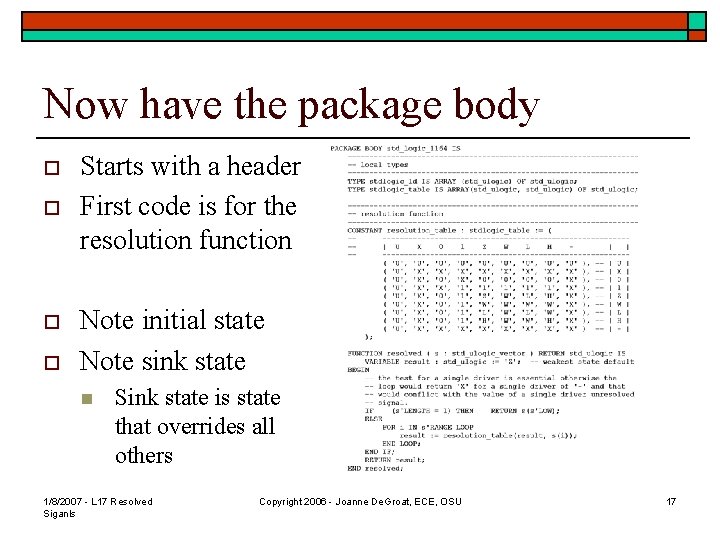

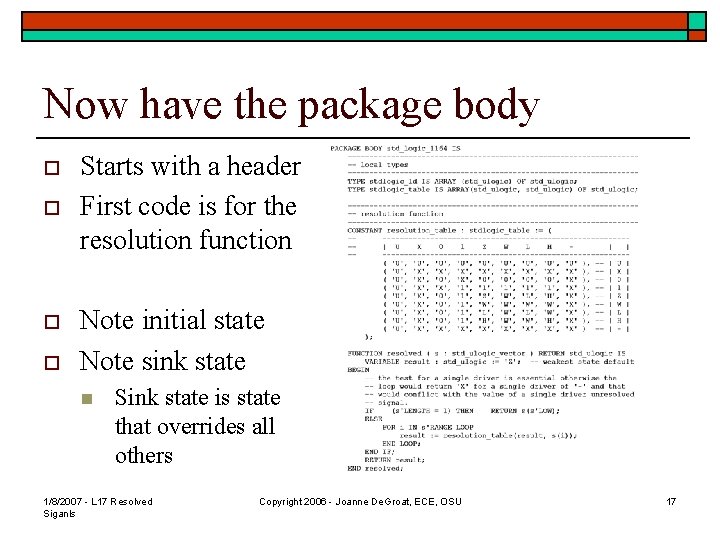

Now have the package body o o Starts with a header First code is for the resolution function Note initial state Note sink state n Sink state is state that overrides all others 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 17

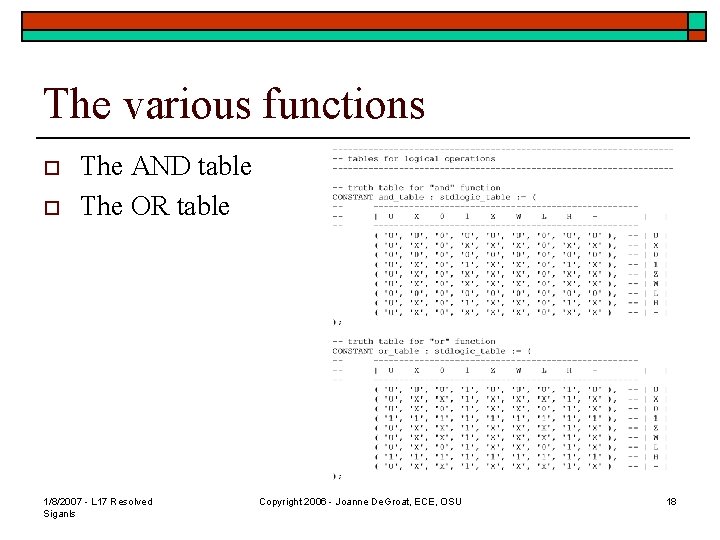

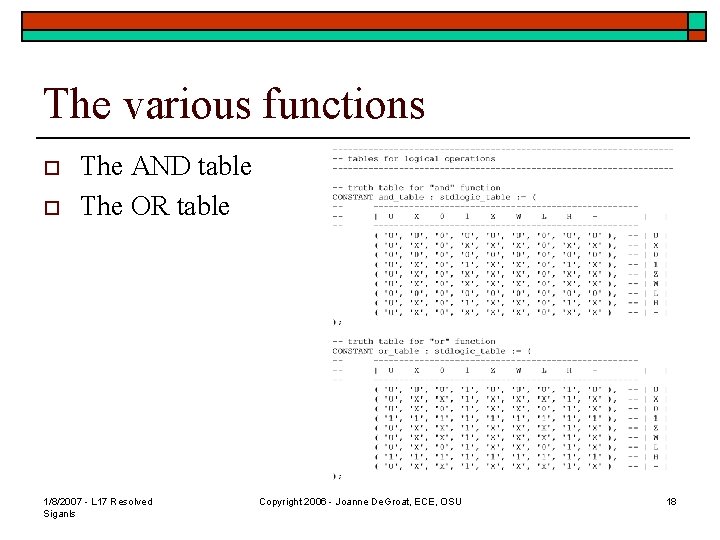

The various functions o o The AND table The OR table 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 18

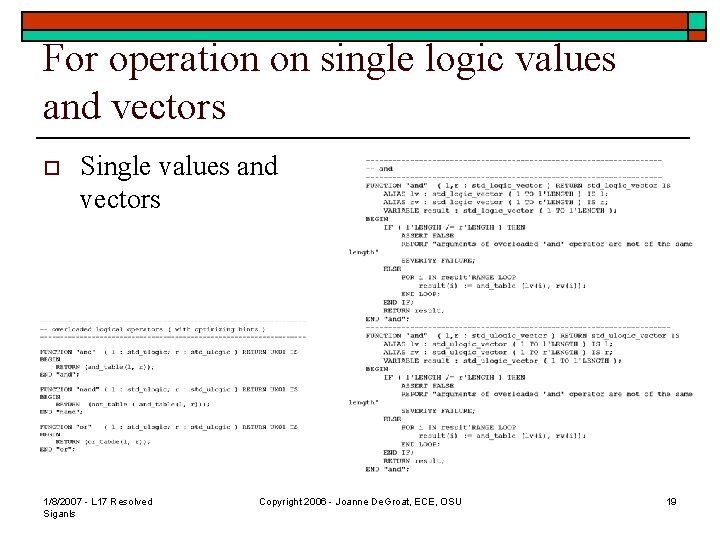

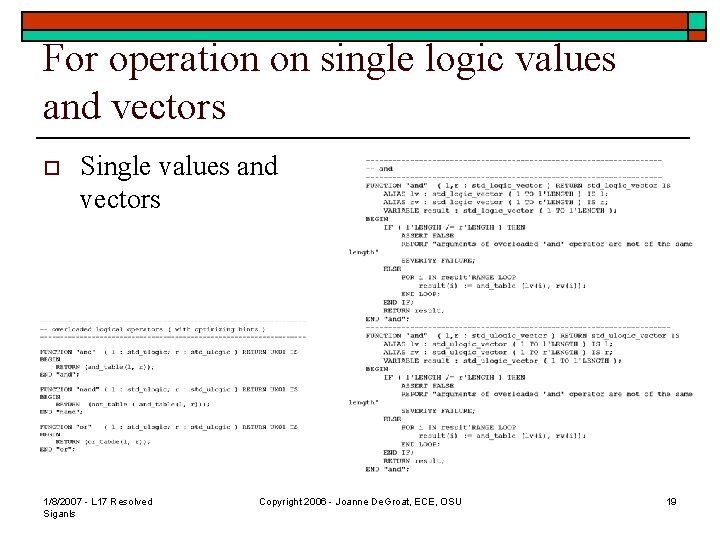

For operation on single logic values and vectors o Single values and vectors 1/8/2007 - L 17 Resolved Siganls Copyright 2006 - Joanne De. Groat, ECE, OSU 19

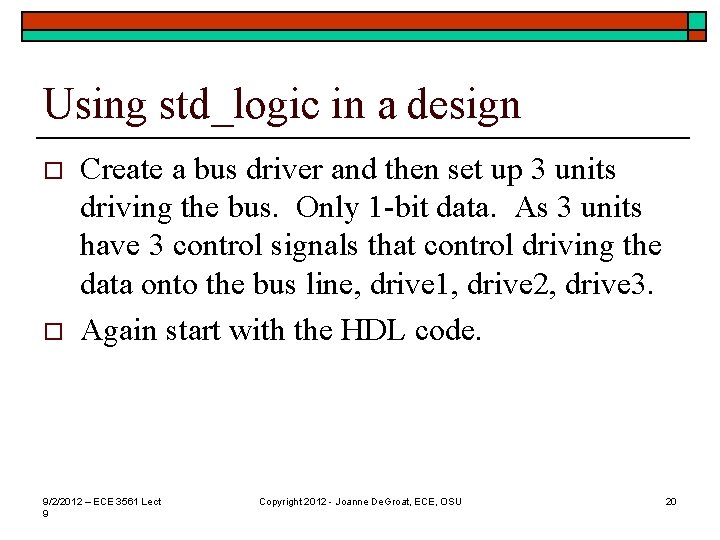

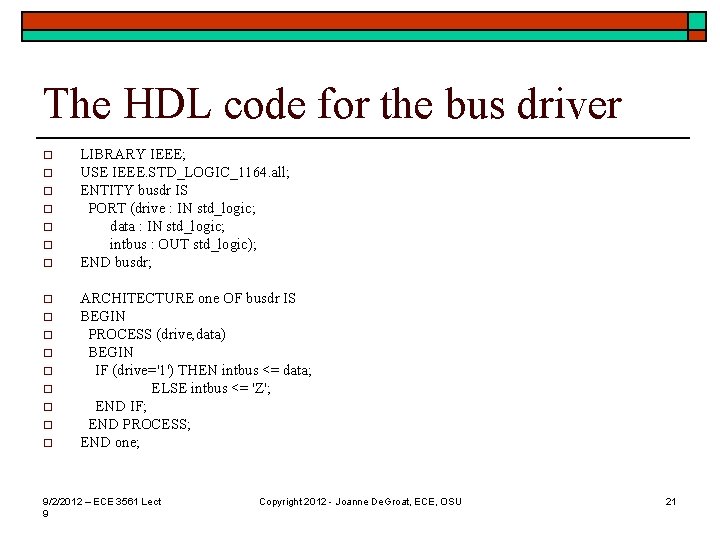

Using std_logic in a design o o Create a bus driver and then set up 3 units driving the bus. Only 1 -bit data. As 3 units have 3 control signals that control driving the data onto the bus line, drive 1, drive 2, drive 3. Again start with the HDL code. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 20

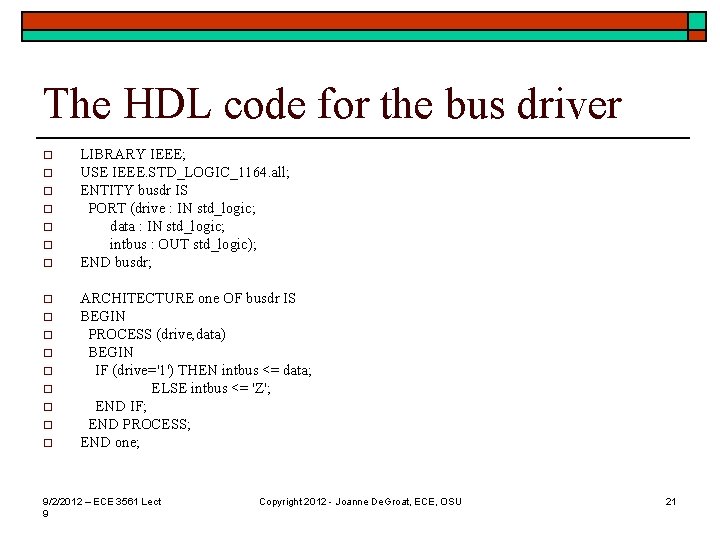

The HDL code for the bus driver o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY busdr IS PORT (drive : IN std_logic; data : IN std_logic; intbus : OUT std_logic); END busdr; ARCHITECTURE one OF busdr IS BEGIN PROCESS (drive, data) BEGIN IF (drive='1') THEN intbus <= data; ELSE intbus <= 'Z'; END IF; END PROCESS; END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 21

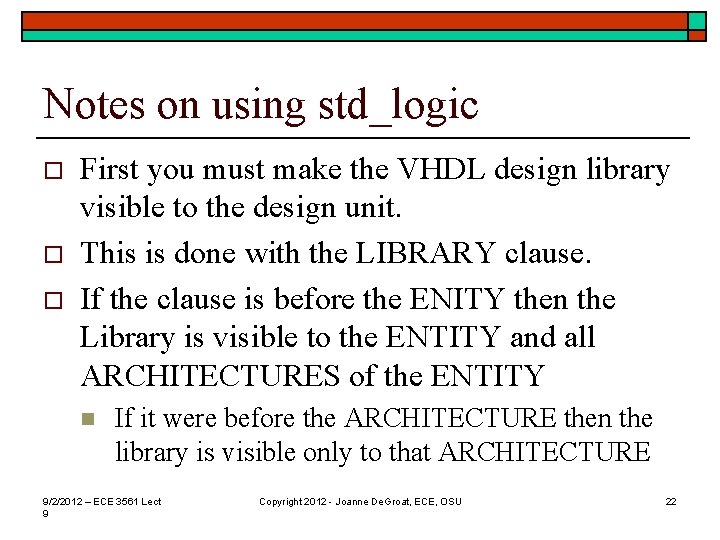

Notes on using std_logic o o o First you must make the VHDL design library visible to the design unit. This is done with the LIBRARY clause. If the clause is before the ENITY then the Library is visible to the ENTITY and all ARCHITECTURES of the ENTITY n If it were before the ARCHITECTURE then the library is visible only to that ARCHITECTURE 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 22

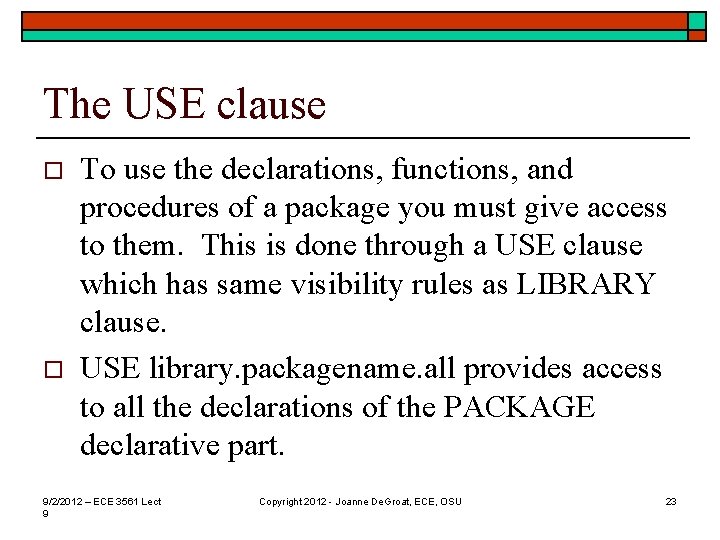

The USE clause o o To use the declarations, functions, and procedures of a package you must give access to them. This is done through a USE clause which has same visibility rules as LIBRARY clause. USE library. packagename. all provides access to all the declarations of the PACKAGE declarative part. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 23

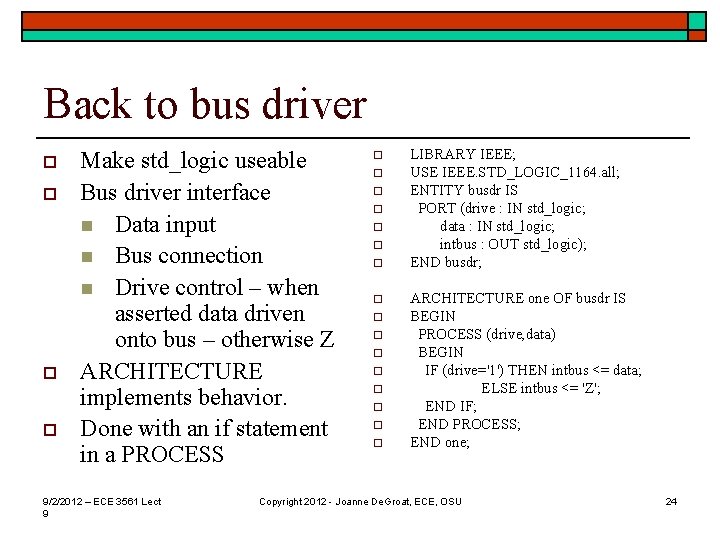

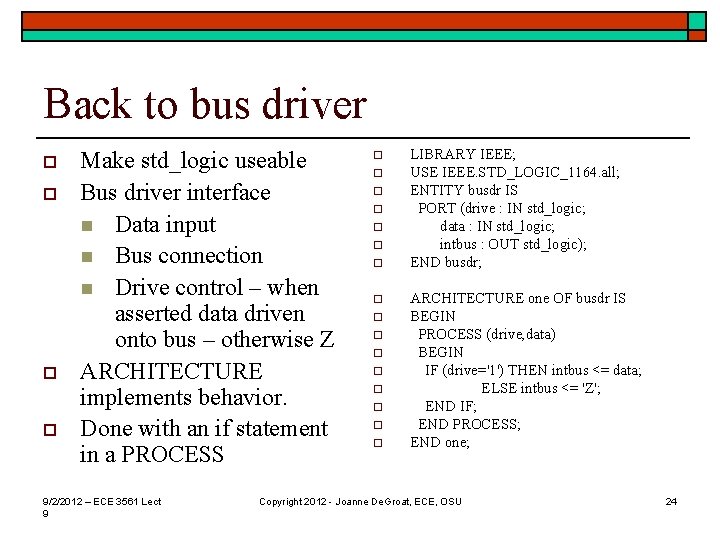

Back to bus driver o o Make std_logic useable Bus driver interface n Data input n Bus connection n Drive control – when asserted data driven onto bus – otherwise Z ARCHITECTURE implements behavior. Done with an if statement in a PROCESS 9/2/2012 – ECE 3561 Lect 9 o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY busdr IS PORT (drive : IN std_logic; data : IN std_logic; intbus : OUT std_logic); END busdr; ARCHITECTURE one OF busdr IS BEGIN PROCESS (drive, data) BEGIN IF (drive='1') THEN intbus <= data; ELSE intbus <= 'Z'; END IF; END PROCESS; END one; Copyright 2012 - Joanne De. Groat, ECE, OSU 24

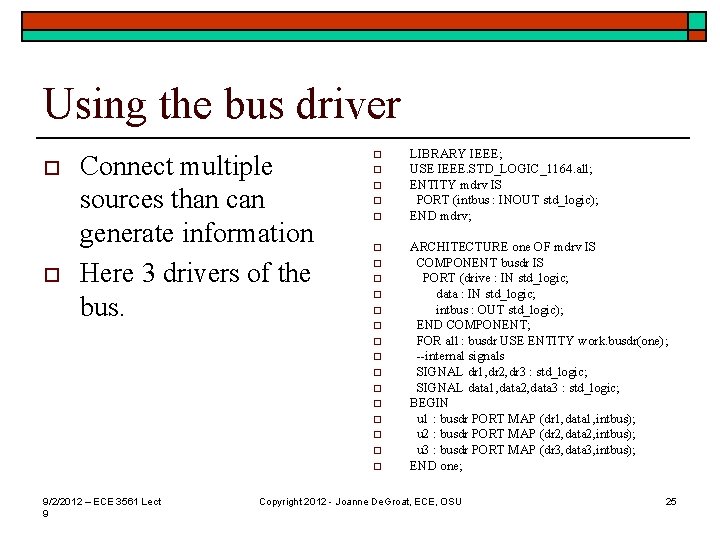

Using the bus driver o o Connect multiple sources than can generate information Here 3 drivers of the bus. o o o o o 9/2/2012 – ECE 3561 Lect 9 LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY mdrv IS PORT (intbus : INOUT std_logic); END mdrv; ARCHITECTURE one OF mdrv IS COMPONENT busdr IS PORT (drive : IN std_logic; data : IN std_logic; intbus : OUT std_logic); END COMPONENT; FOR all : busdr USE ENTITY work. busdr(one); --internal signals SIGNAL dr 1, dr 2, dr 3 : std_logic; SIGNAL data 1, data 2, data 3 : std_logic; BEGIN u 1 : busdr PORT MAP (dr 1, data 1, intbus); u 2 : busdr PORT MAP (dr 2, data 2, intbus); u 3 : busdr PORT MAP (dr 3, data 3, intbus); END one; Copyright 2012 - Joanne De. Groat, ECE, OSU 25

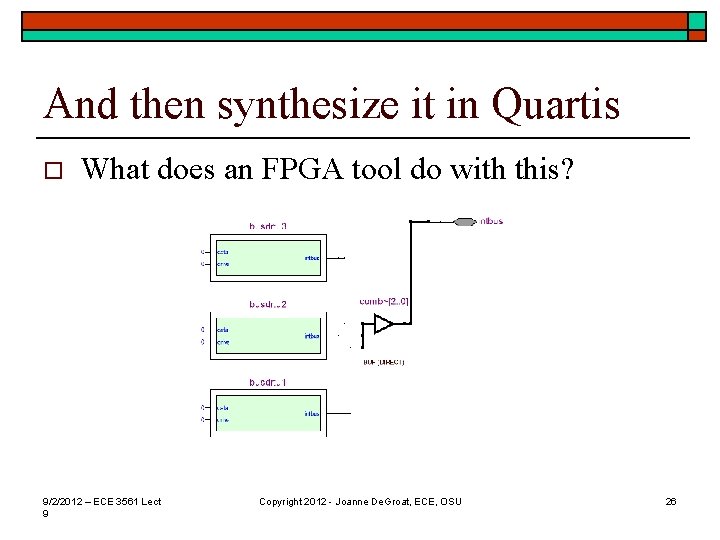

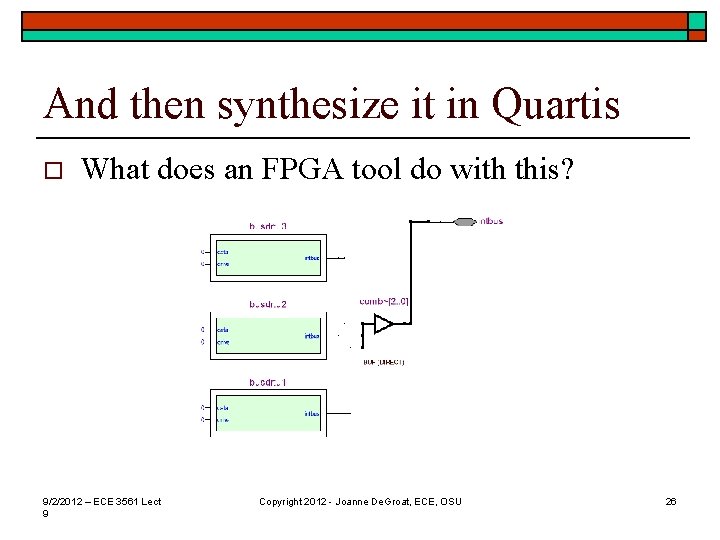

And then synthesize it in Quartis o What does an FPGA tool do with this? 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 26

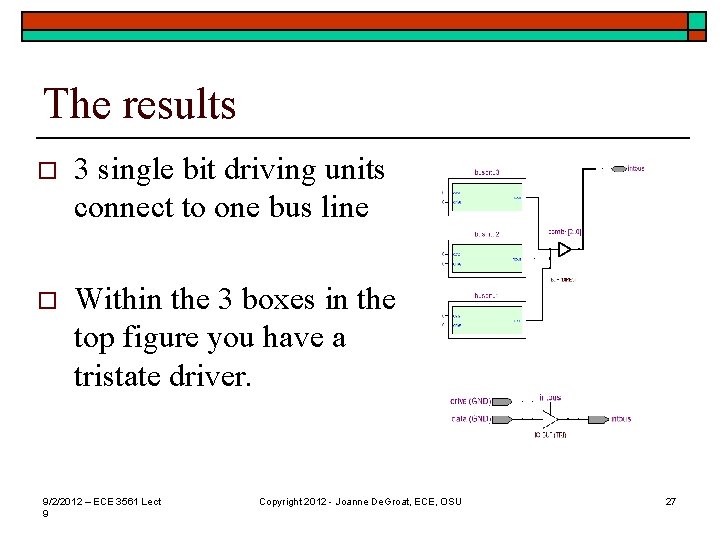

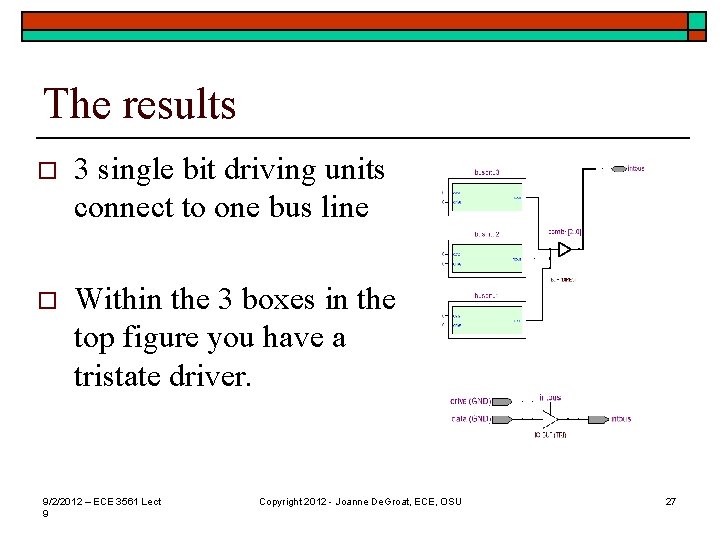

The results o 3 single bit driving units connect to one bus line o Within the 3 boxes in the top figure you have a tristate driver. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 27

Keys to having Quartis work o o o Project has name pnm Top level VHDL file is pnm. vhdl In the VHDL code it is “ENTITY pnm IS …” 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 28

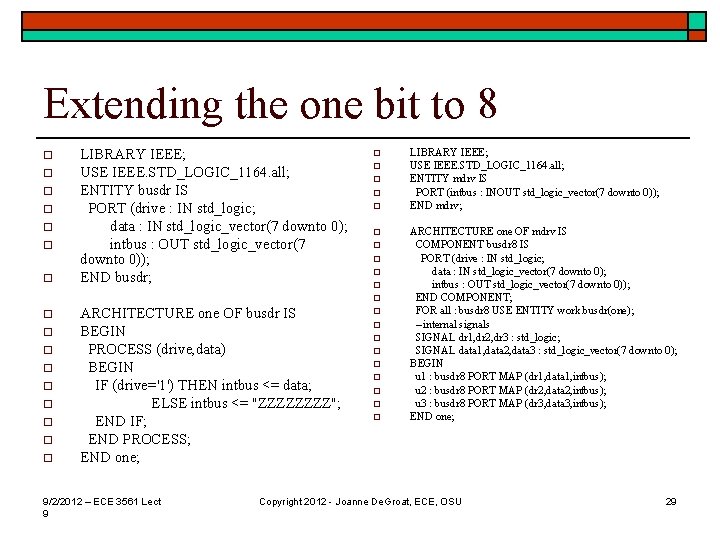

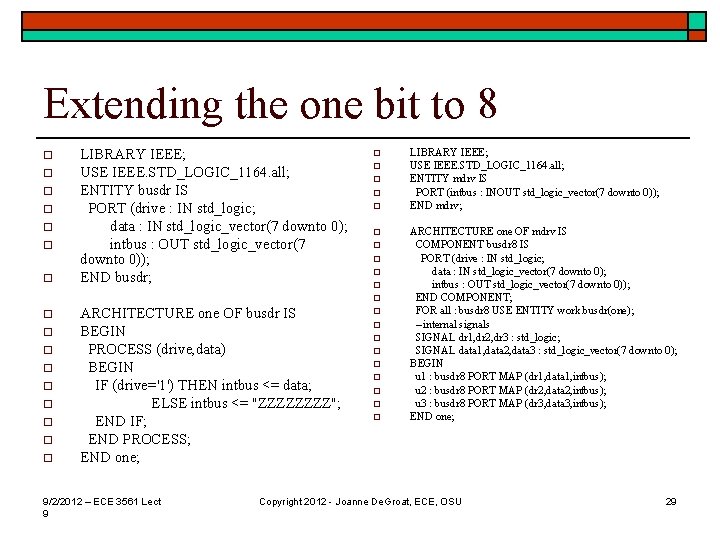

Extending the one bit to 8 o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY busdr IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END busdr; o o o o o ARCHITECTURE one OF busdr IS BEGIN PROCESS (drive, data) BEGIN IF (drive='1') THEN intbus <= data; ELSE intbus <= "ZZZZ"; END IF; END PROCESS; END one; 9/2/2012 – ECE 3561 Lect 9 o o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY mdrv IS PORT (intbus : INOUT std_logic_vector(7 downto 0)); END mdrv; ARCHITECTURE one OF mdrv IS COMPONENT busdr 8 IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END COMPONENT; FOR all : busdr 8 USE ENTITY work. busdr(one); --internal signals SIGNAL dr 1, dr 2, dr 3 : std_logic; SIGNAL data 1, data 2, data 3 : std_logic_vector(7 downto 0); BEGIN u 1 : busdr 8 PORT MAP (dr 1, data 1, intbus); u 2 : busdr 8 PORT MAP (dr 2, data 2, intbus); u 3 : busdr 8 PORT MAP (dr 3, data 3, intbus); END one; Copyright 2012 - Joanne De. Groat, ECE, OSU 29

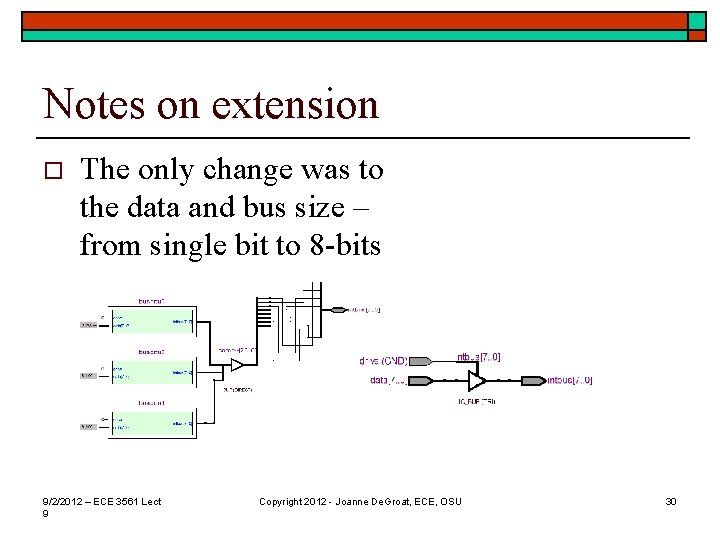

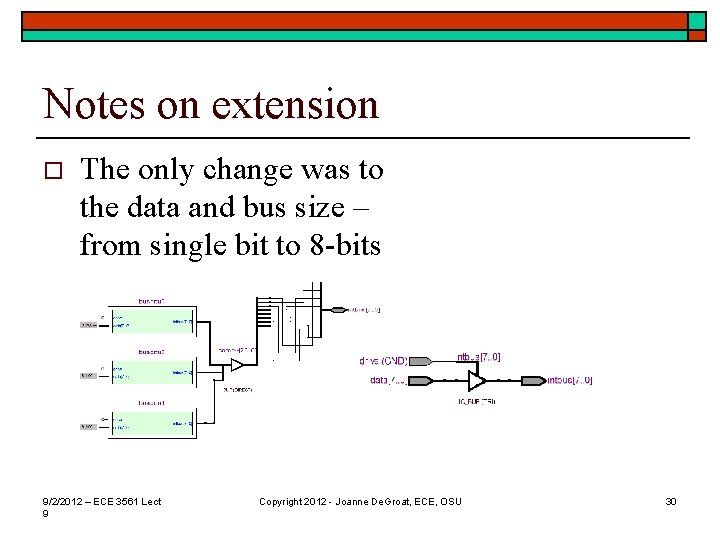

Notes on extension o The only change was to the data and bus size – from single bit to 8 -bits 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 30

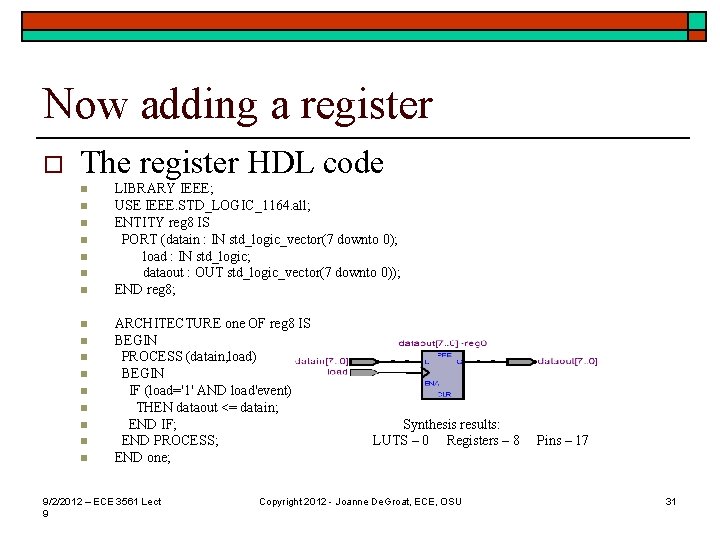

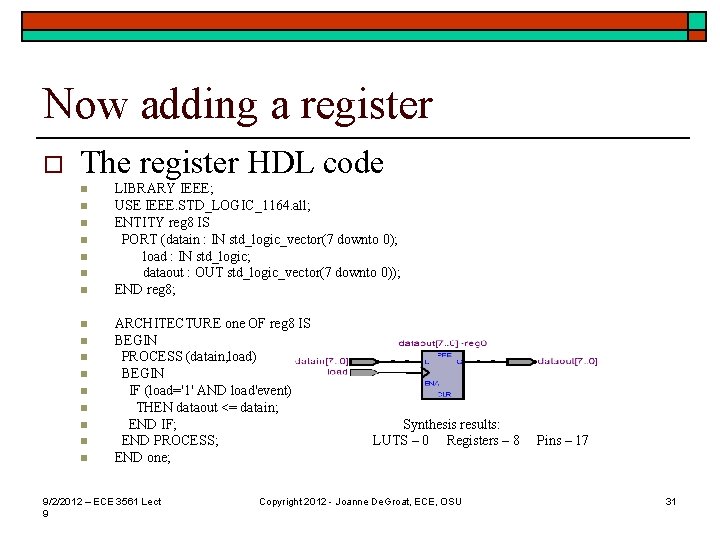

Now adding a register o The register HDL code n n n n LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY reg 8 IS PORT (datain : IN std_logic_vector(7 downto 0); load : IN std_logic; dataout : OUT std_logic_vector(7 downto 0)); END reg 8; ARCHITECTURE one OF reg 8 IS BEGIN PROCESS (datain, load) BEGIN IF (load='1' AND load'event) THEN dataout <= datain; END IF; END PROCESS; END one; 9/2/2012 – ECE 3561 Lect 9 Synthesis results: LUTS – 0 Registers – 8 Copyright 2012 - Joanne De. Groat, ECE, OSU Pins – 17 31

Putting them together o o Now desire to add the register to the bus driver Need 3 segments of VHDL code n Code for the registers 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 32

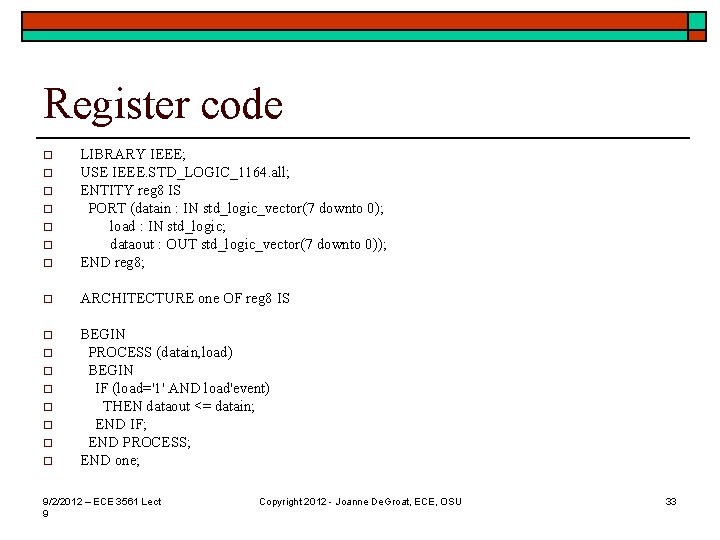

Register code o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY reg 8 IS PORT (datain : IN std_logic_vector(7 downto 0); load : IN std_logic; dataout : OUT std_logic_vector(7 downto 0)); END reg 8; o ARCHITECTURE one OF reg 8 IS o BEGIN PROCESS (datain, load) BEGIN IF (load='1' AND load'event) THEN dataout <= datain; END IF; END PROCESS; END one; o o o o 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 33

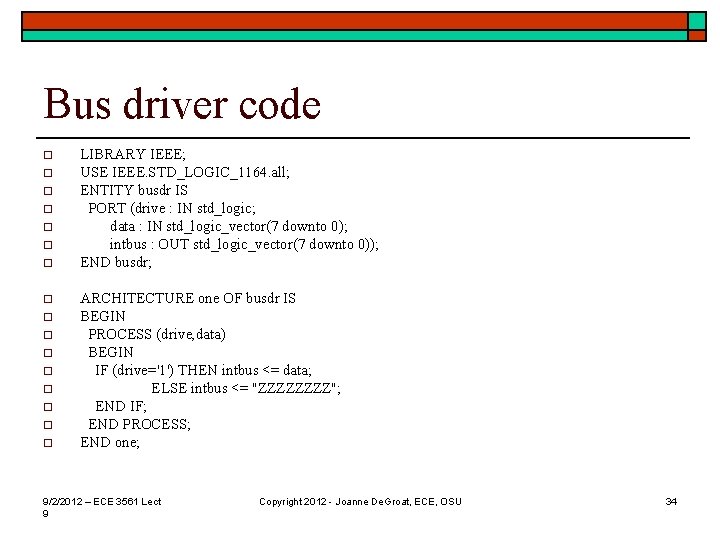

Bus driver code o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY busdr IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END busdr; ARCHITECTURE one OF busdr IS BEGIN PROCESS (drive, data) BEGIN IF (drive='1') THEN intbus <= data; ELSE intbus <= "ZZZZ"; END IF; END PROCESS; END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 34

The total code – 3 instances reg 8 o o o o o LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. all; ENTITY regmdrv 8 IS PORT (intbus : INOUT std_logic_vector(7 downto 0)); END regmdrv 8; o ARCHITECTURE one OF regmdrv 8 IS COMPONENT busdr 8 IS PORT (drive : IN std_logic; data : IN std_logic_vector(7 downto 0); intbus : OUT std_logic_vector(7 downto 0)); END COMPONENT; FOR all : busdr 8 USE ENTITY work. busdr 8(one); COMPONENT reg 8 IS PORT (datain : IN std_logic_vector(7 downto 0); load : IN std_logic; dataout : OUT std_logic_vector(7 downto 0)); END COMPONENT; FOR all : reg 8 USE ENTITY work. reg 8(one); o 9/2/2012 – ECE 3561 Lect 9 o o o --internal signals SIGNAL l 1, l 2, l 3 : std_logic; SIGNAL dr 1, dr 2, dr 3 : std_logic; SIGNAL data 1, data 2, data 3 : std_logic_vector(7 downto 0); SIGNAL datai 1, datai 2, datai 3 : std_logic_vector(7 downto 0); BEGIN u 1 : busdr 8 PORT MAP (dr 1, data 1, intbus); u 2 : busdr 8 PORT MAP (dr 2, data 2, intbus); u 3 : busdr 8 PORT MAP (dr 3, data 3, intbus); r 1 : reg 8 PORT MAP (datai 1, l 1, data 1); r 2 : reg 8 PORT MAP (datai 2, l 1, data 2); r 3 : reg 8 PORT MAP (datai 3, l 1, data 3); END one; Copyright 2012 - Joanne De. Groat, ECE, OSU 35

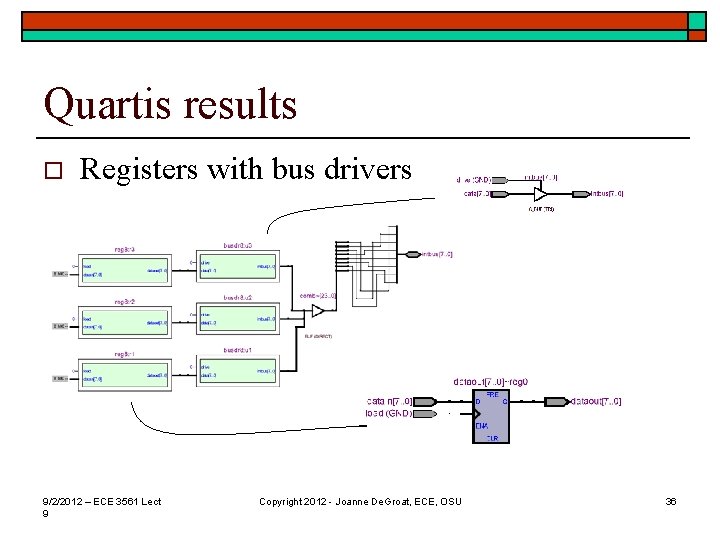

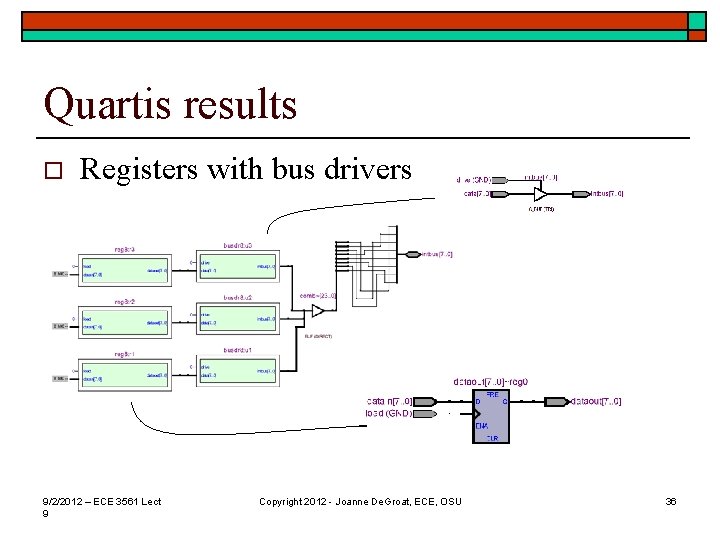

Quartis results o Registers with bus drivers 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 36

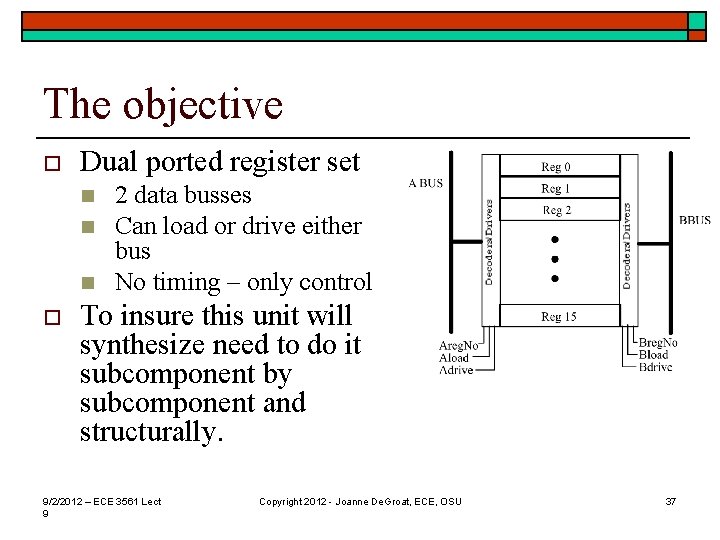

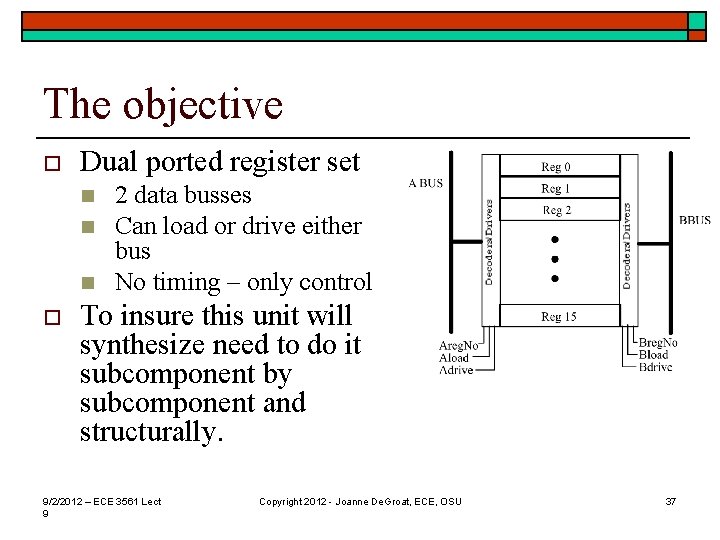

The objective o Dual ported register set n n n o 2 data busses Can load or drive either bus No timing – only control To insure this unit will synthesize need to do it subcomponent by subcomponent and structurally. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 37

Lecture summary o TYPE std_logic Using std_logic to build into creating a register set o Next step – class input? ? ? o 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 38