L 16 VHDL for State Machines with binary

L 16 – VHDL for State Machines with binary encoding

VHDL – binary encoded states o Another example n n o Counter – enumeration states Binary encoded states Gray Code Controlled counters Ref: text Unit 10, 17, 20 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

Counter example o o o Specification – Write a synthesizable VHDL description of a 3 -bit counter that counts from 0 to 7 in binary, i. e. , 000, 001, 010, …, 110, 111. A 3 -bit counter has 8 states, so, s 1, …, s 8. The state occur sequentially without control. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 3

Start the HDL o o This is a problem that one should be able to do without a state diagram to start. The entity n n ENTITY cnt 3 bit IS PORT(clk : IN bit; cnt : OUT bit_vector(2 downto 0)); END cnt 3 bit; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 4

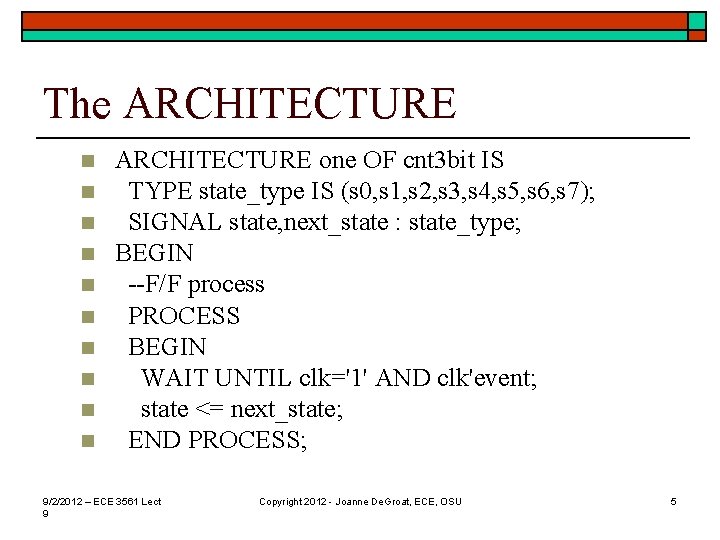

The ARCHITECTURE n n n n n ARCHITECTURE one OF cnt 3 bit IS TYPE state_type IS (s 0, s 1, s 2, s 3, s 4, s 5, s 6, s 7); SIGNAL state, next_state : state_type; BEGIN --F/F process PROCESS BEGIN WAIT UNTIL clk='1' AND clk'event; state <= next_state; END PROCESS; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 5

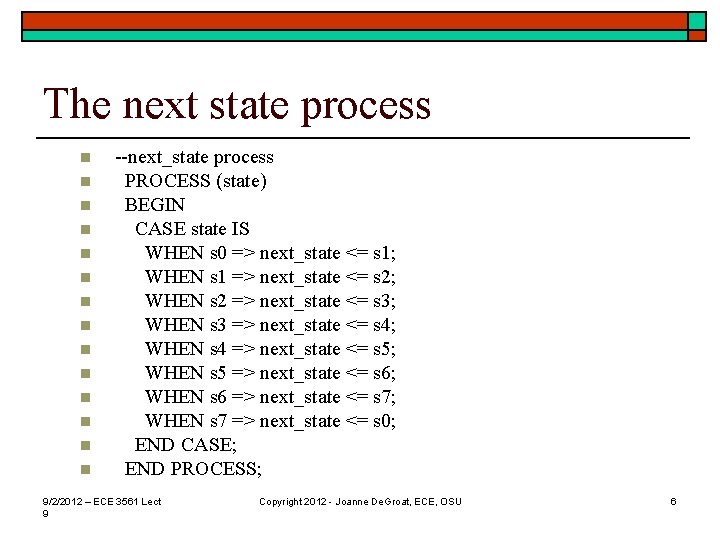

The next state process n n n n --next_state process PROCESS (state) BEGIN CASE state IS WHEN s 0 => next_state <= s 1; WHEN s 1 => next_state <= s 2; WHEN s 2 => next_state <= s 3; WHEN s 3 => next_state <= s 4; WHEN s 4 => next_state <= s 5; WHEN s 5 => next_state <= s 6; WHEN s 6 => next_state <= s 7; WHEN s 7 => next_state <= s 0; END CASE; END PROCESS; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 6

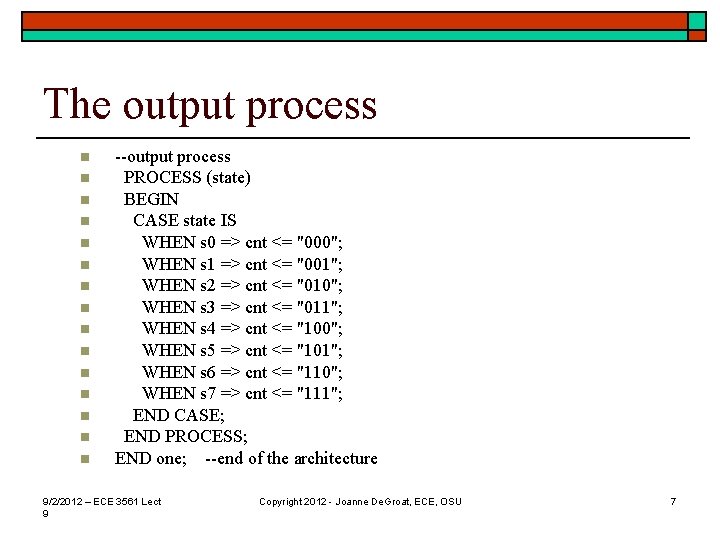

The output process n n n n --output process PROCESS (state) BEGIN CASE state IS WHEN s 0 => cnt <= "000"; WHEN s 1 => cnt <= "001"; WHEN s 2 => cnt <= "010"; WHEN s 3 => cnt <= "011"; WHEN s 4 => cnt <= "100"; WHEN s 5 => cnt <= "101"; WHEN s 6 => cnt <= "110"; WHEN s 7 => cnt <= "111"; END CASE; END PROCESS; END one; --end of the architecture 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 7

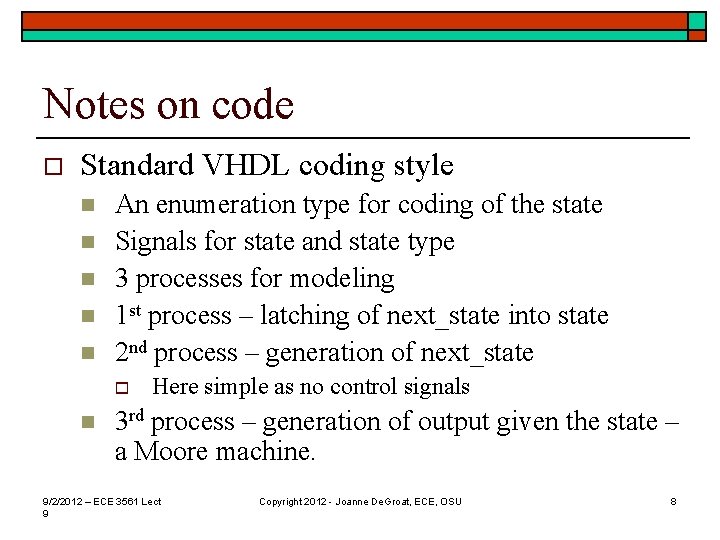

Notes on code o Standard VHDL coding style n n n An enumeration type for coding of the state Signals for state and state type 3 processes for modeling 1 st process – latching of next_state into state 2 nd process – generation of next_state o n Here simple as no control signals 3 rd process – generation of output given the state – a Moore machine. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 8

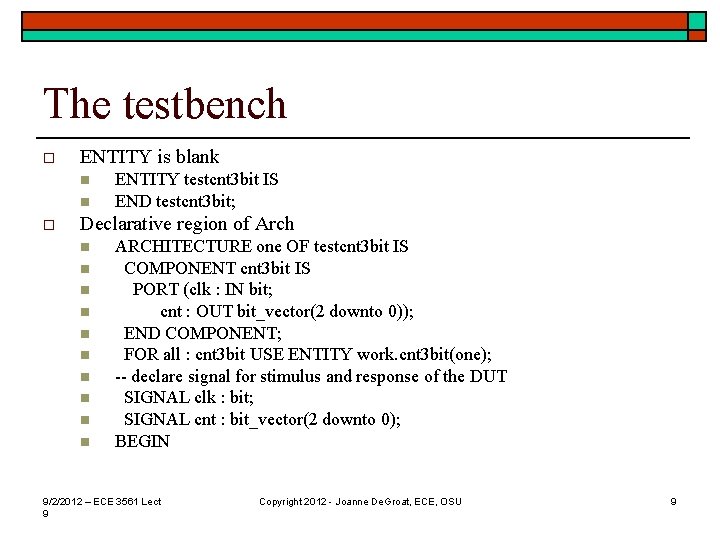

The testbench o ENTITY is blank n n o ENTITY testcnt 3 bit IS END testcnt 3 bit; Declarative region of Arch n n n n n ARCHITECTURE one OF testcnt 3 bit IS COMPONENT cnt 3 bit IS PORT (clk : IN bit; cnt : OUT bit_vector(2 downto 0)); END COMPONENT; FOR all : cnt 3 bit USE ENTITY work. cnt 3 bit(one); -- declare signal for stimulus and response of the DUT SIGNAL clk : bit; SIGNAL cnt : bit_vector(2 downto 0); BEGIN 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 9

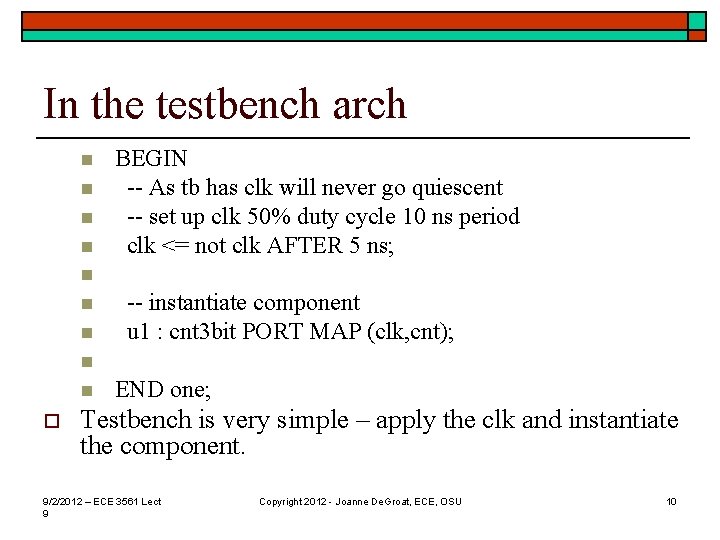

In the testbench arch n n BEGIN -- As tb has clk will never go quiescent -- set up clk 50% duty cycle 10 ns period clk <= not clk AFTER 5 ns; n n n -- instantiate component u 1 : cnt 3 bit PORT MAP (clk, cnt); n n o END one; Testbench is very simple – apply the clk and instantiate the component. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 10

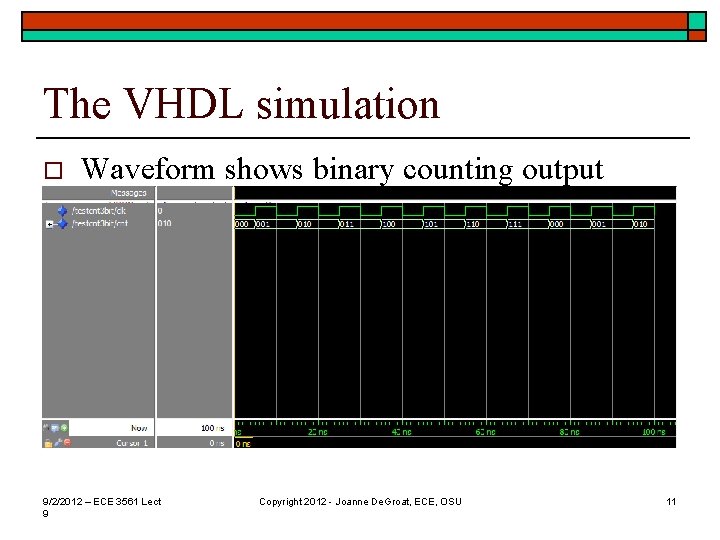

The VHDL simulation o Waveform shows binary counting output 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 11

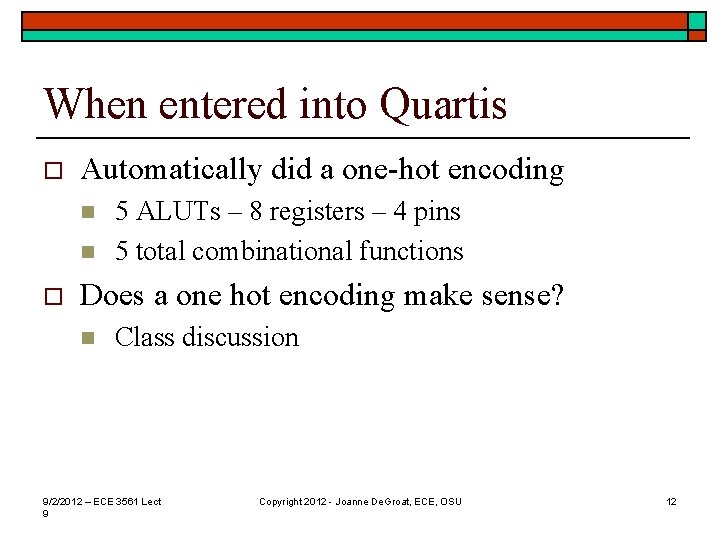

When entered into Quartis o Automatically did a one-hot encoding n n o 5 ALUTs – 8 registers – 4 pins 5 total combinational functions Does a one hot encoding make sense? n Class discussion 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 12

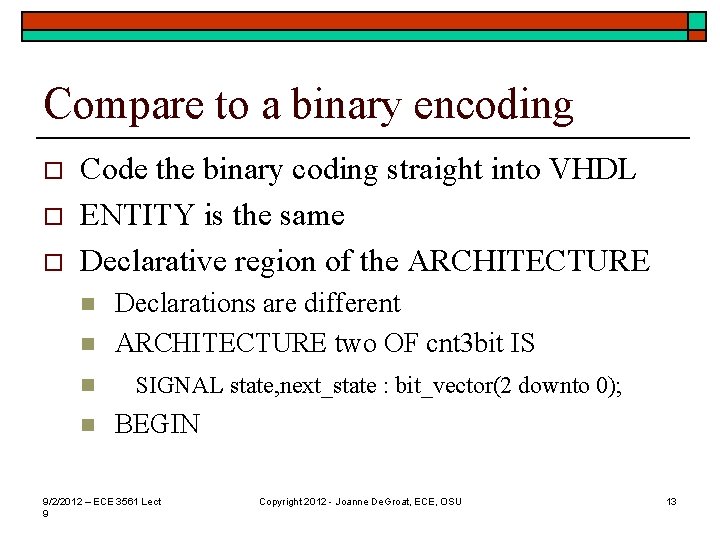

Compare to a binary encoding o o o Code the binary coding straight into VHDL ENTITY is the same Declarative region of the ARCHITECTURE n n Declarations are different ARCHITECTURE two OF cnt 3 bit IS SIGNAL state, next_state : bit_vector(2 downto 0); BEGIN 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 13

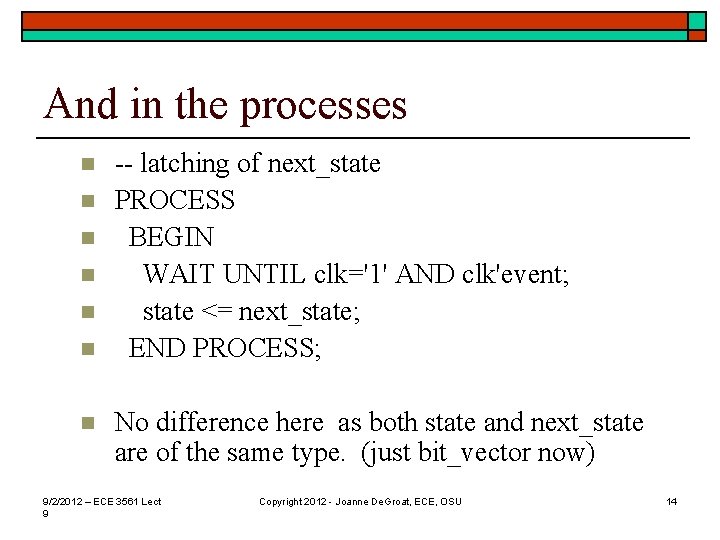

And in the processes n n n n -- latching of next_state PROCESS BEGIN WAIT UNTIL clk='1' AND clk'event; state <= next_state; END PROCESS; No difference here as both state and next_state are of the same type. (just bit_vector now) 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 14

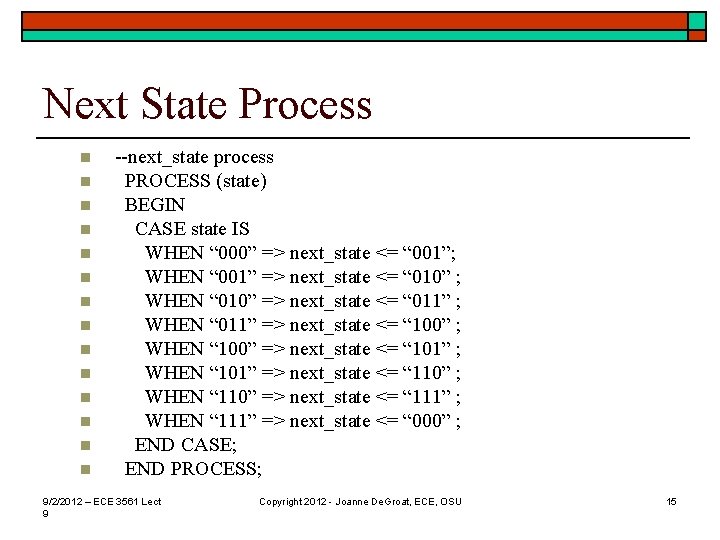

Next State Process n n n n --next_state process PROCESS (state) BEGIN CASE state IS WHEN “ 000” => next_state <= “ 001”; WHEN “ 001” => next_state <= “ 010” ; WHEN “ 010” => next_state <= “ 011” ; WHEN “ 011” => next_state <= “ 100” ; WHEN “ 100” => next_state <= “ 101” ; WHEN “ 101” => next_state <= “ 110” ; WHEN “ 110” => next_state <= “ 111” ; WHEN “ 111” => next_state <= “ 000” ; END CASE; END PROCESS; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 15

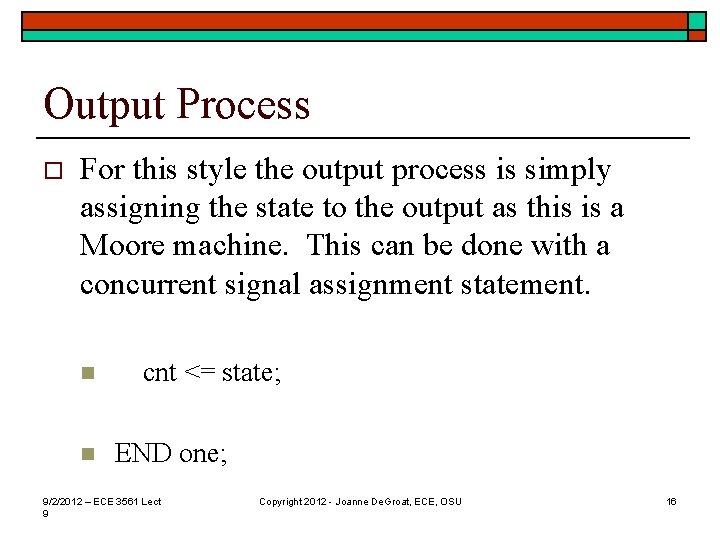

Output Process o For this style the output process is simply assigning the state to the output as this is a Moore machine. This can be done with a concurrent signal assignment statement. n n cnt <= state; END one; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 16

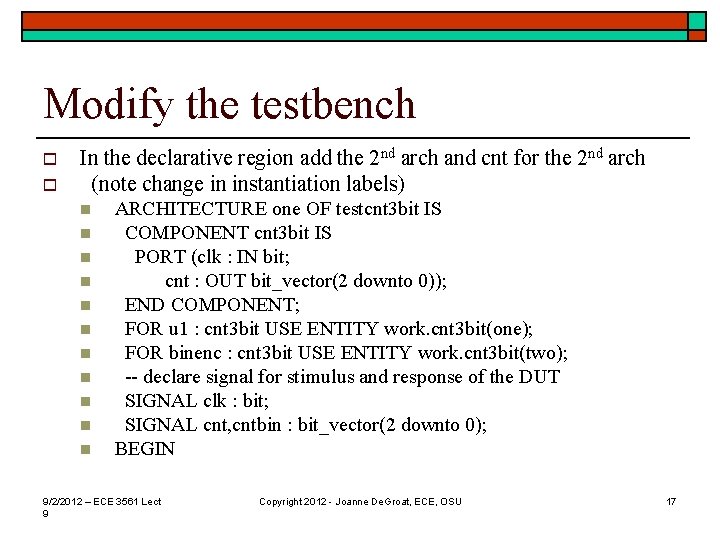

Modify the testbench o o In the declarative region add the 2 nd arch and cnt for the 2 nd arch (note change in instantiation labels) n n n ARCHITECTURE one OF testcnt 3 bit IS COMPONENT cnt 3 bit IS PORT (clk : IN bit; cnt : OUT bit_vector(2 downto 0)); END COMPONENT; FOR u 1 : cnt 3 bit USE ENTITY work. cnt 3 bit(one); FOR binenc : cnt 3 bit USE ENTITY work. cnt 3 bit(two); -- declare signal for stimulus and response of the DUT SIGNAL clk : bit; SIGNAL cnt, cntbin : bit_vector(2 downto 0); BEGIN 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 17

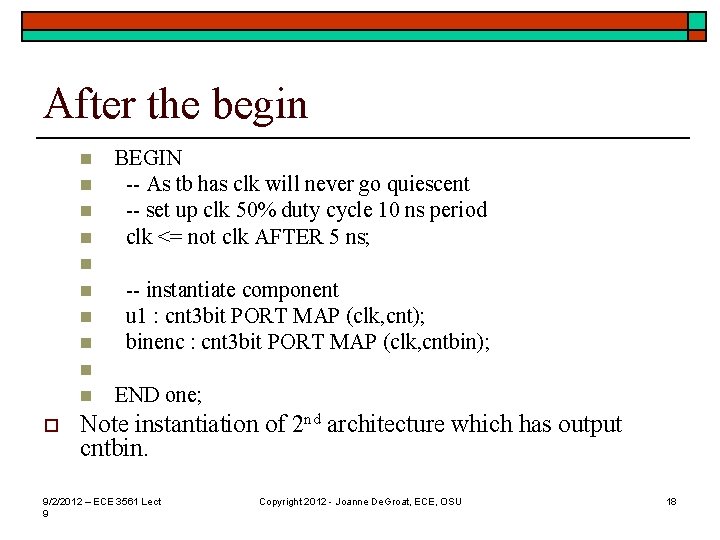

After the begin n n BEGIN -- As tb has clk will never go quiescent -- set up clk 50% duty cycle 10 ns period clk <= not clk AFTER 5 ns; n n -- instantiate component u 1 : cnt 3 bit PORT MAP (clk, cnt); binenc : cnt 3 bit PORT MAP (clk, cntbin); n n o END one; Note instantiation of 2 nd architecture which has output cntbin. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 18

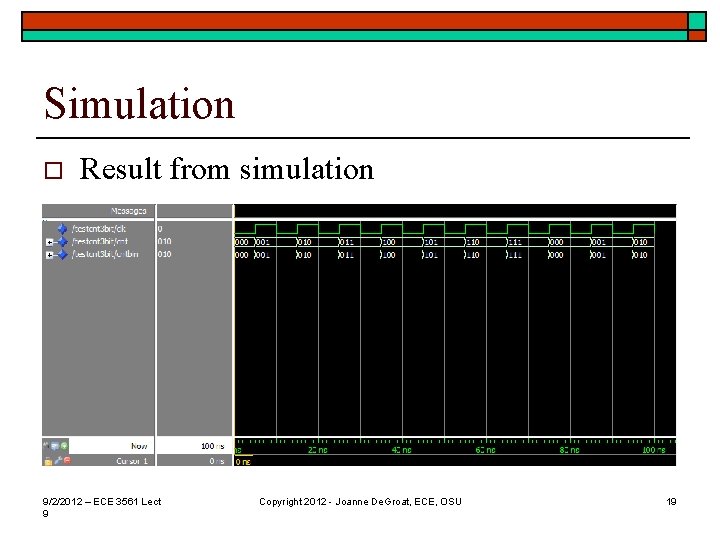

Simulation o Result from simulation 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 19

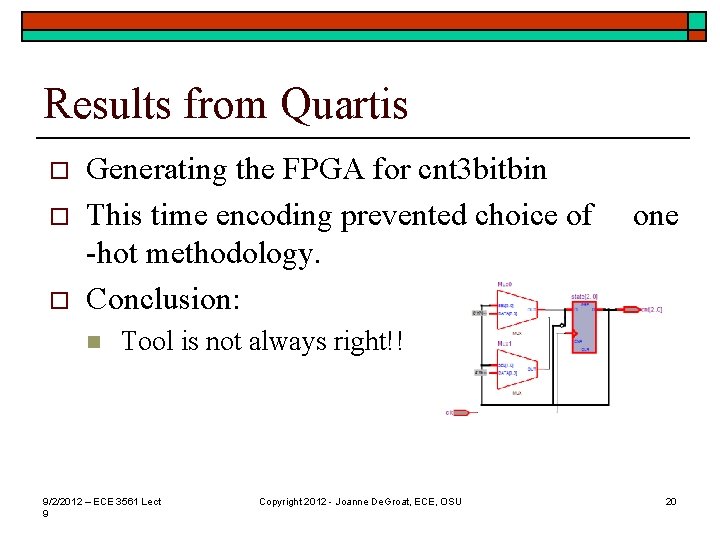

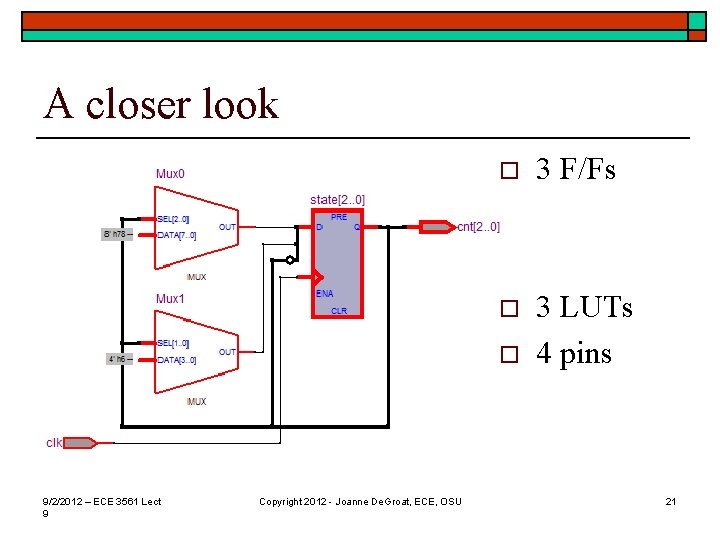

Results from Quartis o o o Generating the FPGA for cnt 3 bitbin This time encoding prevented choice of -hot methodology. Conclusion: n one Tool is not always right!! 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 20

A closer look o 3 F/Fs o 3 LUTs 4 pins o 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 21

Controlling the binary assignment o o Being able to control the binary assign results in more control for the designer and easier design of other counters. Can result in more efficient use of FPGA resources. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 22

Time for live demo o Demo of code in Modelsim Demo of setup in Quartis Probably want to take note of steps and editing shortcuts. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 23

Lecture summary o HDL from code to simulation n o For the 101 sequence detector Testbench for the sequence detector 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 24

- Slides: 24