L 13 VHDL Language Elements VHDL Language Elements

- Slides: 34

L 13 – VHDL Language Elements

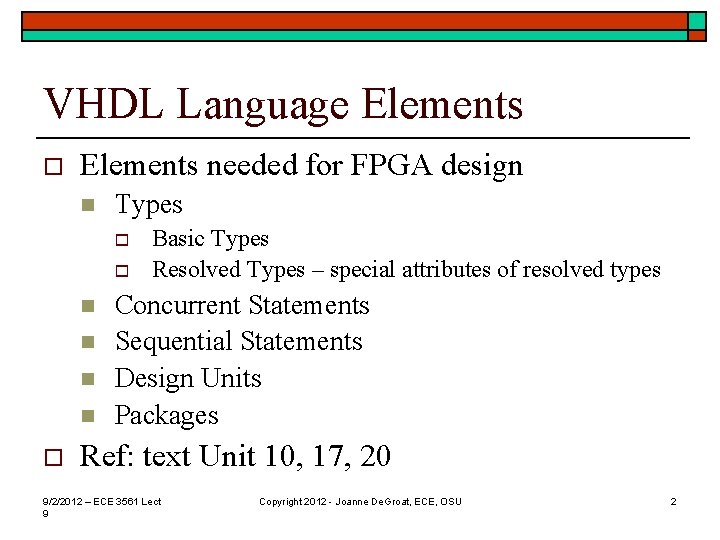

VHDL Language Elements o Elements needed for FPGA design n Types o o n n o Basic Types Resolved Types – special attributes of resolved types Concurrent Statements Sequential Statements Design Units Packages Ref: text Unit 10, 17, 20 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

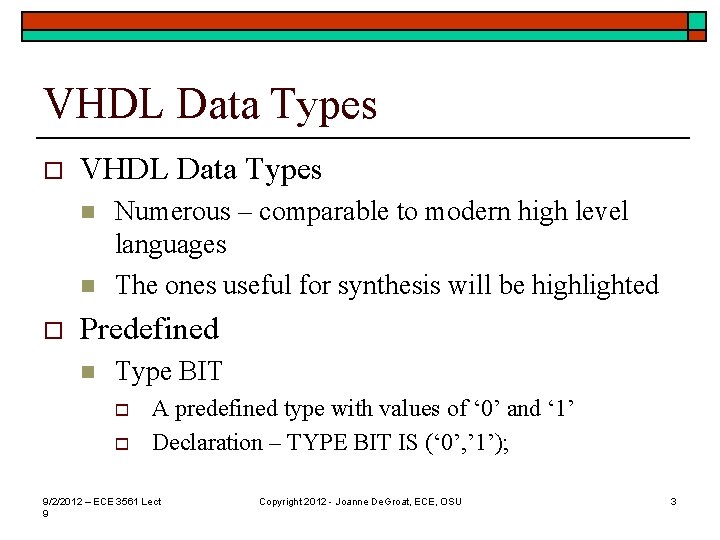

VHDL Data Types o VHDL Data Types n n o Numerous – comparable to modern high level languages The ones useful for synthesis will be highlighted Predefined n Type BIT o o A predefined type with values of ‘ 0’ and ‘ 1’ Declaration – TYPE BIT IS (‘ 0’, ’ 1’); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 3

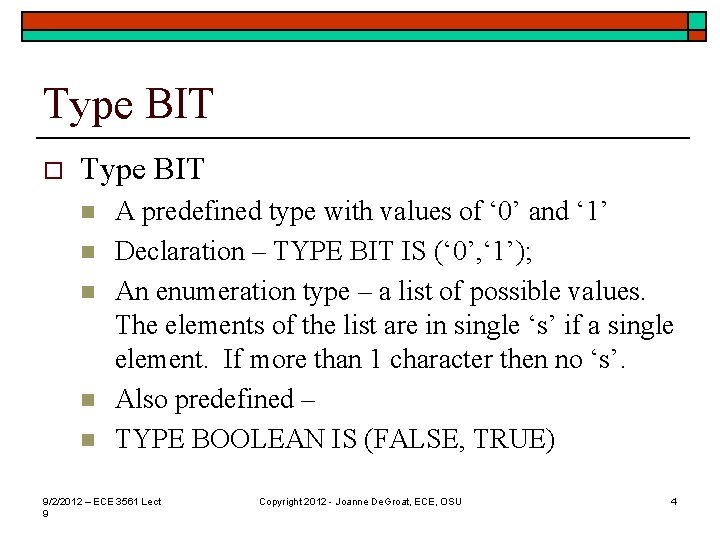

Type BIT o Type BIT n n n A predefined type with values of ‘ 0’ and ‘ 1’ Declaration – TYPE BIT IS (‘ 0’, ‘ 1’); An enumeration type – a list of possible values. The elements of the list are in single ‘s’ if a single element. If more than 1 character then no ‘s’. Also predefined – TYPE BOOLEAN IS (FALSE, TRUE) 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 4

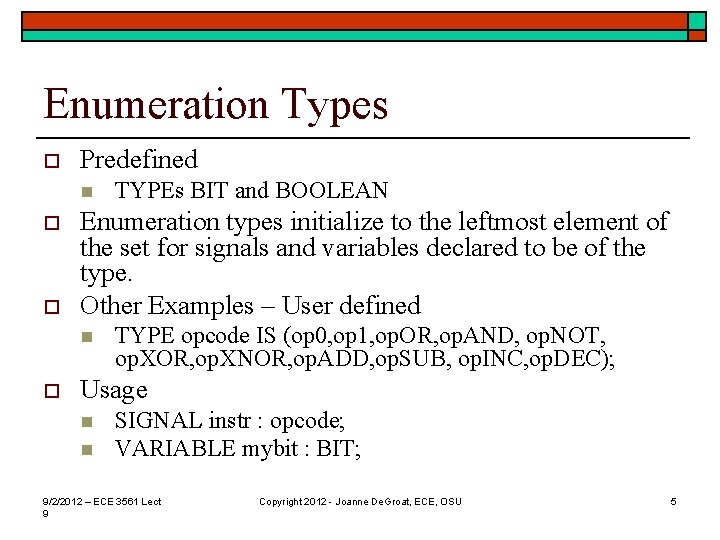

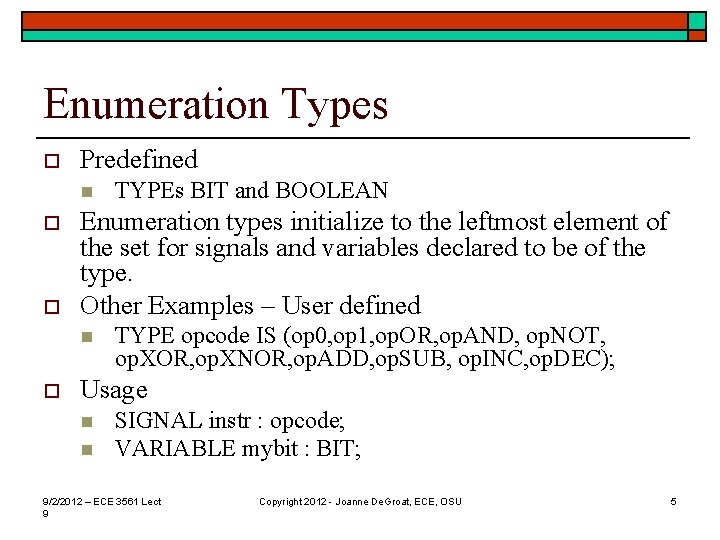

Enumeration Types o Predefined n o o Enumeration types initialize to the leftmost element of the set for signals and variables declared to be of the type. Other Examples – User defined n o TYPEs BIT and BOOLEAN TYPE opcode IS (op 0, op 1, op. OR, op. AND, op. NOT, op. XOR, op. XNOR, op. ADD, op. SUB, op. INC, op. DEC); Usage n n SIGNAL instr : opcode; VARIABLE mybit : BIT; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 5

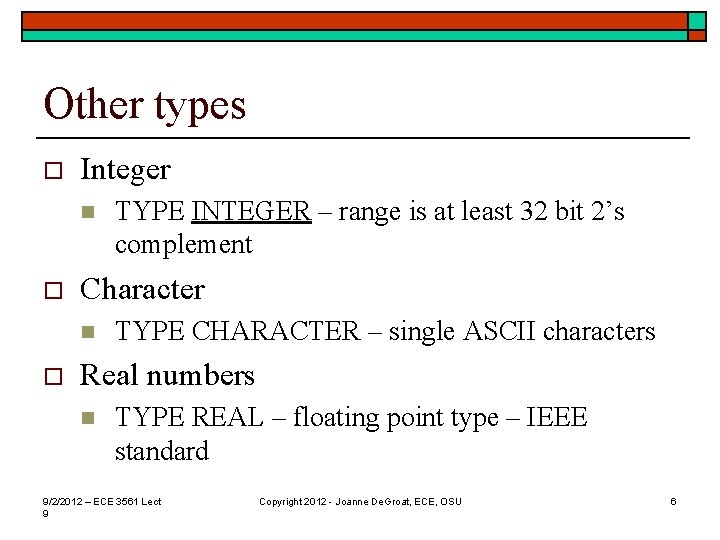

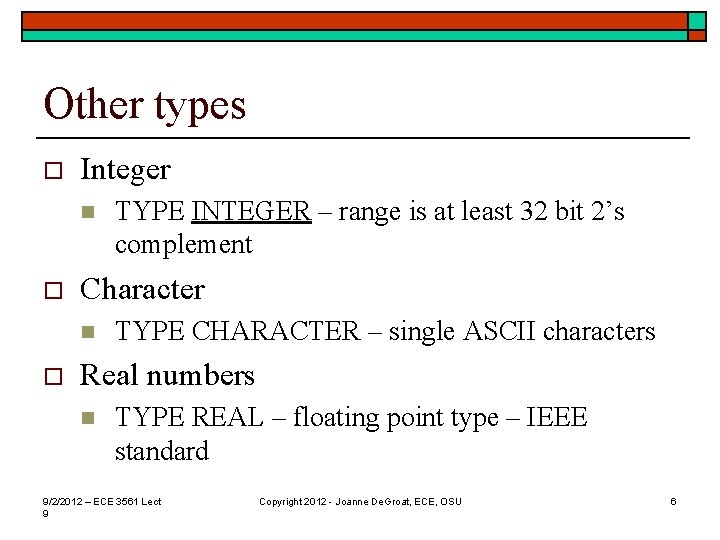

Other types o Integer n o Character n o TYPE INTEGER – range is at least 32 bit 2’s complement TYPE CHARACTER – single ASCII characters Real numbers n TYPE REAL – floating point type – IEEE standard 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 6

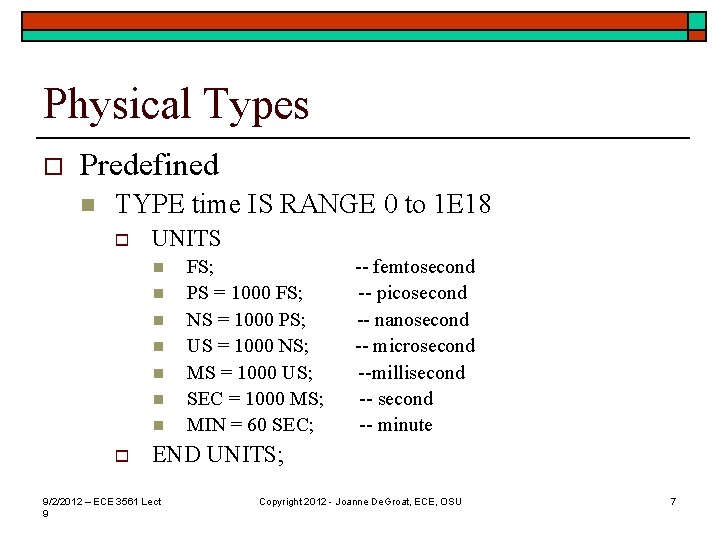

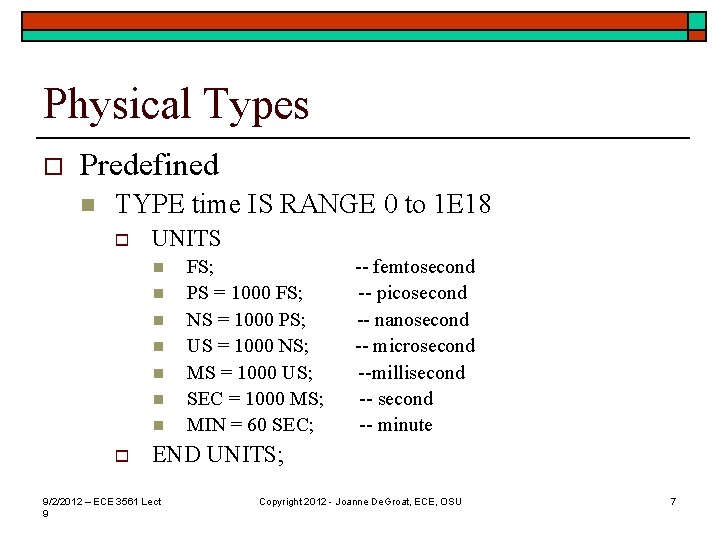

Physical Types o Predefined n TYPE time IS RANGE 0 to 1 E 18 o UNITS n n n n o FS; PS = 1000 FS; NS = 1000 PS; US = 1000 NS; MS = 1000 US; SEC = 1000 MS; MIN = 60 SEC; -- femtosecond -- picosecond -- nanosecond -- microsecond --millisecond -- minute END UNITS; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 7

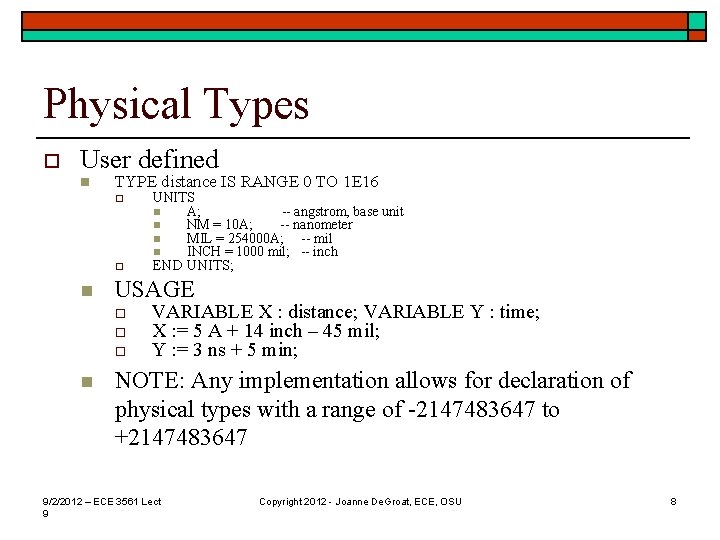

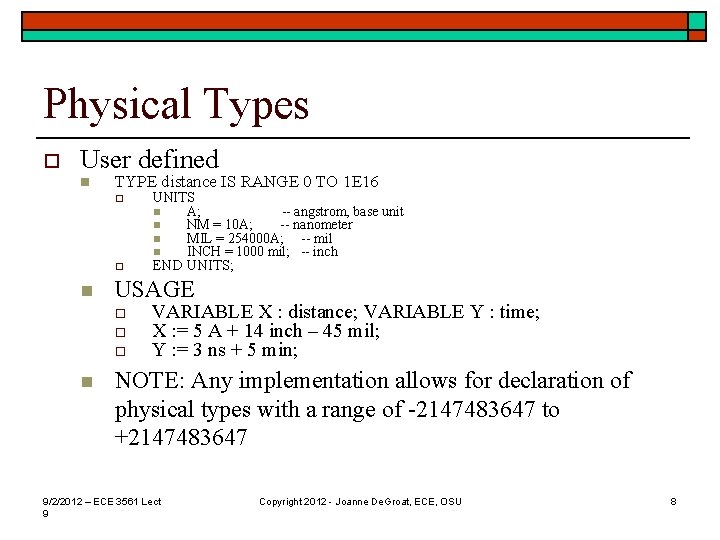

Physical Types o User defined n TYPE distance IS RANGE 0 TO 1 E 16 o UNITS n n o n END UNITS; USAGE o o o n A; -- angstrom, base unit NM = 10 A; -- nanometer MIL = 254000 A; -- mil INCH = 1000 mil; -- inch VARIABLE X : distance; VARIABLE Y : time; X : = 5 A + 14 inch – 45 mil; Y : = 3 ns + 5 min; NOTE: Any implementation allows for declaration of physical types with a range of -2147483647 to +2147483647 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 8

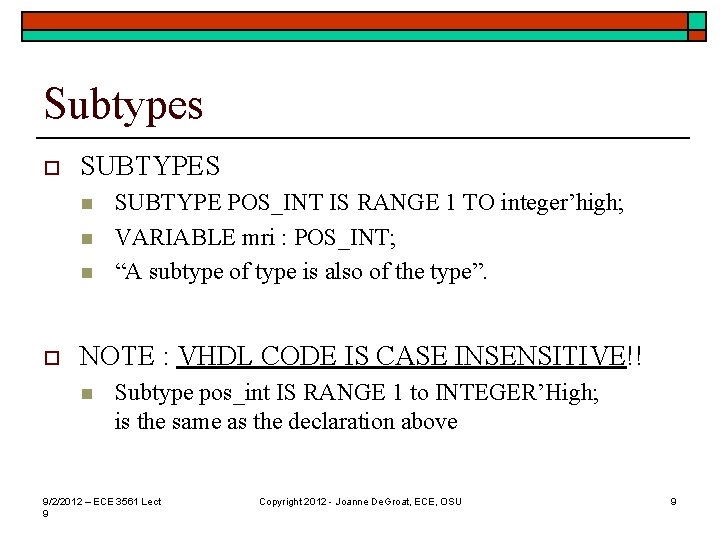

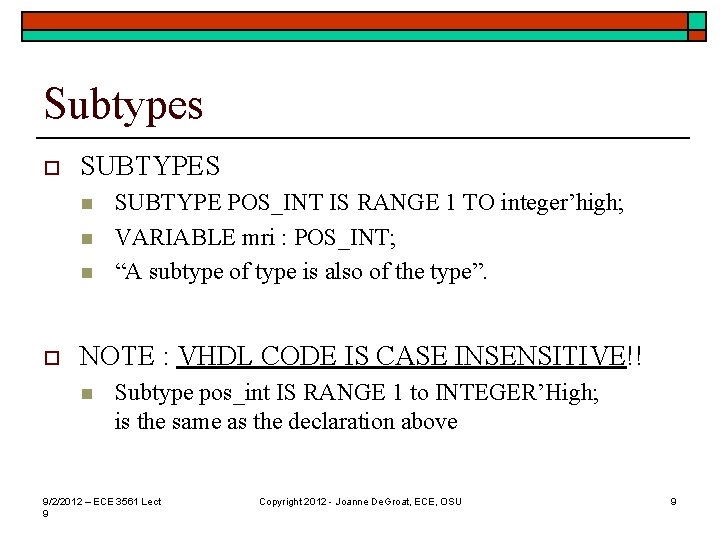

Subtypes o SUBTYPES n n n o SUBTYPE POS_INT IS RANGE 1 TO integer’high; VARIABLE mri : POS_INT; “A subtype of type is also of the type”. NOTE : VHDL CODE IS CASE INSENSITIVE!! n Subtype pos_int IS RANGE 1 to INTEGER’High; is the same as the declaration above 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 9

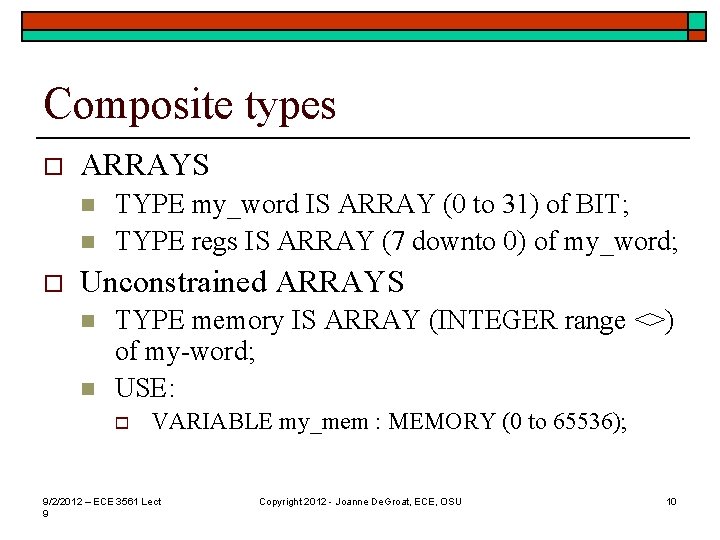

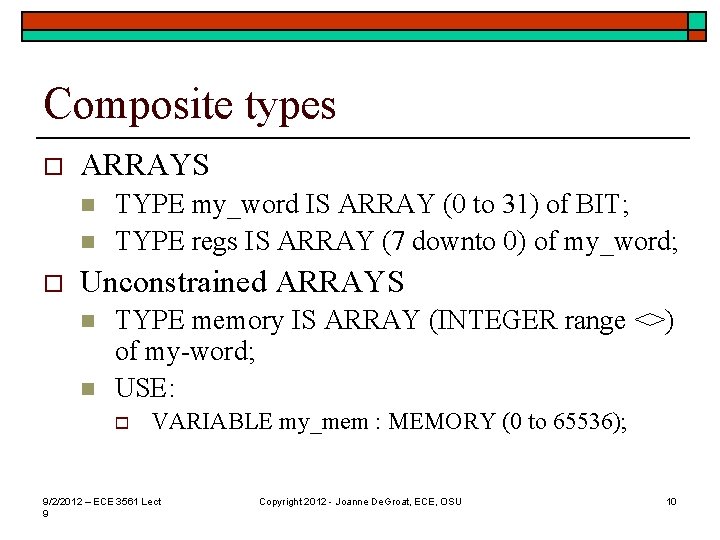

Composite types o ARRAYS n n o TYPE my_word IS ARRAY (0 to 31) of BIT; TYPE regs IS ARRAY (7 downto 0) of my_word; Unconstrained ARRAYS n n TYPE memory IS ARRAY (INTEGER range <>) of my-word; USE: o VARIABLE my_mem : MEMORY (0 to 65536); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 10

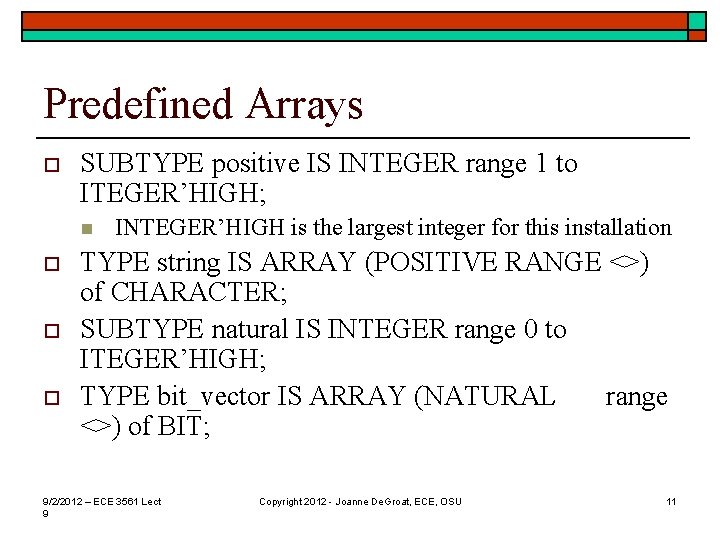

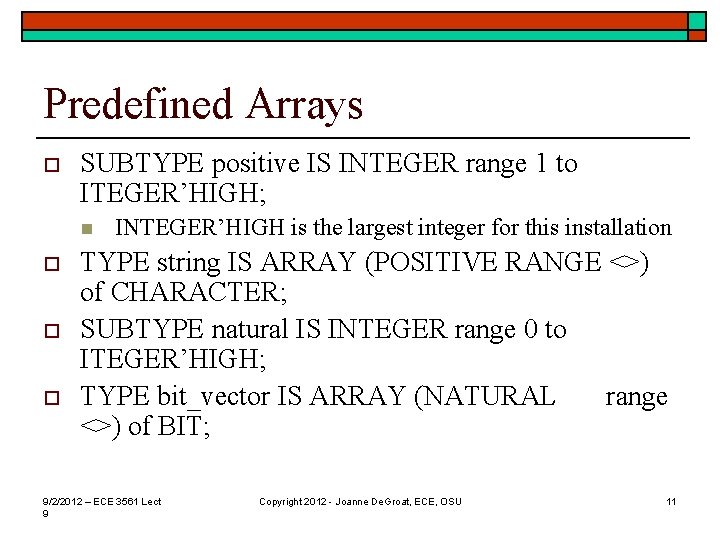

Predefined Arrays o SUBTYPE positive IS INTEGER range 1 to ITEGER’HIGH; n o o o INTEGER’HIGH is the largest integer for this installation TYPE string IS ARRAY (POSITIVE RANGE <>) of CHARACTER; SUBTYPE natural IS INTEGER range 0 to ITEGER’HIGH; TYPE bit_vector IS ARRAY (NATURAL range <>) of BIT; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 11

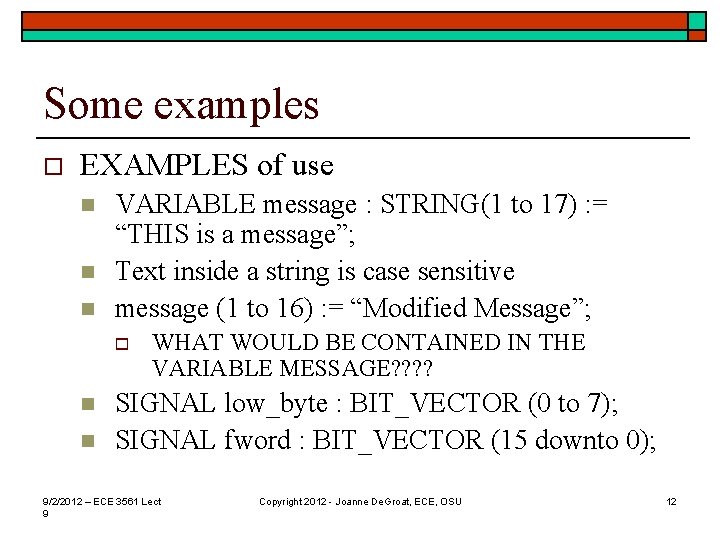

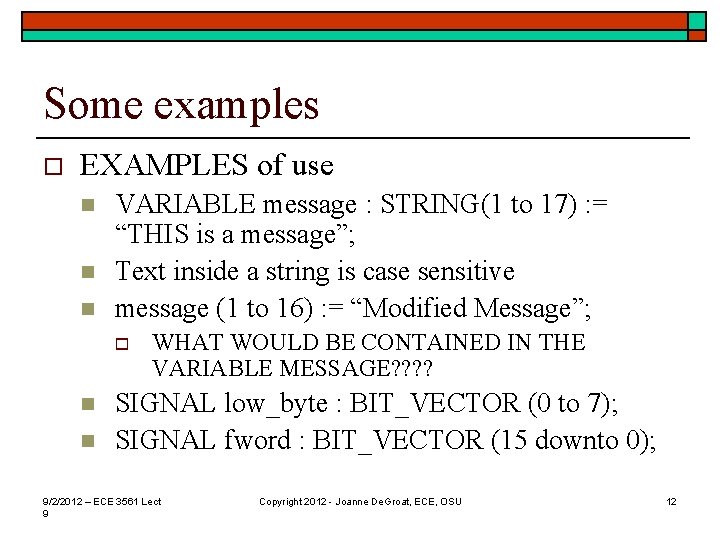

Some examples o EXAMPLES of use n n n VARIABLE message : STRING(1 to 17) : = “THIS is a message”; Text inside a string is case sensitive message (1 to 16) : = “Modified Message”; o n n WHAT WOULD BE CONTAINED IN THE VARIABLE MESSAGE? ? SIGNAL low_byte : BIT_VECTOR (0 to 7); SIGNAL fword : BIT_VECTOR (15 downto 0); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 12

Other types o o o Composite types – RECORDS Dynamic records – ACCESS TYPES File I/O – FILE TYPES 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 13

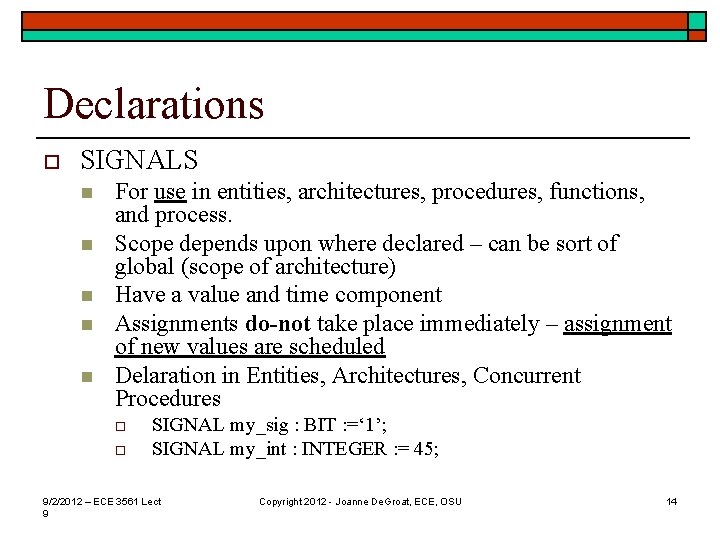

Declarations o SIGNALS n n n For use in entities, architectures, procedures, functions, and process. Scope depends upon where declared – can be sort of global (scope of architecture) Have a value and time component Assignments do-not take place immediately – assignment of new values are scheduled Delaration in Entities, Architectures, Concurrent Procedures o o SIGNAL my_sig : BIT : =‘ 1’; SIGNAL my_int : INTEGER : = 45; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 14

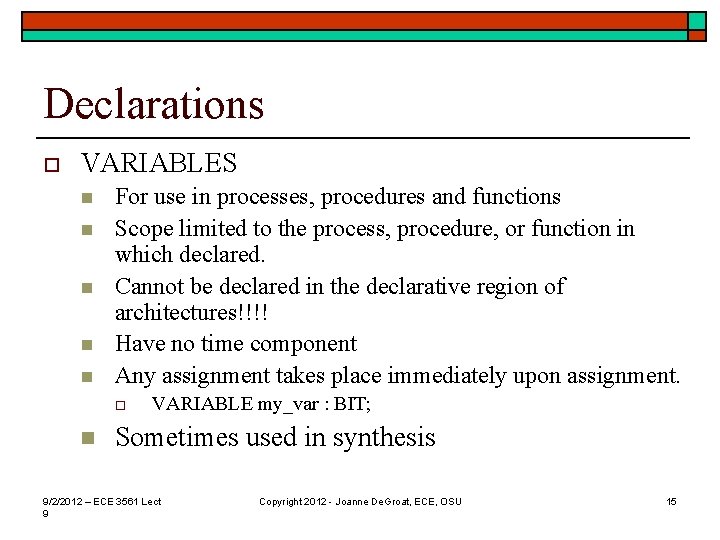

Declarations o VARIABLES n n n For use in processes, procedures and functions Scope limited to the process, procedure, or function in which declared. Cannot be declared in the declarative region of architectures!!!! Have no time component Any assignment takes place immediately upon assignment. o n VARIABLE my_var : BIT; Sometimes used in synthesis 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 15

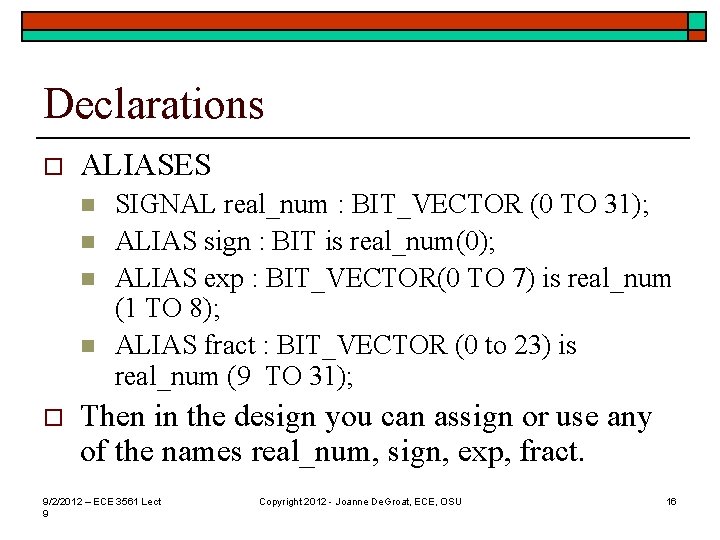

Declarations o ALIASES n n o SIGNAL real_num : BIT_VECTOR (0 TO 31); ALIAS sign : BIT is real_num(0); ALIAS exp : BIT_VECTOR(0 TO 7) is real_num (1 TO 8); ALIAS fract : BIT_VECTOR (0 to 23) is real_num (9 TO 31); Then in the design you can assign or use any of the names real_num, sign, exp, fract. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 16

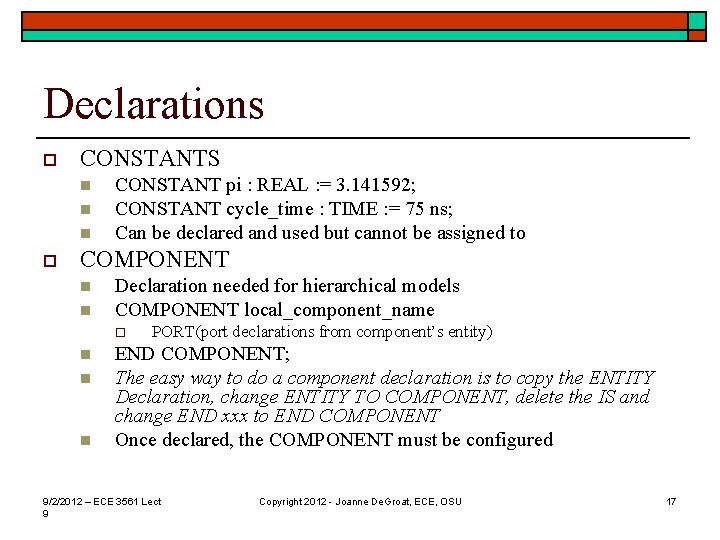

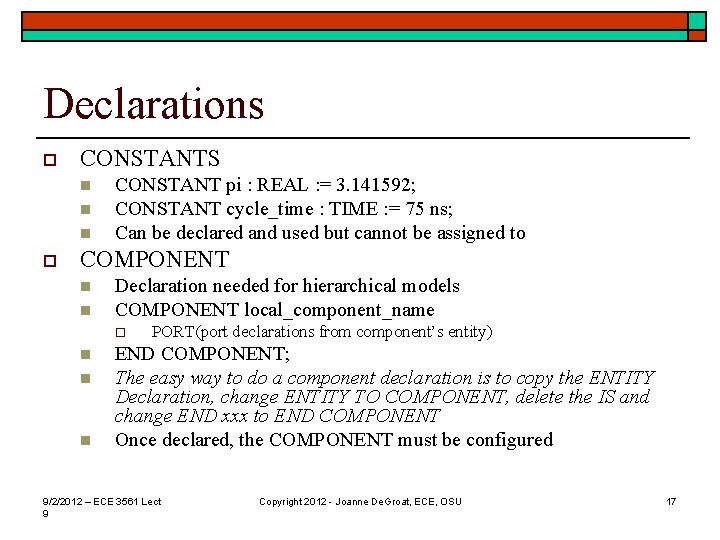

Declarations o CONSTANTS n n n o CONSTANT pi : REAL : = 3. 141592; CONSTANT cycle_time : TIME : = 75 ns; Can be declared and used but cannot be assigned to COMPONENT n n Declaration needed for hierarchical models COMPONENT local_component_name o n n n PORT(port declarations from component’s entity) END COMPONENT; The easy way to do a component declaration is to copy the ENTITY Declaration, change ENTITY TO COMPONENT, delete the IS and change END xxx to END COMPONENT Once declared, the COMPONENT must be configured 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 17

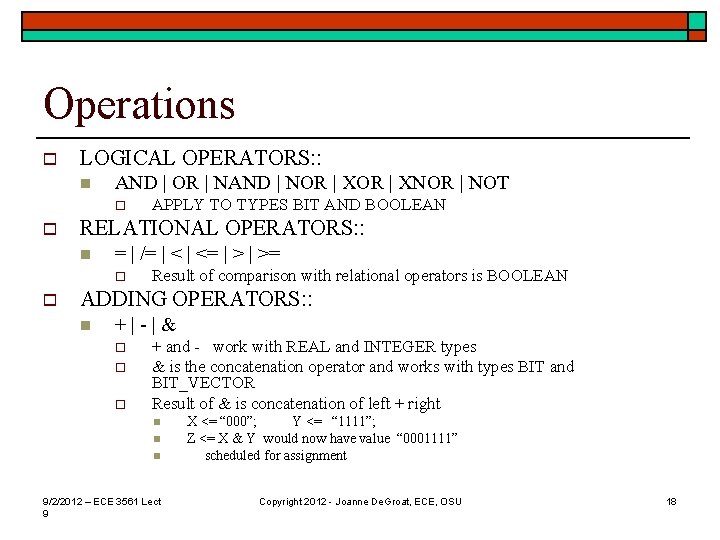

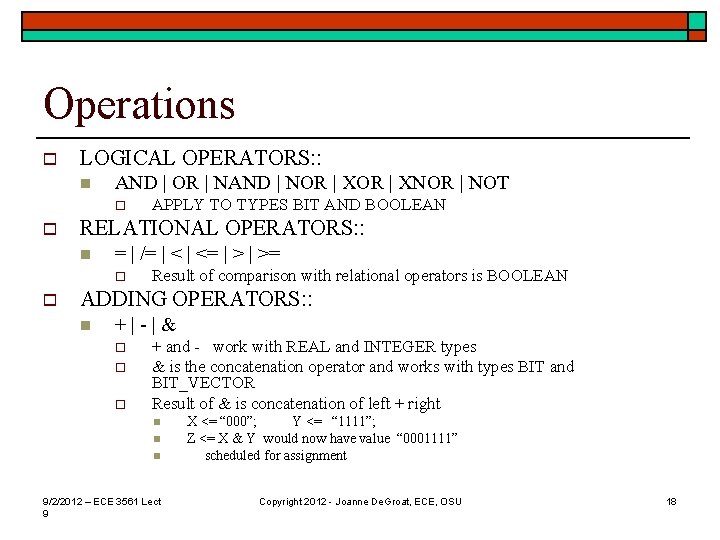

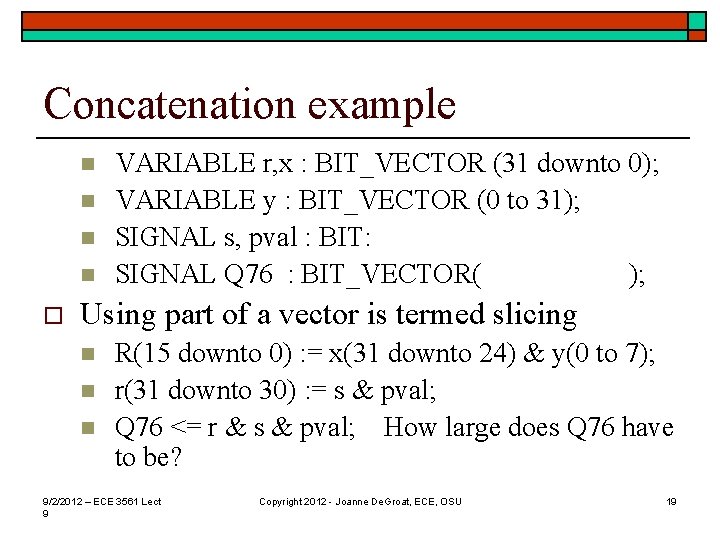

Operations o LOGICAL OPERATORS: : n AND | OR | NAND | NOR | XNOR | NOT o o RELATIONAL OPERATORS: : n = | /= | <= | >= o o APPLY TO TYPES BIT AND BOOLEAN Result of comparison with relational operators is BOOLEAN ADDING OPERATORS: : n +|-|& o o o + and - work with REAL and INTEGER types & is the concatenation operator and works with types BIT and BIT_VECTOR Result of & is concatenation of left + right n n n 9/2/2012 – ECE 3561 Lect 9 X <= “ 000”; Y <= “ 1111”; Z <= X & Y would now have value “ 0001111” scheduled for assignment Copyright 2012 - Joanne De. Groat, ECE, OSU 18

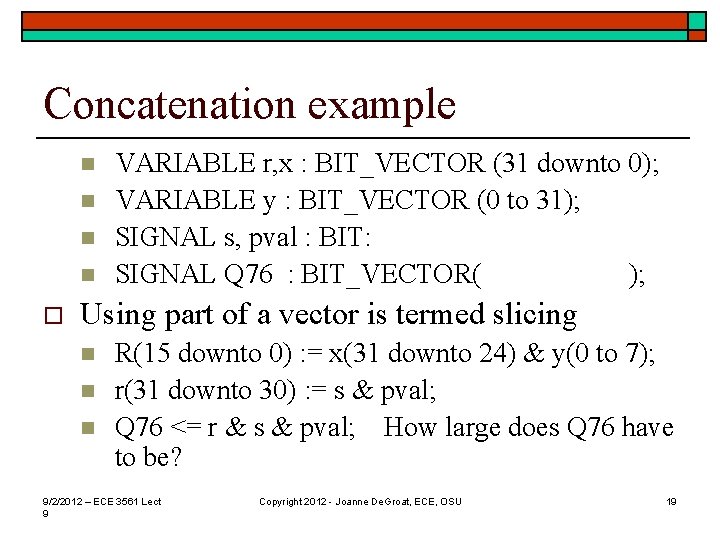

Concatenation example n n o VARIABLE r, x : BIT_VECTOR (31 downto 0); VARIABLE y : BIT_VECTOR (0 to 31); SIGNAL s, pval : BIT: SIGNAL Q 76 : BIT_VECTOR( ); Using part of a vector is termed slicing n n n R(15 downto 0) : = x(31 downto 24) & y(0 to 7); r(31 downto 30) : = s & pval; Q 76 <= r & s & pval; How large does Q 76 have to be? 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 19

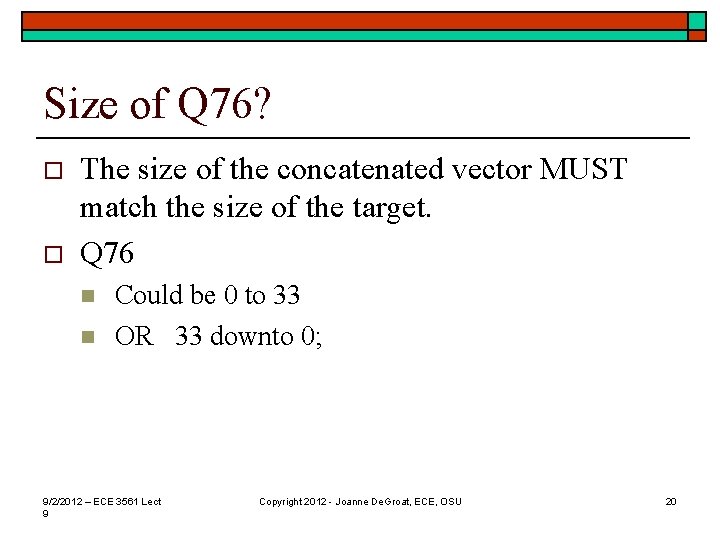

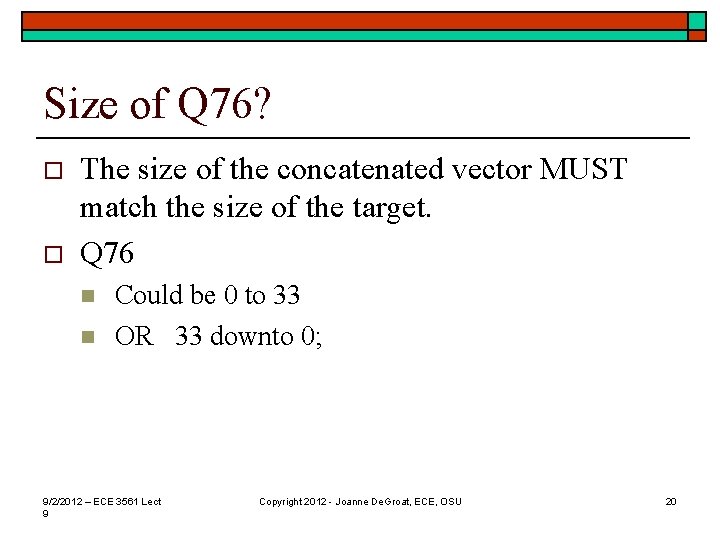

Size of Q 76? o o The size of the concatenated vector MUST match the size of the target. Q 76 n n Could be 0 to 33 OR 33 downto 0; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 20

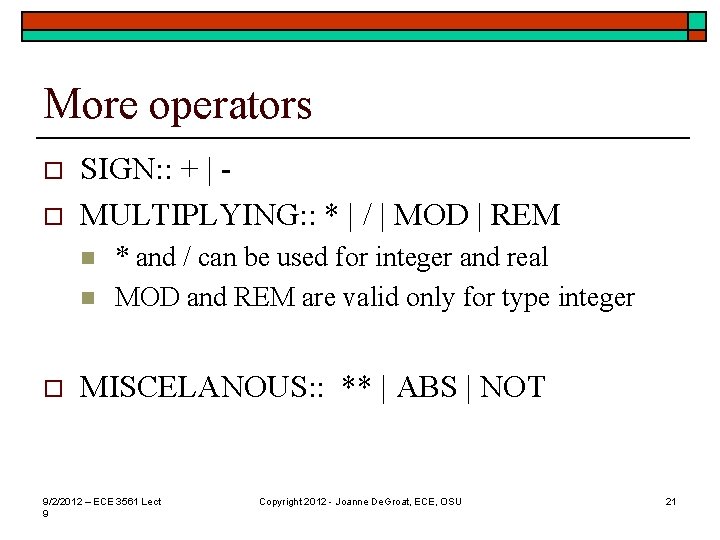

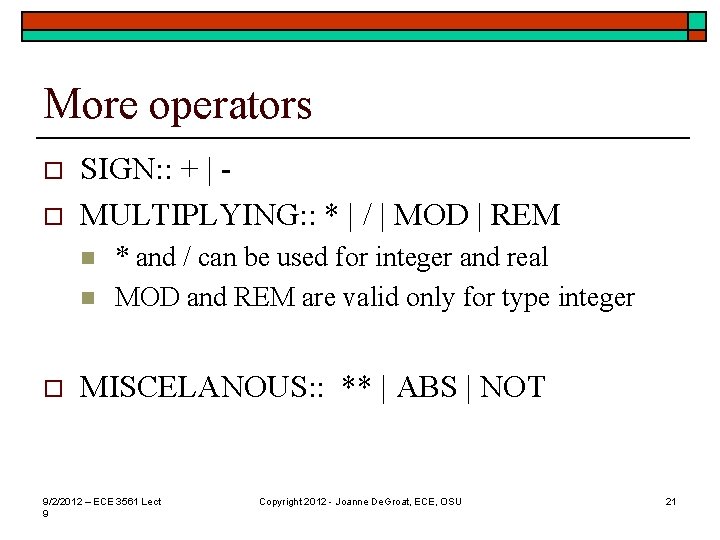

More operators o o SIGN: : + | MULTIPLYING: : * | / | MOD | REM n n o * and / can be used for integer and real MOD and REM are valid only for type integer MISCELANOUS: : ** | ABS | NOT 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 21

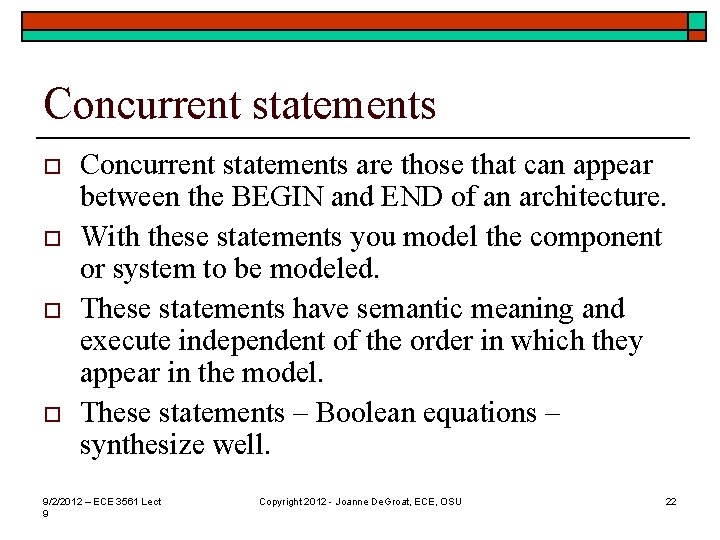

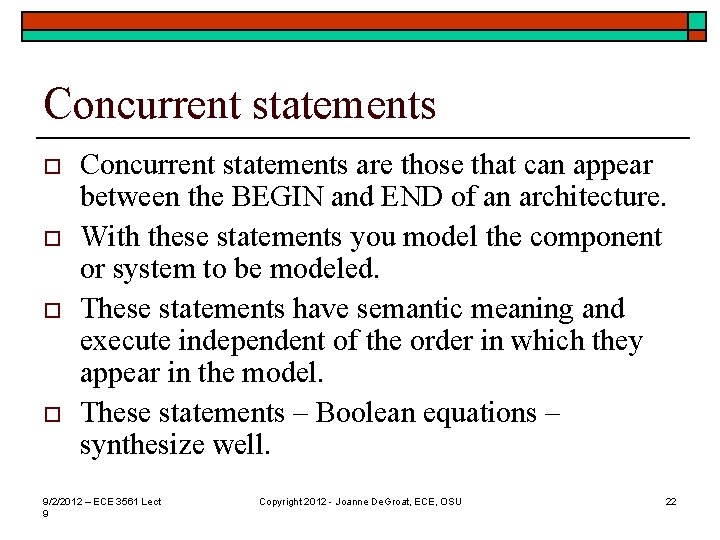

Concurrent statements o o Concurrent statements are those that can appear between the BEGIN and END of an architecture. With these statements you model the component or system to be modeled. These statements have semantic meaning and execute independent of the order in which they appear in the model. These statements – Boolean equations – synthesize well. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 22

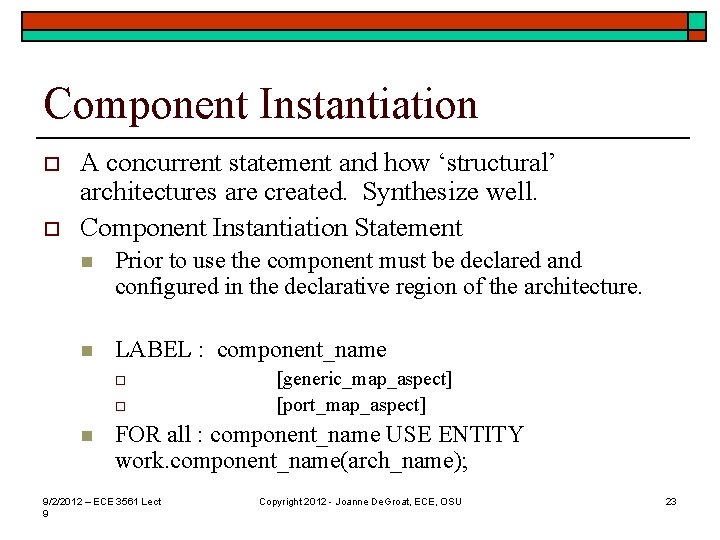

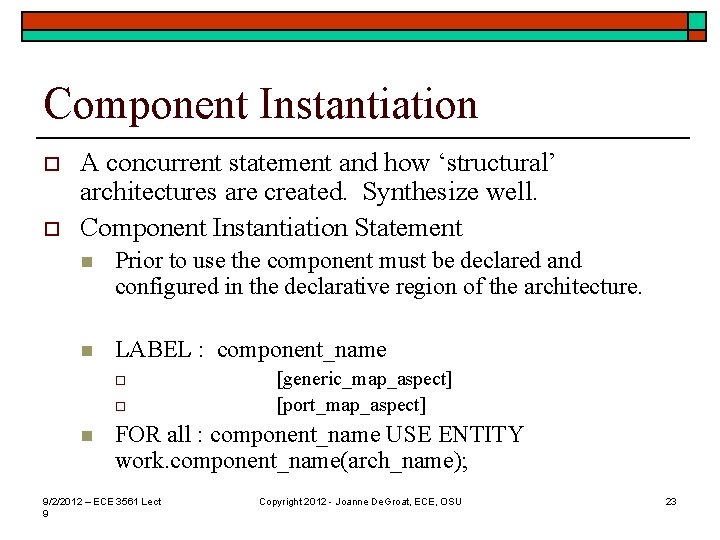

Component Instantiation o o A concurrent statement and how ‘structural’ architectures are created. Synthesize well. Component Instantiation Statement n Prior to use the component must be declared and configured in the declarative region of the architecture. n LABEL : component_name o o n [generic_map_aspect] [port_map_aspect] FOR all : component_name USE ENTITY work. component_name(arch_name); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 23

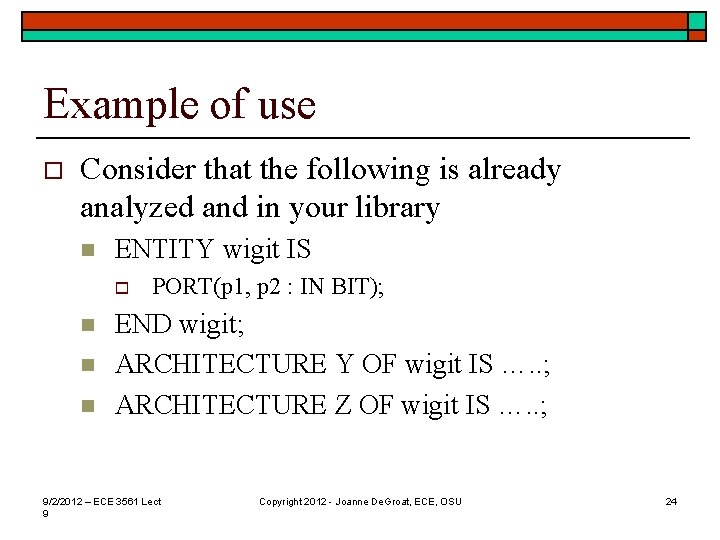

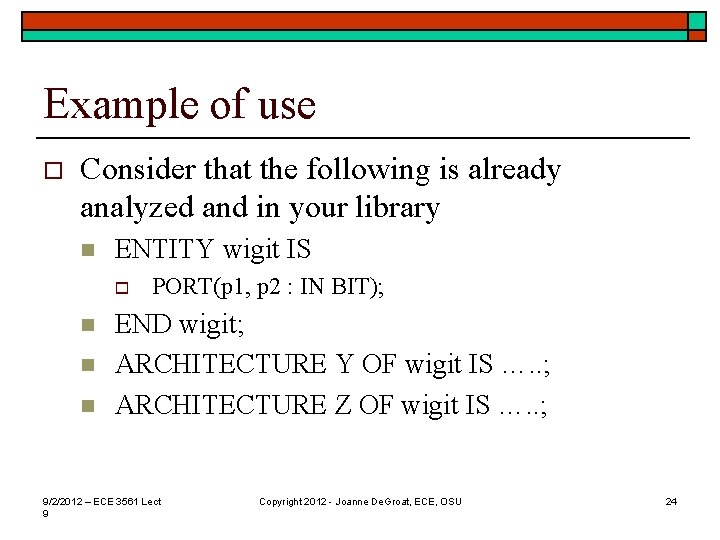

Example of use o Consider that the following is already analyzed and in your library n ENTITY wigit IS o n n n PORT(p 1, p 2 : IN BIT); END wigit; ARCHITECTURE Y OF wigit IS …. . ; ARCHITECTURE Z OF wigit IS …. . ; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 24

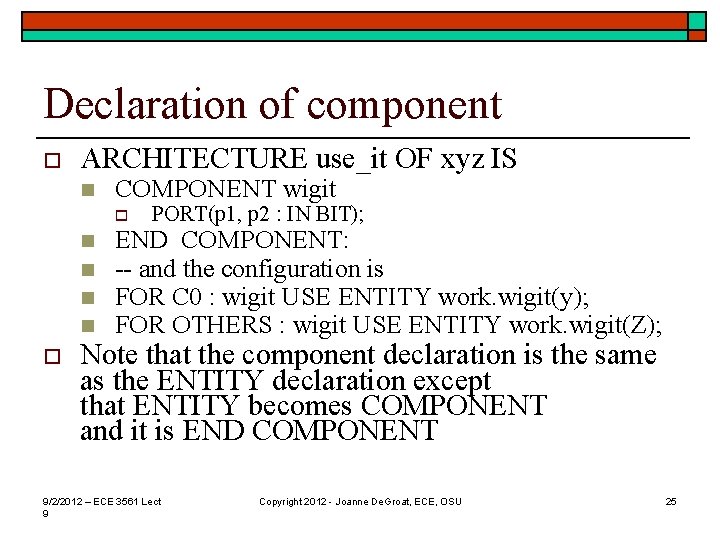

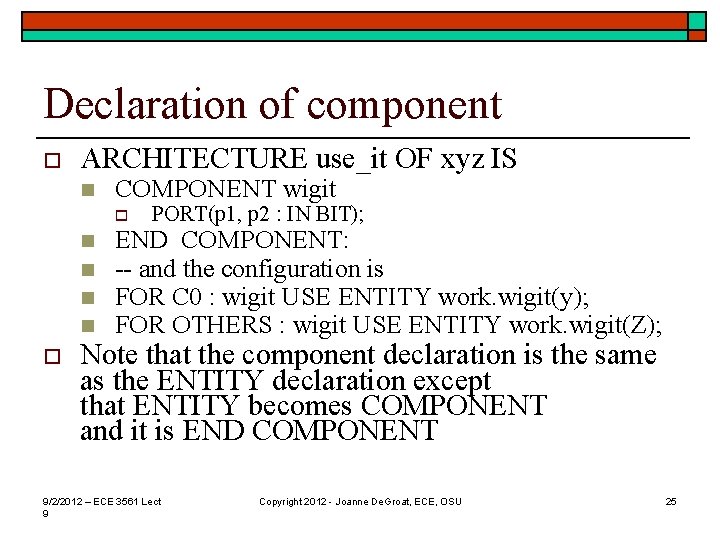

Declaration of component o ARCHITECTURE use_it OF xyz IS n COMPONENT wigit o n n o PORT(p 1, p 2 : IN BIT); END COMPONENT: -- and the configuration is FOR C 0 : wigit USE ENTITY work. wigit(y); FOR OTHERS : wigit USE ENTITY work. wigit(Z); Note that the component declaration is the same as the ENTITY declaration except that ENTITY becomes COMPONENT and it is END COMPONENT 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 25

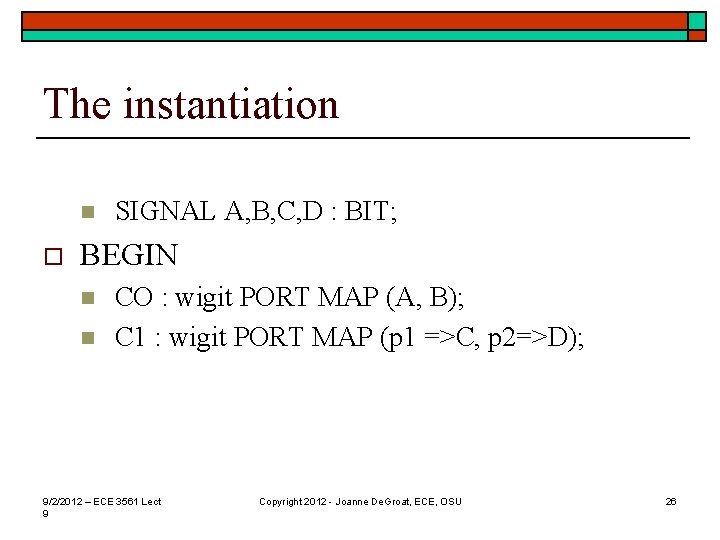

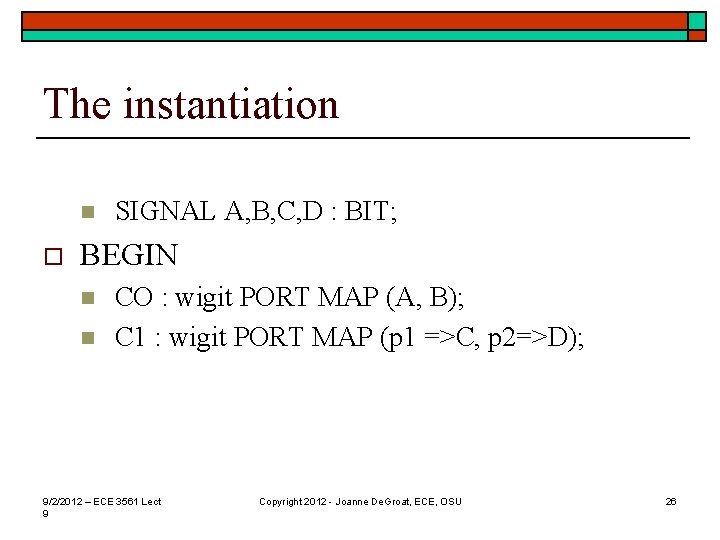

The instantiation n o SIGNAL A, B, C, D : BIT; BEGIN n n CO : wigit PORT MAP (A, B); C 1 : wigit PORT MAP (p 1 =>C, p 2=>D); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 26

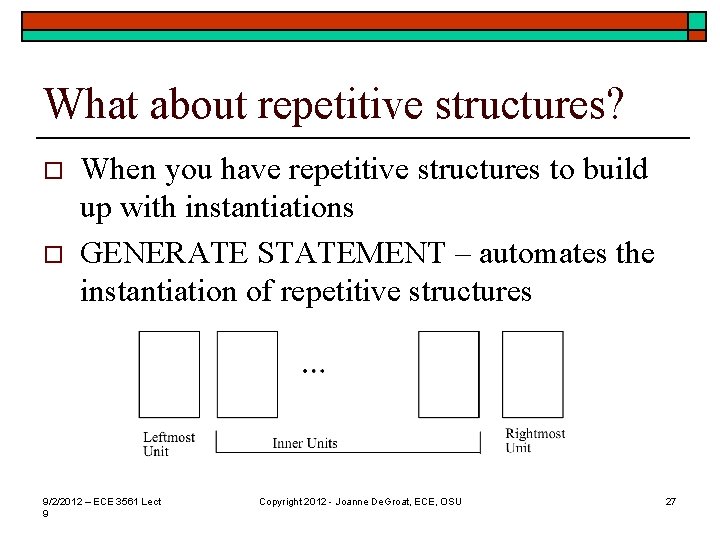

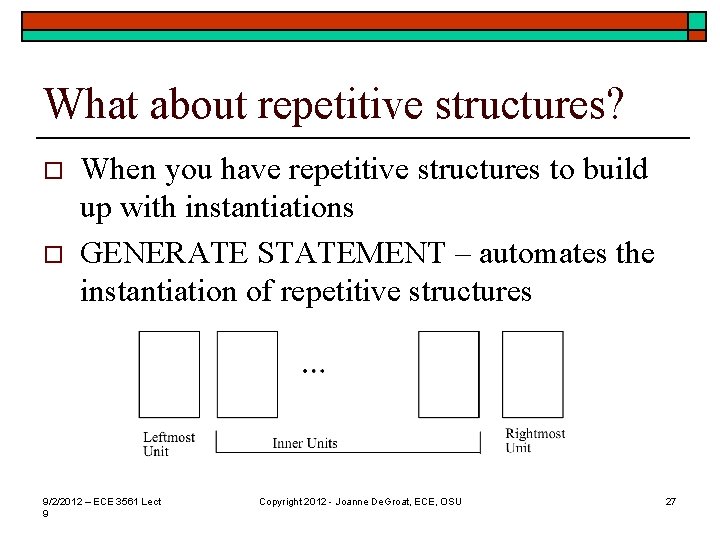

What about repetitive structures? o o When you have repetitive structures to build up with instantiations GENERATE STATEMENT – automates the instantiation of repetitive structures 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 27

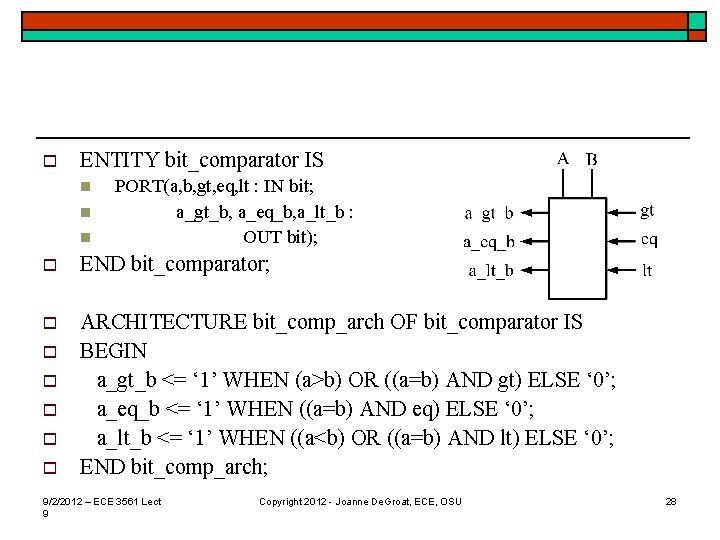

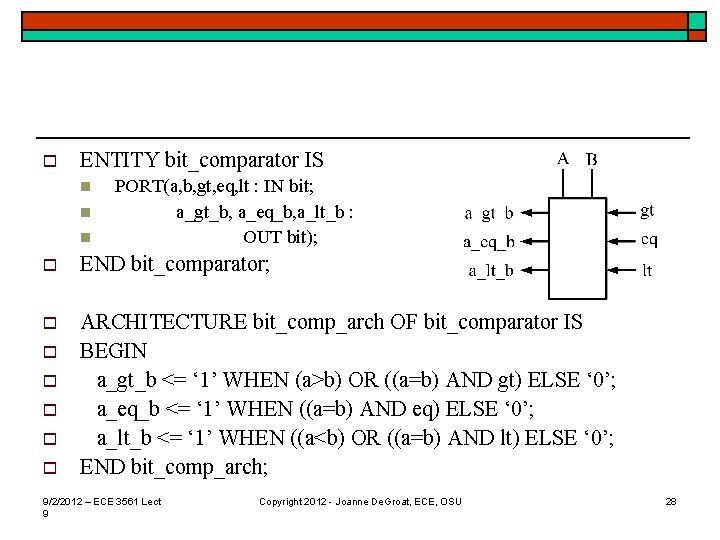

o ENTITY bit_comparator IS n n n PORT(a, b, gt, eq, lt : IN bit; a_gt_b, a_eq_b, a_lt_b : OUT bit); o END bit_comparator; o ARCHITECTURE bit_comp_arch OF bit_comparator IS BEGIN a_gt_b <= ‘ 1’ WHEN (a>b) OR ((a=b) AND gt) ELSE ‘ 0’; a_eq_b <= ‘ 1’ WHEN ((a=b) AND eq) ELSE ‘ 0’; a_lt_b <= ‘ 1’ WHEN ((a<b) OR ((a=b) AND lt) ELSE ‘ 0’; END bit_comp_arch; o o o 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 28

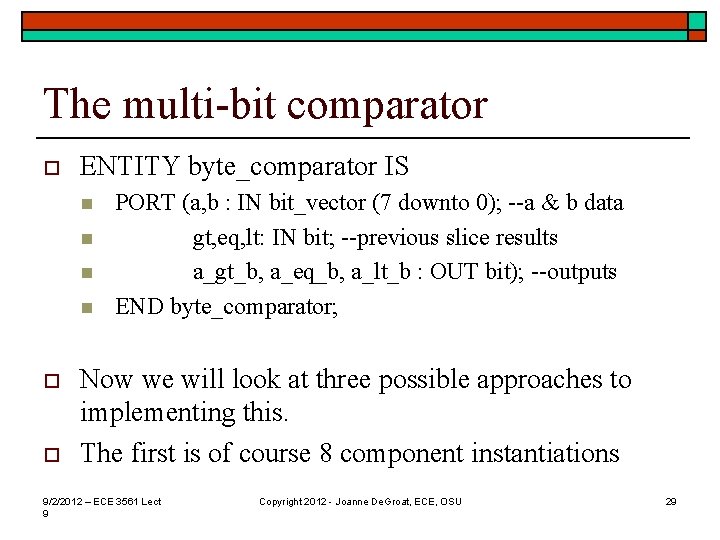

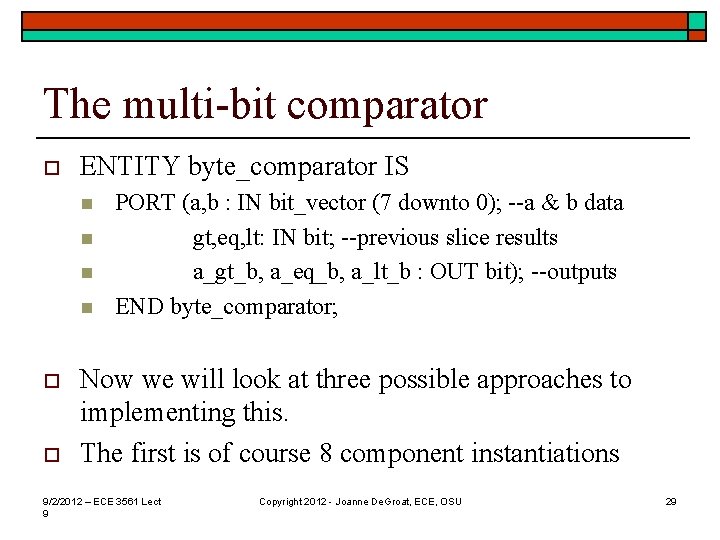

The multi-bit comparator o ENTITY byte_comparator IS n n o o PORT (a, b : IN bit_vector (7 downto 0); --a & b data gt, eq, lt: IN bit; --previous slice results a_gt_b, a_eq_b, a_lt_b : OUT bit); --outputs END byte_comparator; Now we will look at three possible approaches to implementing this. The first is of course 8 component instantiations 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 29

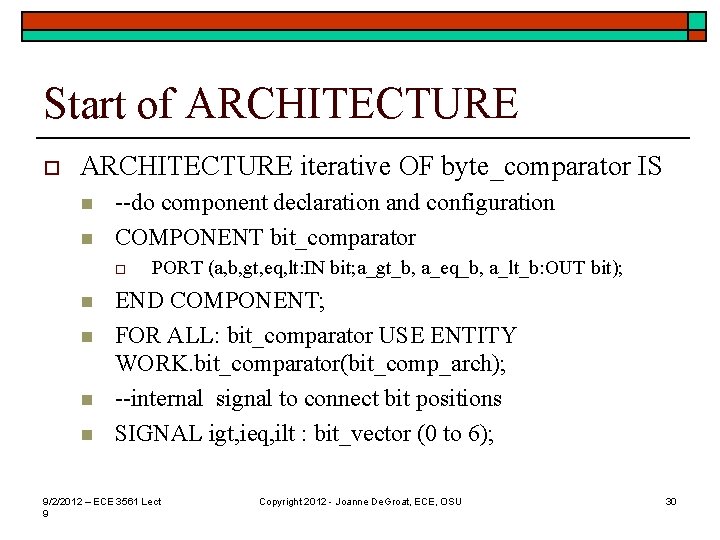

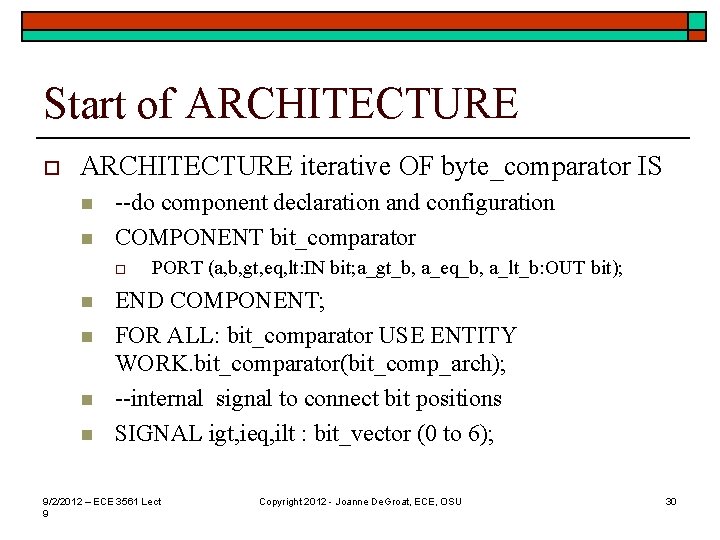

Start of ARCHITECTURE o ARCHITECTURE iterative OF byte_comparator IS n n --do component declaration and configuration COMPONENT bit_comparator o n n PORT (a, b, gt, eq, lt: IN bit; a_gt_b, a_eq_b, a_lt_b: OUT bit); END COMPONENT; FOR ALL: bit_comparator USE ENTITY WORK. bit_comparator(bit_comp_arch); --internal signal to connect bit positions SIGNAL igt, ieq, ilt : bit_vector (0 to 6); 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 30

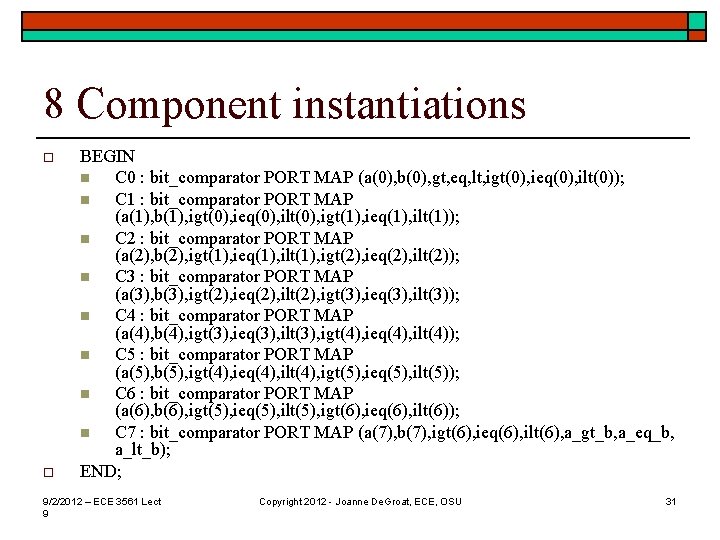

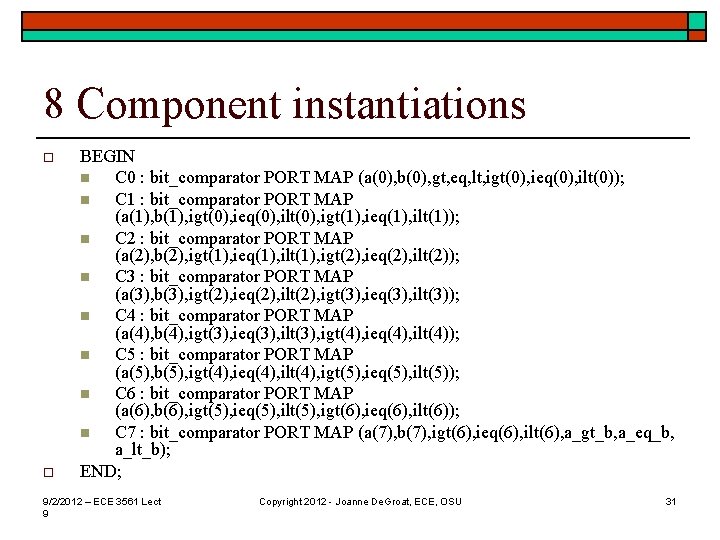

8 Component instantiations o o BEGIN n C 0 : bit_comparator PORT MAP (a(0), b(0), gt, eq, lt, igt(0), ieq(0), ilt(0)); n C 1 : bit_comparator PORT MAP (a(1), b(1), igt(0), ieq(0), ilt(0), igt(1), ieq(1), ilt(1)); n C 2 : bit_comparator PORT MAP (a(2), b(2), igt(1), ieq(1), ilt(1), igt(2), ieq(2), ilt(2)); n C 3 : bit_comparator PORT MAP (a(3), b(3), igt(2), ieq(2), ilt(2), igt(3), ieq(3), ilt(3)); n C 4 : bit_comparator PORT MAP (a(4), b(4), igt(3), ieq(3), ilt(3), igt(4), ieq(4), ilt(4)); n C 5 : bit_comparator PORT MAP (a(5), b(5), igt(4), ieq(4), ilt(4), igt(5), ieq(5), ilt(5)); n C 6 : bit_comparator PORT MAP (a(6), b(6), igt(5), ieq(5), ilt(5), igt(6), ieq(6), ilt(6)); n C 7 : bit_comparator PORT MAP (a(7), b(7), igt(6), ieq(6), ilt(6), a_gt_b, a_eq_b, a_lt_b); END; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 31

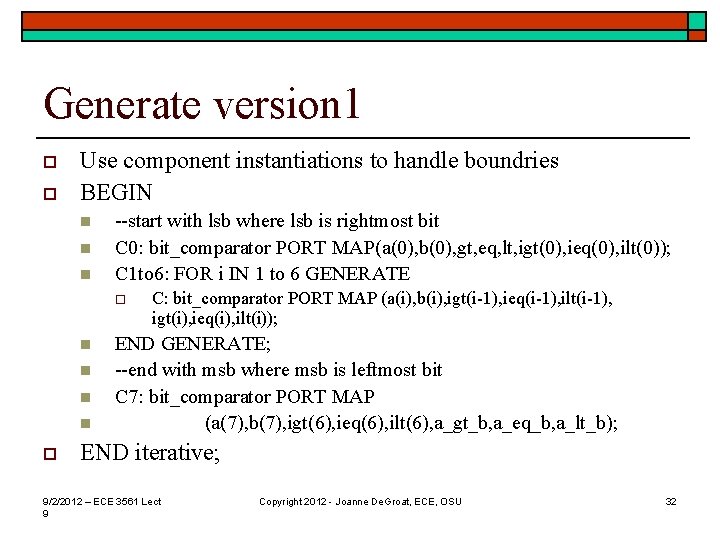

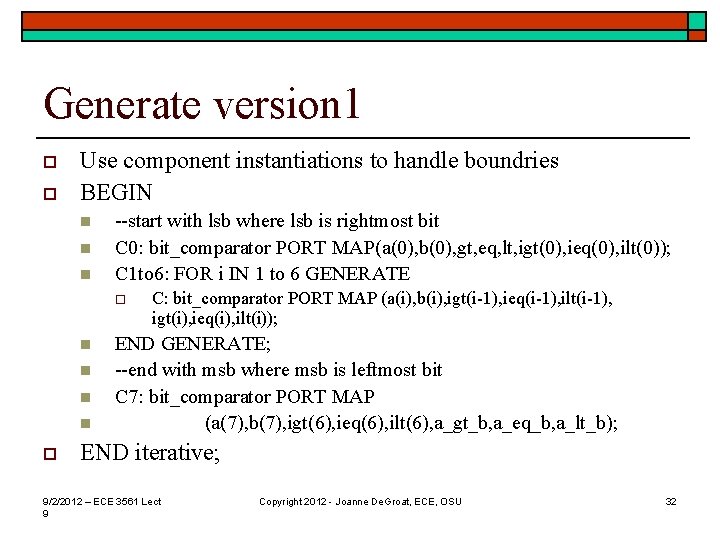

Generate version 1 o o Use component instantiations to handle boundries BEGIN n n n --start with lsb where lsb is rightmost bit C 0: bit_comparator PORT MAP(a(0), b(0), gt, eq, lt, igt(0), ieq(0), ilt(0)); C 1 to 6: FOR i IN 1 to 6 GENERATE o n n o C: bit_comparator PORT MAP (a(i), b(i), igt(i-1), ieq(i-1), ilt(i-1), igt(i), ieq(i), ilt(i)); END GENERATE; --end with msb where msb is leftmost bit C 7: bit_comparator PORT MAP (a(7), b(7), igt(6), ieq(6), ilt(6), a_gt_b, a_eq_b, a_lt_b); END iterative; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 32

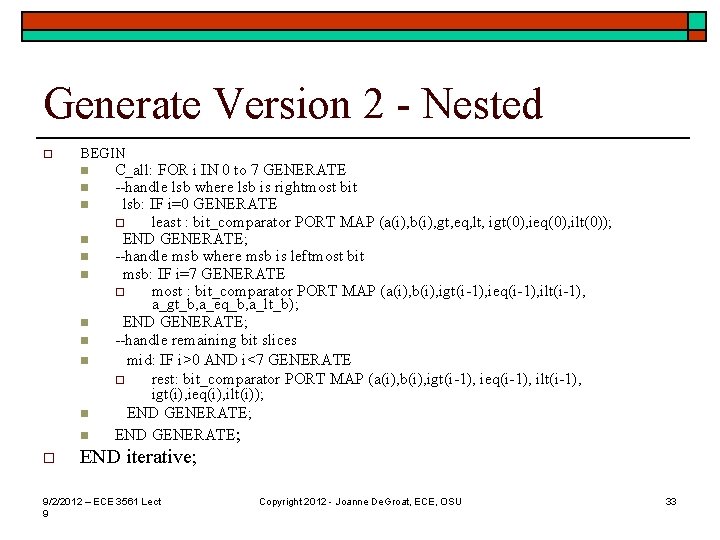

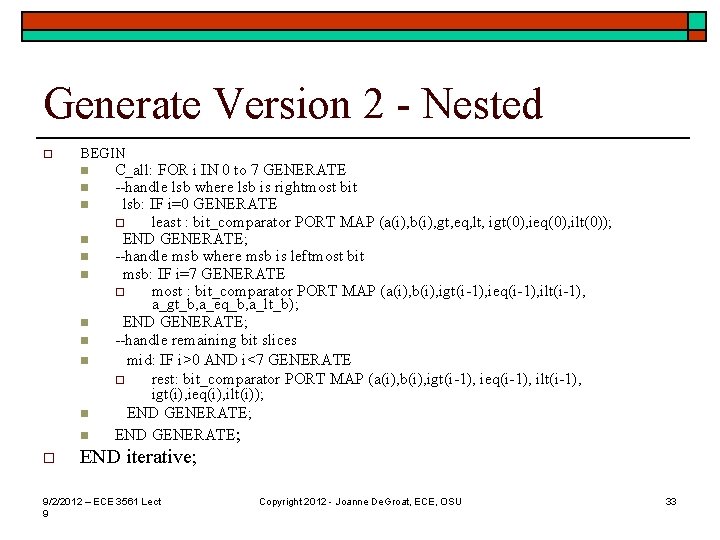

Generate Version 2 - Nested o BEGIN n n n o C_all: FOR i IN 0 to 7 GENERATE --handle lsb where lsb is rightmost bit lsb: IF i=0 GENERATE o least : bit_comparator PORT MAP (a(i), b(i), gt, eq, lt, igt(0), ieq(0), ilt(0)); END GENERATE; --handle msb where msb is leftmost bit msb: IF i=7 GENERATE o most : bit_comparator PORT MAP (a(i), b(i), igt(i-1), ieq(i-1), ilt(i-1), a_gt_b, a_eq_b, a_lt_b); END GENERATE; --handle remaining bit slices mid: IF i>0 AND i<7 GENERATE o rest: bit_comparator PORT MAP (a(i), b(i), igt(i-1), ieq(i-1), ilt(i-1), igt(i), ieq(i), ilt(i)); END GENERATE; END iterative; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 33

Lecture summary o o VHDL Data Types VHDL concurrent language statements VHDL generate VHDL concurrent statements synthesize well. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 34