Kuliah Rangkaian Digital Kuliah 7 Unit Aritmatika Teknik

- Slides: 17

Kuliah Rangkaian Digital Kuliah 7: Unit Aritmatika Teknik Komputer Universitas Gunadarma 1

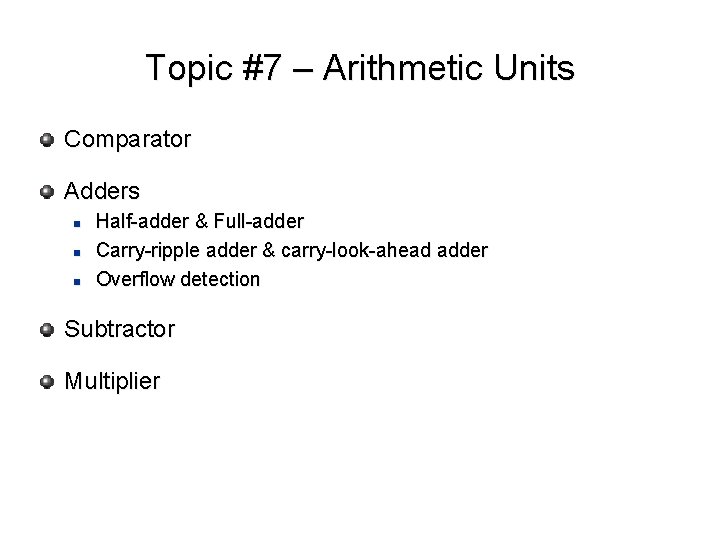

Topic #7 – Arithmetic Units Comparator Adders n n n Half-adder & Full-adder Carry-ripple adder & carry-look-ahead adder Overflow detection Subtractor Multiplier

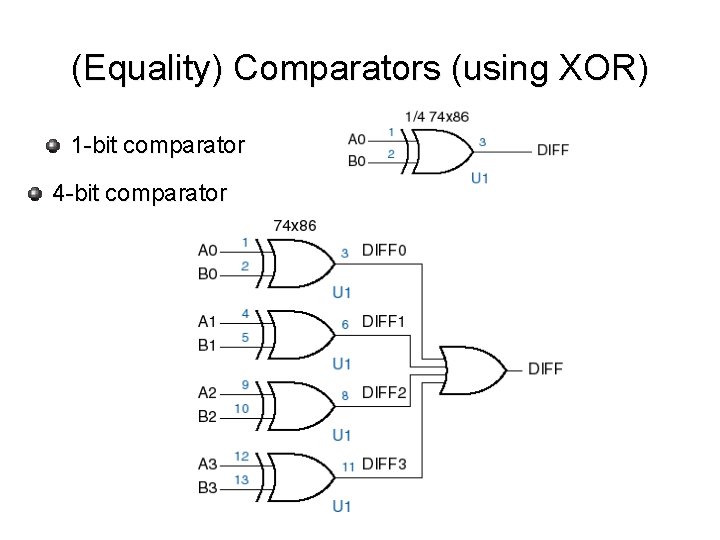

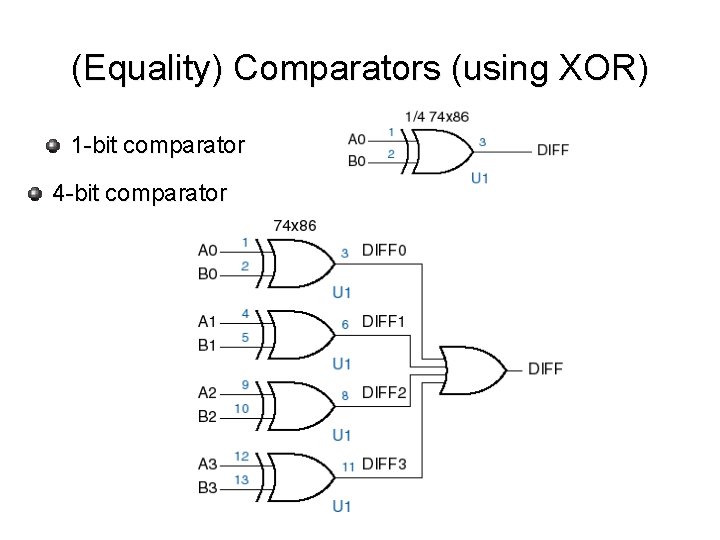

(Equality) Comparators (using XOR) 1 -bit comparator 4 -bit comparator

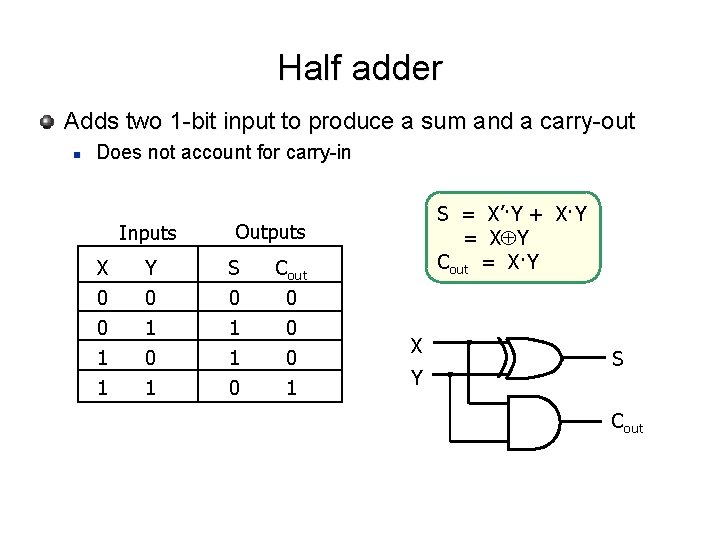

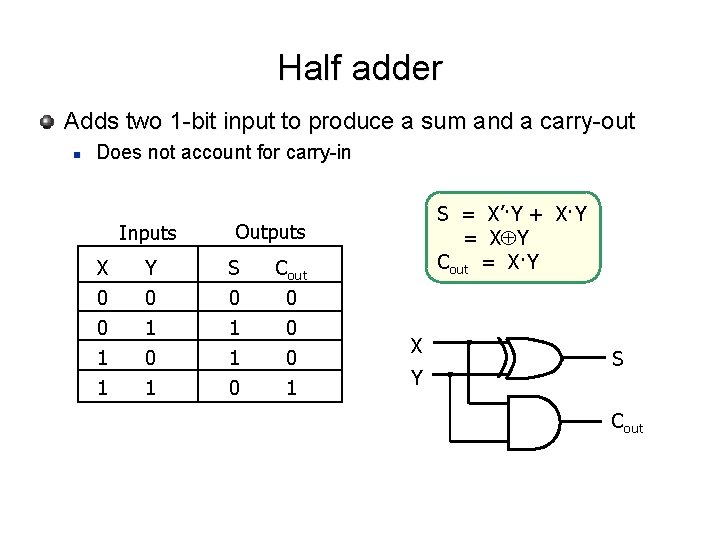

Half adder Adds two 1 -bit input to produce a sum and a carry-out n Does not account for carry-in Inputs X 0 0 1 1 Y 0 1 S = X’·Y + X·Y = X Y Cout = X·Y Outputs S 0 1 1 0 Cout 0 0 0 1 X Y S Cout

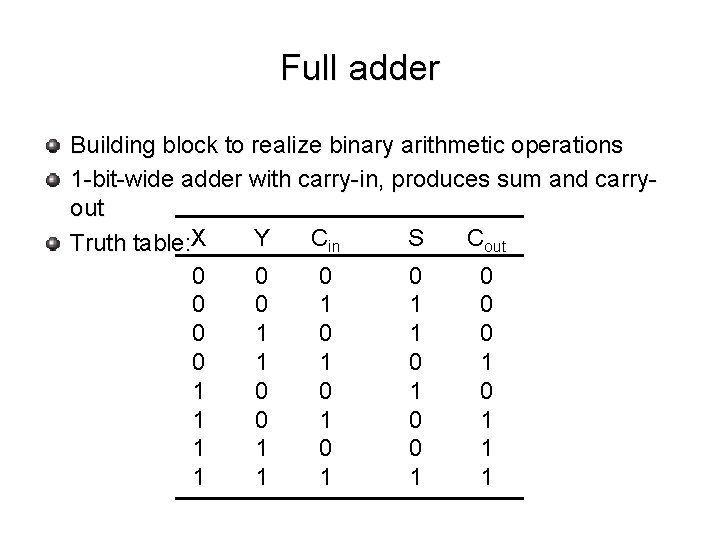

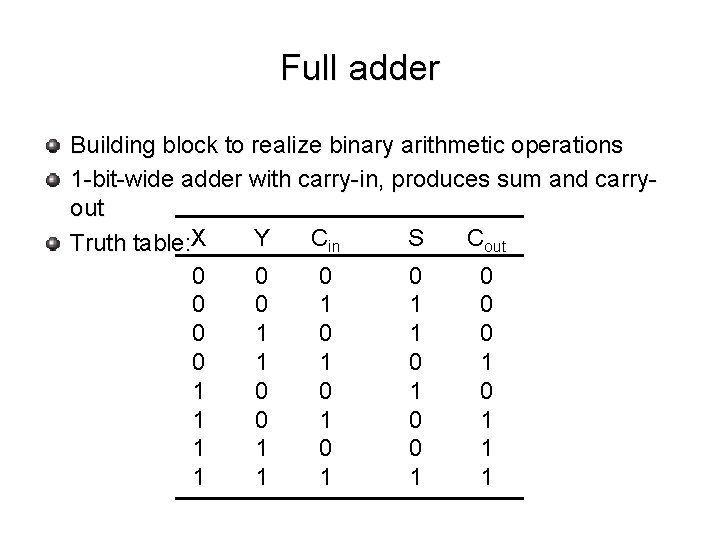

Full adder Building block to realize binary arithmetic operations 1 -bit-wide adder with carry-in, produces sum and carryout Y Cin S Cout Truth table: X 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1

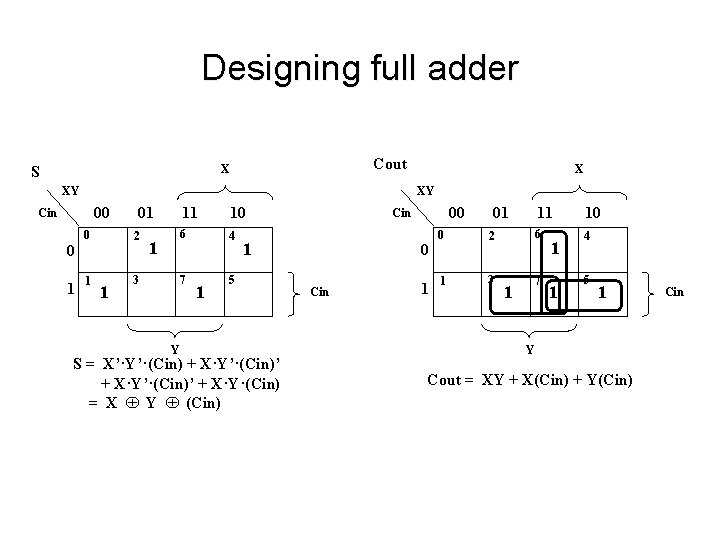

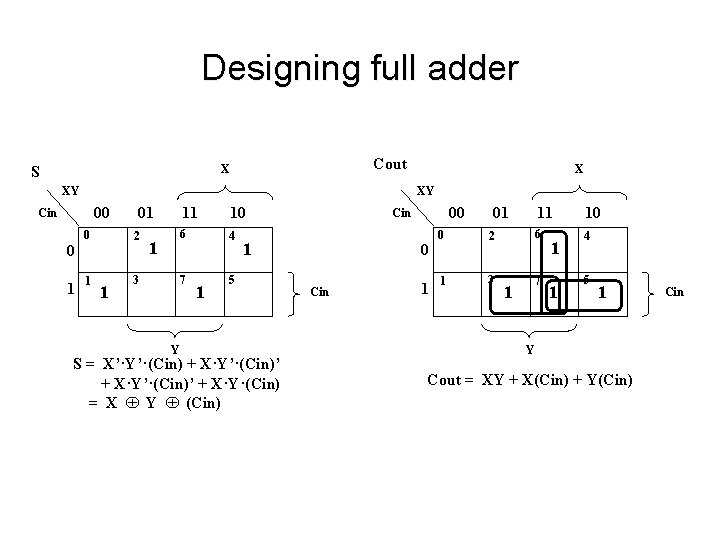

Designing full adder Cout X S XY XY 00 Cin 0 1 X 0 1 01 2 1 1 3 11 10 6 4 7 Y 1 1 5 S = X’·Y’·(Cin) + X·Y’·(Cin)’ + X·Y·(Cin) = X Y (Cin) 00 Cin 1 01 0 2 1 3 11 10 6 4 7 1 1 1 5 1 Y Cout = XY + X(Cin) + Y(Cin) Cin

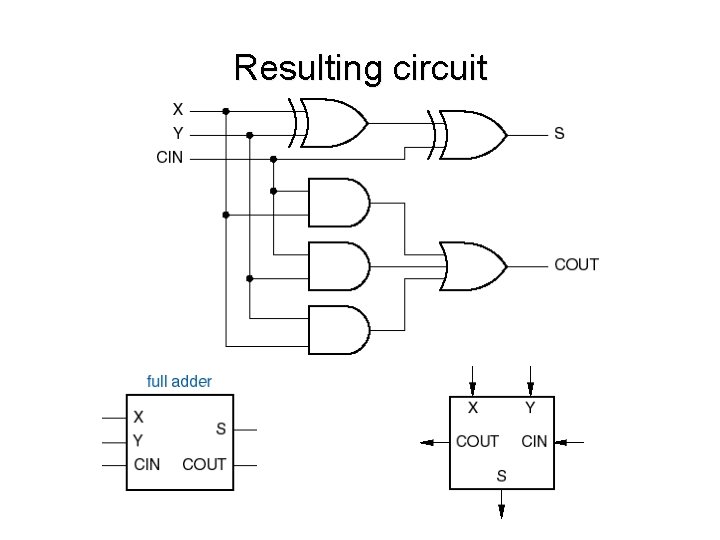

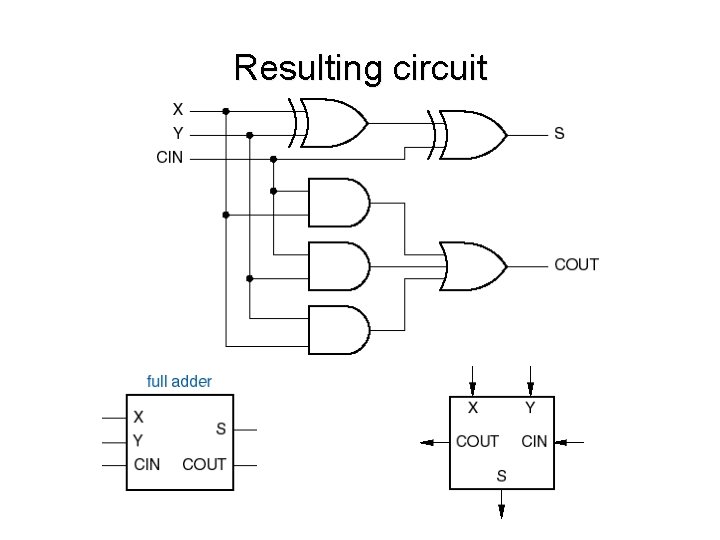

Resulting circuit

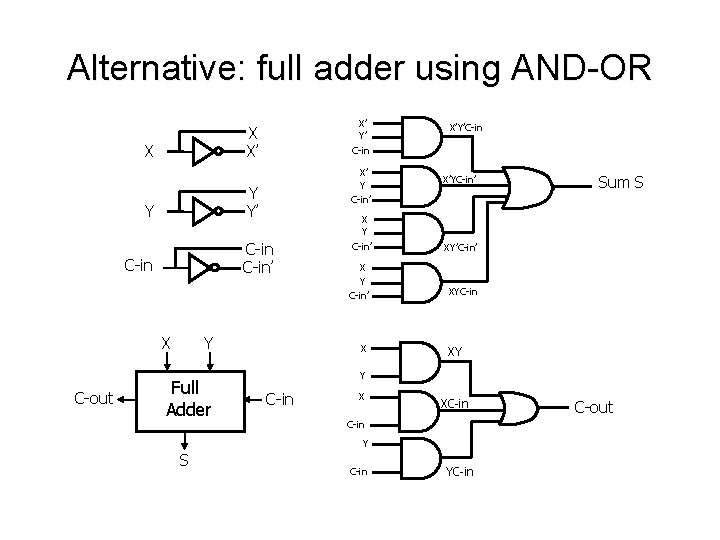

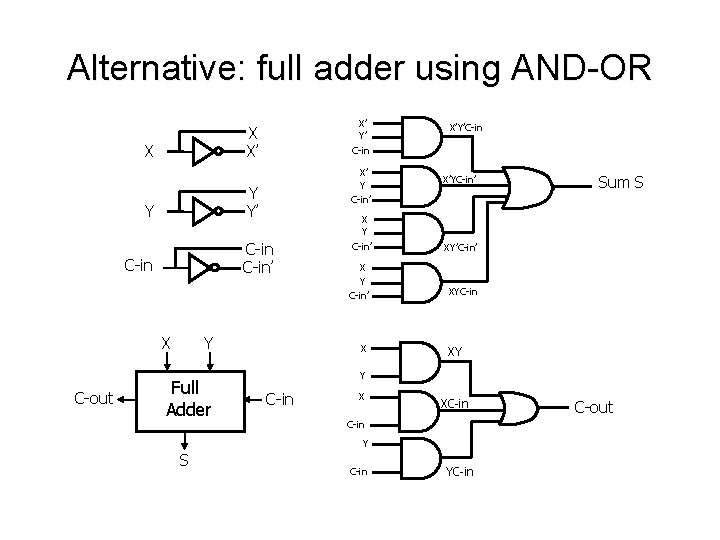

Alternative: full adder using AND-OR X X’ Y C-in’ Y Y’ Y X Y Full Adder X’Y’C-in X’YC-in’ X Y C-in’ X XY’C-in’ XYC-in XY Y C-in X XC-in Y S Sum S X Y C-in’ C-in C-out X’ Y’ C-in X X’ C-in YC-in C-out

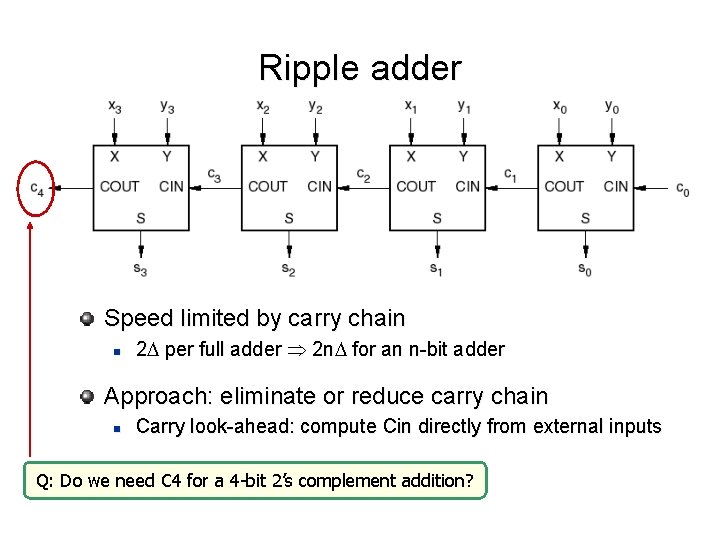

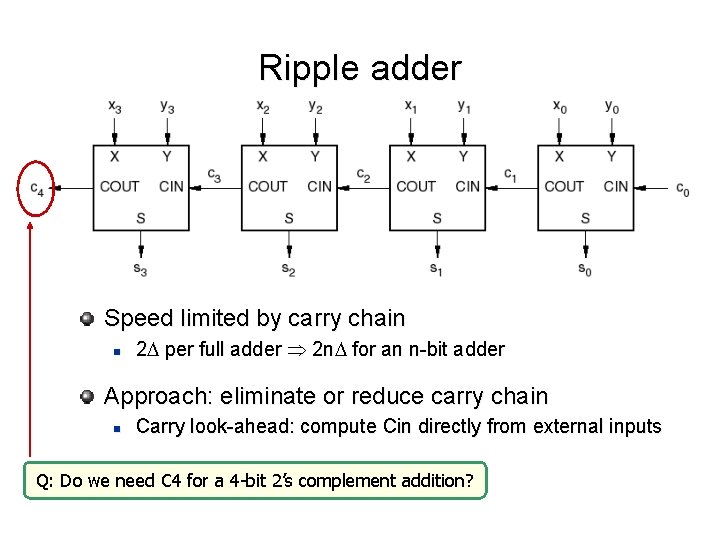

Ripple adder Speed limited by carry chain n 2 per full adder 2 n for an n-bit adder Approach: eliminate or reduce carry chain n Carry look-ahead: compute Cin directly from external inputs Q: Do we need C 4 for a 4 -bit 2’s complement addition?

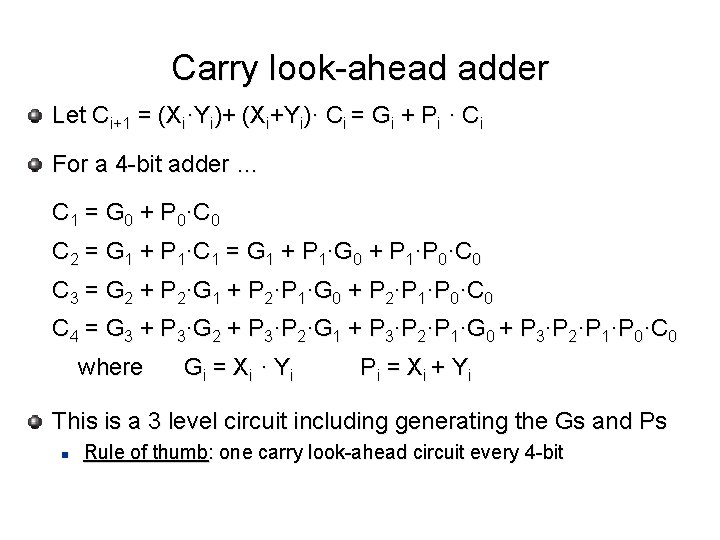

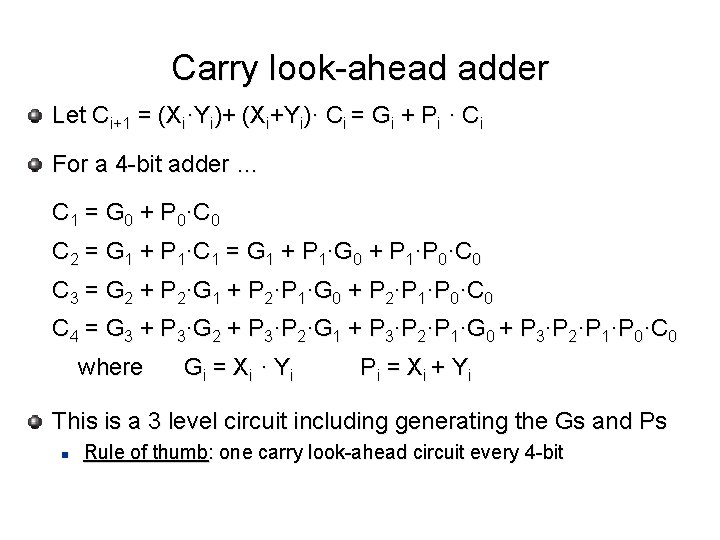

Carry look-ahead adder Let Ci+1 = (Xi·Yi)+ (Xi+Yi)· Ci = Gi + Pi · Ci For a 4 -bit adder … C 1 = G 0 + P 0·C 0 C 2 = G 1 + P 1·C 1 = G 1 + P 1·G 0 + P 1·P 0·C 0 C 3 = G 2 + P 2·G 1 + P 2·P 1·G 0 + P 2·P 1·P 0·C 0 C 4 = G 3 + P 3·G 2 + P 3·P 2·G 1 + P 3·P 2·P 1·G 0 + P 3·P 2·P 1·P 0·C 0 where Gi = X i · Y i P i = Xi + Yi This is a 3 level circuit including generating the Gs and Ps n Rule of thumb: one carry look-ahead circuit every 4 -bit

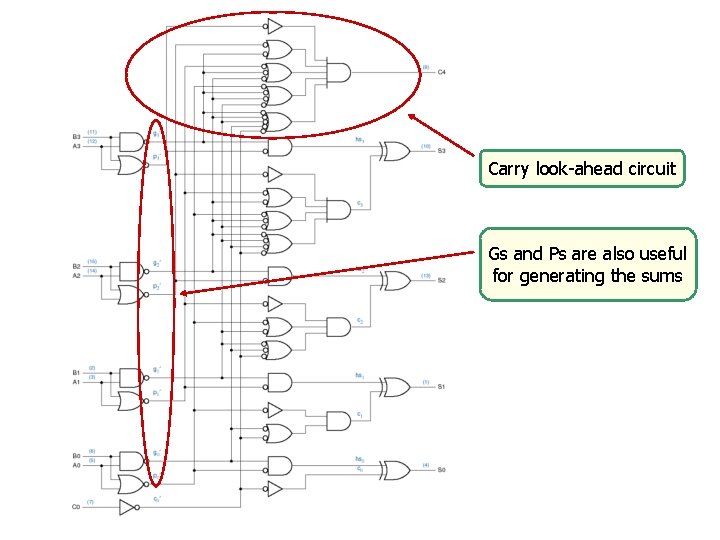

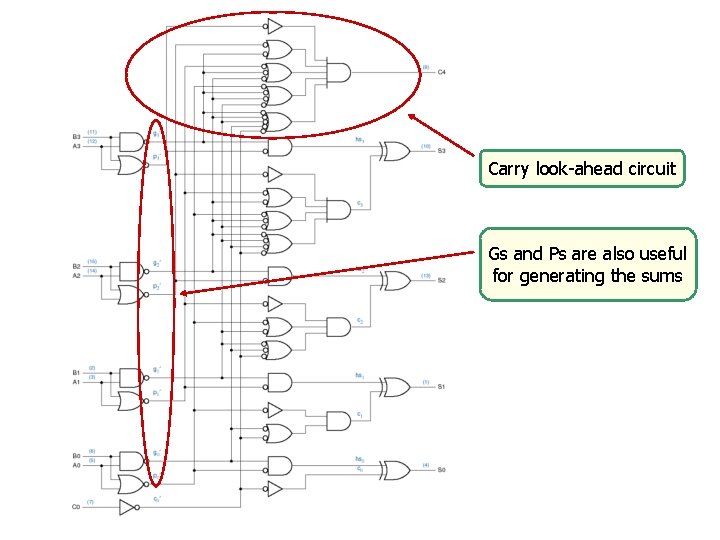

Carry look-ahead circuit Gs and Ps are also useful for generating the sums

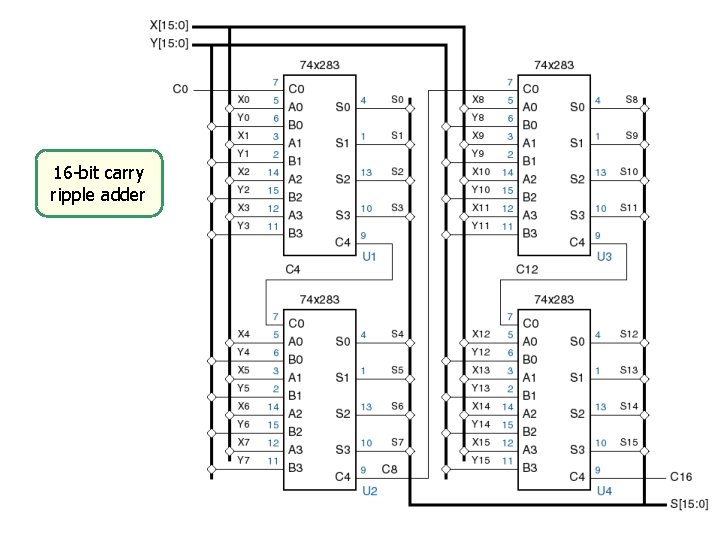

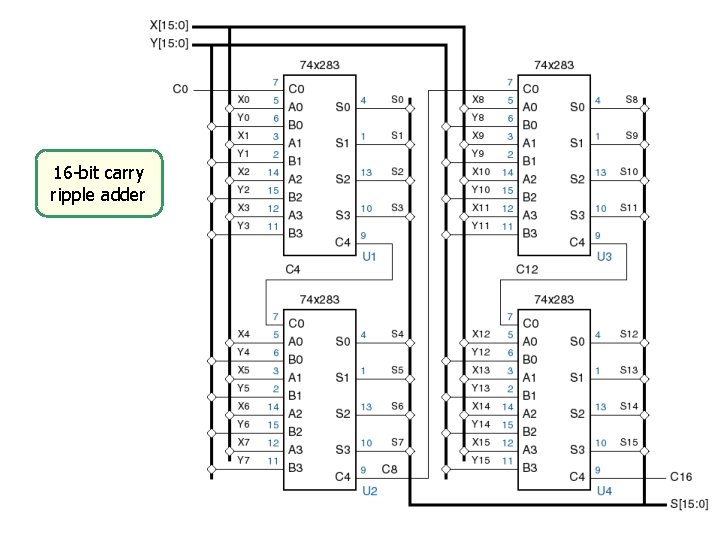

16 -bit carry ripple adder

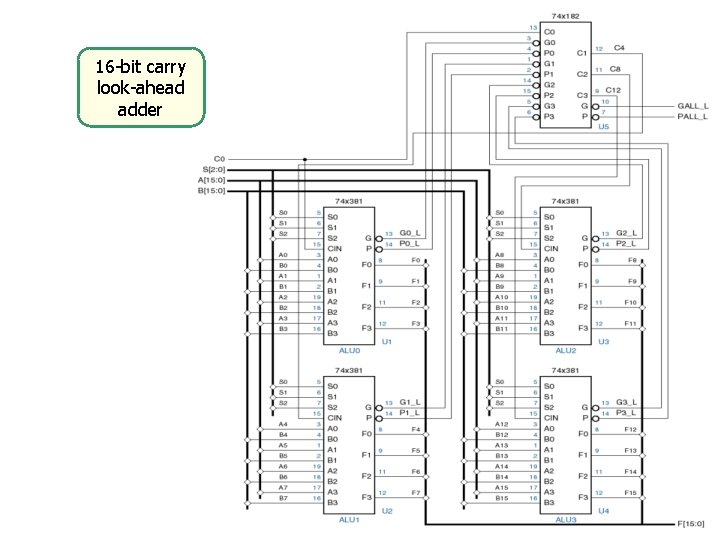

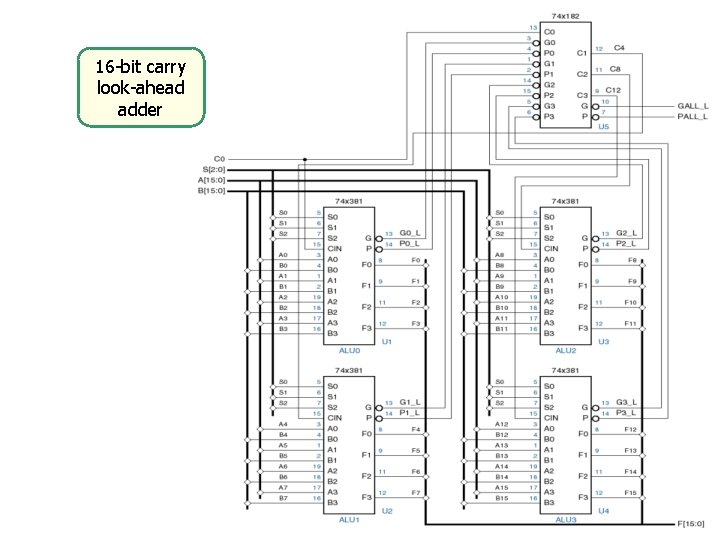

16 -bit carry look-ahead adder

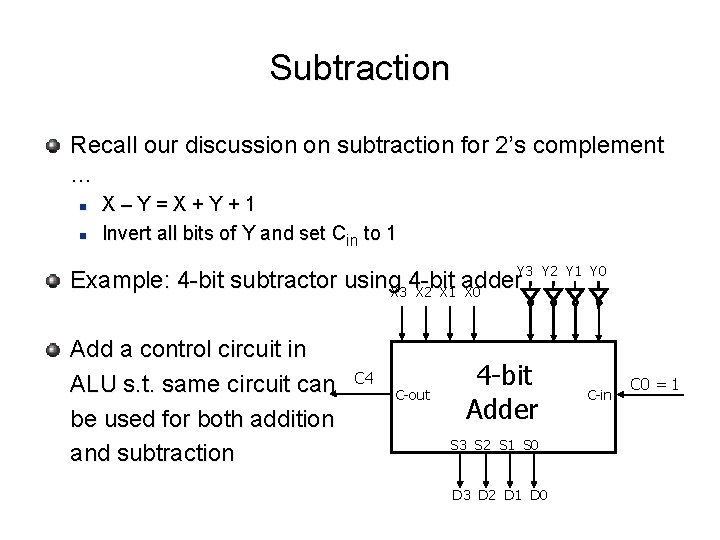

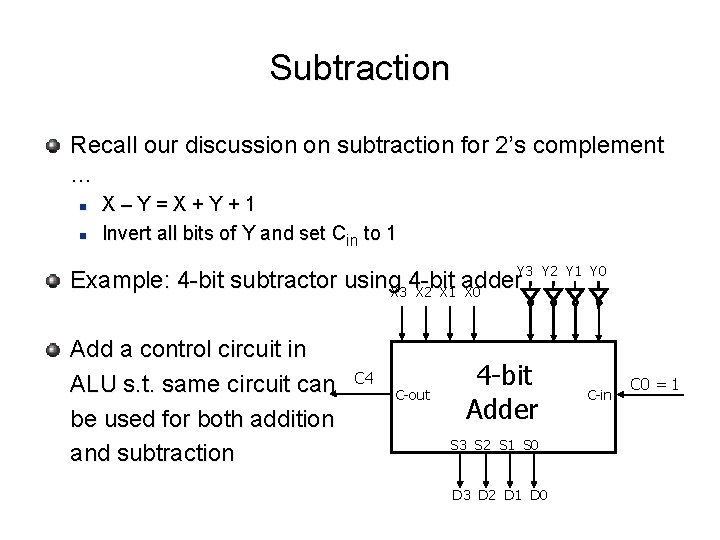

Subtraction Recall our discussion on subtraction for 2’s complement … n n X–Y=X+Y+1 Invert all bits of Y and set Cin to 1 Y 3 Y 2 Y 1 Y 0 Example: 4 -bit subtractor using. X 34 -bit adder X 2 X 1 X 0 Add a control circuit in ALU s. t. same circuit can be used for both addition and subtraction C 4 C-out 4 -bit Adder S 3 S 2 S 1 S 0 D 3 D 2 D 1 D 0 C-in C 0 = 1

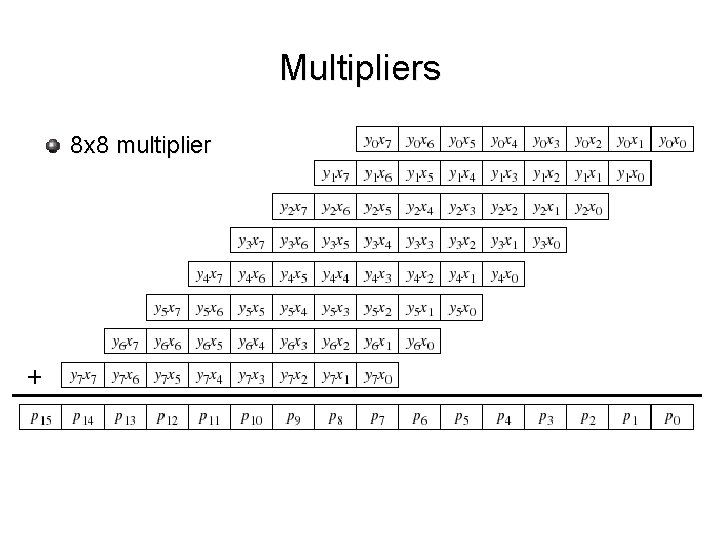

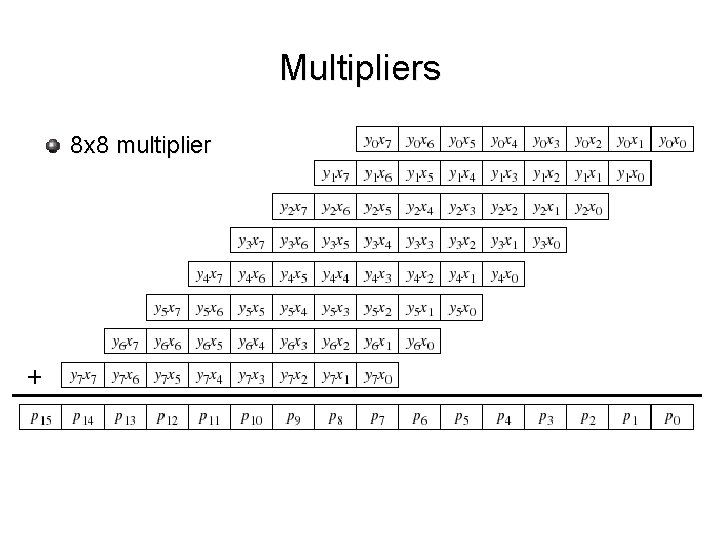

Multipliers 8 x 8 multiplier

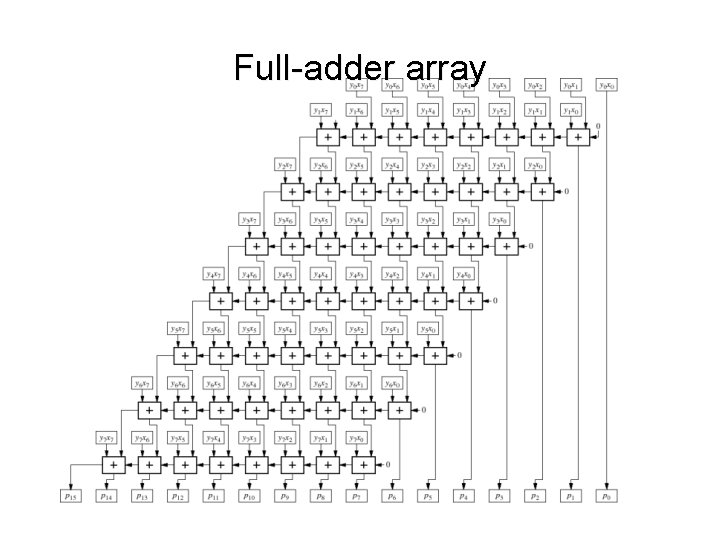

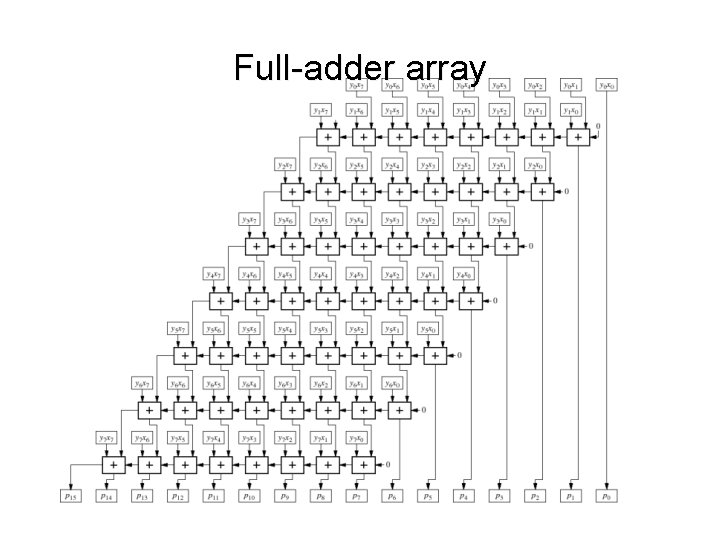

Full-adder array

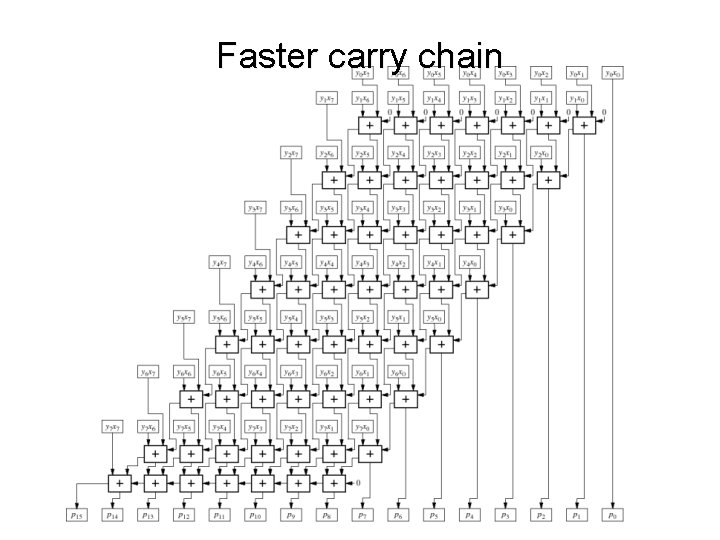

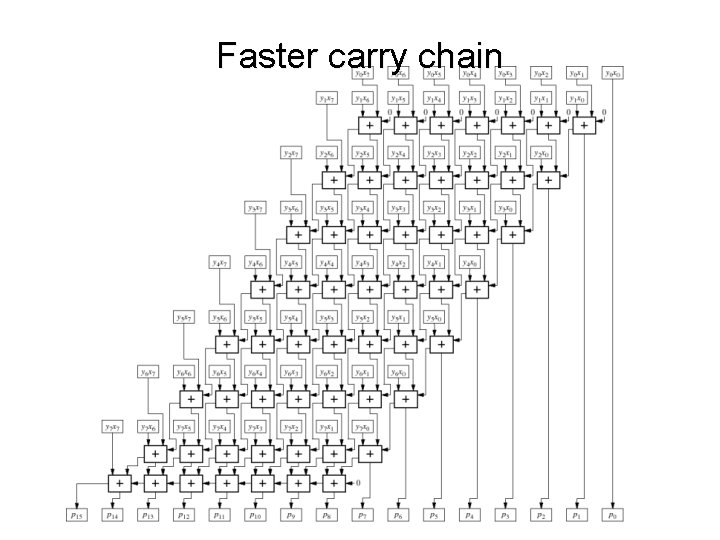

Faster carry chain