Kuliah Rangkaian Digital Kuliah 6 Blok Pembangun Logika

Kuliah Rangkaian Digital Kuliah 6: Blok Pembangun Logika Kombinasional Teknik Komputer Universitas Gunadarma 1

Topic #6 – Combinational Logic Building Blocks Tri-state buffers XOR & XNOR Decoders Encoders Multiplexers Demultiplexers 2

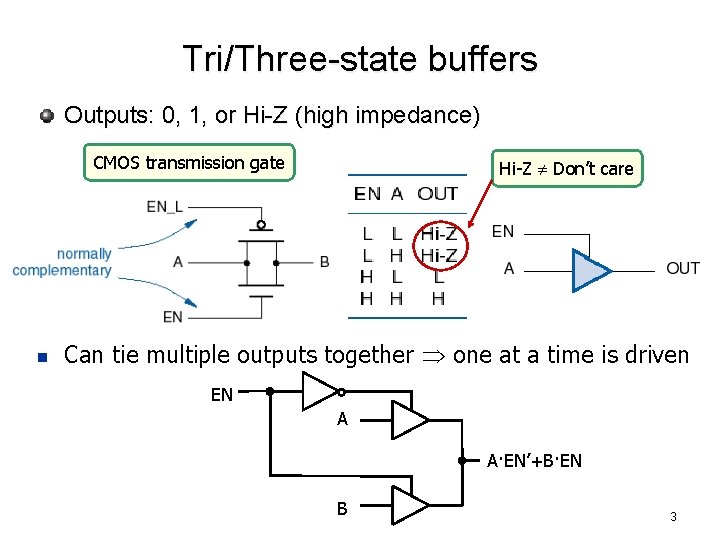

Tri/Three-state buffers Outputs: 0, 1, or Hi-Z (high impedance) CMOS transmission gate n Hi-Z Don’t care Can tie multiple outputs together one at a time is driven EN A A·EN’+B·EN B 3

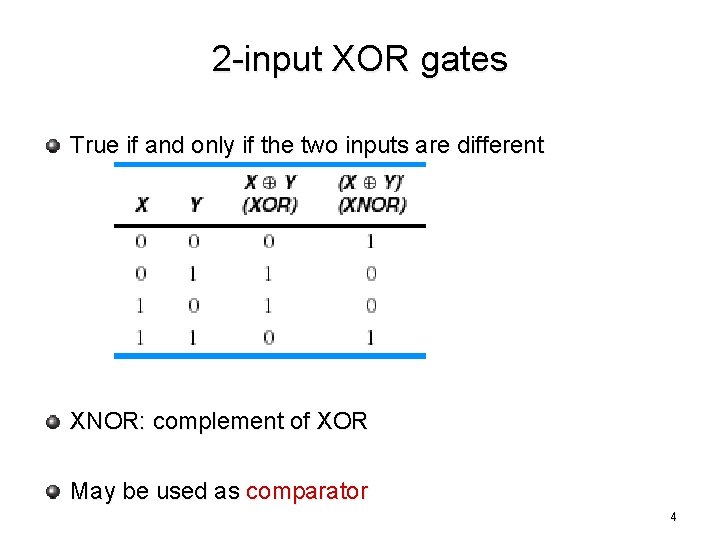

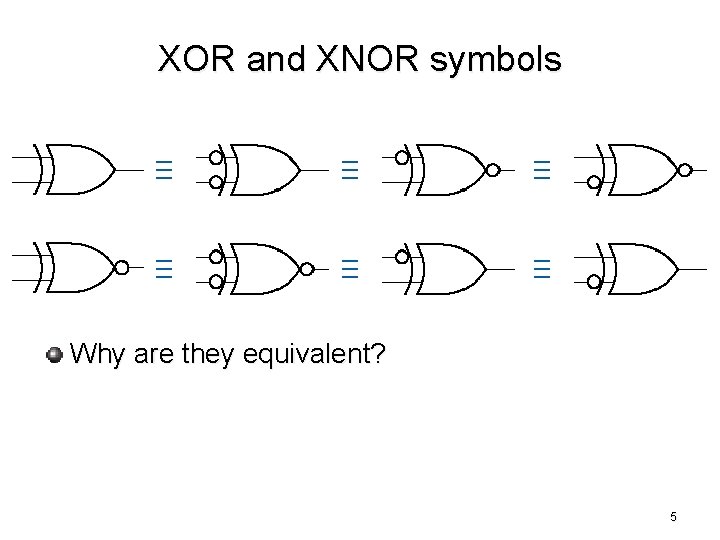

2 -input XOR gates True if and only if the two inputs are different XNOR: complement of XOR May be used as comparator 4

XOR and XNOR symbols Why are they equivalent? 5

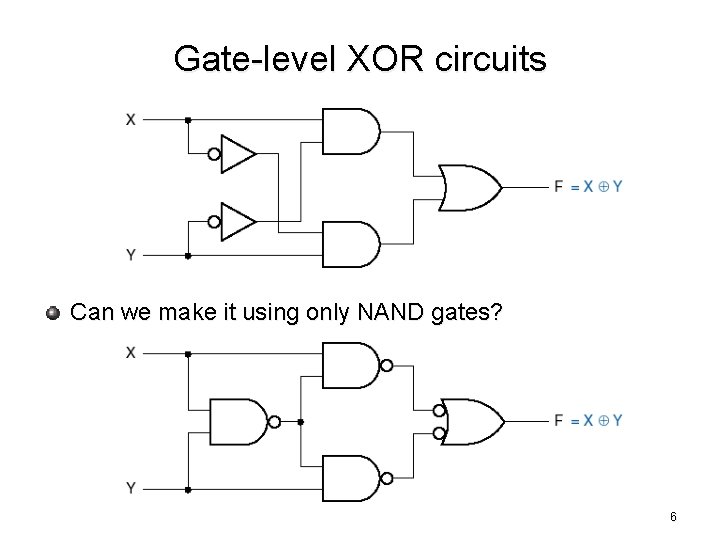

Gate-level XOR circuits Can we make it using only NAND gates? 6

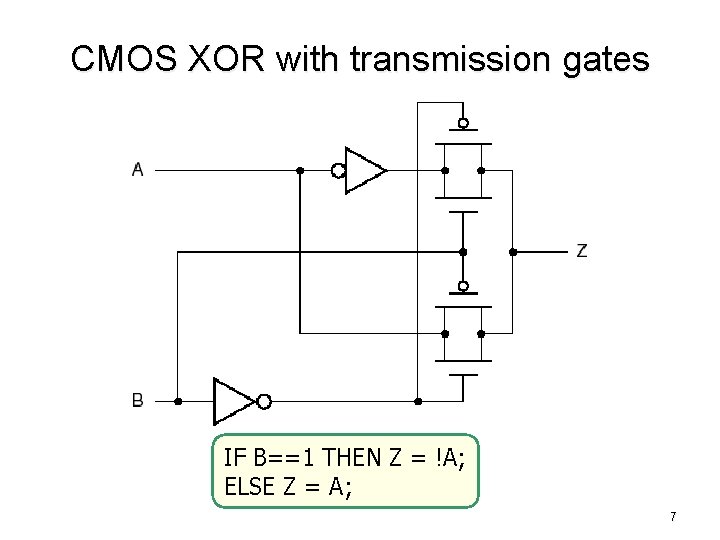

CMOS XOR with transmission gates IF B==1 THEN Z = !A; ELSE Z = A; 7

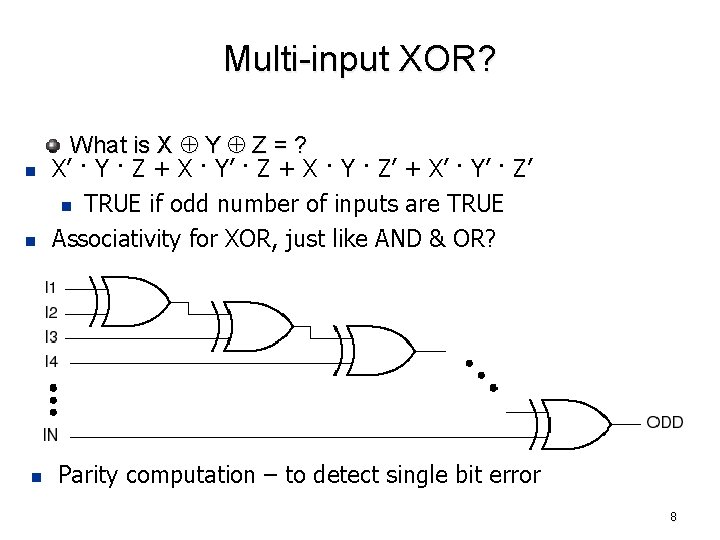

Multi-input XOR? n n n What is X Y Z = ? X’ · Y · Z + X · Y’ · Z + X · Y · Z’ + X’ · Y’ · Z’ n TRUE if odd number of inputs are TRUE Associativity for XOR, just like AND & OR? Parity computation – to detect single bit error 8

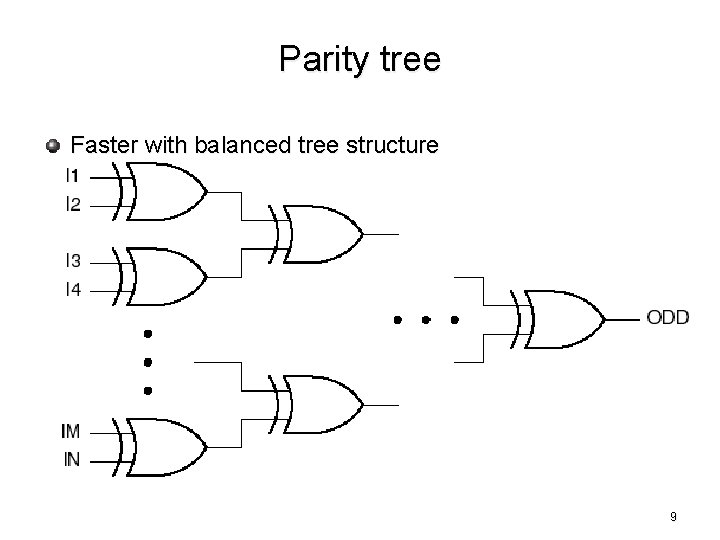

Parity tree Faster with balanced tree structure 9

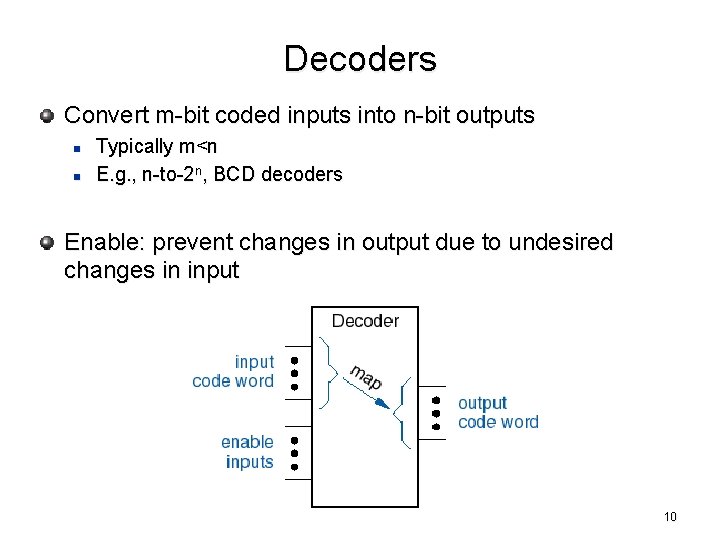

Decoders Convert m-bit coded inputs into n-bit outputs n n Typically m<n E. g. , n-to-2 n, BCD decoders Enable: prevent changes in output due to undesired changes in input 10

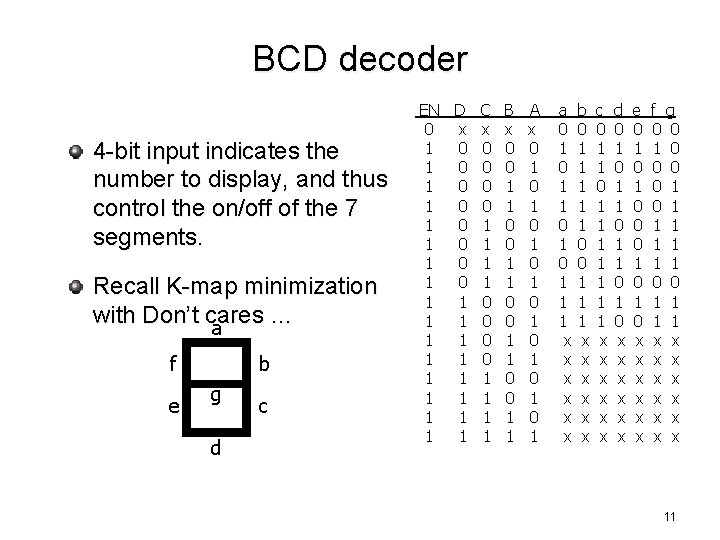

BCD decoder 4 -bit input indicates the number to display, and thus control the on/off of the 7 segments. Recall K-map minimization with Don’t cares … a f e b g d c EN D 0 x 1 0 1 0 1 1 1 1 C x 0 0 0 0 1 1 1 1 B x 0 0 1 1 A x 0 1 0 1 a 0 1 0 1 1 1 x x x b 0 1 1 1 0 0 1 1 1 x x x c 0 1 1 1 1 1 x x x d 0 1 1 0 1 0 x x x e 0 1 0 0 0 1 0 x x x f g 0 0 1 0 1 1 1 1 0 0 1 1 x x x 11

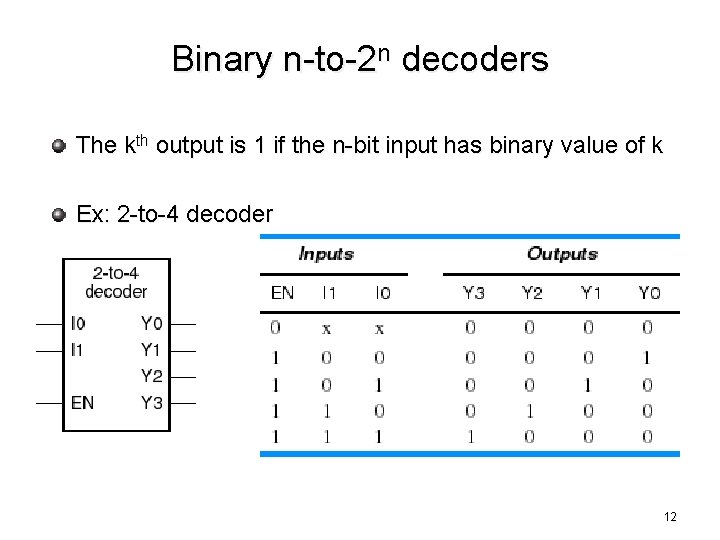

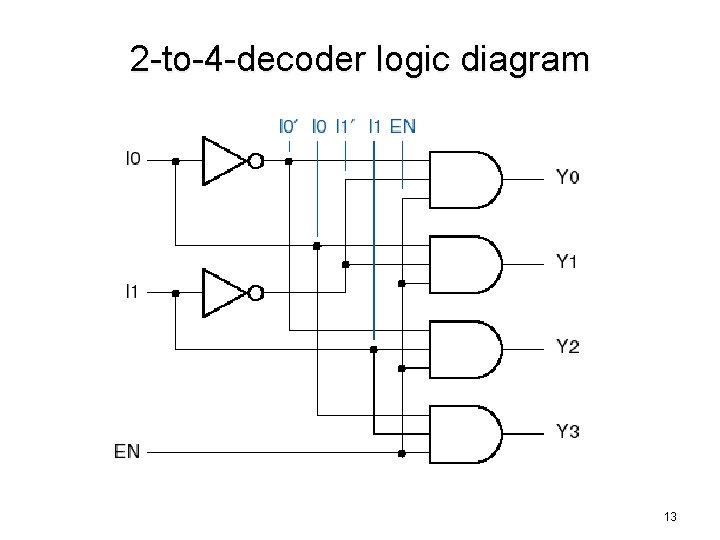

Binary n-to-2 n decoders The kth output is 1 if the n-bit input has binary value of k Ex: 2 -to-4 decoder 12

2 -to-4 -decoder logic diagram 13

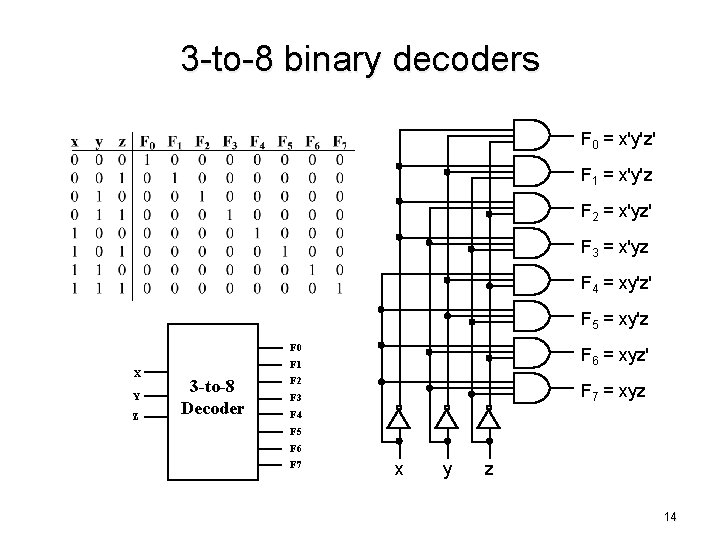

3 -to-8 binary decoders F 0 = x'y'z' F 1 = x'y'z F 2 = x'yz' F 3 = x'yz F 4 = xy'z' F 5 = xy'z F 0 X Y Z F 6 = xyz' F 1 3 -to-8 Decoder F 2 F 7 = xyz F 3 F 4 F 5 F 6 F 7 x y z 14

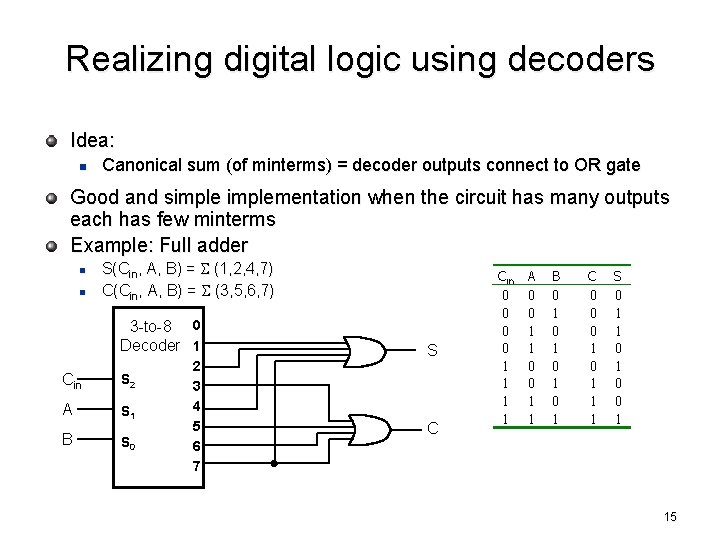

Realizing digital logic using decoders Idea: n Canonical sum (of minterms) = decoder outputs connect to OR gate Good and simplementation when the circuit has many outputs each has few minterms Example: Full adder n n S(Cin, A, B) = S (1, 2, 4, 7) C(Cin, A, B) = S (3, 5, 6, 7) 3 -to-8 0 Decoder 1 Cin S 2 A S 1 B S 0 2 3 4 5 6 7 S C Cin A B C S 0 0 1 1 0 1 0 1 0 0 0 1 1 1 0 1 0 0 1 1 15

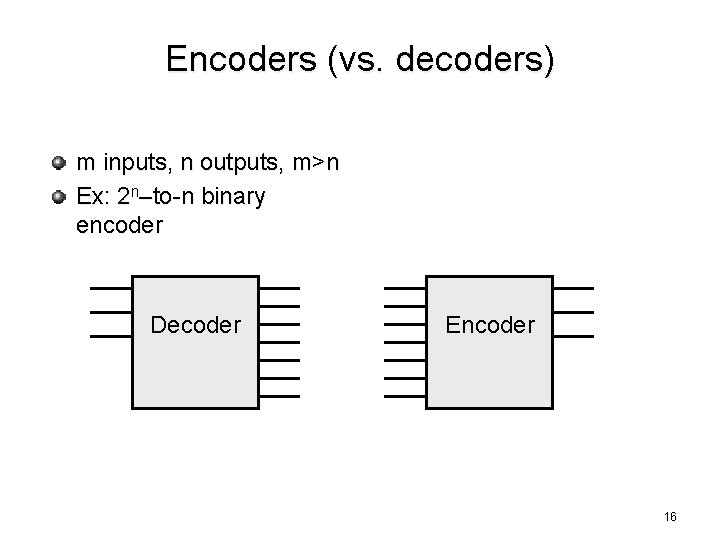

Encoders (vs. decoders) m inputs, n outputs, m>n Ex: 2 n–to-n binary encoder Decoder Encoder 16

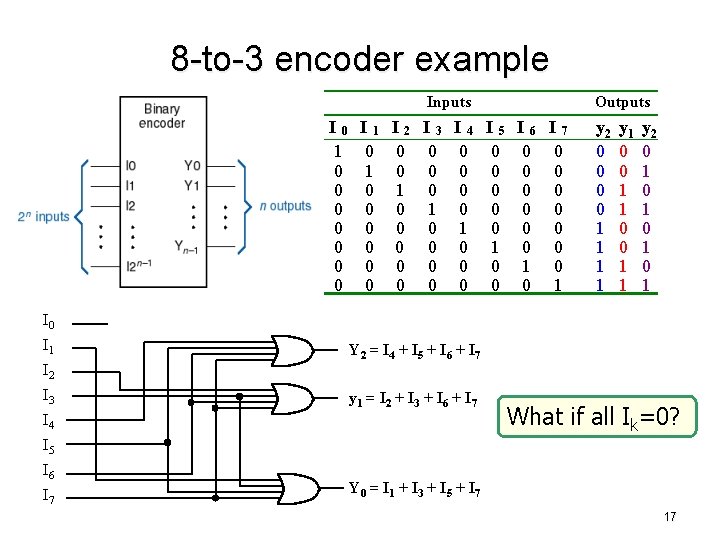

8 -to-3 encoder example Inputs I 0 1 0 0 0 0 I 2 0 0 1 0 0 0 I 3 0 0 0 1 0 0 I 4 0 0 1 0 0 0 Outputs I 5 0 0 0 1 0 0 I 6 0 0 0 1 0 I 7 0 0 0 0 1 y 2 0 0 1 1 y 1 0 0 1 1 y 2 0 1 0 1 I 0 I 1 I 2 I 3 Y 2 = I 4 + I 5 + I 6 + I 7 y 1 = I 2 + I 3 + I 6 + I 7 I 4 What if all Ik=0? I 5 I 6 I 7 Y 0 = I 1 + I 3 + I 5 + I 7 17

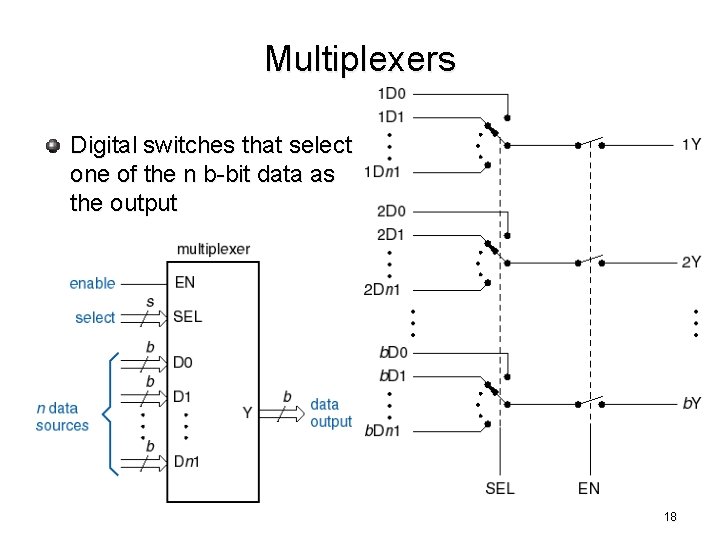

Multiplexers Digital switches that select one of the n b-bit data as the output 18

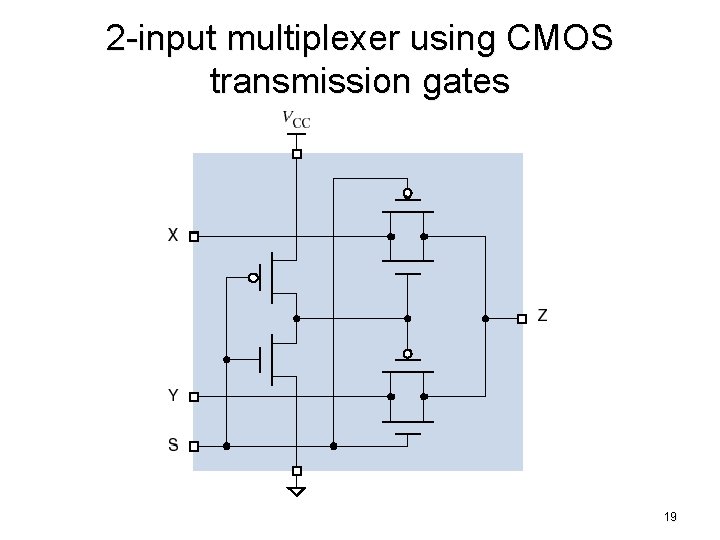

2 -input multiplexer using CMOS transmission gates 19

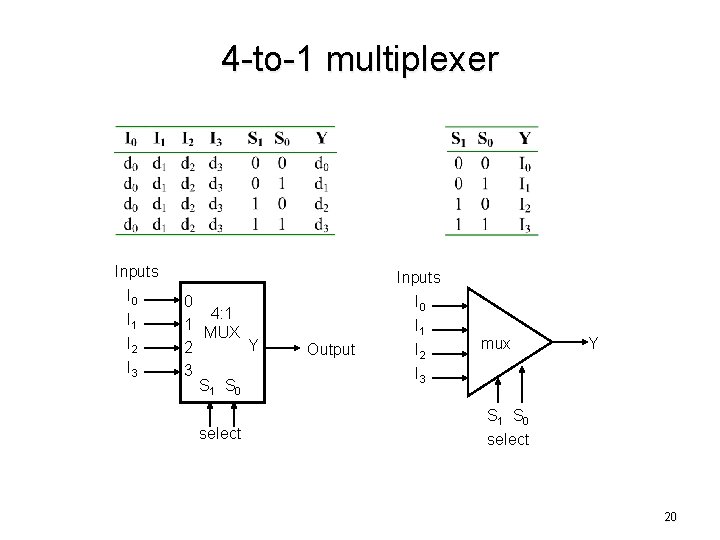

4 -to-1 multiplexer Inputs I 0 I 1 I 2 I 3 Inputs 0 4: 1 1 MUX Y 2 3 S 1 S 0 select Output I 0 I 1 I 2 I 3 mux Y S 1 S 0 select 20

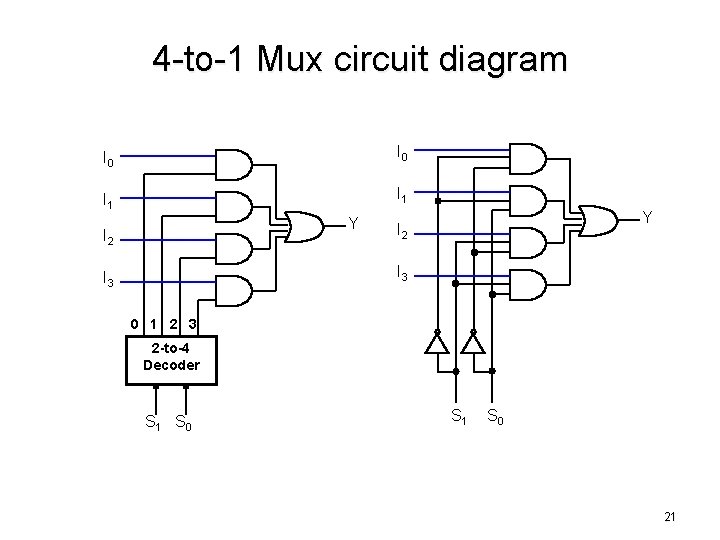

4 -to-1 Mux circuit diagram I 0 I 1 Y I 2 I 3 0 1 2 3 2 -to-4 Decoder S 1 S 0 21

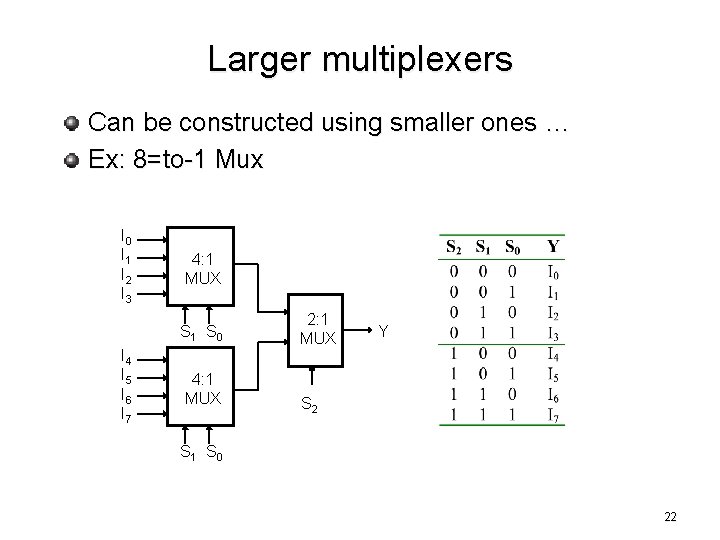

Larger multiplexers Can be constructed using smaller ones … Ex: 8=to-1 Mux I 0 I 1 I 2 I 3 4: 1 MUX S 1 S 0 I 4 I 5 I 6 I 7 4: 1 MUX 2: 1 MUX Y S 2 S 1 S 0 22

16 -to-1 multiplexer 23

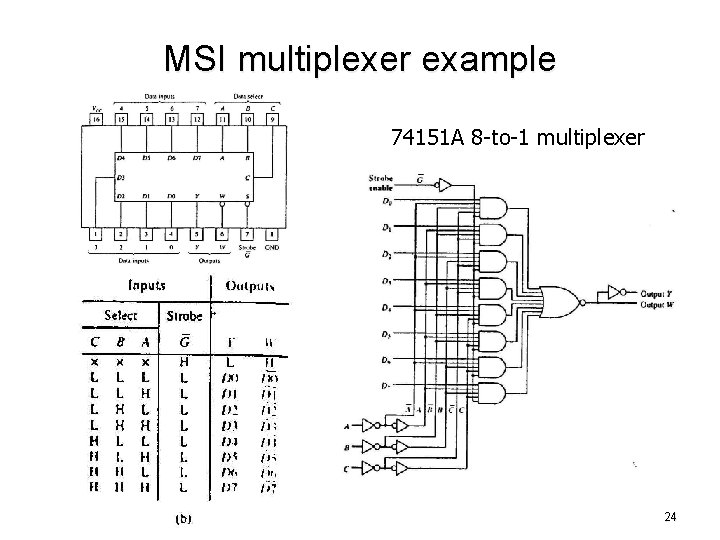

MSI multiplexer example 74151 A 8 -to-1 multiplexer 24

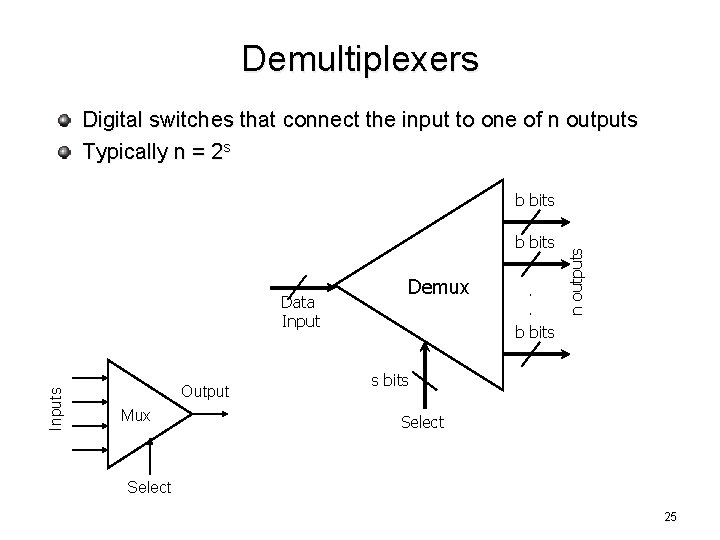

Demultiplexers Digital switches that connect the input to one of n outputs Typically n = 2 s b bits Inputs Data Input Output Mux Demux . . b bits n outputs b bits s bits Select 25

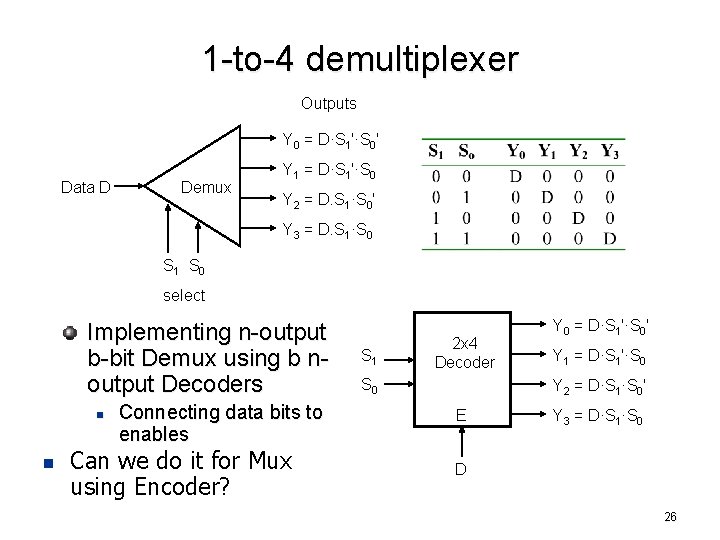

1 -to-4 demultiplexer Outputs Y 0 = D·S 1'·S 0' Data D Demux Y 1 = D·S 1'·S 0 Y 2 = D. S 1·S 0' Y 3 = D. S 1·S 0 S 1 S 0 select Implementing n-output b-bit Demux using b noutput Decoders n n Connecting data bits to enables Can we do it for Mux using Encoder? S 1 2 x 4 Decoder S 0 Y 0 = D·S 1'·S 0' Y 1 = D·S 1'·S 0 Y 2 = D·S 1·S 0' E Y 3 = D·S 1·S 0 D 26

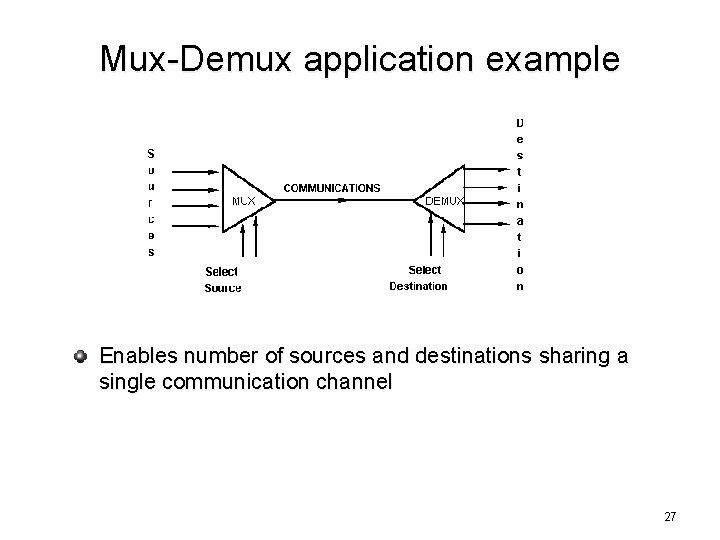

Mux-Demux application example Enables number of sources and destinations sharing a single communication channel 27

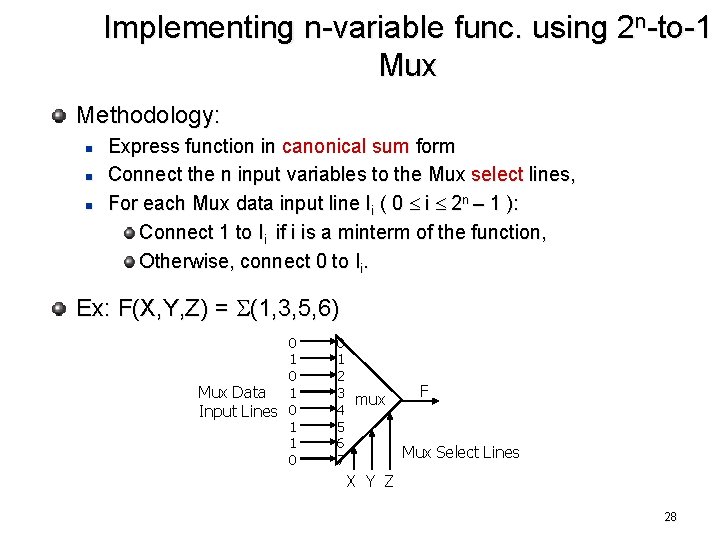

Implementing n-variable func. using 2 n-to-1 Mux Methodology: n n n Express function in canonical sum form Connect the n input variables to the Mux select lines, For each Mux data input line Ii ( 0 £ i £ 2 n – 1 ): Connect 1 to Ii if i is a minterm of the function, Otherwise, connect 0 to Ii. Ex: F(X, Y, Z) = S(1, 3, 5, 6) 0 1 0 Mux Data 1 Input Lines 0 1 1 0 0 1 2 3 mux 4 5 6 7 F Mux Select Lines X Y Z 28

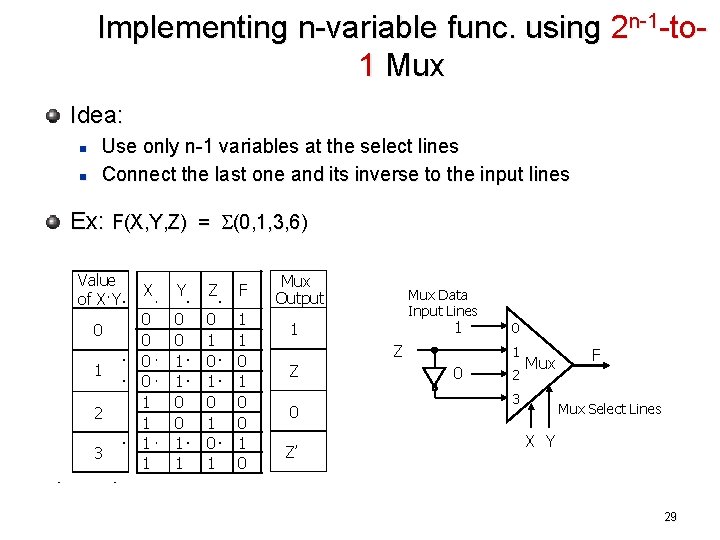

Implementing n-variable func. using 2 n-1 -to 1 Mux Idea: n n Use only n-1 variables at the select lines Connect the last one and its inverse to the input lines Ex: F(X, Y, Z) = S(0, 1, 3, 6) Value of X·Y 0 1 2 3 X Y Z F 0 0 1 1 0 1 0 1 1 1 0 0 1 0 Mux Output Mux Data Input Lines 1 1 Z Z 0 Z’ 0 1 0 2 Mux 3 F Mux Select Lines X Y 29

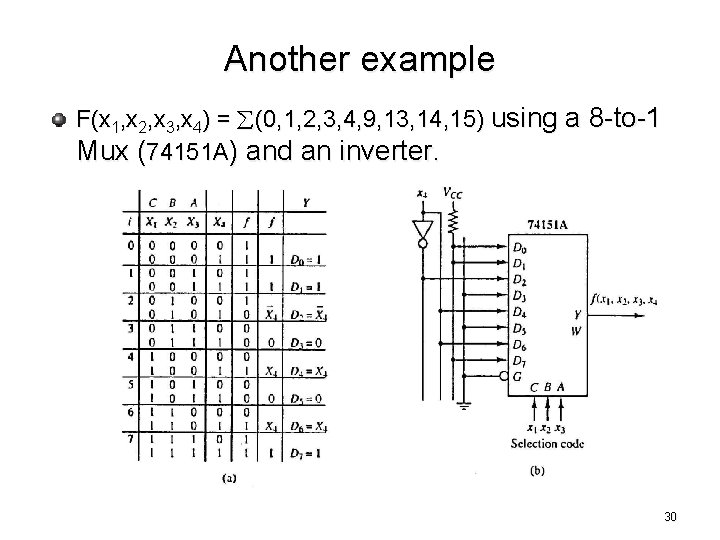

Another example F(x 1, x 2, x 3, x 4) = (0, 1, 2, 3, 4, 9, 13, 14, 15) using a 8 -to-1 Mux (74151 A) and an inverter. 30

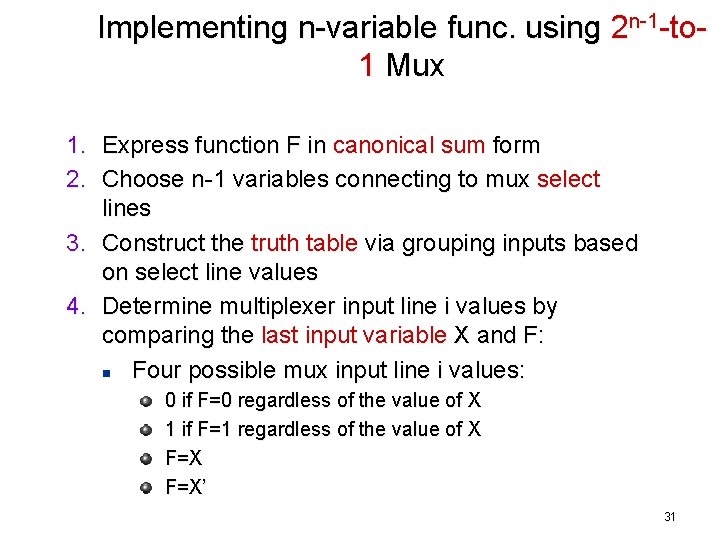

Implementing n-variable func. using 2 n-1 -to 1 Mux 1. Express function F in canonical sum form 2. Choose n-1 variables connecting to mux select lines 3. Construct the truth table via grouping inputs based on select line values 4. Determine multiplexer input line i values by comparing the last input variable X and F: n Four possible mux input line i values: 0 if F=0 regardless of the value of X 1 if F=1 regardless of the value of X F=X’ 31

- Slides: 31