Korszakvlts a processzorok fejldsben Sima Dezs 2013 szi

Korszakváltás a processzorok fejlődésében Sima Dezső 2013 őszi félév (verzió 3. 4)

Áttekintés • 1 Processzorok teljesítménye • 2 A processzorok hatékonysága • 3 A processzorok hatékonyságának stagnálása által kiváltott fejlődési főirányok • 4 Az órafrekvencia erőteljes növelése • 5 A Hatékonysági korlát • 6 A disszipációs korlát • 7 Párhuzamos buszok frekvenciakorlátja • 8 EPIC architektúrák/processzorok • 9 Paradigmaváltás

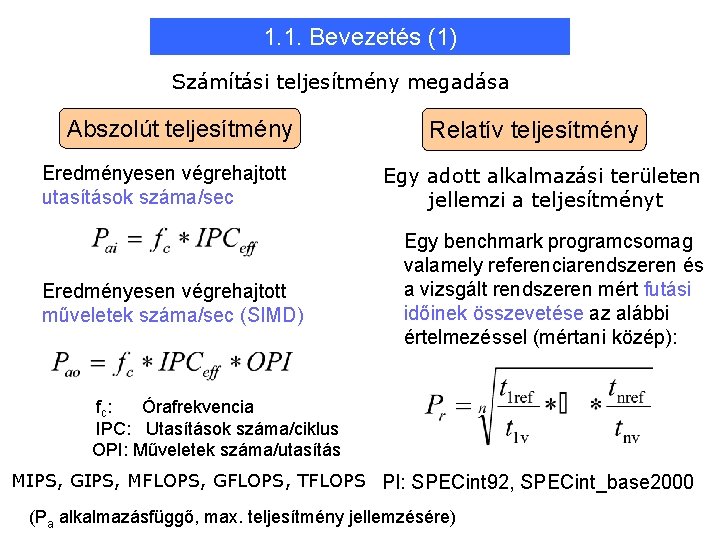

1. 1. Bevezetés (1) Számítási teljesítmény megadása Abszolút teljesítmény Eredményesen végrehajtott utasítások száma/sec Eredményesen végrehajtott műveletek száma/sec (SIMD) Relatív teljesítmény Egy adott alkalmazási területen jellemzi a teljesítményt Egy benchmark programcsomag valamely referenciarendszeren és a vizsgált rendszeren mért futási időinek összevetése az alábbi értelmezéssel (mértani közép): fc : Órafrekvencia IPC: Utasítások száma/ciklus OPI: Műveletek száma/utasítás MIPS, GIPS, MFLOPS, GFLOPS, TFLOPS Pl: SPECint 92, SPECint_base 2000 (Pa alkalmazásfüggő, max. teljesítmény jellemzésére)

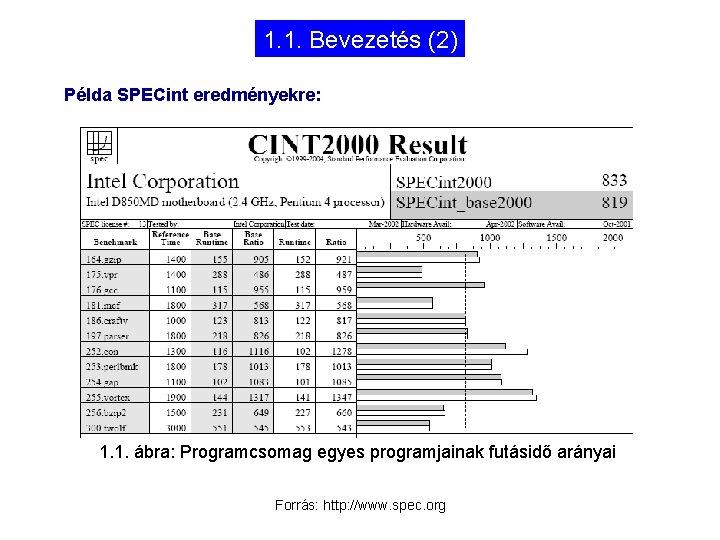

1. 1. Bevezetés (2) Példa SPECint eredményekre: 1. 1. ábra: Programcsomag egyes programjainak futásidő arányai Forrás: http: //www. spec. org

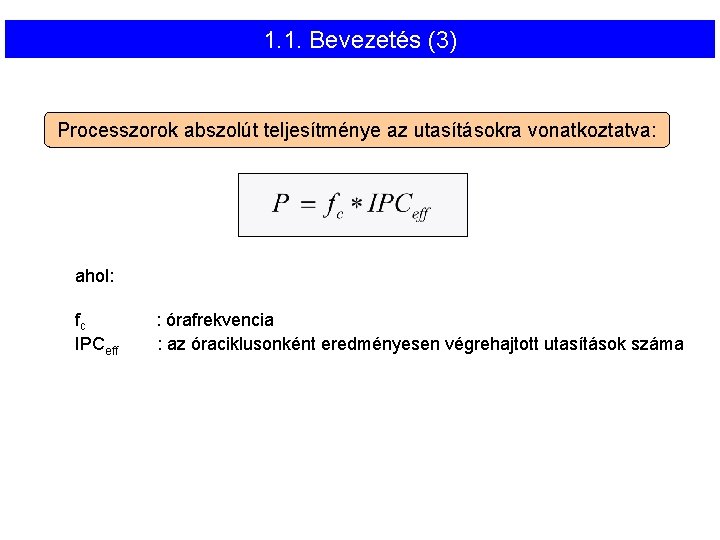

1. 1. Bevezetés (3) Processzorok abszolút teljesítménye az utasításokra vonatkoztatva: ahol: fc IPCeff : órafrekvencia : az óraciklusonként eredményesen végrehajtott utasítások száma

1. 1. Bevezetés (4) Processzorok hatékonysága (H): az óraciklusonként eredményesen végrehajtott utasítások száma Mivel H = IPCeff P = fc * H

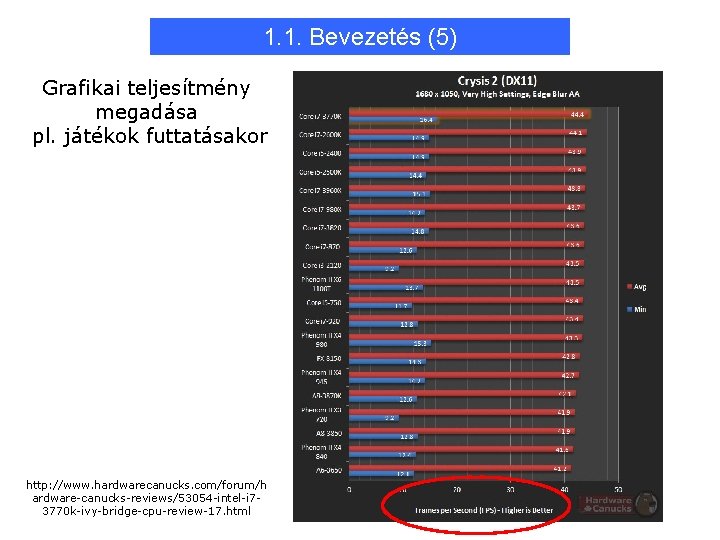

1. 1. Bevezetés (5) Grafikai teljesítmény megadása pl. játékok futtatásakor http: //www. hardwarecanucks. com/forum/h ardware-canucks-reviews/53054 -intel-i 73770 k-ivy-bridge-cpu-review-17. html

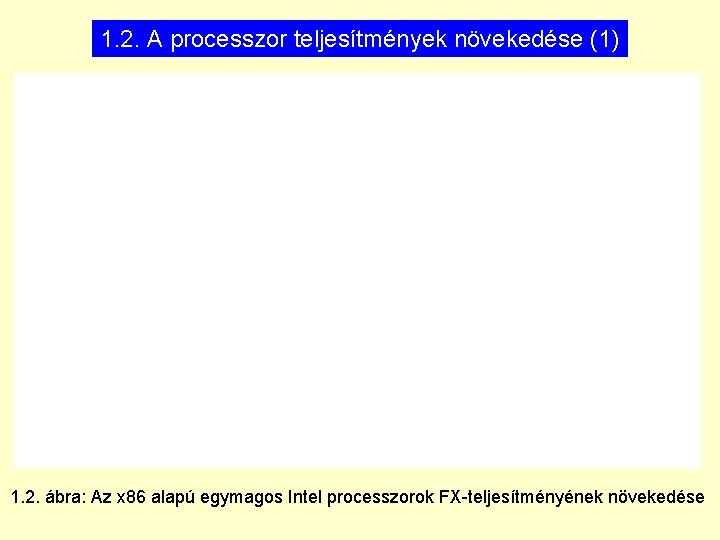

1. 2. A processzor teljesítmények növekedése (1) 1. 2. ábra: Az x 86 alapú egymagos Intel processzorok FX-teljesítményének növekedése

1. 2. A processzor teljesítmények növekedése (2) 1. 4. ábra: 3. A fixpontos teljesítmények növekedése (általában - 2) Forrás: F. Labonte, www-vlsi. stanford. edu/group/chart/spec. Inf 2000. pdf

2. A processzorok hatékonysága 2. 1. Bevezetés ?

2. 2. A processzorok hatékonyságának növekedése (1) 2. 1. ábra: Intel processzorok hatékonysága

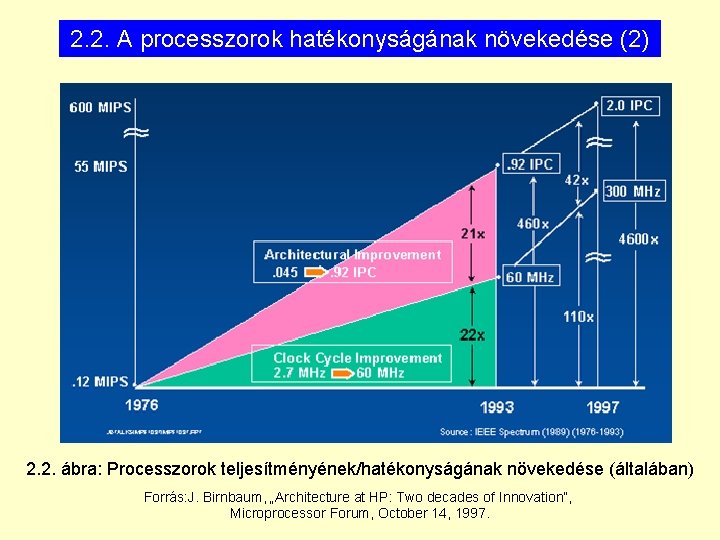

2. 2. A processzorok hatékonyságának növekedése (2) 2. 2. ábra: Processzorok teljesítményének/hatékonyságának növekedése (általában) Forrás: J. Birnbaum, „Architecture at HP: Two decades of Innovation”, Microprocessor Forum, October 14, 1997.

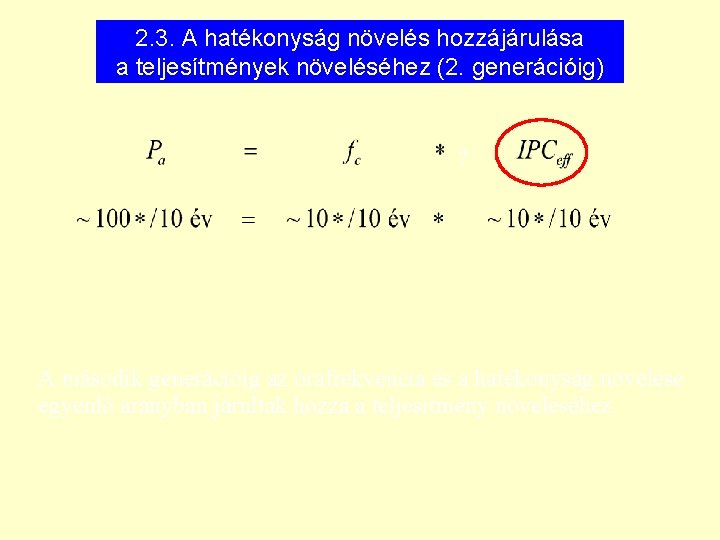

2. 3. A hatékonyság növelés hozzájárulása a teljesítmények növeléséhez (2. generációig) ? A második generációig az órafrekvencia és a hatékonyság növelése egyenlő arányban járultak hozzá a teljesítmény növeléséhez.

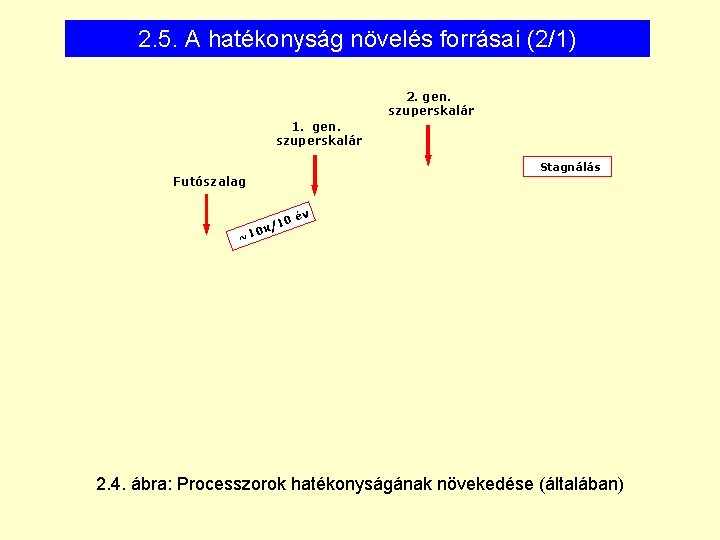

2. 4. A hatékonyság növekedése és annak korlátja 2. 4. ábra: Processzorok hatékonyságának növekedése (általában)

2. 5. A hatékonyság növelés forrásai (1) • Szóhossz növelése 8/16 32 bit (286 386 DX) • Időbeli párhuzamosság bevezetése, növelése 1. és 2. generációs futószalag processzorok (386 DX, 486 DX) • Kibocsátási párhuzamosság bevezetése, növelése 1. és 2. generációs szuperskalárok (Pentium, Pentium Pro)

2. 5. A hatékonyság növelés forrásai (2/1) 2. gen. szuperskalár 1. gen. szuperskalár Stagnálás Futószalag 10 0 x/ év ~1 2. 4. ábra: Processzorok hatékonyságának növekedése (általában)

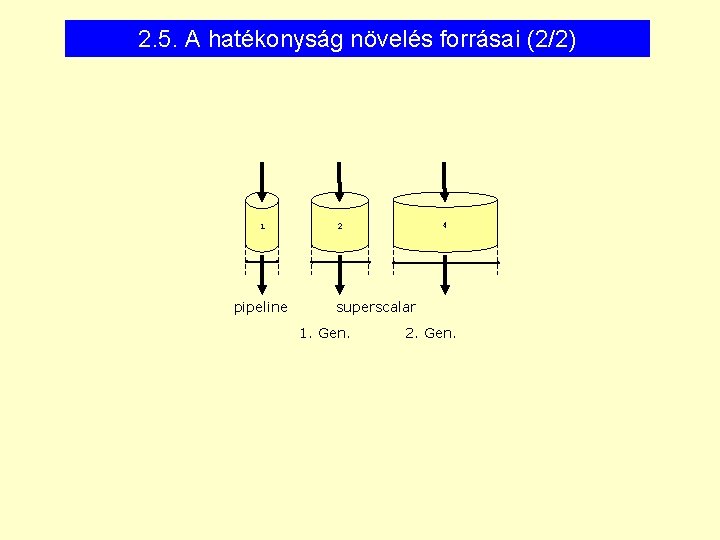

2. 5. A hatékonyság növelés forrásai (2/2) 1 pipeline 4 2 superscalar 1. Gen. 2. Gen.

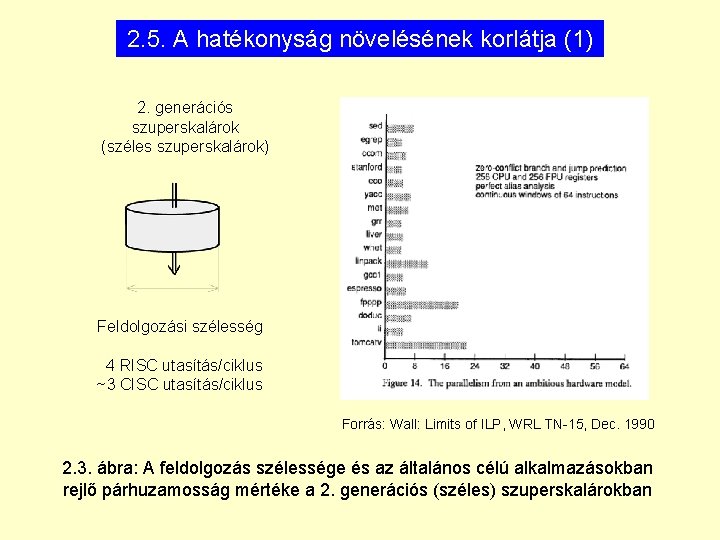

2. 5. A hatékonyság növelésének korlátja (1) 2. generációs szuperskalárok (széles szuperskalárok) Feldolgozási szélesség 4 RISC utasítás/ciklus ~3 CISC utasítás/ciklus Forrás: Wall: Limits of ILP, WRL TN-15, Dec. 1990 2. 3. ábra: A feldolgozás szélessége és az általános célú alkalmazásokban rejlő párhuzamosság mértéke a 2. generációs (széles) szuperskalárokban

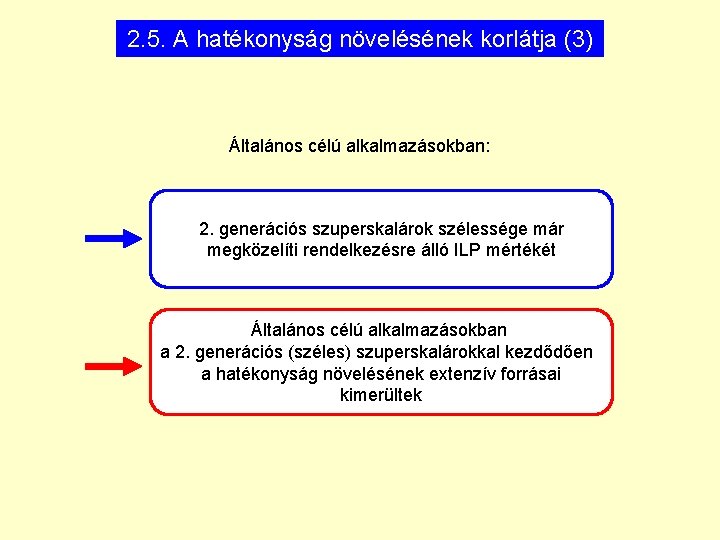

2. 5. A hatékonyság növelésének korlátja (3) Általános célú alkalmazásokban: 2. generációs szuperskalárok szélessége már megközelíti rendelkezésre álló ILP mértékét Általános célú alkalmazásokban a 2. generációs (széles) szuperskalárokkal kezdődően a hatékonyság növelésének extenzív forrásai kimerültek

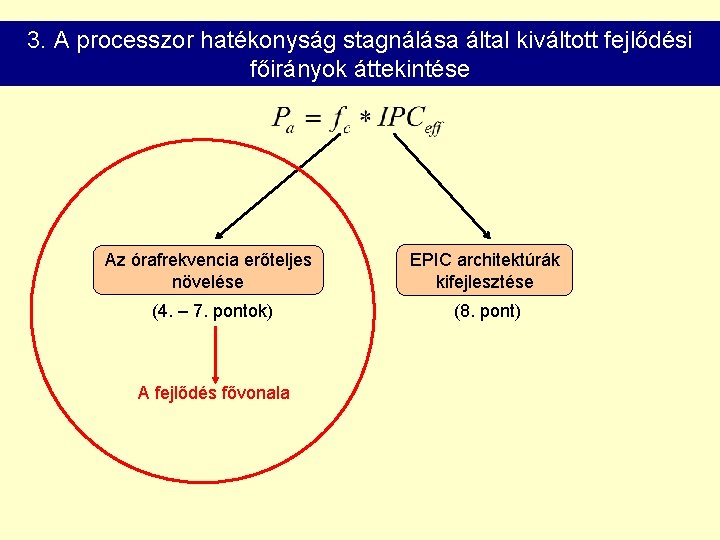

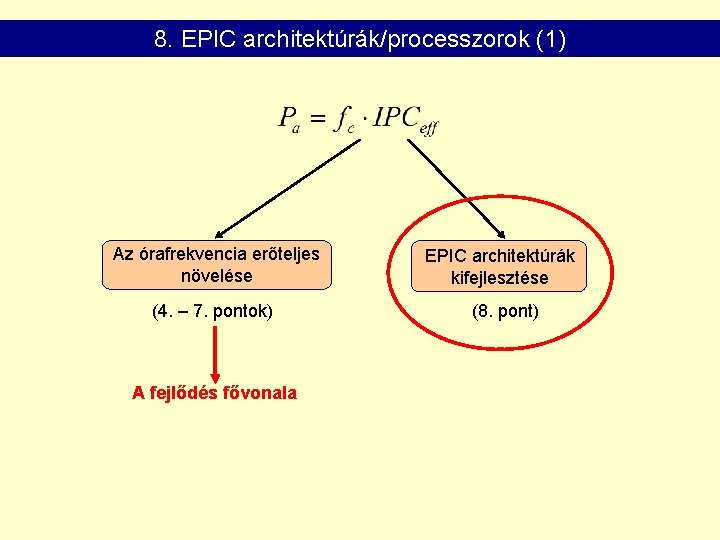

3. A processzor hatékonyság stagnálása által kiváltott fejlődési főirányok áttekintése Az órafrekvencia erőteljes növelése EPIC architektúrák kifejlesztése (4. – 7. pontok) (8. pont) A fejlődés fővonala

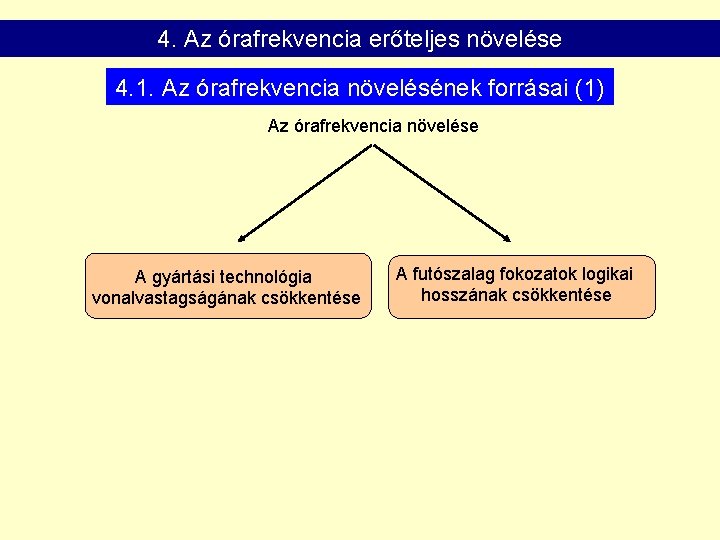

4. Az órafrekvencia erőteljes növelése 4. 1. Az órafrekvencia növelésének forrásai (1) Az órafrekvencia növelése A gyártási technológia vonalvastagságának csökkentése A futószalag fokozatok logikai hosszának csökkentése

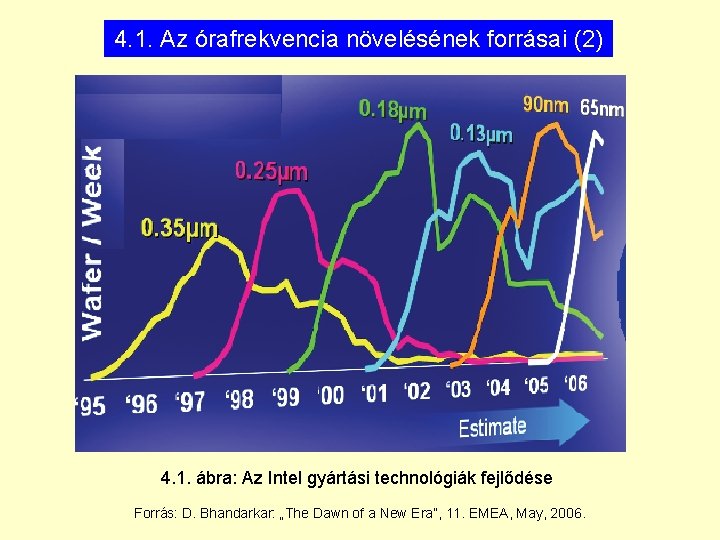

4. 1. Az órafrekvencia növelésének forrásai (2) 4. 1. ábra: Az Intel gyártási technológiák fejlődése Forrás: D. Bhandarkar: „The Dawn of a New Era”, 11. EMEA, May, 2006.

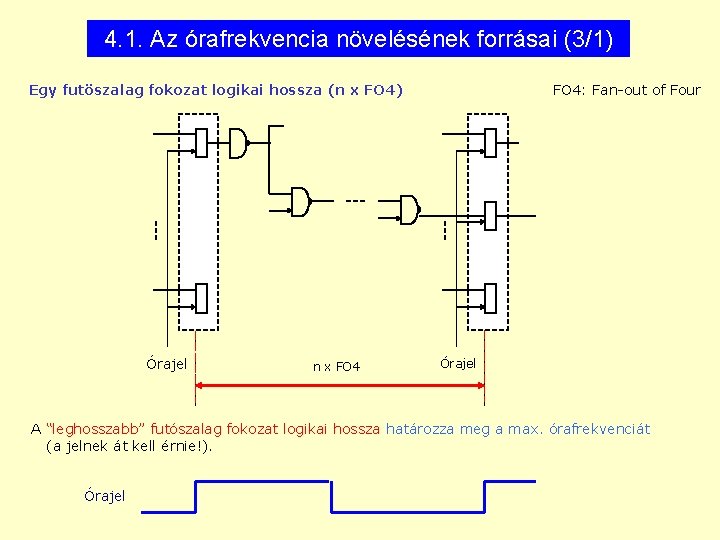

4. 1. Az órafrekvencia növelésének forrásai (3/1) Egy futöszalag fokozat logikai hossza (n x FO 4) Órajel n x FO 4: Fan-out of Four Órajel A “leghosszabb” futószalag fokozat logikai hossza határozza meg a max. órafrekvenciát (a jelnek át kell érnie!). Órajel

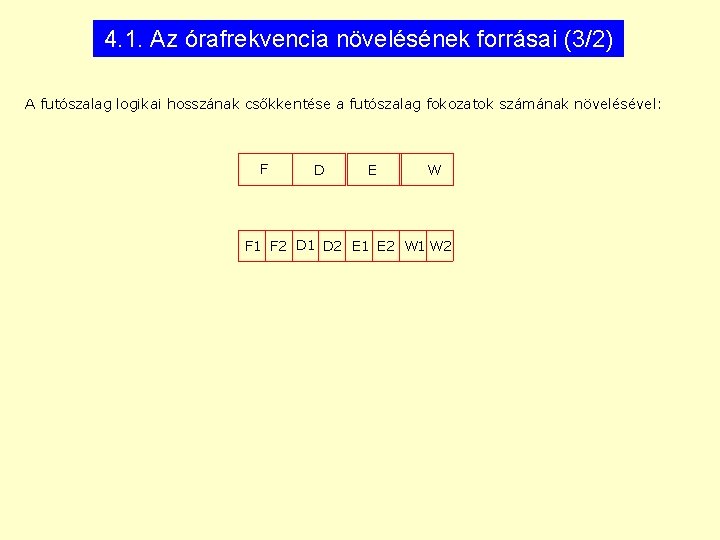

4. 1. Az órafrekvencia növelésének forrásai (3/2) A futószalag logikai hosszának csőkkentése a futószalag fokozatok számának növelésével: F D E W F 1 F 2 D 1 D 2 E 1 E 2 W 1 W 2

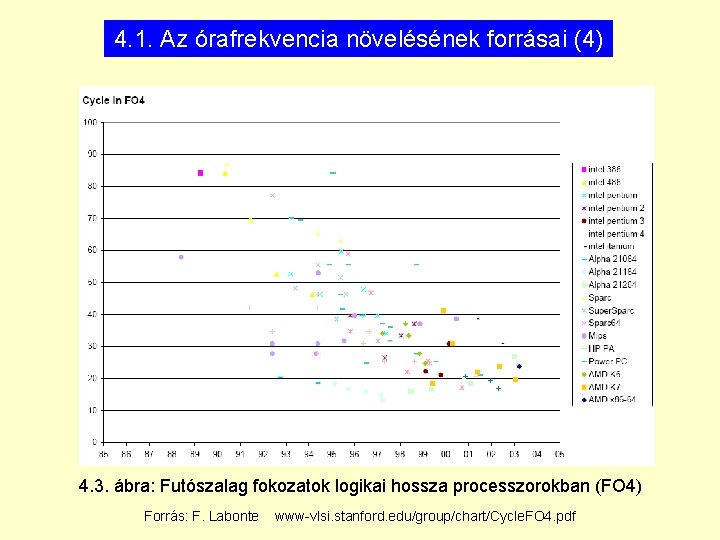

4. 1. Az órafrekvencia növelésének forrásai (4) 4. 3. ábra: Futószalag fokozatok logikai hossza processzorokban (FO 4) Forrás: F. Labonte www-vlsi. stanford. edu/group/chart/Cycle. FO 4. pdf

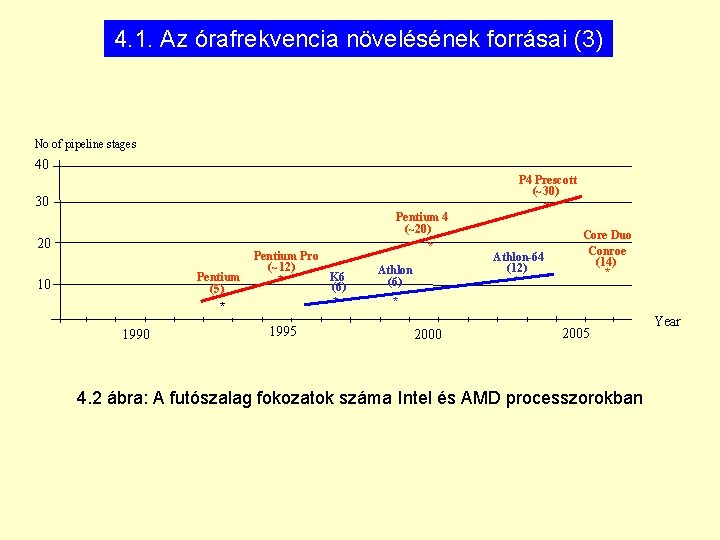

4. 1. Az órafrekvencia növelésének forrásai (3) No of pipeline stages 40 30 20 Pentium (5) 10 * 1990 Pentium Pro (~12) K 6 * (6) * 1995 Pentium 4 (~20) * Athlon (6) P 4 Prescott (~30) * Athlon-64 (12) * Core Duo Conroe (14) * * 2000 2005 4. 2 ábra: A futószalag fokozatok száma Intel és AMD processzorokban Year

4. 2. Az órafrekvenciák növekedési üteme (1) 4. 4. ábra: Az x 86 alapú Intel processzorok órafrekvenciájának növekedése

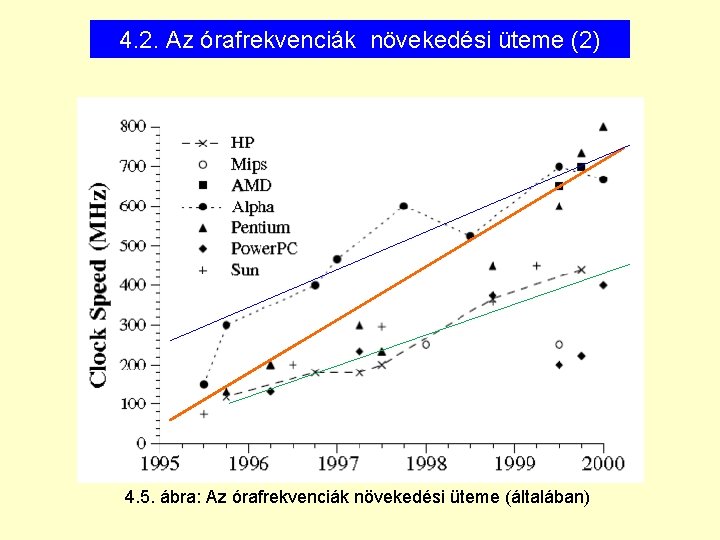

4. 2. Az órafrekvenciák növekedési üteme (2) 4. 5. ábra: Az órafrekvenciák növekedési üteme (általában)

4. 3. Az órafrekvencia erőteljes növelésének konzekvenciái 4. 3. 1. Áttekintés • RISC processzorok kiszorulása (4. 3. 2) • Fejlődési korlátok megjelenése (4. 3. 3)

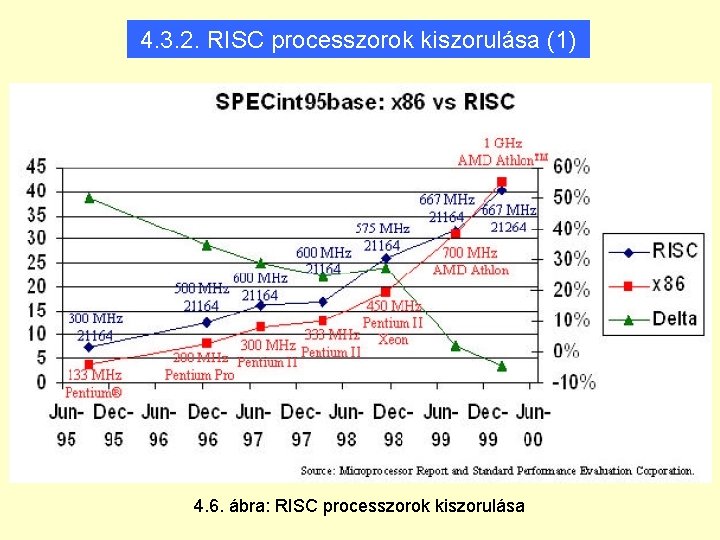

4. 3. 2. RISC processzorok kiszorulása (1) 4. 6. ábra: RISC processzorok kiszorulása

4. 3. 2. RISC processzorok kiszorulása (2) 1995 -2000: A CISC processzorok átvették a vezetést a teljesítmény versenyben, mivel magasabb órafrekvenciáról indulva (RISC) nem volt tartható az azonos iramú frekvencia növelés, mint alacsonyabb frekvencia értékről (CISC) 1997: Intel és HP bejelentették az IA-64/Merced architektúrát/processzorcsaládot, mint a 32 -bites x 86 architektúrát leváltó új generációt A legtöbb RISC processzorcsalád fejlesztésének leállítása, mint pl. MIPS R családja, HP Alpha és PA családjai, illetve a Power. PC Consortium Power. PC családja

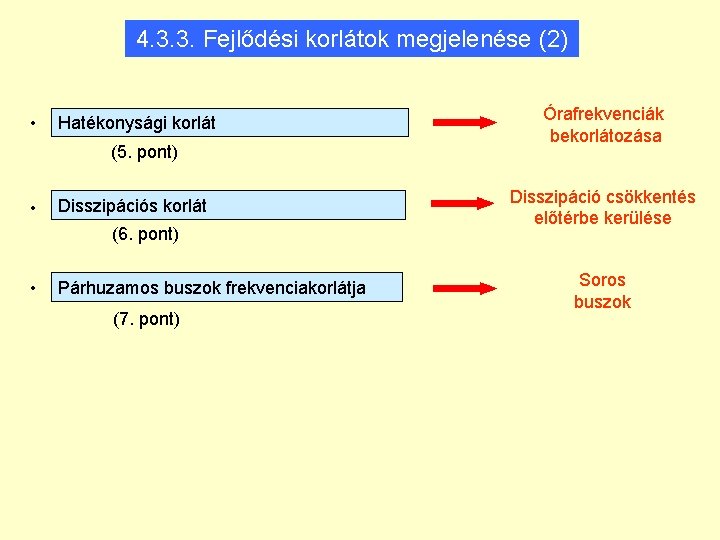

4. 3. 3. Fejlődési korlátok megjelenése (1) • Hatékonysági korlát (5. pont) • Disszipációs korlát (6. pont) • Párhuzamos buszok frekvenciakorlátja (7. pont)

4. 3. 3. Fejlődési korlátok megjelenése (2) • Hatékonysági korlát (5. pont) • Disszipációs korlát (6. pont) • Párhuzamos buszok frekvenciakorlátja (7. pont) Órafrekvenciák stagnálása Disszipáció csökkentés előtérbe kerülése Soros buszok megjelenése

5. A Hatékonysági korlát 5. 1. Áttekintés Alapvető ok: A processzor és a memória közötti sebességolló (növekvő órafrekvenciákon tágul)

5. 1. Áttekintés (2) A sebességolló konkrét megnyilvánulásai: • DRAM késleltetési ideje • Memória átviteli rátája • L 2 cache tárak elérési ideje • A processzor busz átviteli rátája

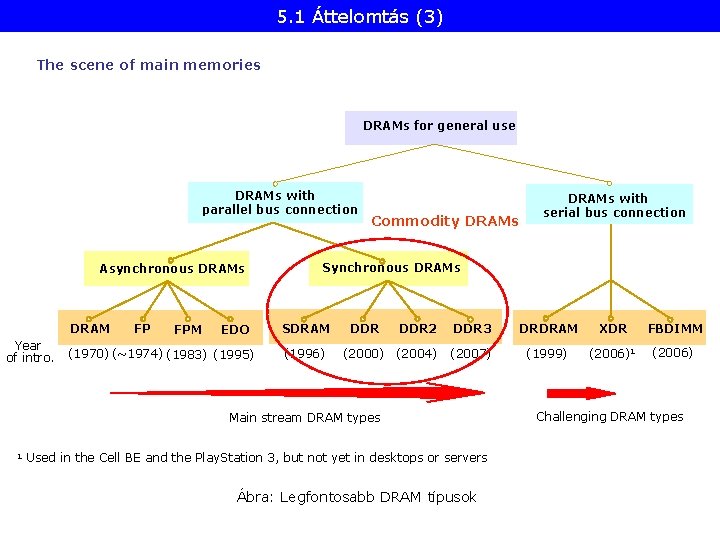

5. 1 Áttelomtás (3) The scene of main memories DRAMs for general use DRAMs with parallel bus connection Asynchronous DRAM Year of intro. FP FPM EDO (1970) (~1974) (1983) (1995) Commodity DRAMs Synchronous DRAMs SDRAM (1996) DDR 2 DDR 3 DRDRAM XDR FBDIMM (2000) (2004) (2007) (1999) (2006)1 (2006) DDR Main stream DRAM types 1 DRAMs with serial bus connection Used in the Cell BE and the Play. Station 3, but not yet in desktops or servers Ábra: Legfontosabb DRAM típusok Challenging DRAM types

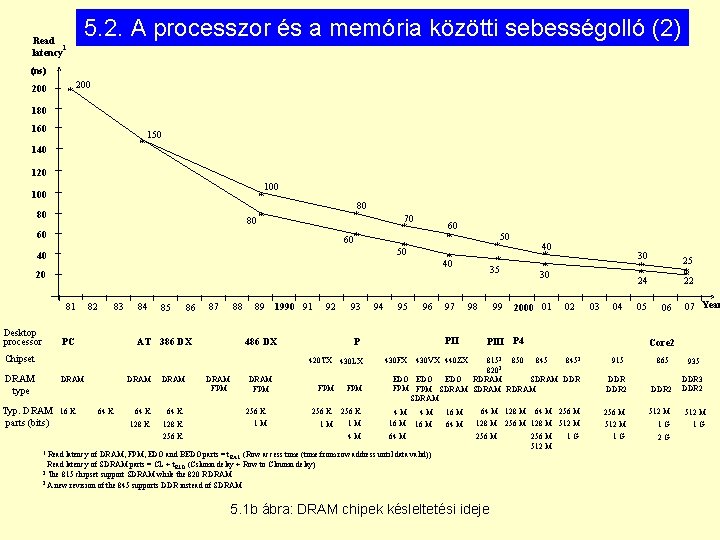

5. 2. A processzor és a memória közötti sebességolló (2) Read 1 latency (ns) 200 * 200 180 160 * 140 150 120 100 * 80 80 * 100 80 * 60 70 * 60 * * 50 40 50 * * 35 * 40 20 81 Desktop processor 82 83 84 85 86 87 AT 386 DX PC 88 89 1990 91 92 486 DX Chipset DRAM Typ. DRAM parts (bits) 16 K DRAM 64 K DRAM FPM 94 95 96 430 LX FPM 97 PII P 420 TX DRAM type 93 430 FX 98 99 40 * * 30 2000 01 30 * * 24 02 64 K 256 K 128 K 256 K 1 M 1 M 1 M 4 M 4 M 16 M 4 M 64 M 16 M 64 M 05 06 07 Year Core 2 915 865 935 DDR 2 DDR 3 DDR 2 64 M 128 M 64 M 256 M 128 M 512 M 256 M 512 M 1 G 1 G 2 G 8152 850 8453 8202 EDO SDRAM DDR EDO RDRAM FPM SDRAM RDRAM SDRAM 64 K 04 PIII P 4 430 VX 440 ZX 128 K 03 25 ** 22 256 M Read latency of DRAM, FPM, EDO and BEDO parts = t. RAC (Row access time (time from row address until data valid)) Read latency of SDRAM parts = CL + t. RCD (Cslumn delay + Row to Cloumn delay) 2 The 815 chipset support SDRAM while the 820 RDRAM 3 A new revision of the 845 supports DDR instead of SDRAM 1 5. 1 b ábra: DRAM chipek késleltetési ideje 256 M 512 M

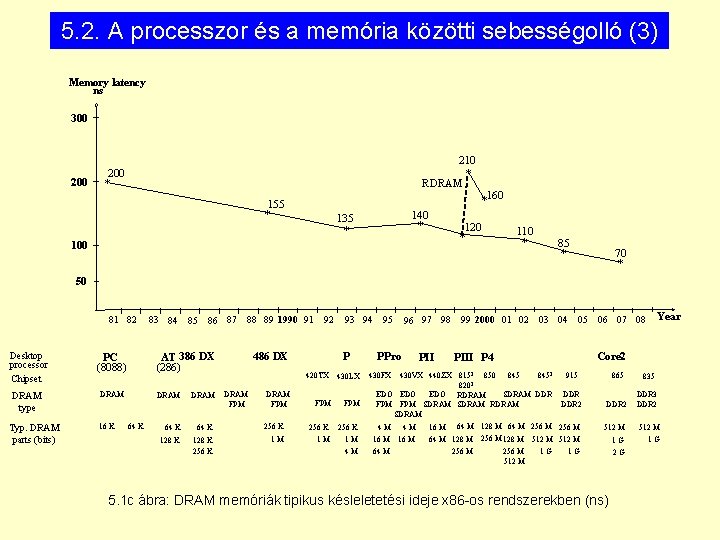

5. 2. A processzor és a memória közötti sebességolló (3) Memory latency ns 300 210 * RDRAM 200 * 155 * 140 * 135 * *160 120 * 100 110 * 85 * 70 * 50 81 82 Desktop processor Chipset DRAM type Typ. DRAM parts (bits) 86 87 88 89 1990 91 92 AT 386 DX (286) PC (8088) DRAM 16 K 83 84 85 DRAM 64 K DRAM 486 DX P 420 TX DRAM FPM 93 94 430 LX FPM 95 96 97 98 99 2000 01 02 PPro PII 03 04 05 PIII P 4 430 VX 440 ZX 8152 850 915 8453 8202 EDO SDRAM DDR EDO RDRAM FPM SDRAM RDRAM DDR 2 SDRAM Core 2 430 FX 64 K 256 K 128 K 256 K 1 M 1 M 1 M 4 M 4 M 16 M 4 M 64 M 128 M 64 M 256 M 64 M 128 M 256 M 128 M 512 M 1 G 256 M 1 G 512 M 16 M Year 06 07 08 865 835 DDR 2 DDR 3 DDR 2 512 M 1 G 1 G 5. 1 c ábra: DRAM memóriák tipikus késleletetési ideje x 86 -os rendszerekben (ns) 2 G

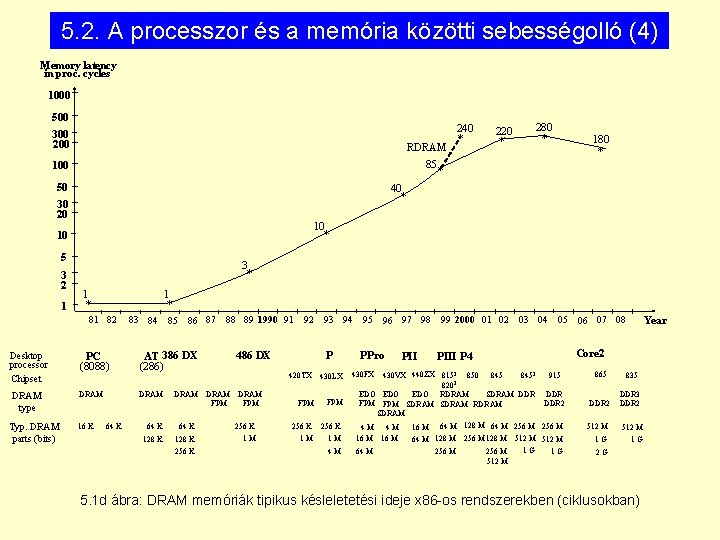

5. 2. A processzor és a memória közötti sebességolló (4) Memory latency in proc. cycles 1000 500 300 200 RDRAM 50 180 * 10 5 3 83 84 85 86 87 Desktop processor Chipset PC (8088) AT 386 DX (286) DRAM type DRAM 16 K * 1 * 81 82 Typ. DRAM parts (bits) 280 * 40 * 30 20 1 220 * 85 * 100 3 2 240 * 64 K DRAM 88 89 1990 91 92 486 DX 420 TX DRAM FPM 96 97 98 99 2000 01 02 93 94 95 P PPro 430 LX FPM PII 03 04 05 PIII P 4 430 FX 430 VX 440 ZX 8152 850 915 8453 8202 EDO SDRAM DDR EDO RDRAM FPM SDRAM RDRAM DDR 2 SDRAM 64 K 256 K 128 K 256 K 1 M 1 M 1 M 4 M 4 M 16 M 4 M 64 M 128 M 64 M 256 M 64 M 128 M 256 M 128 M 512 M 1 G 256 M 1 G 512 M 16 M Year 06 07 08 Core 2 865 835 DDR 2 DDR 3 DDR 2 512 M 1 G 1 G 2 G 5. 1 d ábra: DRAM memóriák tipikus késleletetési ideje x 86 -os rendszerekben (ciklusokban)

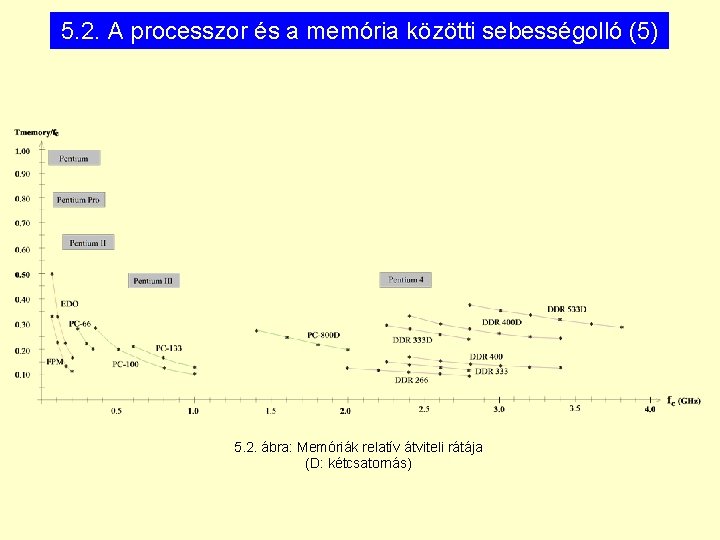

5. 2. A processzor és a memória közötti sebességolló (5) 5. 2. ábra: Memóriák relatív átviteli rátája (D: kétcsatornás)

5. 2. A processzor és a memória közötti sebességolló (7) 5. 4. ábra: A processzor busz (FSB) relatív átviteli rátája

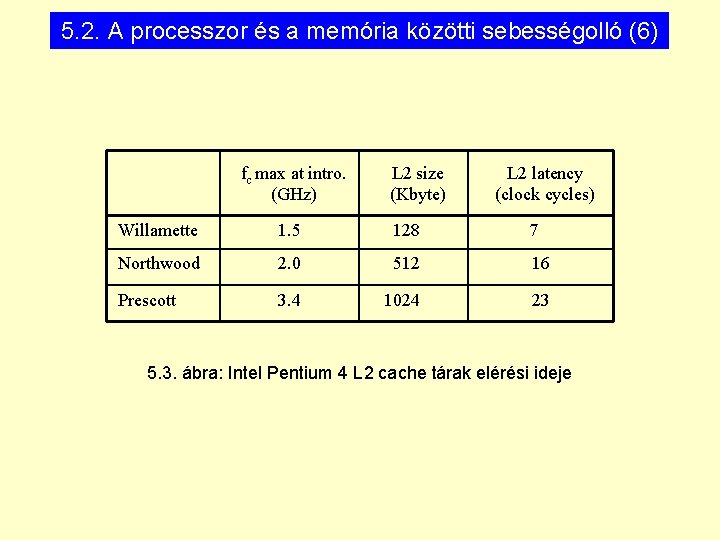

5. 2. A processzor és a memória közötti sebességolló (6) fc max at intro. (GHz) L 2 size (Kbyte) L 2 latency (clock cycles) Willamette 1. 5 128 7 Northwood 2. 0 512 16 Prescott 3. 4 1024 23 5. 3. ábra: Intel Pentium 4 L 2 cache tárak elérési ideje

5. 3. A 3. generációs szuperskalárok hatékonysága (1) FSB órafrekvencia Memoria átviteli rátája Háttértár típusa 5. 5. ábra: Intel Pentium III és Pentium 4 processzorainak hatékonysága fixpontos feldolgozás esetén

5. 3. A 3. generációs szuperskalárok hatékonysága (2) 5. 6. ábra: AMD Athlon, Athlon XP és Athlon 64 processzorainak hatékonysága fixpontos feldolgozás esetén

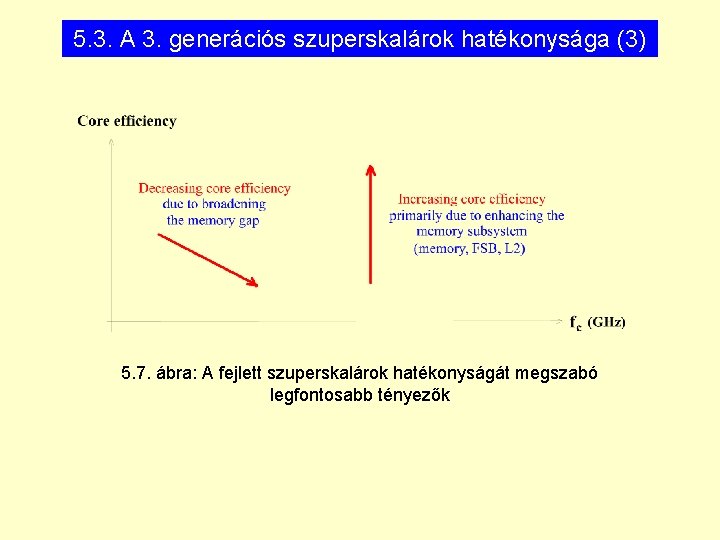

5. 3. A 3. generációs szuperskalárok hatékonysága (3) 5. 7. ábra: A fejlett szuperskalárok hatékonyságát megszabó legfontosabb tényezők

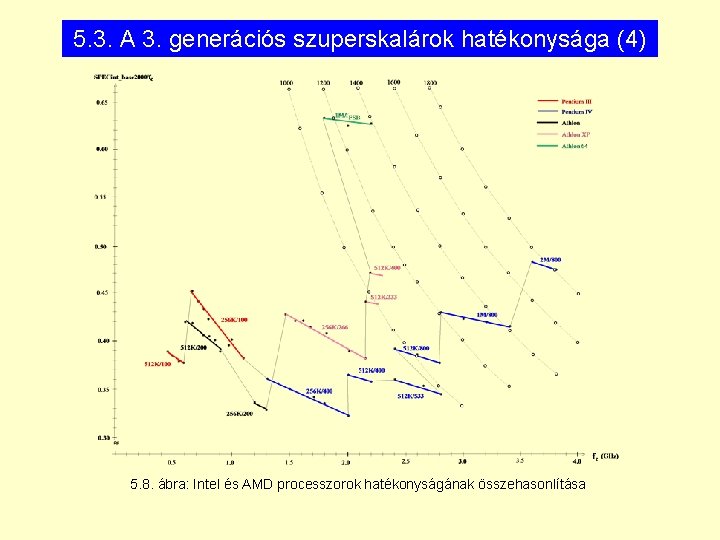

5. 3. A 3. generációs szuperskalárok hatékonysága (4) 5. 8. ábra: Intel és AMD processzorok hatékonyságának összehasonlítása

5. 3. A 3. generációs szuperskalárok hatékonysága (5) 5. 9. ábra: Intel és AMD processzorok tervezési filozófiájának összehasonlítása

5. 3. A 3. generációs szuperskalárok hatékonysága (6) A processzorok hatékonysági korlátjának konzekvenciája: Növekvő órafrekvenciákon egyre csökkenő teljesítménytöbblet Magasabb órafrekvencia Magasabb disszipáció Az órafrekvenciák stagnálása

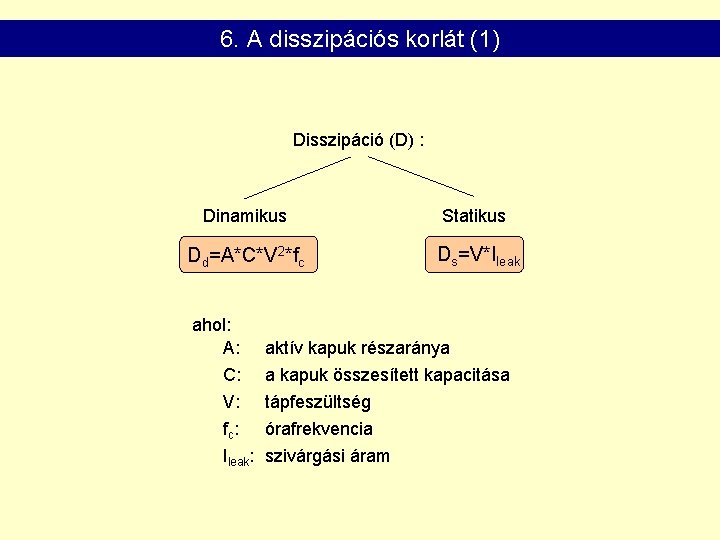

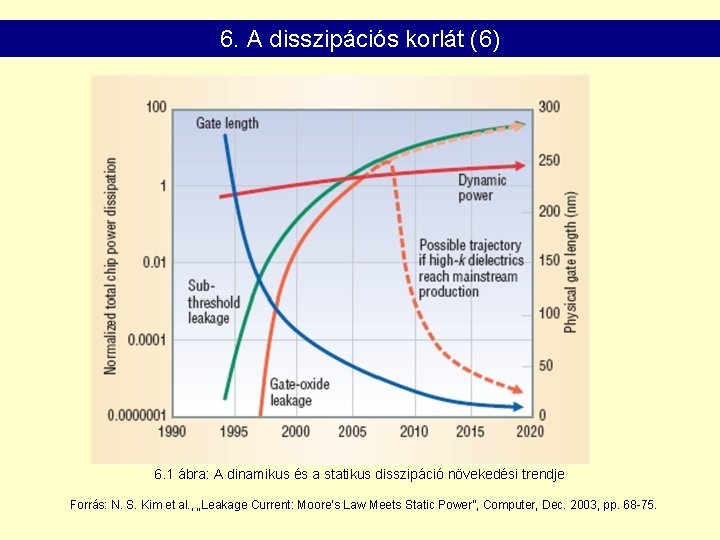

6. A disszipációs korlát (1) Disszipáció (D) : Dinamikus Statikus Dd=A*C*V 2*fc Ds=V*Ileak ahol: A: aktív kapuk részaránya C: V: a kapuk összesített kapacitása tápfeszültség fc : órafrekvencia Ileak: szivárgási áram

6. A disszipációs korlát (2) 6. 2. ábra: Intel processzorok fajlagos disszipációja

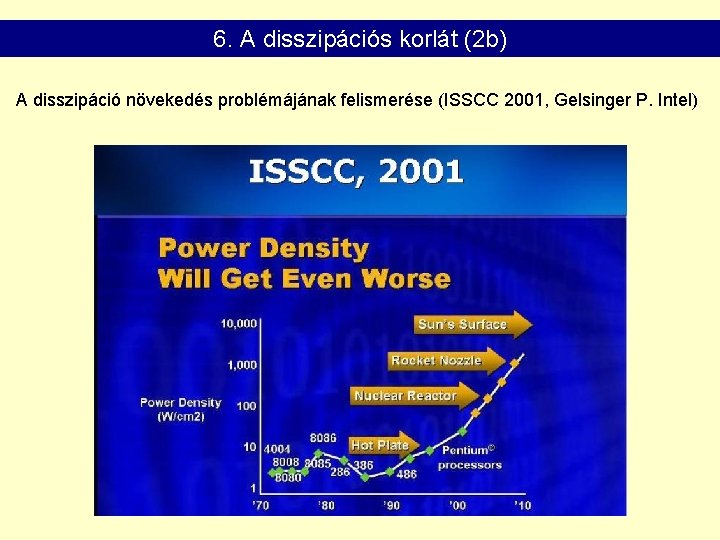

6. A disszipációs korlát (2 b) A disszipáció növekedés problémájának felismerése (ISSCC 2001, Gelsinger P. Intel)

6. A disszipációs korlát (2 c) A tápfeszűltség skálázása a gyártási technológiával Forrás: Gelsinger P. IDF, June 7 2006

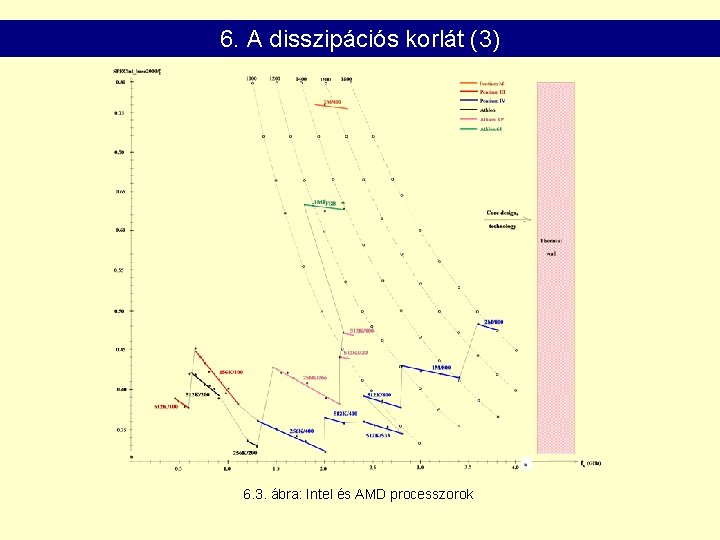

6. A disszipációs korlát (3) 6. 3. ábra: Intel és AMD processzorok

6. A disszipációs korlát (4) 6. 4. ábra: Intel P 4 processzorcsaládja (Netburst architektúra)

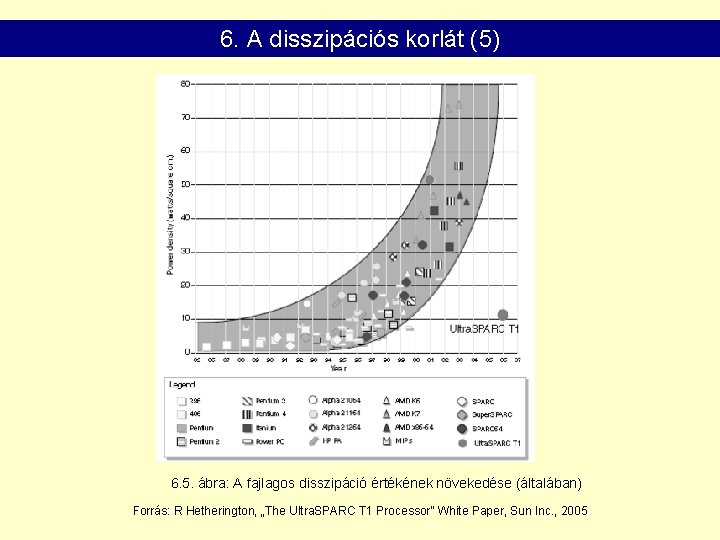

6. A disszipációs korlát (5) 6. 5. ábra: A fajlagos disszipáció értékének növekedése (általában) Forrás: R Hetherington, „The Ultra. SPARC T 1 Processor” White Paper, Sun Inc. , 2005

6. A disszipációs korlát (6) 6. 1 ábra: A dinamikus és a statikus disszipáció növekedési trendje Forrás: N. S. Kim et al. , „Leakage Current: Moore’s Law Meets Static Power”, Computer, Dec. 2003, pp. 68 -75.

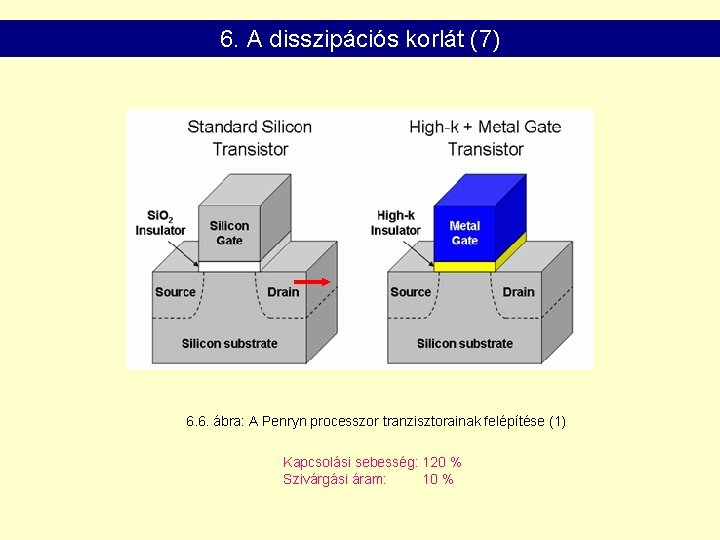

6. A disszipációs korlát (7) 6. 6. ábra: A Penryn processzor tranzisztorainak felépítése (1) Kapcsolási sebesség: 120 % Szivárgási áram: 10 %

6. A disszipációs korlát (8) A disszipációs korlát konzekvenciái: Az órafrekvencia növelésén alapuló fejlesztési irány háttérbe szorulása A processzorok tervezésében a disszipáció csökkentő technikák előtérbe kerülése

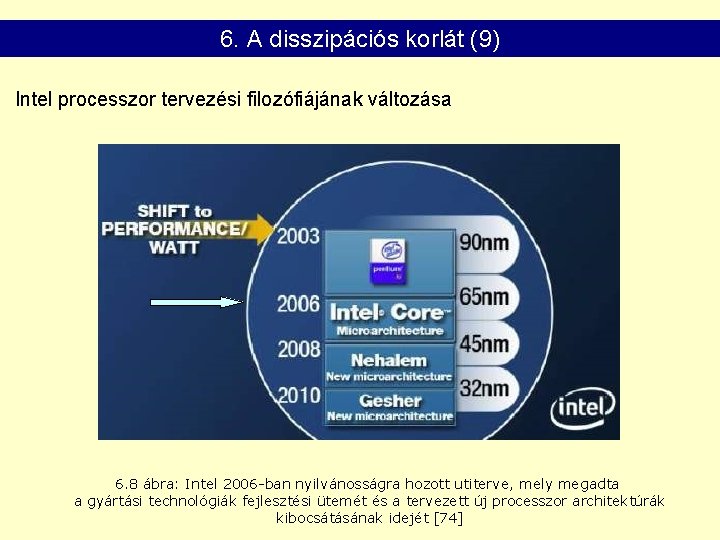

6. A disszipációs korlát (9) Intel processzor tervezési filozófiájának változása 6. 8 ábra: Intel 2006 -ban nyilvánosságra hozott utiterve, mely megadta a gyártási technológiák fejlesztési ütemét és a tervezett új processzor architektúrák kibocsátásának idejét [74]

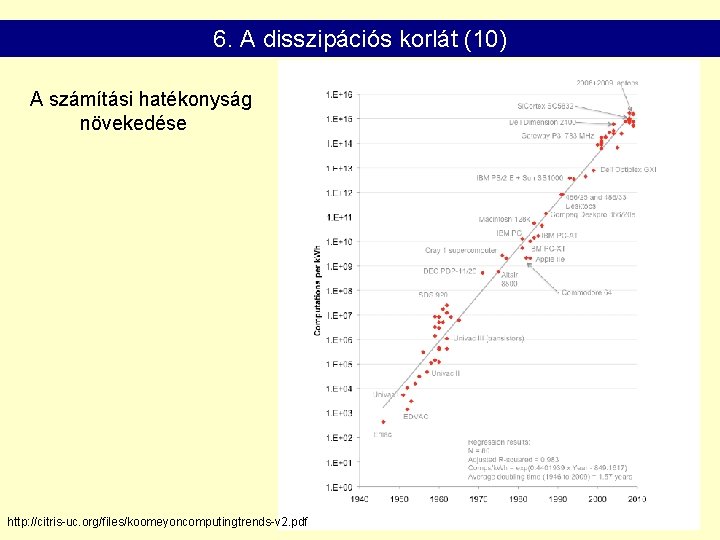

6. A disszipációs korlát (10) A számítási hatékonyság növekedése http: //citris-uc. org/files/koomeyoncomputingtrends-v 2. pdf

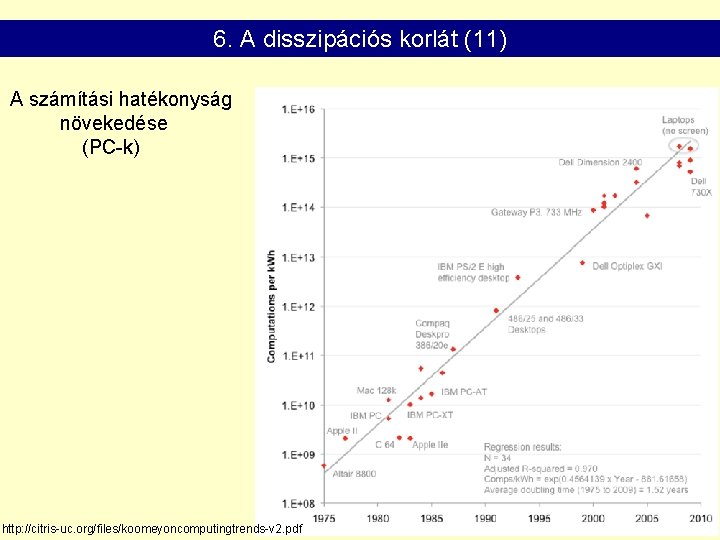

6. A disszipációs korlát (11) A számítási hatékonyság növekedése (PC-k) http: //citris-uc. org/files/koomeyoncomputingtrends-v 2. pdf

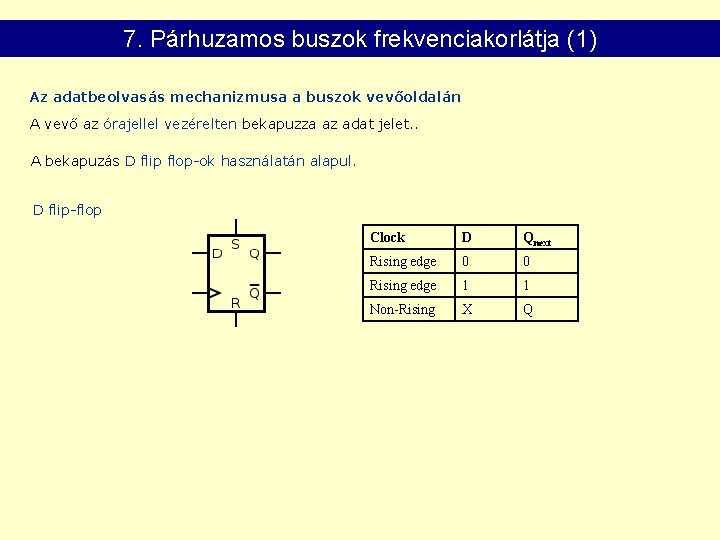

7. Párhuzamos buszok frekvenciakorlátja (1) Az adatbeolvasás mechanizmusa a buszok vevőoldalán A vevő az órajellel vezérelten bekapuzza az adat jelet. . A bekapuzás D flip flop-ok használatán alapul. D flip-flop Clock D Qnext Rising edge 0 0 Rising edge 1 1 Non-Rising X Q

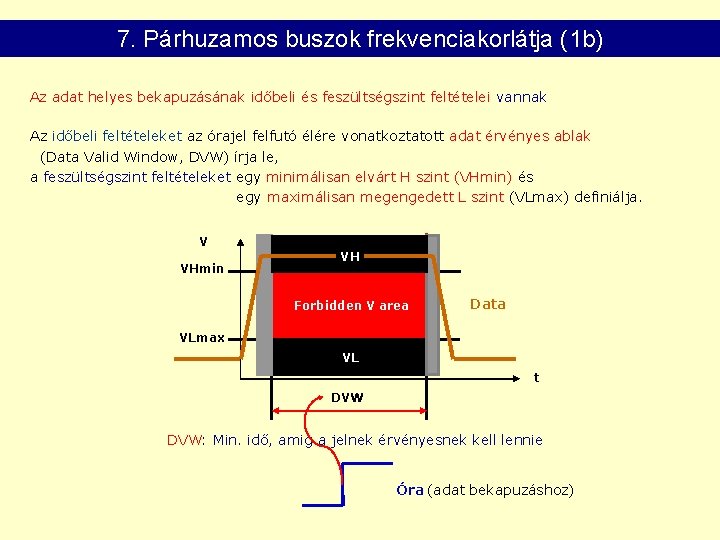

7. Párhuzamos buszok frekvenciakorlátja (1 b) Az adat helyes bekapuzásának időbeli és feszültségszint feltételei vannak Az időbeli feltételeket az órajel felfutó élére vonatkoztatott adat érvényes ablak (Data Valid Window, DVW) írja le, a feszültségszint feltételeket egy minimálisan elvárt H szint (VHmin) és egy maximálisan megengedett L szint (VLmax) definiálja. V VHmin VH Forbidden V area Data VLmax VL t DVW: Min. idő, amig a jelnek érvényesnek kell lennie Óra (adat bekapuzáshoz)

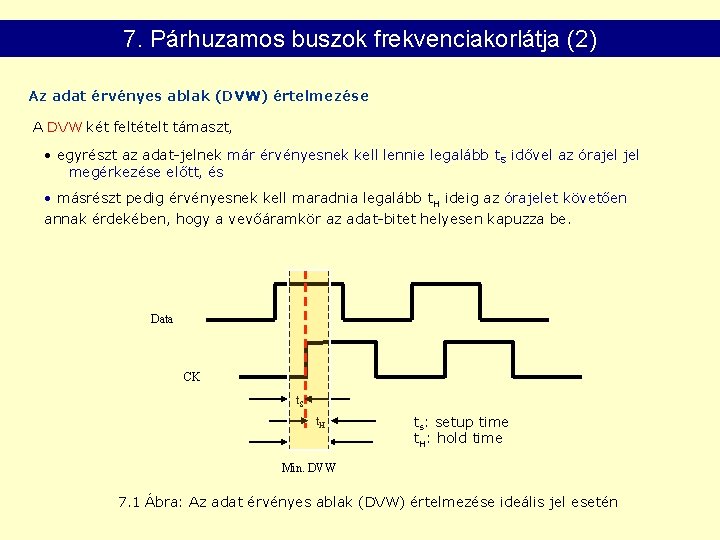

7. Párhuzamos buszok frekvenciakorlátja (2) Az adat érvényes ablak (DVW) értelmezése A DVW két feltételt támaszt, • egyrészt az adat-jelnek már érvényesnek kell lennie legalább t. S idővel az órajel megérkezése előtt, és • másrészt pedig érvényesnek kell maradnia legalább t. H ideig az órajelet követően annak érdekében, hogy a vevőáramkör az adat-bitet helyesen kapuzza be. Data CK t. S t. H ts: setup time t. H: hold time Min. DVW 7. 1 Ábra: Az adat érvényes ablak (DVW) értelmezése ideális jel esetén

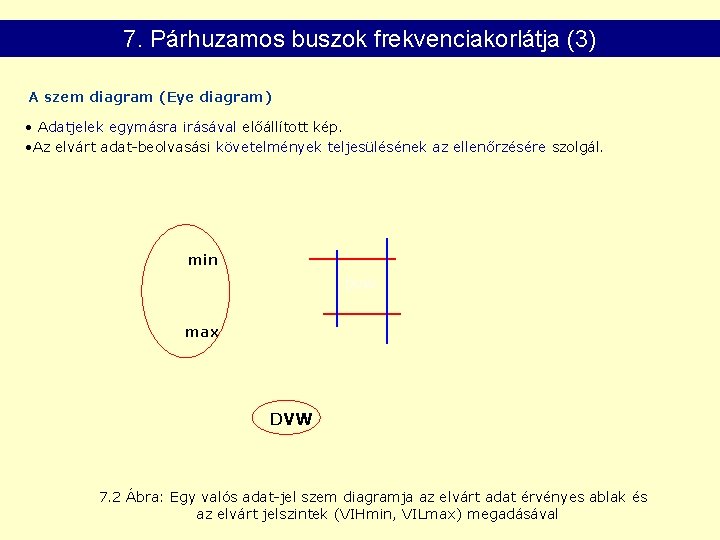

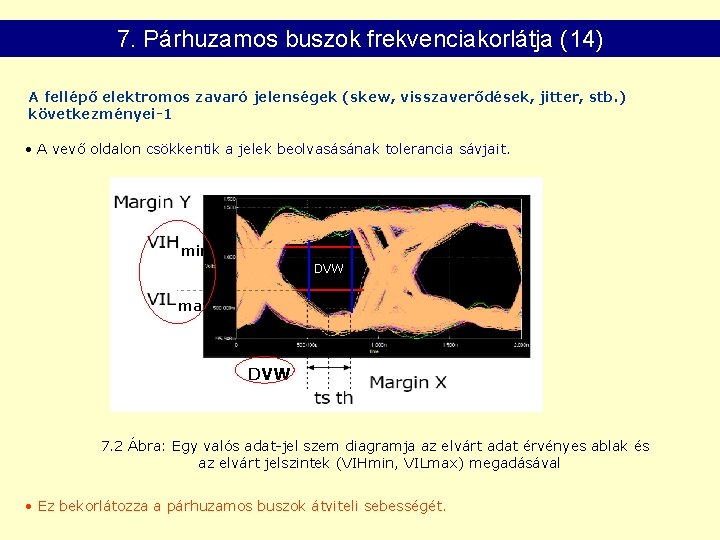

7. Párhuzamos buszok frekvenciakorlátja (3) A szem diagram (Eye diagram) • Adatjelek egymásra irásával előállított kép. • Az elvárt adat-beolvasási követelmények teljesülésének az ellenőrzésére szolgál. min DVW max DVW 7. 2 Ábra: Egy valós adat-jel szem diagramja az elvárt adat érvényes ablak és az elvárt jelszintek (VIHmin, VILmax) megadásával

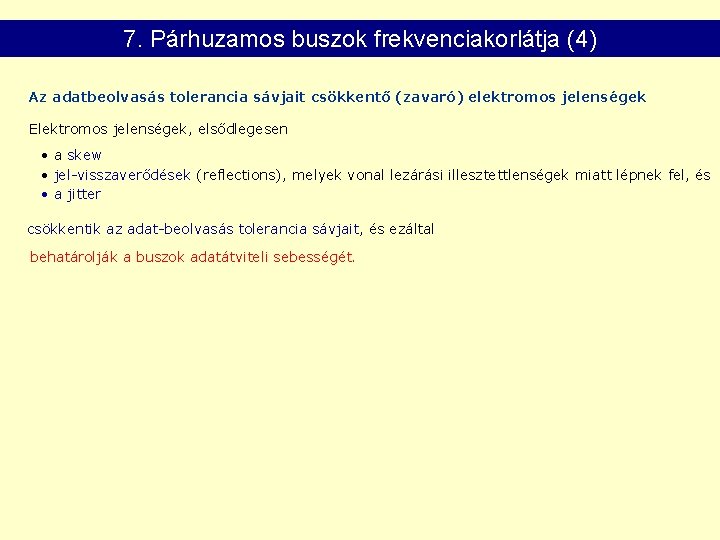

7. Párhuzamos buszok frekvenciakorlátja (4) Az adatbeolvasás tolerancia sávjait csökkentő (zavaró) elektromos jelenségek Elektromos jelenségek, elsődlegesen • a skew • jel-visszaverődések (reflections), melyek vonal lezárási illesztettlenségek miatt lépnek fel, és • a jitter csökkentik az adat-beolvasás tolerancia sávjait, és ezáltal behatárolják a buszok adatátviteli sebességét.

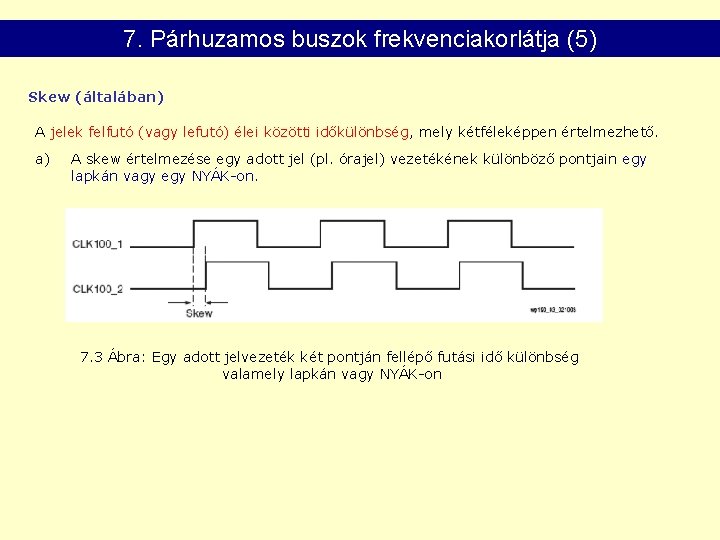

7. Párhuzamos buszok frekvenciakorlátja (5) Skew (általában) A jelek felfutó (vagy lefutó) élei közötti időkülönbség, mely kétféleképpen értelmezhető. a) A skew értelmezése egy adott jel (pl. órajel) vezetékének különböző pontjain egy lapkán vagy egy NYÁK-on. 7. 3 Ábra: Egy adott jelvezeték két pontján fellépő futási idő különbség valamely lapkán vagy NYÁK-on

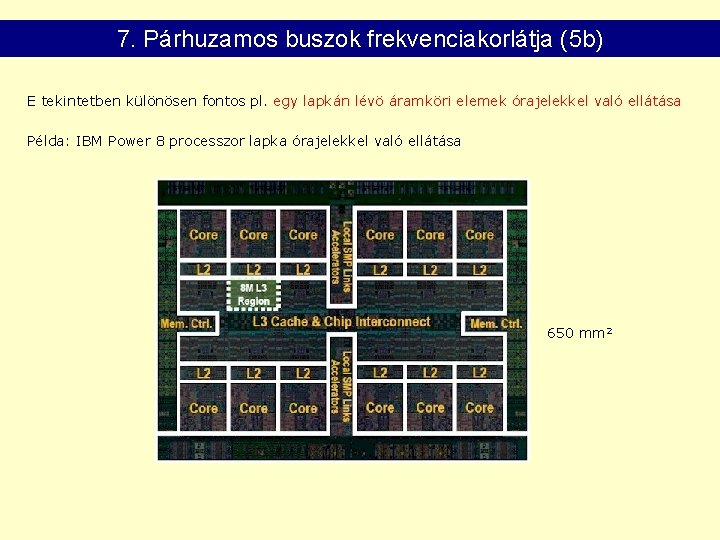

7. Párhuzamos buszok frekvenciakorlátja (5 b) E tekintetben különösen fontos pl. egy lapkán lévö áramköri elemek órajelekkel való ellátása Példa: IBM Power 8 processzor lapka órajelekkel való ellátása 650 mm 2

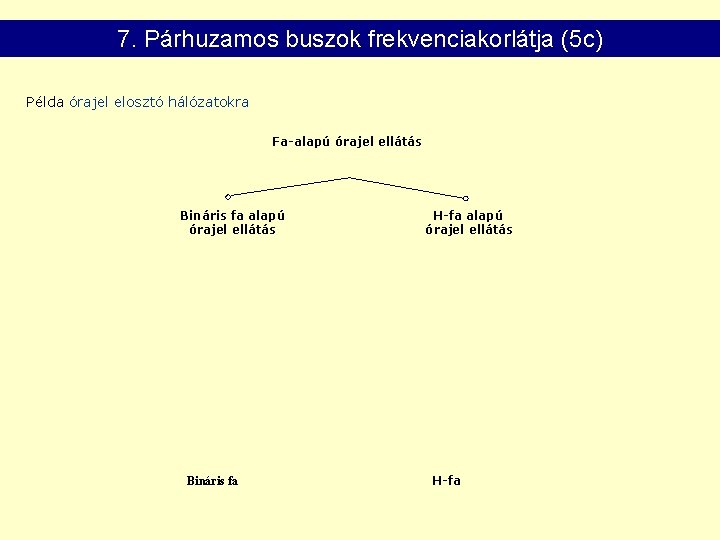

7. Párhuzamos buszok frekvenciakorlátja (5 c) Példa órajel elosztó hálózatokra Fa-alapú órajel ellátás Bináris fa H-fa alapú órajel ellátás H-fa

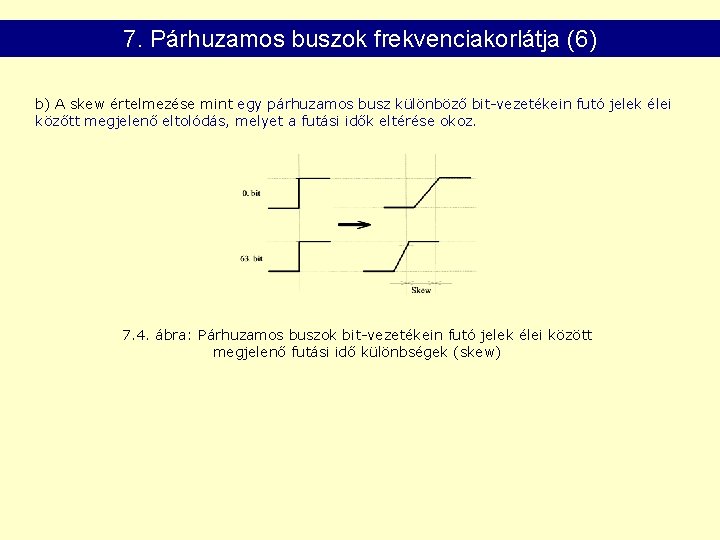

7. Párhuzamos buszok frekvenciakorlátja (6) b) A skew értelmezése mint egy párhuzamos busz különböző bit-vezetékein futó jelek élei közőtt megjelenő eltolódás, melyet a futási idők eltérése okoz. 7. 4. ábra: Párhuzamos buszok bit-vezetékein futó jelek élei között megjelenő futási idő különbségek (skew)

7. Párhuzamos buszok frekvenciakorlátja (7) A párhuzamos buszok egyes bitvezetékei között megjelenő skew előidéző okai (elsődlegesen) a) Párhuzamos buszok egyes bit-vezetékeinek eltérő hosszai NYÁK lapokon. Adott jelterjedési sebesség (time of flight) mellett, melynek értéke kb. 170 ps/inch) [8], ill. kb. 60 ps/cm, a hosszeltérések él-eltolódásokhoz vezetnek. A hossz-különbségeket a tervezők NYÁK lapokon (pl. alaplapokon) bizonyos mértékben kiegyenlítik.

7. Párhuzamos buszok frekvenciakorlátja (8) 7. 5. ábra: A futási idő különbségek (skew) kiegyenlítése az MSI 915 G Combo alaplapon

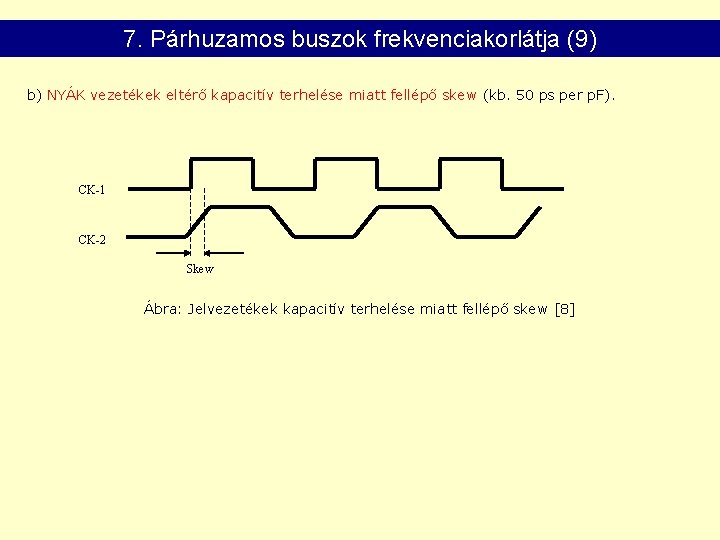

7. Párhuzamos buszok frekvenciakorlátja (9) b) NYÁK vezetékek eltérő kapacitív terhelése miatt fellépő skew (kb. 50 ps per p. F). CK-1 CK-2 Skew Ábra: Jelvezetékek kapacitív terhelése miatt fellépő skew [8]

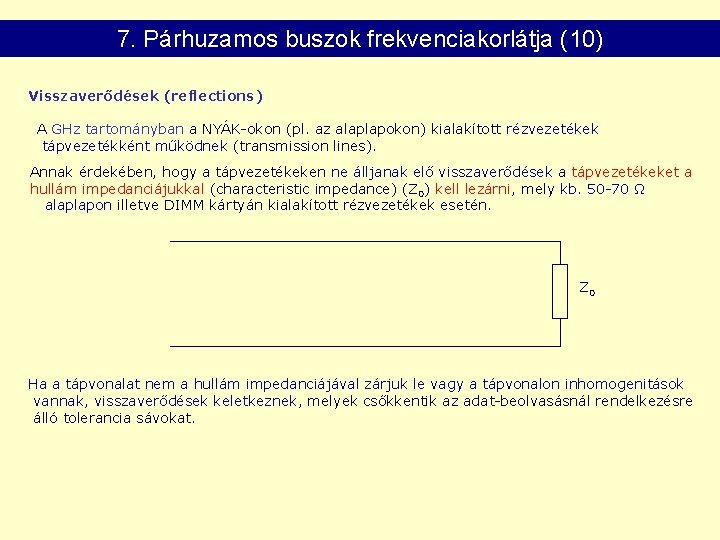

7. Párhuzamos buszok frekvenciakorlátja (10) Visszaverődések (reflections) A GHz tartományban a NYÁK-okon (pl. az alaplapokon) kialakított rézvezetékek tápvezetékként működnek (transmission lines). Annak érdekében, hogy a tápvezetékeken ne álljanak elő visszaverődések a tápvezetékeket a hullám impedanciájukkal (characteristic impedance) (Z 0) kell lezárni, mely kb. 50 -70 Ω alaplapon illetve DIMM kártyán kialakított rézvezetékek esetén. Z 0 Ha a tápvonalat nem a hullám impedanciájával zárjuk le vagy a tápvonalon inhomogenitások vannak, visszaverődések keletkeznek, melyek csőkkentik az adat-beolvasásnál rendelkezésre álló tolerancia sávokat.

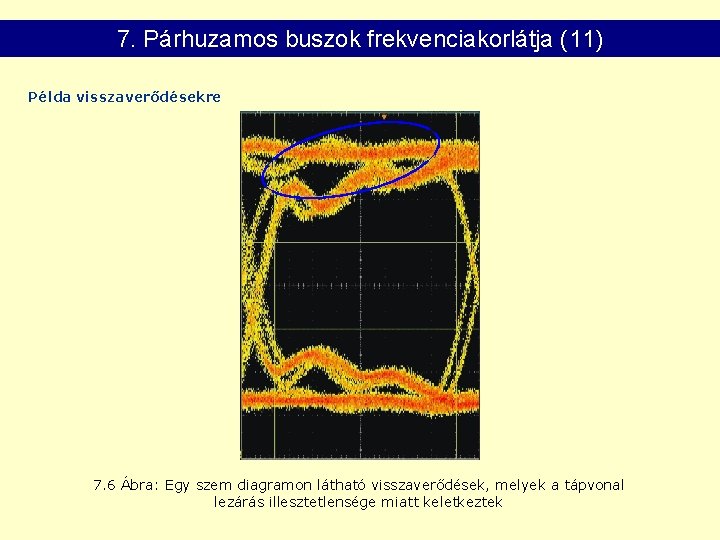

7. Párhuzamos buszok frekvenciakorlátja (11) Példa visszaverődésekre 7. 6 Ábra: Egy szem diagramon látható visszaverődések, melyek a tápvonal lezárás illesztetlensége miatt keletkeztek

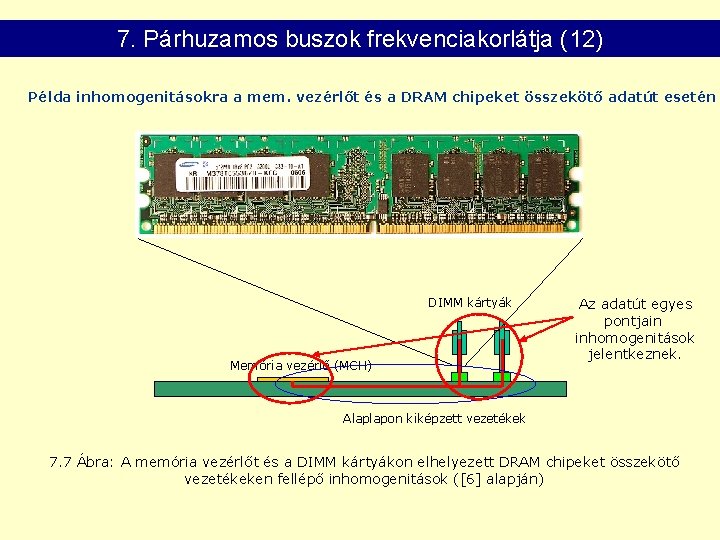

7. Párhuzamos buszok frekvenciakorlátja (12) Példa inhomogenitásokra a mem. vezérlőt és a DRAM chipeket összekötő adatút esetén DIMM kártyák Memória vezérlő (MCH) Az adatút egyes pontjain inhomogenitások jelentkeznek. Alaplapon kiképzett vezetékek 7. 7 Ábra: A memória vezérlőt és a DIMM kártyákon elhelyezett DRAM chipeket összekötő vezetékeken fellépő inhomogenitások ([6] alapján)

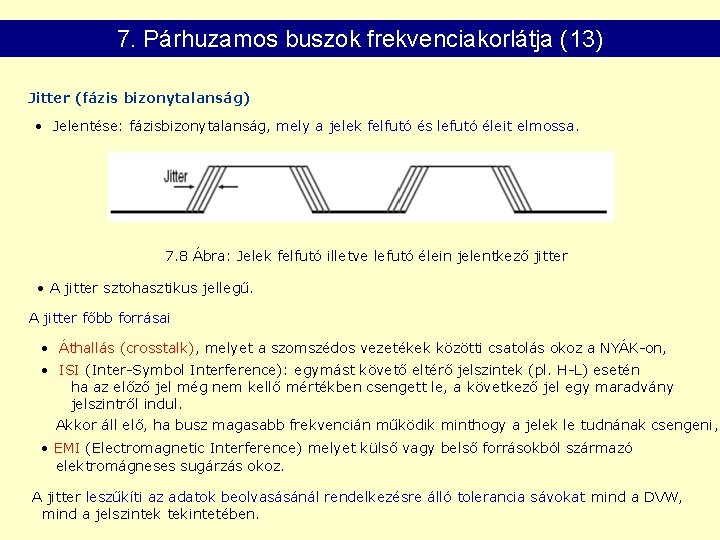

7. Párhuzamos buszok frekvenciakorlátja (13) Jitter (fázis bizonytalanság) • Jelentése: fázisbizonytalanság, mely a jelek felfutó és lefutó éleit elmossa. 7. 8 Ábra: Jelek felfutó illetve lefutó élein jelentkező jitter • A jitter sztohasztikus jellegű. A jitter főbb forrásai • Áthallás (crosstalk), melyet a szomszédos vezetékek közötti csatolás okoz a NYÁK-on, • ISI (Inter-Symbol Interference): egymást követő eltérő jelszintek (pl. H-L) esetén ha az előző jel még nem kellő mértékben csengett le, a következő jel egy maradvány jelszintről indul. Akkor áll elő, ha busz magasabb frekvencián működik minthogy a jelek le tudnának csengeni, • EMI (Electromagnetic Interference) melyet külső vagy belső forrásokból származó elektromágneses sugárzás okoz. A jitter leszűkíti az adatok beolvasásánál rendelkezésre álló tolerancia sávokat mind a DVW, mind a jelszintek tekintetében.

7. Párhuzamos buszok frekvenciakorlátja (14) A fellépő elektromos zavaró jelenségek (skew, visszaverődések, jitter, stb. ) következményei-1 • A vevő oldalon csökkentik a jelek beolvasásának tolerancia sávjait. min DVW max DVW 7. 2 Ábra: Egy valós adat-jel szem diagramja az elvárt adat érvényes ablak és az elvárt jelszintek (VIHmin, VILmax) megadásával • Ez bekorlátozza a párhuzamos buszok átviteli sebességét.

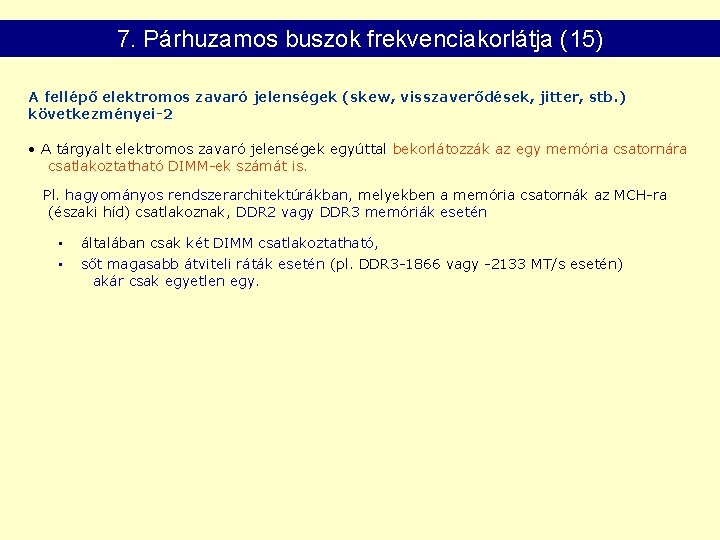

7. Párhuzamos buszok frekvenciakorlátja (15) A fellépő elektromos zavaró jelenségek (skew, visszaverődések, jitter, stb. ) következményei-2 • A tárgyalt elektromos zavaró jelenségek egyúttal bekorlátozzák az egy memória csatornára csatlakoztatható DIMM-ek számát is. Pl. hagyományos rendszerarchitektúrákban, melyekben a memória csatornák az MCH-ra (északi híd) csatlakoznak, DDR 2 vagy DDR 3 memóriák esetén • • általában csak két DIMM csatlakoztatható, sőt magasabb átviteli ráták esetén (pl. DDR 3 -1866 vagy -2133 MT/s esetén) akár csak egyetlen egy.

7. Párhuzamos buszok frekvenciakorlátja (16) Párhuzamos buszok frekvenciakorlátja által kiváltott trend: Soros buszok használata 7. 9. ábra: Jelátvitel soros buszon

7. Párhuzamos buszok frekvenciakorlátja (17) Példák“gyors”soros buszokra: • PCI-e • SATA • SAS • HT (Hyper. Transport bus) • QPI (Quick Path Interconnect bus) Soros buszok bevezetéselassú periféria buszok esetén is(költségokokból!): • USB 2

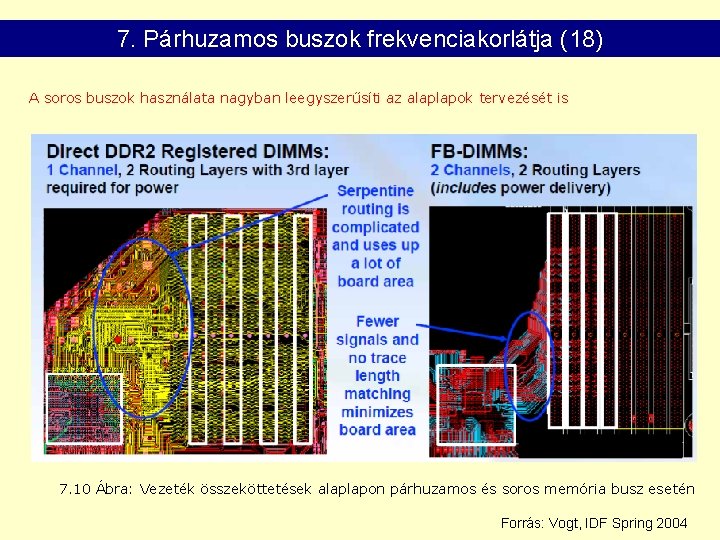

7. Párhuzamos buszok frekvenciakorlátja (18) A soros buszok használata nagyban leegyszerűsíti az alaplapok tervezését is 7. 10 Ábra: Vezeték összeköttetések alaplapon párhuzamos és soros memória busz esetén Forrás: Vogt, IDF Spring 2004

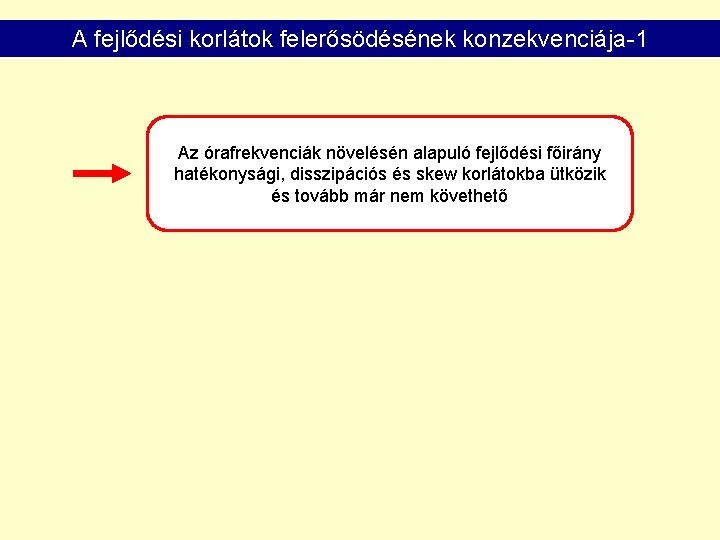

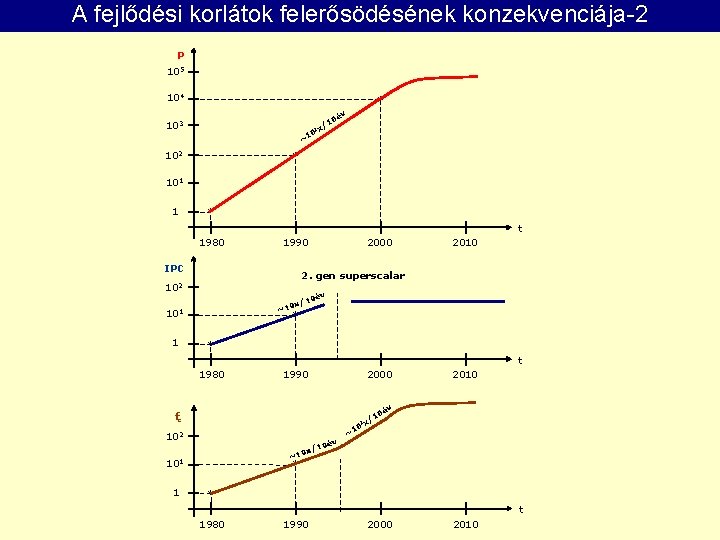

A fejlődési korlátok felerősödésének konzekvenciája-1 Az órafrekvenciák növelésén alapuló fejlődési főirány hatékonysági, disszipációs és skew korlátokba ütközik és tovább már nem követhető

4. 3. 3. Fejlődési korlátok megjelenése (2) • Hatékonysági korlát (5. pont) • Disszipációs korlát (6. pont) • Párhuzamos buszok frekvenciakorlátja (7. pont) Órafrekvenciák bekorlátozása Disszipáció csökkentés előtérbe kerülése Soros buszok

A fejlődési korlátok felerősödésének konzekvenciája-2 P 105 104 * 103 2 x 0 ~1 102 v 0é /1 * 101 1 * t 1980 1990 IPC 2000 2010 2. gen superscalar 102 év /10 0 x ~1 101 1 * * t 1980 1990 2000 v 0é fc /1 2 x 0 1 102 0év x/1 ~ 0 ~1 101 1 2010 * * t 1980 1990 2000 2010

8. EPIC architektúrák/processzorok (1) Az órafrekvencia erőteljes növelése EPIC architektúrák kifejlesztése (4. – 7. pontok) (8. pont) A fejlődés fővonala

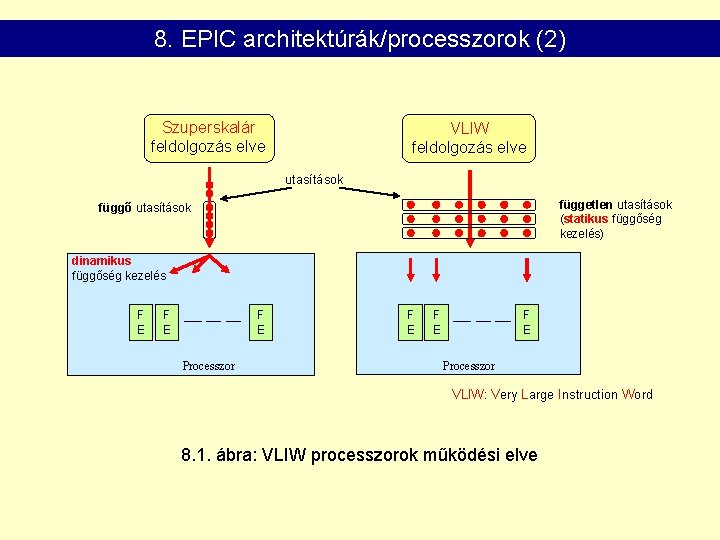

8. EPIC architektúrák/processzorok (2) Szuperskalár feldolgozás elve VLIW feldolgozás elve utasítások független utasítások (statikus függőség kezelés) függő utasítások dinamikus függőség kezelés F E F E F E Processzor VLIW: Very Large Instruction Word 8. 1. ábra: VLIW processzorok működési elve

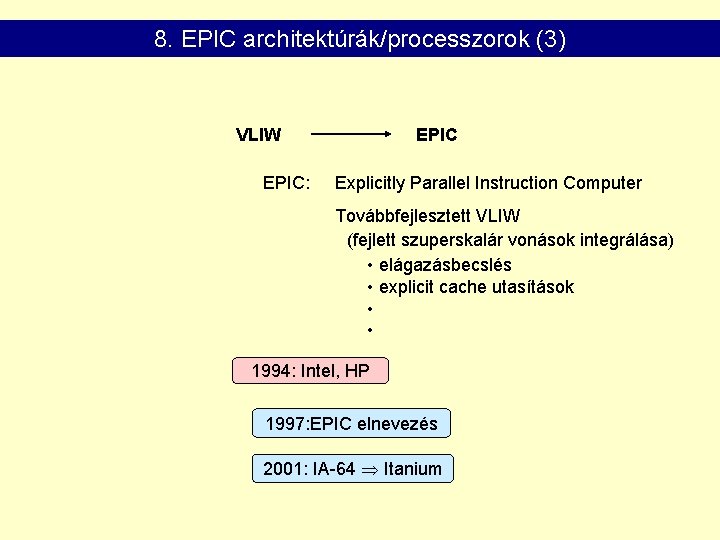

8. EPIC architektúrák/processzorok (3) VLIW EPIC: EPIC Explicitly Parallel Instruction Computer Továbbfejlesztett VLIW (fejlett szuperskalár vonások integrálása) • elágazásbecslés • explicit cache utasítások • • 1994: Intel, HP 1997: EPIC elnevezés 2001: IA-64 Itanium

8. EPIC architektúrák/processzorok (4) Tukwila (2/2010) 8. 2. ábra: Itanium alapú magok áttekintése

8. EPIC architektúrák/processzorok (5) 8. 3. ábra: Itanium processzorok hatékonysága

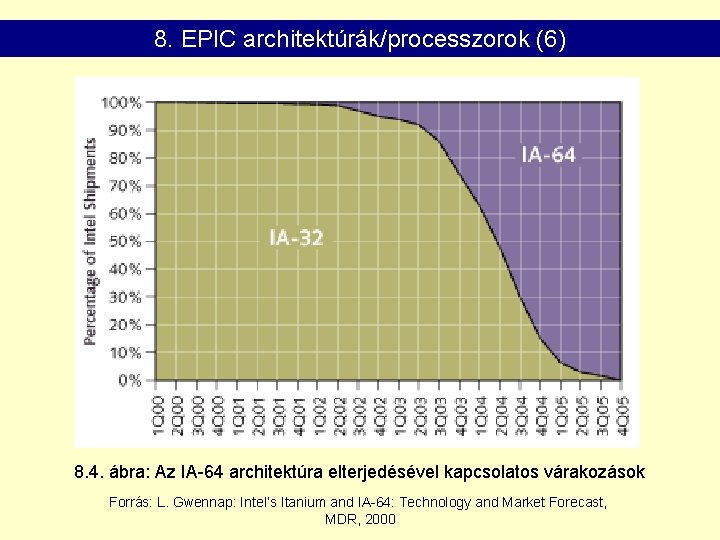

8. EPIC architektúrák/processzorok (6) 8. 4. ábra: Az IA-64 architektúra elterjedésével kapcsolatos várakozások Forrás: L. Gwennap: Intel’s Itanium and IA-64: Technology and Market Forecast, MDR, 2000

8. EPIC architektúrák/processzorok (7) 8. 5. ábra: Az Itanium processzorok értékesítési elvárásainak módosulása

8. EPIC architektúrák/processzorok (8) az EPIC architektúrák/processzorok kiszorulása • Microsoft 2010 áprilisában bejelentette, hogy a továbbiakban nem támogatja az Itanium architektúrát. Windows Server 2008 R 2/SQL Server 2008 R 2 és Visual Studio 2010 lesz az utolsó szerver szoftver környezet, mely támogatja az Itanium-ot. • 2011 márciusában Oracle is bejelentette, hogy a jövőben beszünteti szoftver fejlesztéseit az Itanium architektúrára.

9. Paradigmaváltás (1) Általános célú alkalmazásokban a 2. generációs szuperskalárok megjelenésével a processzorok hatékonysága stagnálni kezdett, ez két fejlesztési főirányt váltott ki, de mindkét megközelítés korlátokba ütközött Egymagos szuperskalárok alkonya

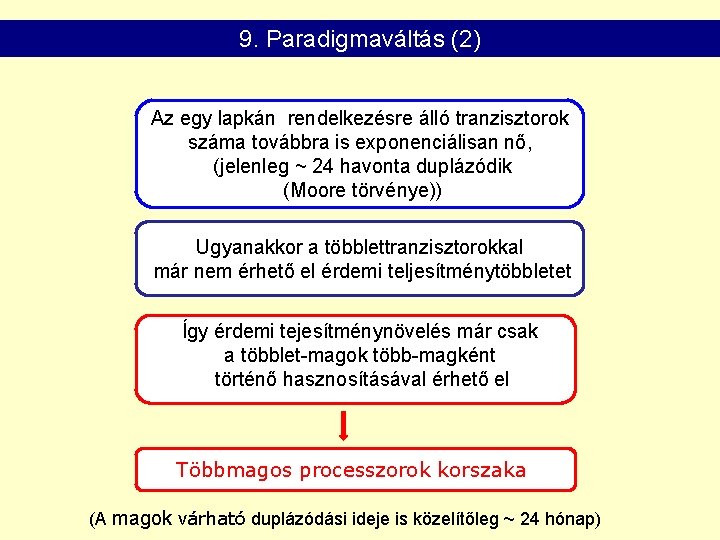

9. Paradigmaváltás (2) Az egy lapkán rendelkezésre álló tranzisztorok száma továbbra is exponenciálisan nő, (jelenleg ~ 24 havonta duplázódik (Moore törvénye)) Ugyanakkor a többlettranzisztorokkal már nem érhető el érdemi teljesítménytöbbletet Így érdemi tejesítménynövelés már csak a többlet-magok több-magként történő hasznosításával érhető el Többmagos processzorok korszaka (A magok várható duplázódási ideje is közelítőleg ~ 24 hónap)

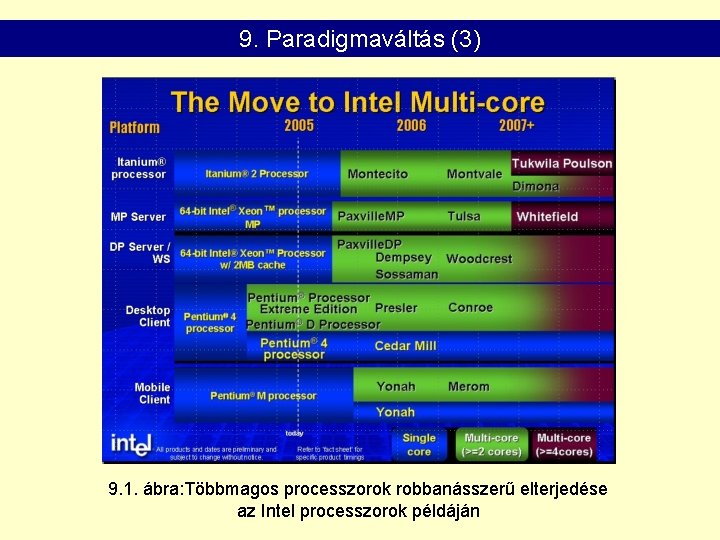

9. Paradigmaváltás (3) 9. 1. ábra: Többmagos processzorok robbanásszerű elterjedése az Intel processzorok példáján

- Slides: 96