KLMH 1 VLSI Physical Design From Graph Partitioning

- Slides: 30

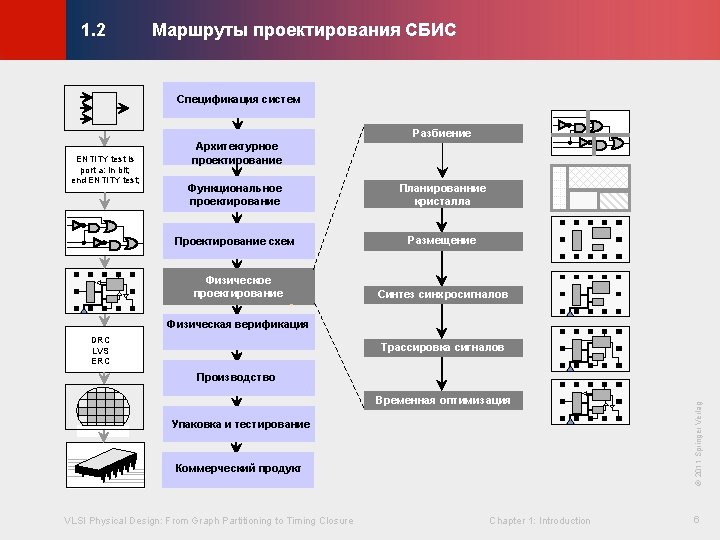

© KLMH Физическое Проектирование СБИС: от Разбиения Графов до Оптимизации Временных Характеристик Глава 1 – Введение Авторы книги: VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 1 Lienig Andrew B. Kahng, Jens Lienig, Igor L. Markov, Jin Hu

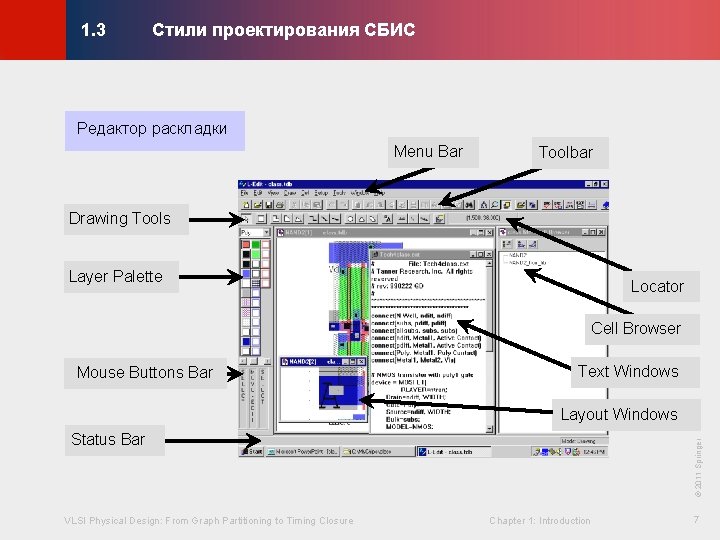

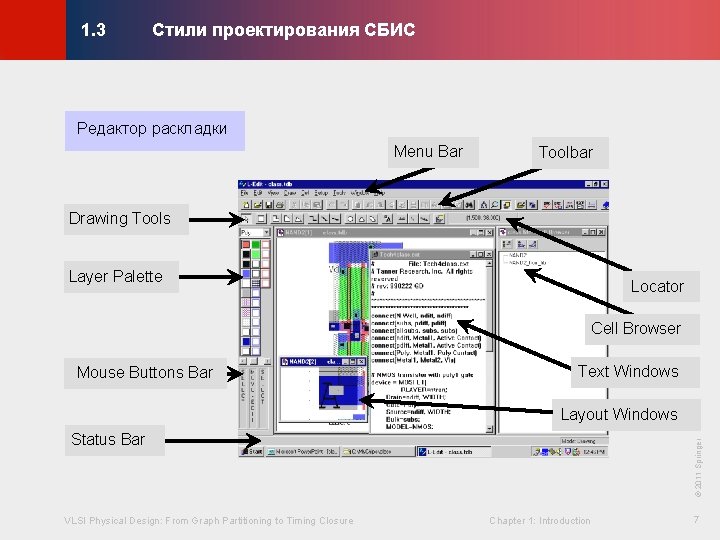

Стили проектирования СБИС © KLMH 1. 3 Редактор раскладки Menu Bar Toolbar Drawing Tools Layer Palette Locator Cell Browser Mouse Buttons Bar Text Windows Layout Windows Chapter 1: Introduction 7 Lienig VLSI Physical Design: From Graph Partitioning to Timing Closure © 2011 Springer Status Bar

Стили проектирования СБИС © KLMH 1. 3 Типичные цифровые вентили IN 1 IN 2 OR OUT IN 1 IN 2 INV NAND OUT IN 1 IN 2 NOR OUT IN 1 IN 2 OUT 0 0 0 0 1 1 0 0 1 0 1 1 0 0 0 1 1 1 0 0 1 1 1 1 1 0 VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 8 Lienig AND

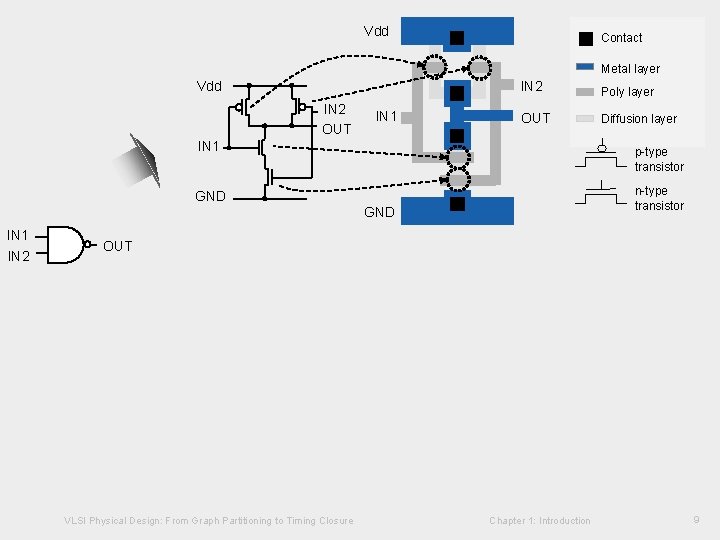

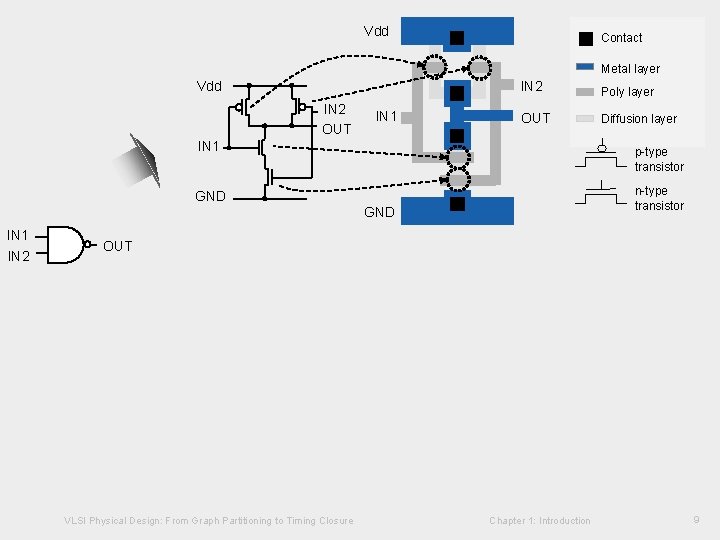

VLSI Design Styles Vdd Contact Metal layer Vdd IN 2 OUT IN 1 IN 2 Poly layer OUT Diffusion layer IN 1 GND IN 2 p-type transistor n-type transistor GND OUT VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 9 Lienig IN 1 © KLMH 1. 3

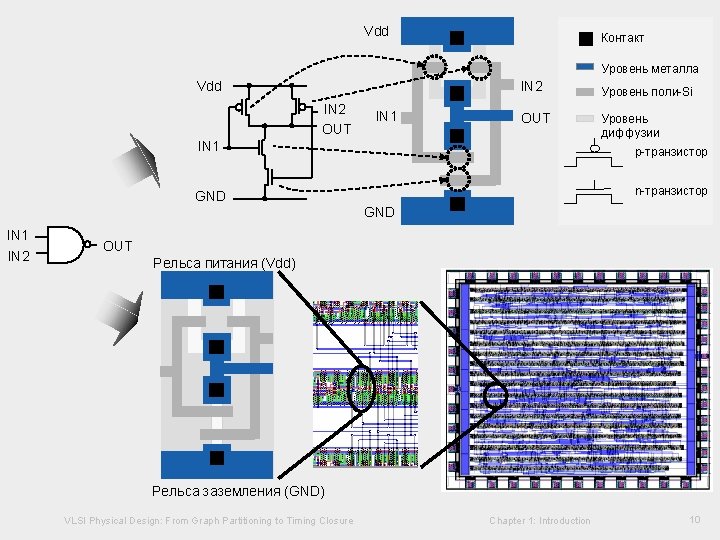

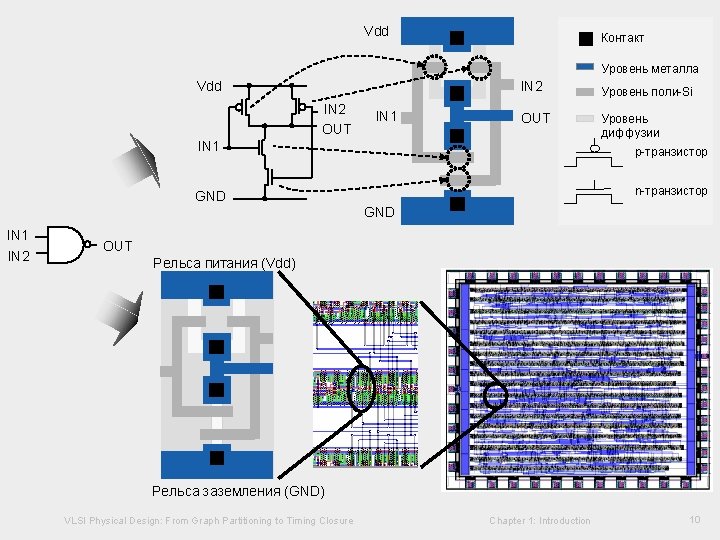

1. 3 VLSI Design Styles Vdd Контакт Vdd IN 2 OUT IN 1 GND IN 2 Уровень диффузии p-транзистор n-транзистор GND OUT Рельса питания (Vdd) Рельса заземления (GND) VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 10 Lienig IN 1 Уровень поли-Si © KLMH Уровень металла

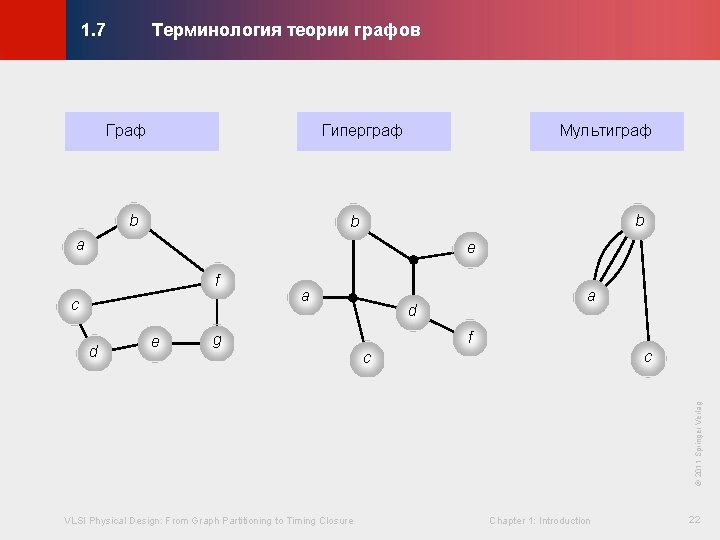

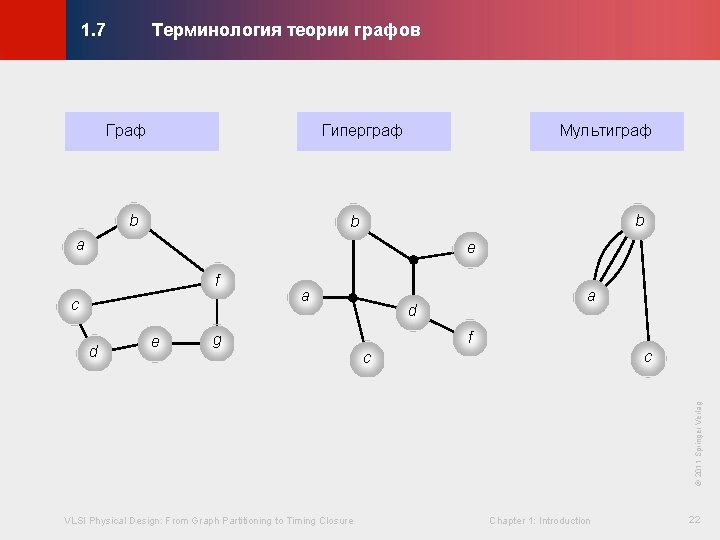

Терминология теории графов © KLMH 1. 7 Граф Гиперграф b Мультиграф b b a e f c g a d f c c VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 22 Lienig © 2011 Springer Verlag d e a

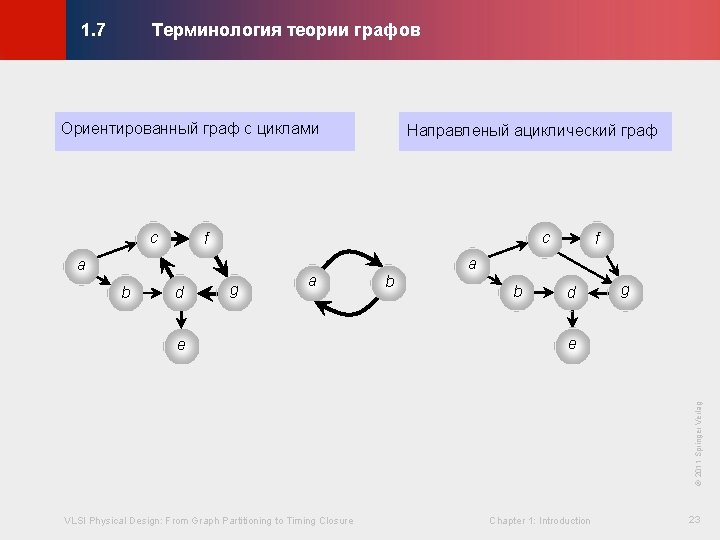

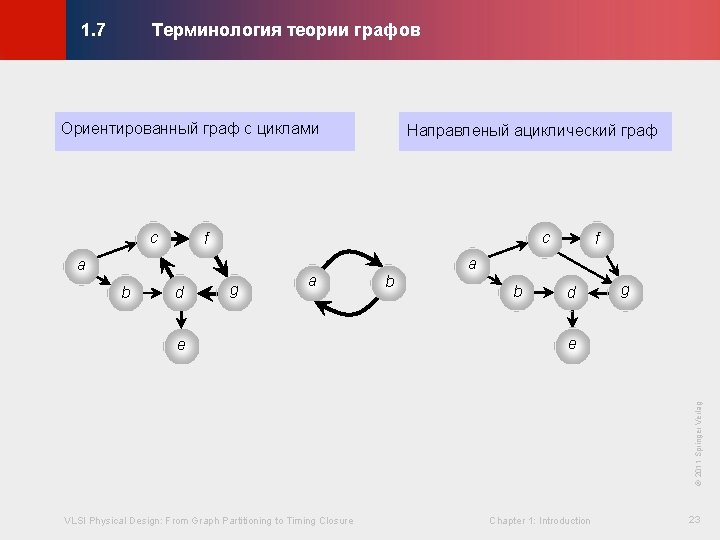

Терминология теории графов © KLMH 1. 7 Ориентированный граф с циклами c c f a b Направленый ациклический граф d g a a b d g e VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 23 Lienig © 2011 Springer Verlag e b f

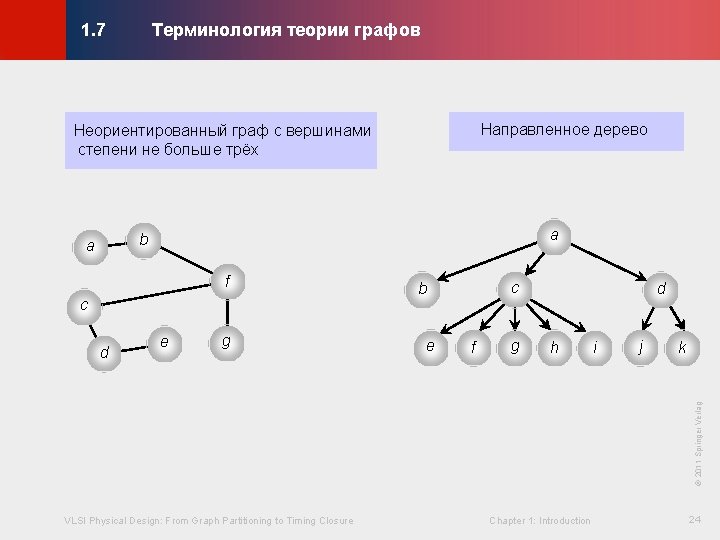

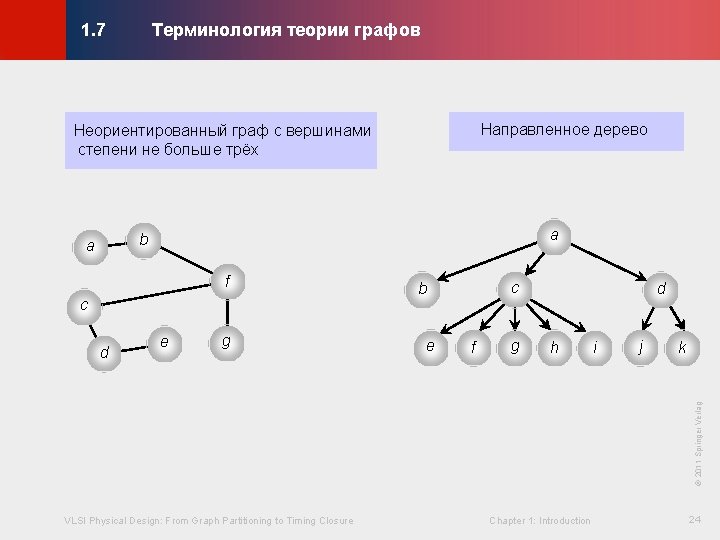

Терминология теории графов © KLMH 1. 7 Направленное дерево Неориентированный граф с вершинами степени не больше трёх a b a f c e g e f g d h i j k VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 24 Lienig © 2011 Springer Verlag d c b

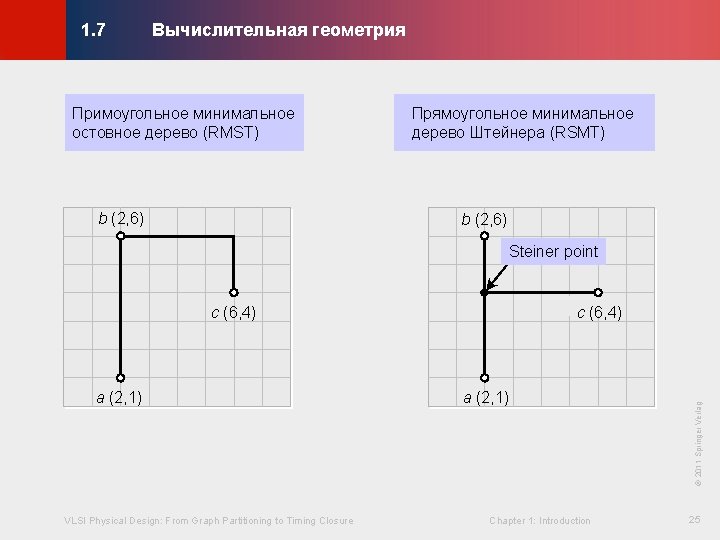

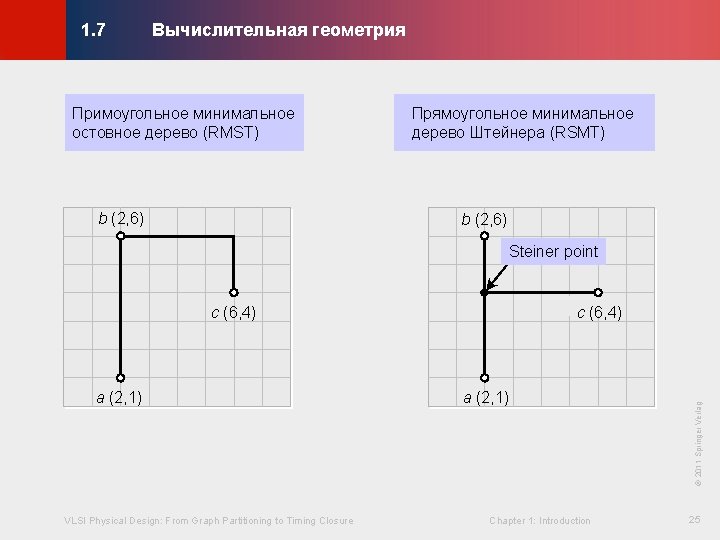

Вычислительная геометрия © KLMH 1. 7 Примоугольное минимальное остовное дерево (RMST) b (2, 6) Прямоугольное минимальное дерево Штейнера (RSMT) b (2, 6) Steiner point VLSI Physical Design: From Graph Partitioning to Timing Closure a (2, 1) Chapter 1: Introduction © 2011 Springer Verlag a (2, 1) c (6, 4) 25 Lienig c (6, 4)

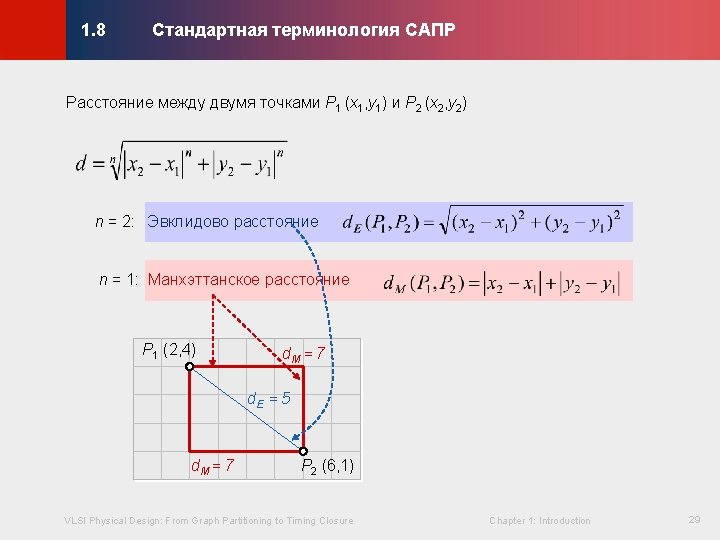

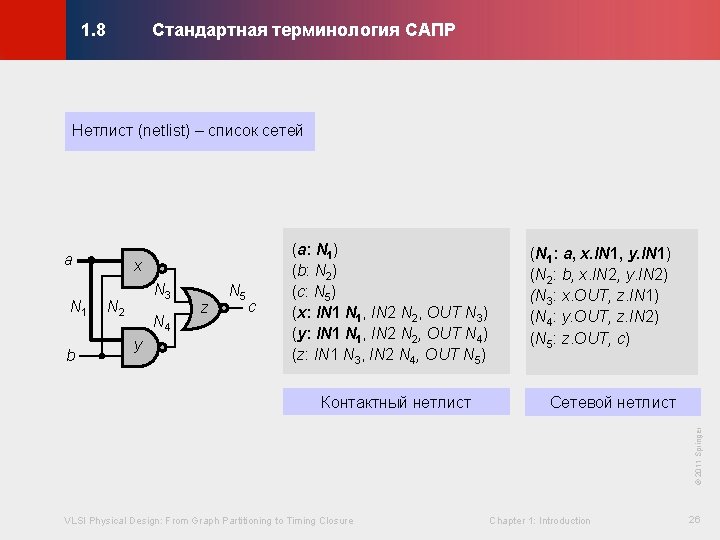

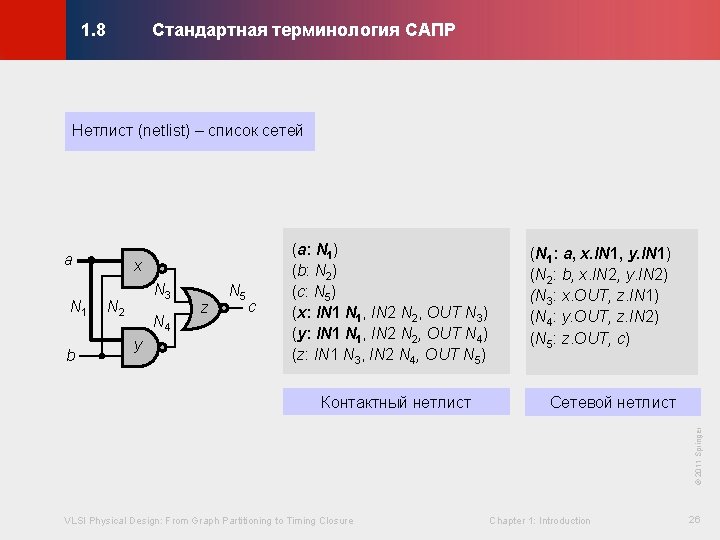

Стандартная терминология САПР © KLMH 1. 8 Нетлист (netlist) – список сетей a N 1 b x N 3 N 2 N 4 y z N 5 c (a: N 1) (b: N 2) (c: N 5) (x: IN 1 N 1, IN 2 N 2, OUT N 3) (y: IN 1 N 1, IN 2 N 2, OUT N 4) (z: IN 1 N 3, IN 2 N 4, OUT N 5) Сетевой нетлист VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 26 Lienig © 2011 Springer Контактный нетлист (N 1: a, x. IN 1, y. IN 1) (N 2: b, x. IN 2, y. IN 2) (N 3: x. OUT, z. IN 1) (N 4: y. OUT, z. IN 2) (N 5: z. OUT, c)

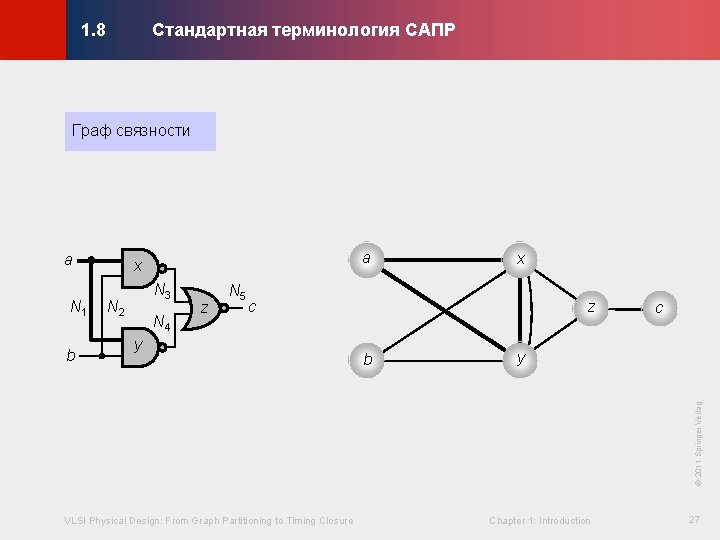

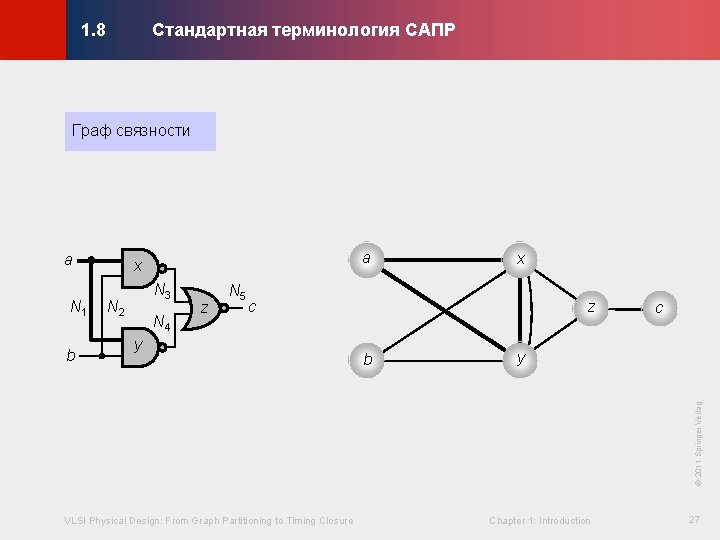

Стандартная терминология САПР © KLMH 1. 8 Граф связности a N 1 N 3 N 2 N 4 z N 5 x c y z b c y VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 27 Lienig © 2011 Springer Verlag b a x

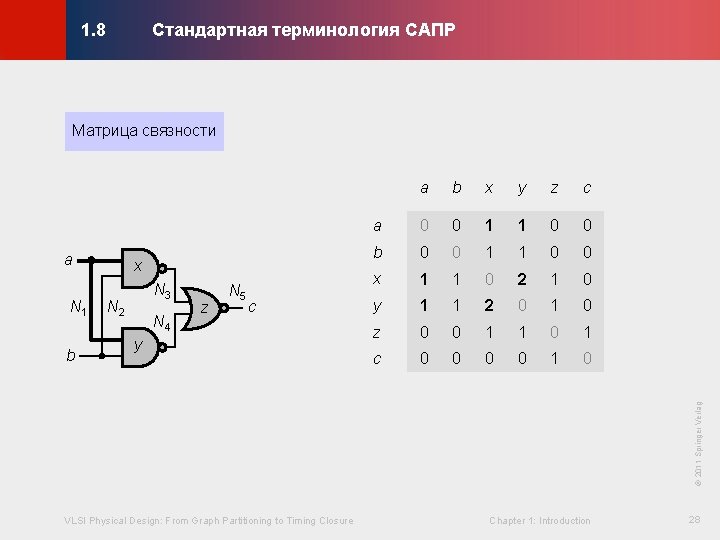

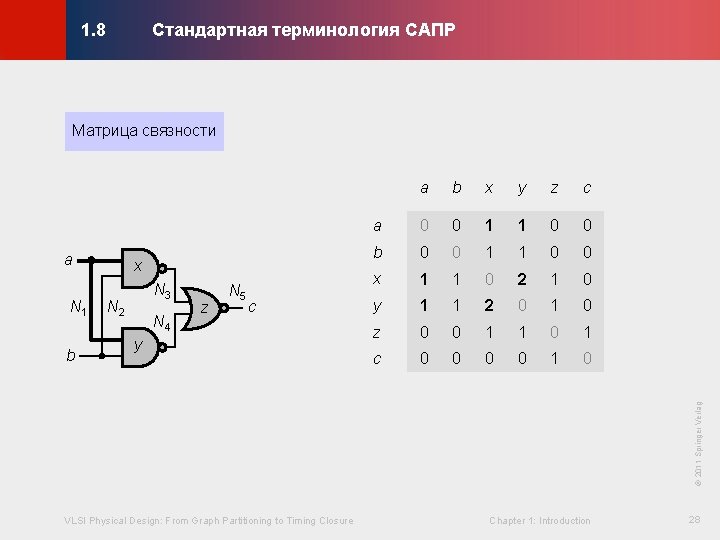

Стандартная терминология САПР © KLMH 1. 8 Матрица связности a N 1 N 3 N 2 N 4 z N 5 c y b x y z c a 0 0 1 1 0 0 b 0 0 1 1 0 0 x 1 1 0 2 1 0 y 1 1 2 0 1 0 z 0 0 1 1 0 1 c 0 0 1 0 VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 28 Lienig © 2011 Springer Verlag b x a