KIRK CH 09 FIGURE 9 1 Electrostatic potential

![KIRK CH: 09 FIGURE 9. 2 The contribution of atom[i] to the electrostatic potential KIRK CH: 09 FIGURE 9. 2 The contribution of atom[i] to the electrostatic potential](https://slidetodoc.com/presentation_image_h/23c4654010a354989b1f7149904c2838/image-2.jpg)

- Slides: 12

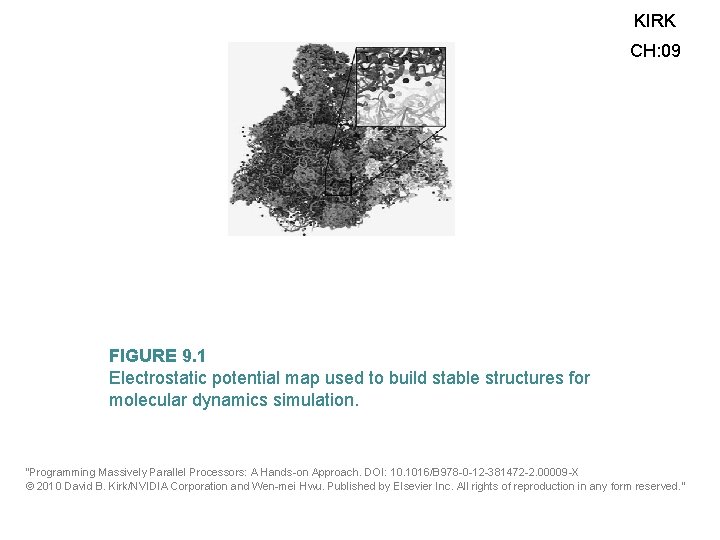

KIRK CH: 09 FIGURE 9. 1 Electrostatic potential map used to build stable structures for molecular dynamics simulation. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

![KIRK CH 09 FIGURE 9 2 The contribution of atomi to the electrostatic potential KIRK CH: 09 FIGURE 9. 2 The contribution of atom[i] to the electrostatic potential](https://slidetodoc.com/presentation_image_h/23c4654010a354989b1f7149904c2838/image-2.jpg)

KIRK CH: 09 FIGURE 9. 2 The contribution of atom[i] to the electrostatic potential at lattice point j (potential[j]) is atom[i]. charge/rij. In the direct Coulomb summation (DCS) method, the total potential at lattice point j is the sum of contributions from all atoms in the system. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

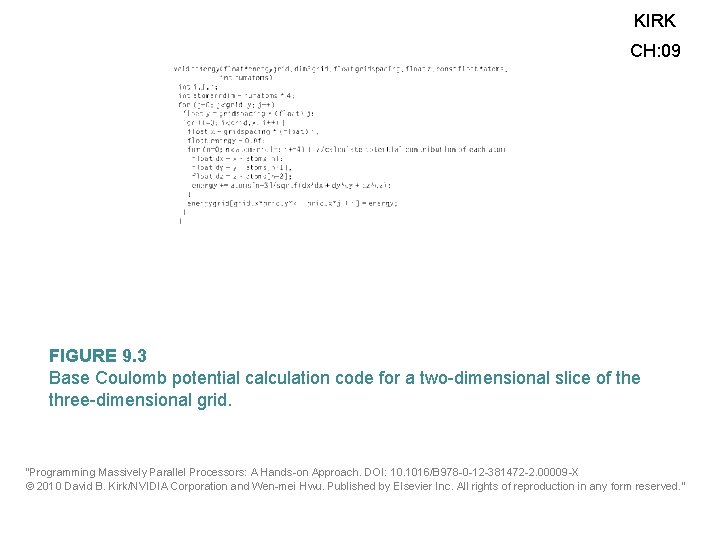

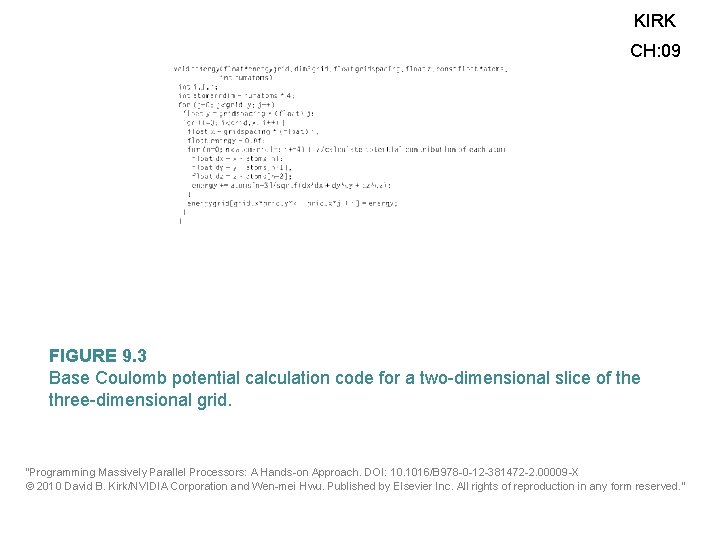

KIRK CH: 09 FIGURE 9. 3 Base Coulomb potential calculation code for a two-dimensional slice of the three-dimensional grid. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

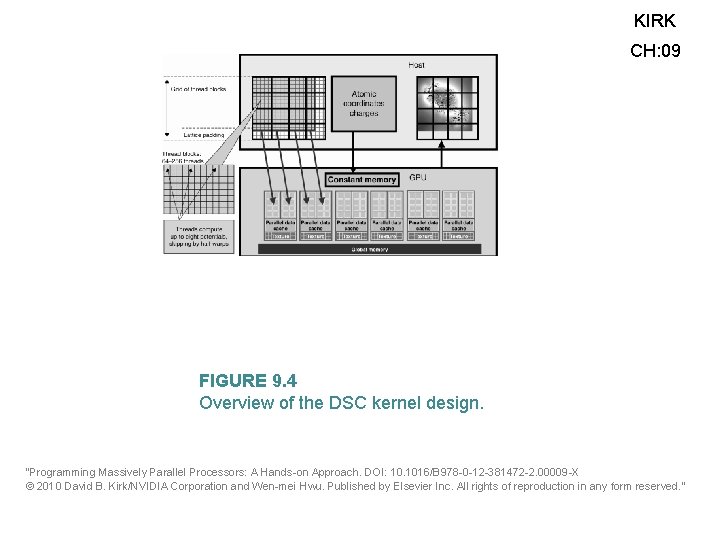

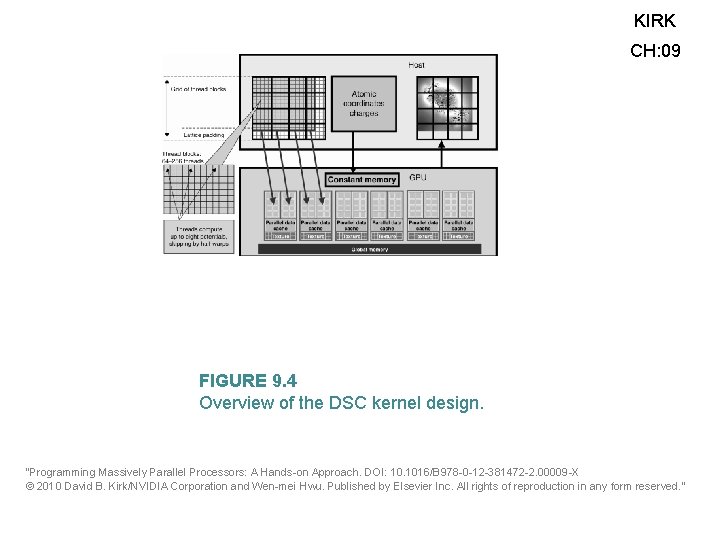

KIRK CH: 09 FIGURE 9. 4 Overview of the DSC kernel design. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

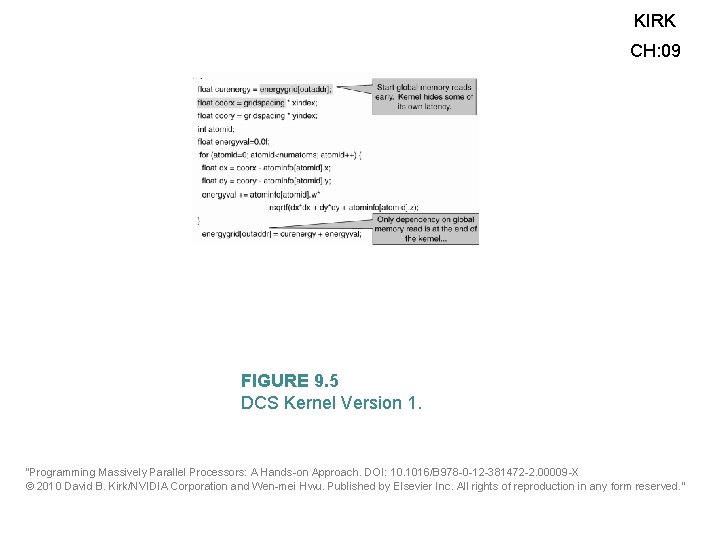

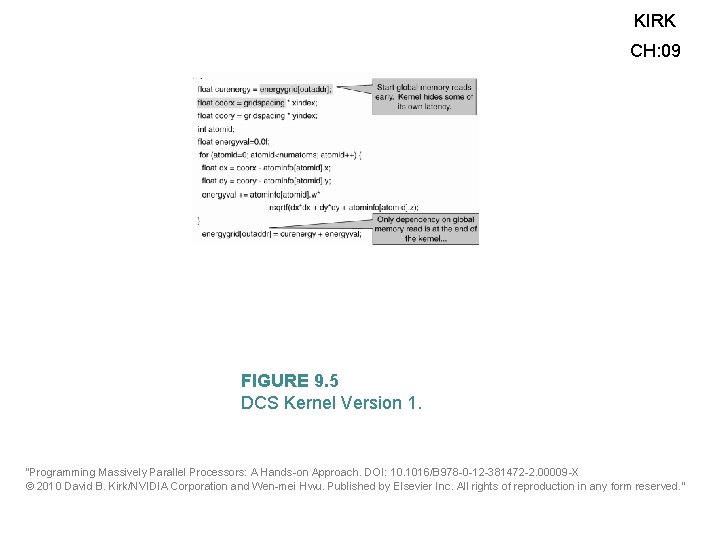

KIRK CH: 09 FIGURE 9. 5 DCS Kernel Version 1. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

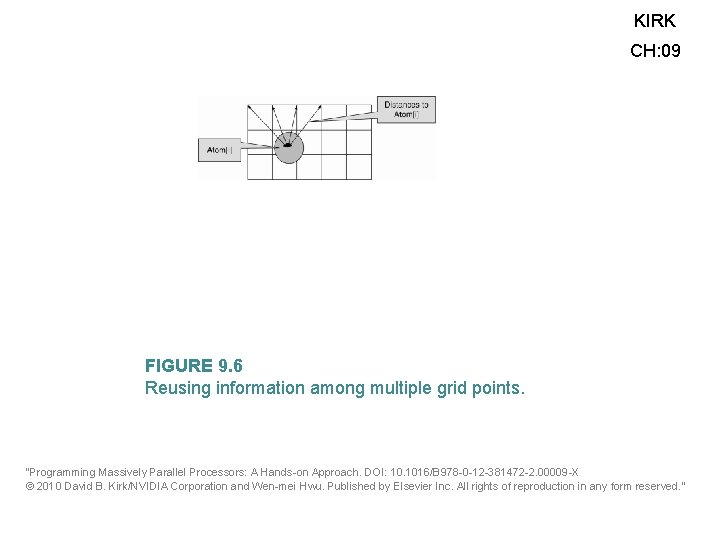

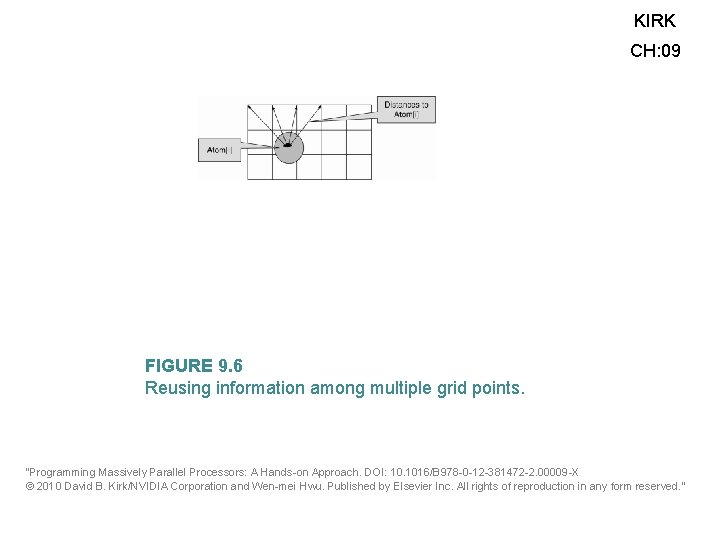

KIRK CH: 09 FIGURE 9. 6 Reusing information among multiple grid points. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

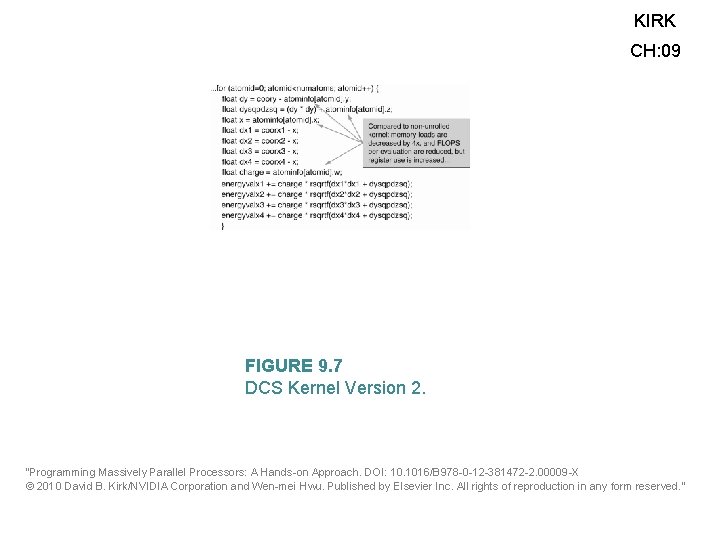

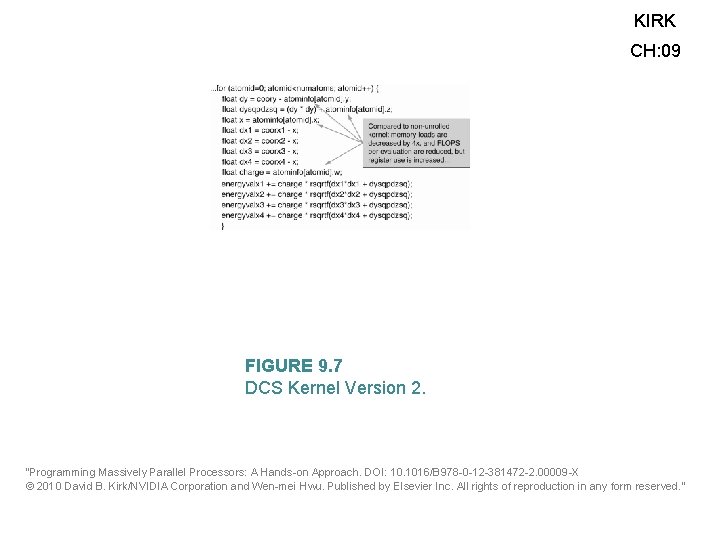

KIRK CH: 09 FIGURE 9. 7 DCS Kernel Version 2. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

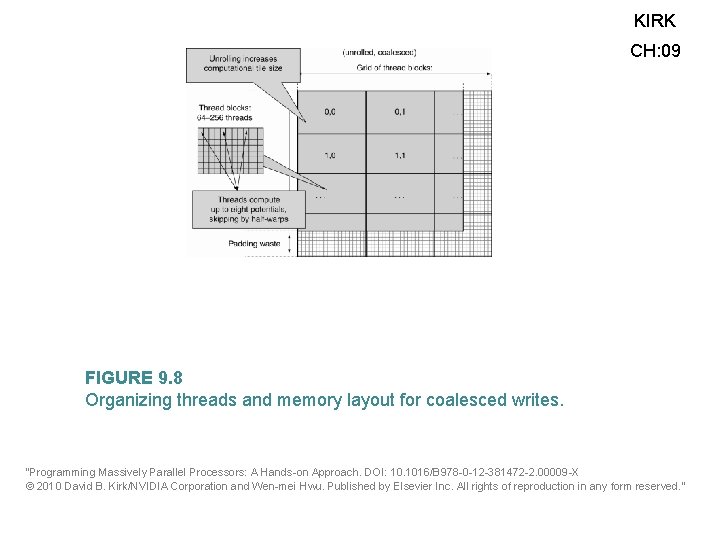

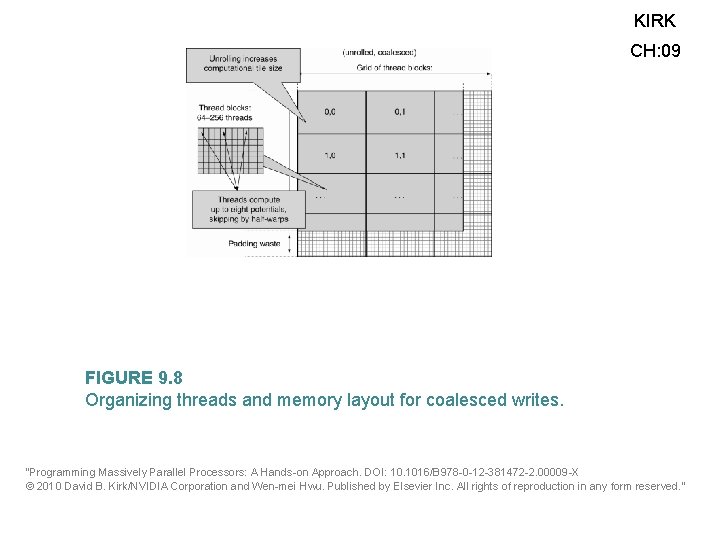

KIRK CH: 09 FIGURE 9. 8 Organizing threads and memory layout for coalesced writes. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

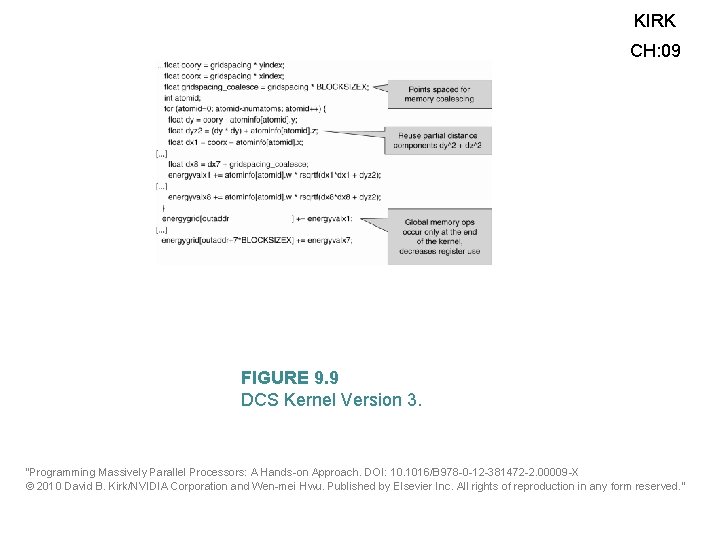

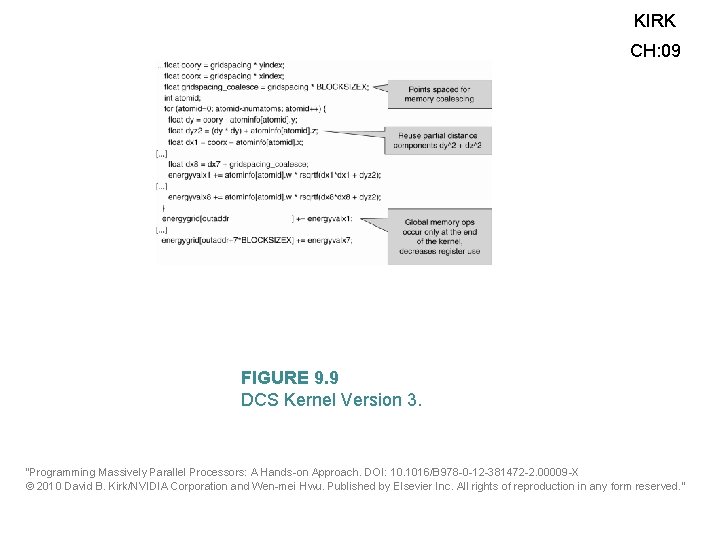

KIRK CH: 09 FIGURE 9. 9 DCS Kernel Version 3. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

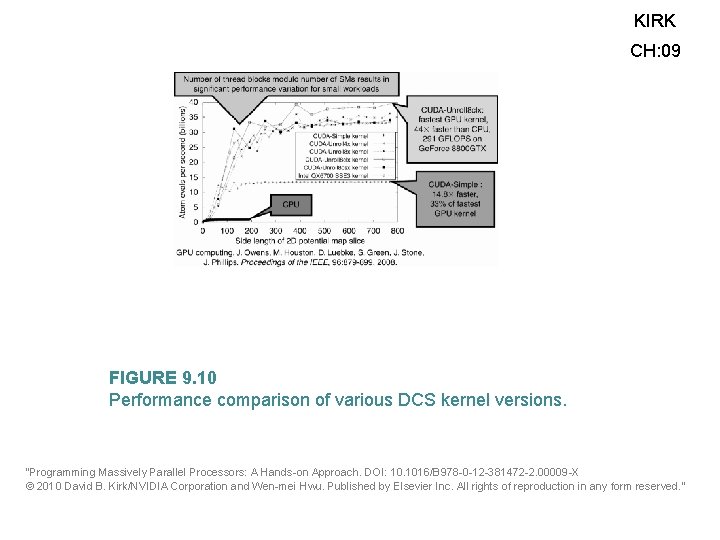

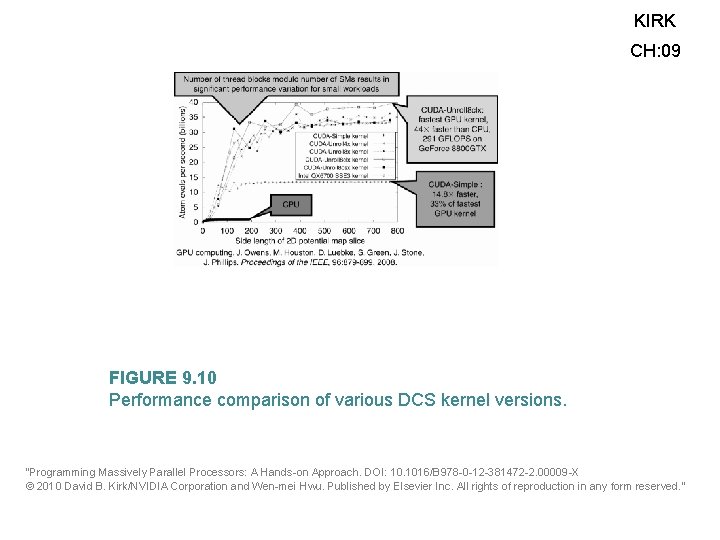

KIRK CH: 09 FIGURE 9. 10 Performance comparison of various DCS kernel versions. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

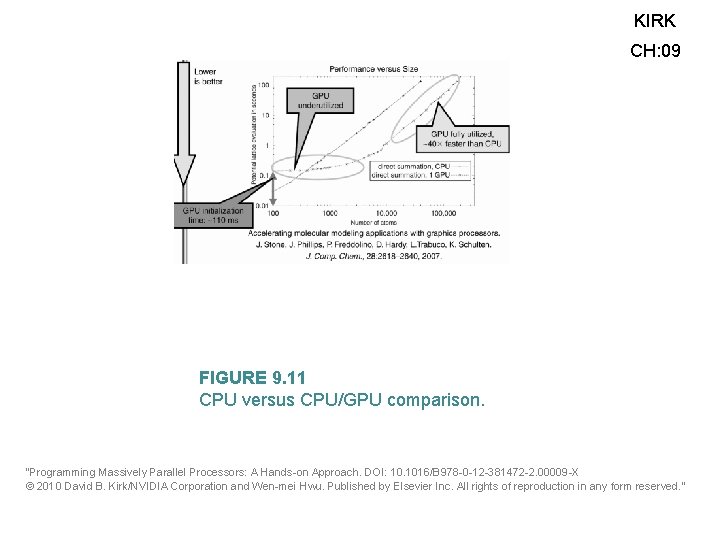

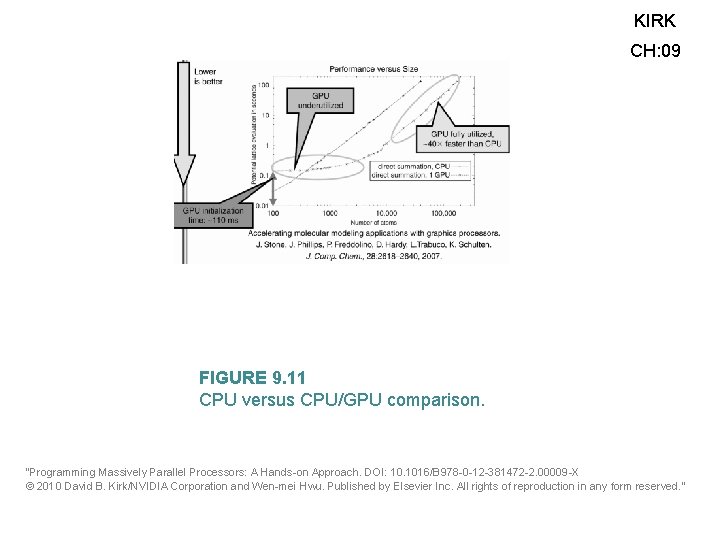

KIRK CH: 09 FIGURE 9. 11 CPU versus CPU/GPU comparison. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

KIRK CH: 09 FIGURE 9. 12 A PC with three Ge. Force® 8800 GTX GPUs at 700 W of total system power. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”