KIRK CH 05 FIGURE 5 1 Matrix multiplication

- Slides: 8

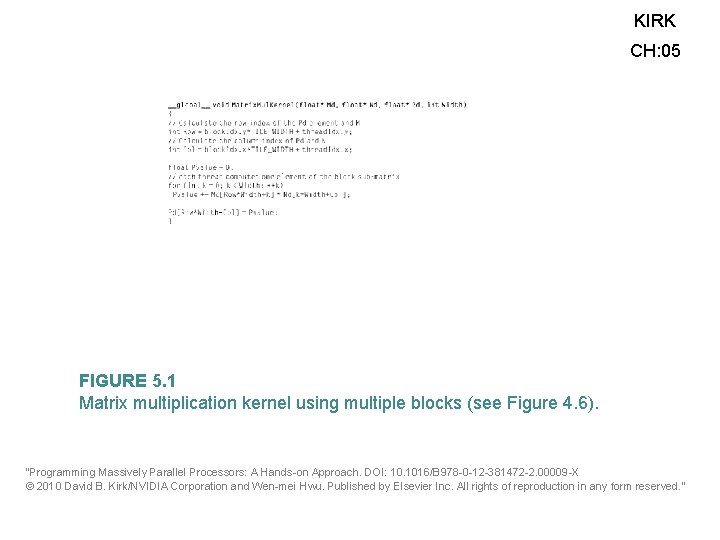

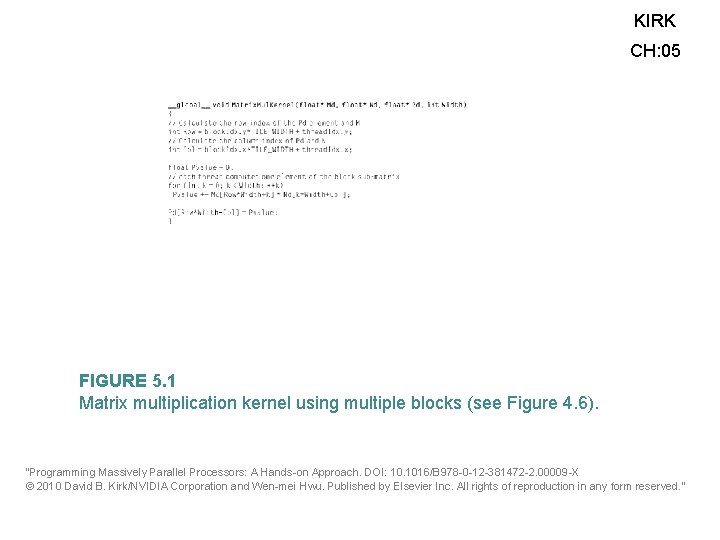

KIRK CH: 05 FIGURE 5. 1 Matrix multiplication kernel using multiple blocks (see Figure 4. 6). “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

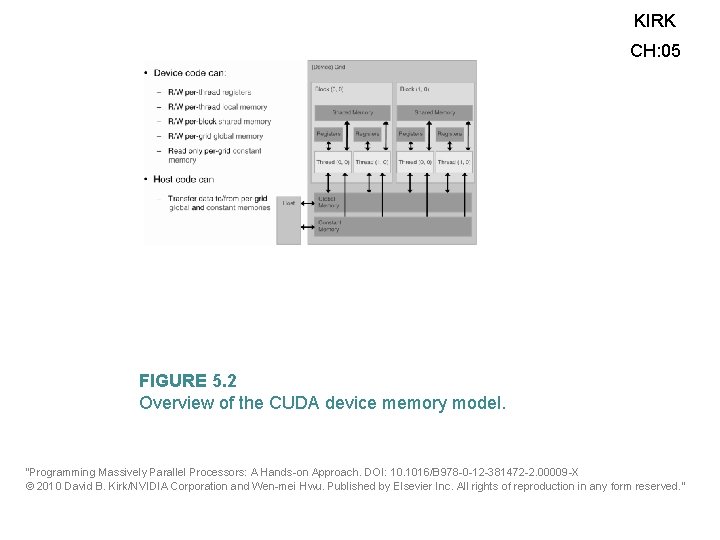

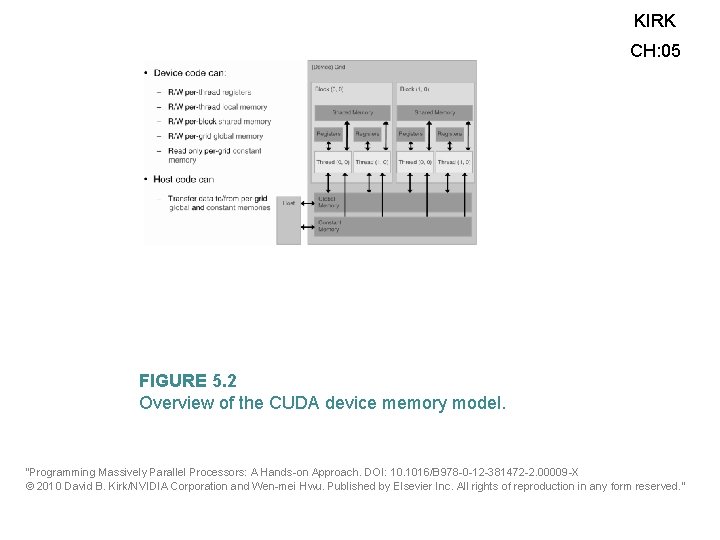

KIRK CH: 05 FIGURE 5. 2 Overview of the CUDA device memory model. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

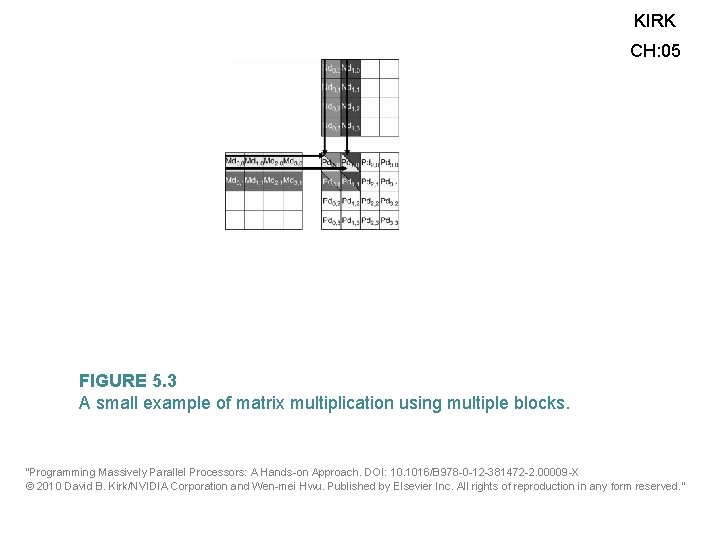

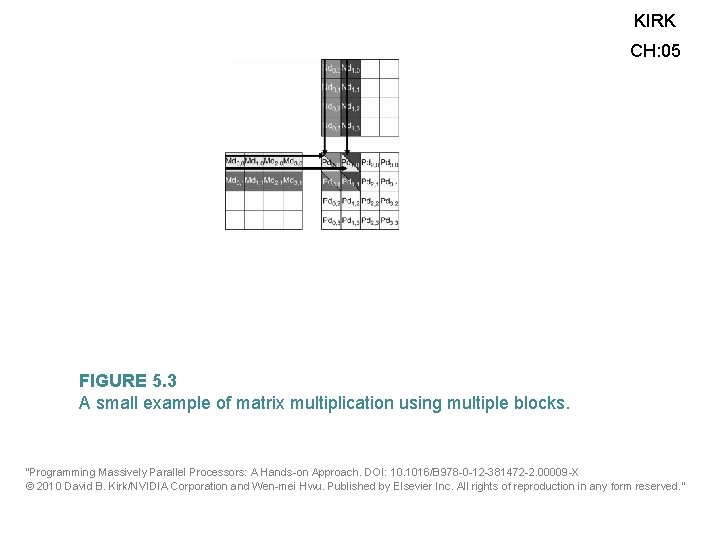

KIRK CH: 05 FIGURE 5. 3 A small example of matrix multiplication using multiple blocks. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

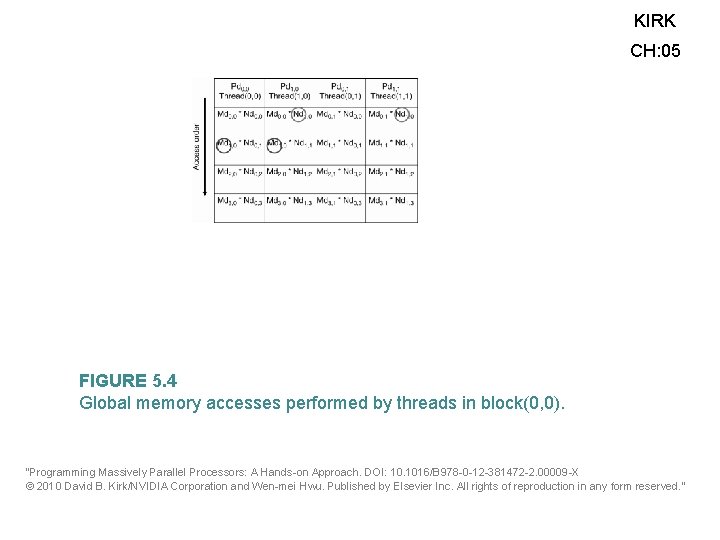

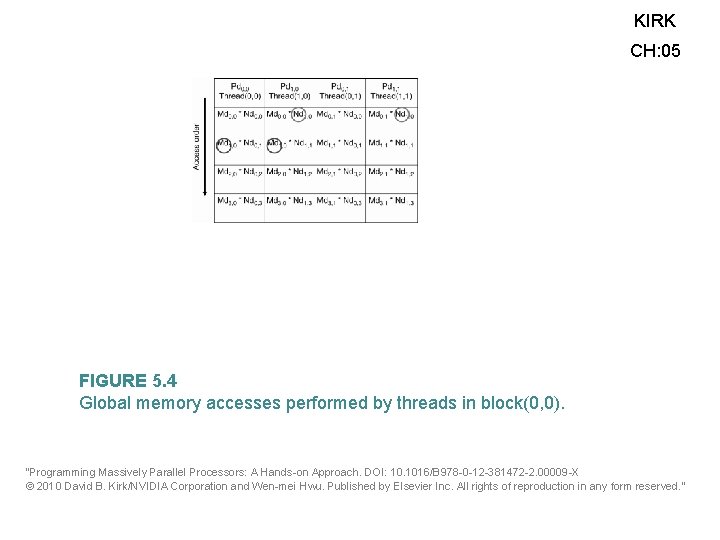

KIRK CH: 05 FIGURE 5. 4 Global memory accesses performed by threads in block(0, 0). “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

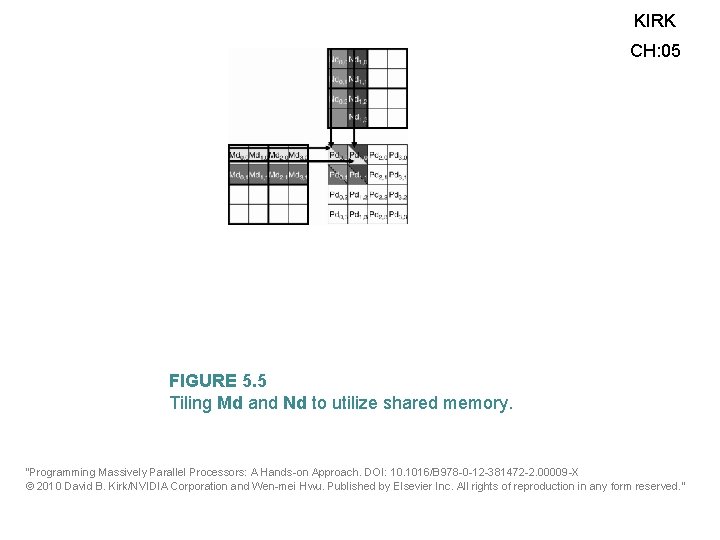

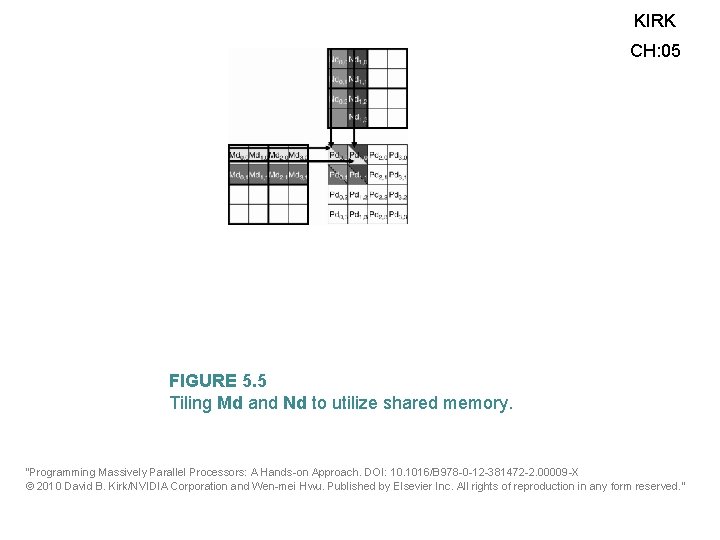

KIRK CH: 05 FIGURE 5. 5 Tiling Md and Nd to utilize shared memory. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

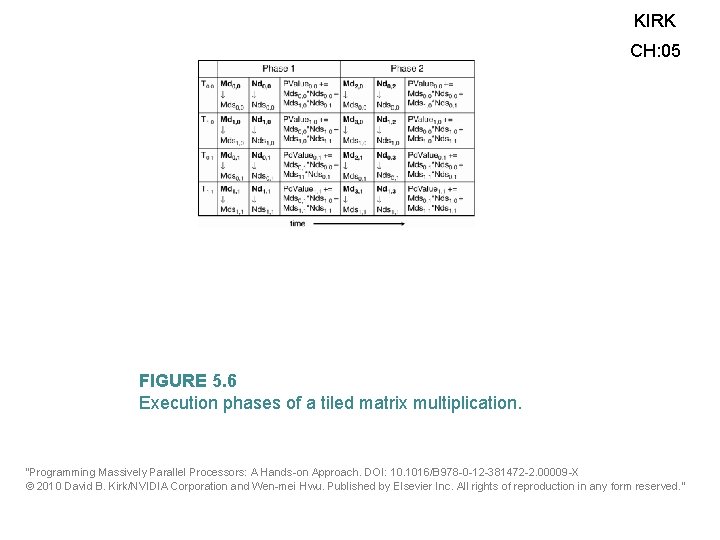

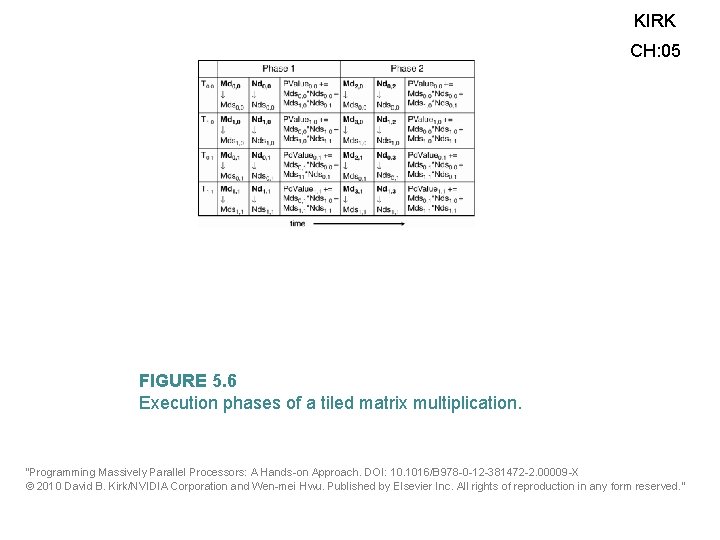

KIRK CH: 05 FIGURE 5. 6 Execution phases of a tiled matrix multiplication. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

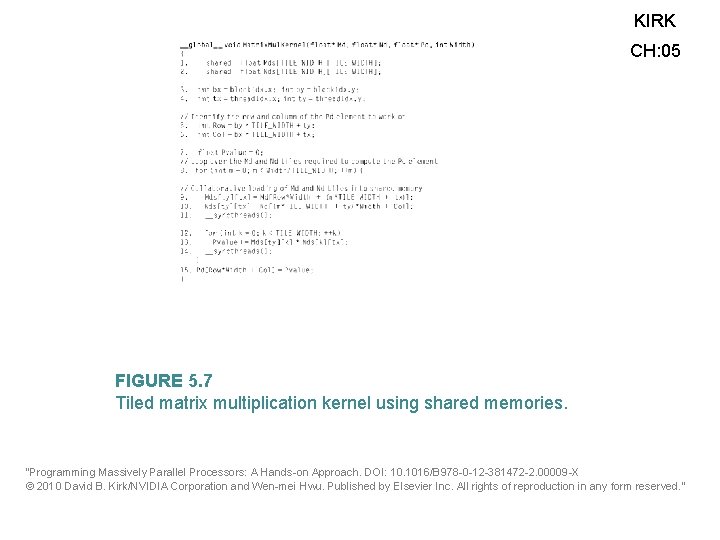

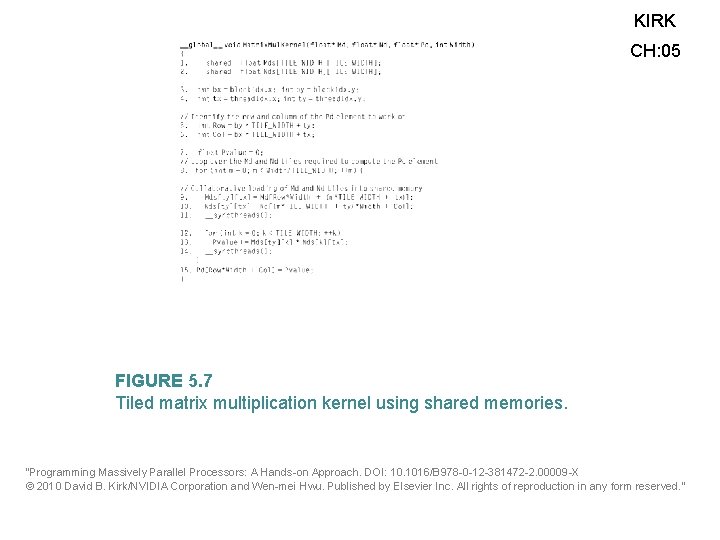

KIRK CH: 05 FIGURE 5. 7 Tiled matrix multiplication kernel using shared memories. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

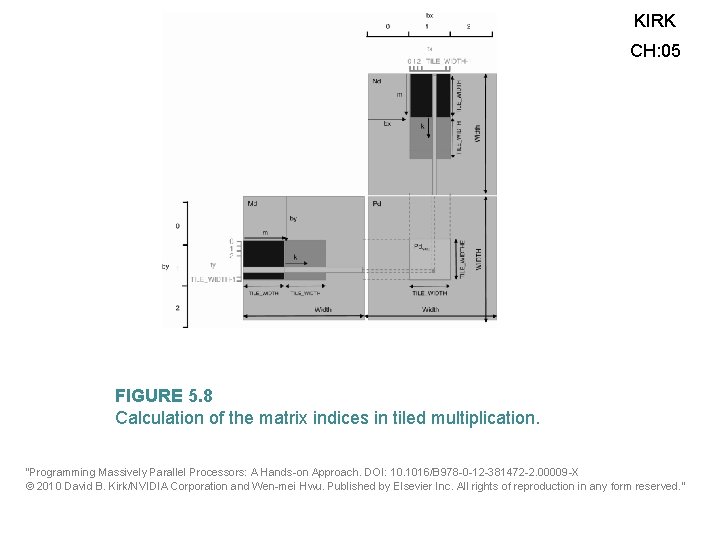

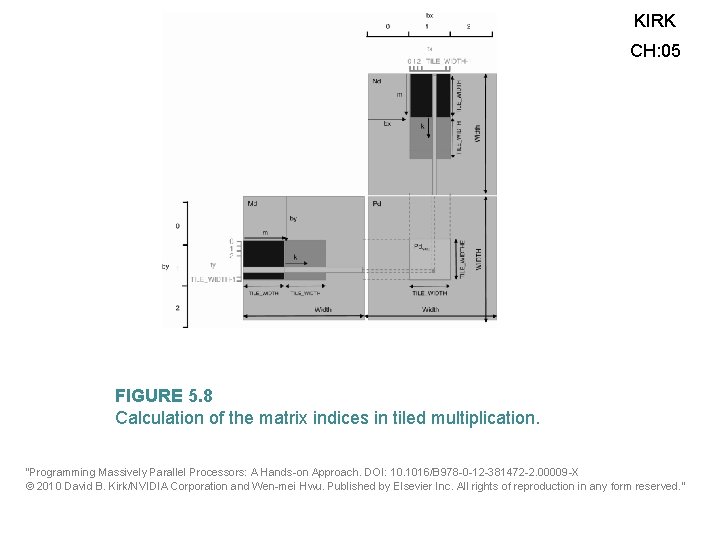

KIRK CH: 05 FIGURE 5. 8 Calculation of the matrix indices in tiled multiplication. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”