kili Karar Diyagramlar Yardmyla Lojik Devre Tasarm kili

- Slides: 20

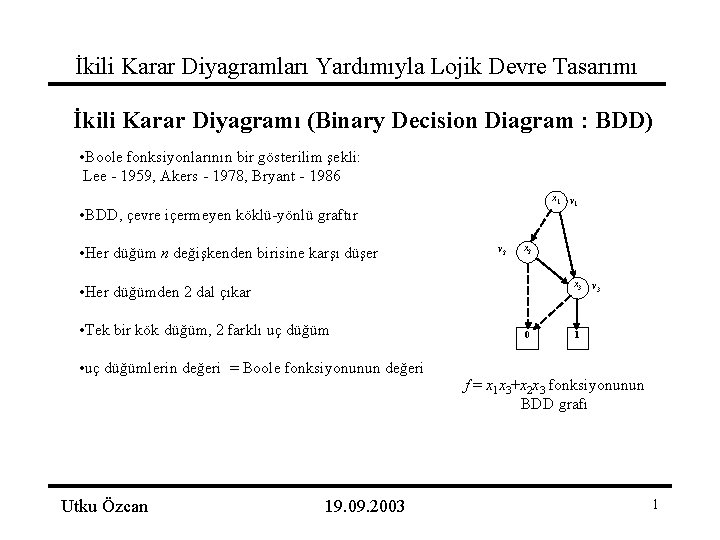

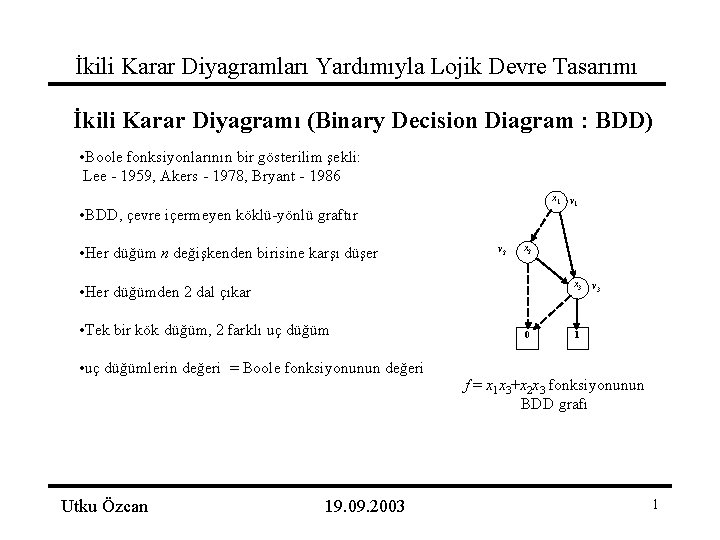

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı İkili Karar Diyagramı (Binary Decision Diagram : BDD) • Boole fonksiyonlarının bir gösterilim şekli: Lee - 1959, Akers - 1978, Bryant - 1986 x 1 v 1 • BDD, çevre içermeyen köklü-yönlü graftır • Her düğüm n değişkenden birisine karşı düşer v 2 x 3 • Her düğümden 2 dal çıkar • Tek bir kök düğüm, 2 farklı uç düğüm • uç düğümlerin değeri = Boole fonksiyonunun değeri Utku Özcan 19. 09. 2003 0 v 3 1 f = x 1 x 3+x 2 x 3 fonksiyonunun BDD grafı 1

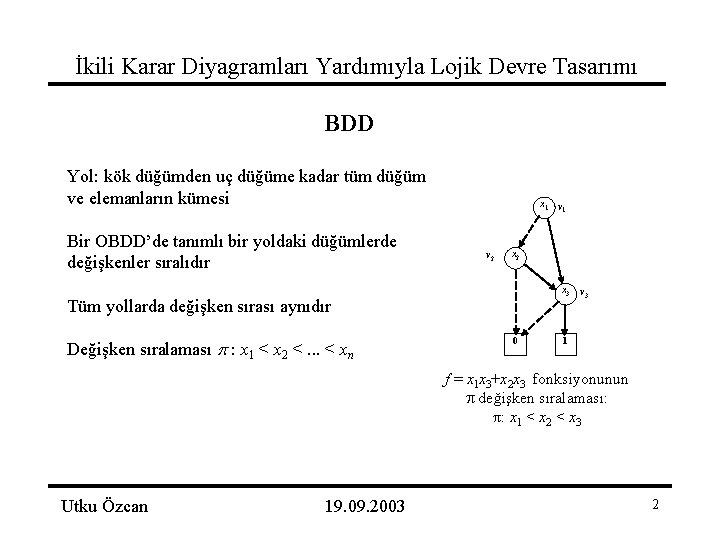

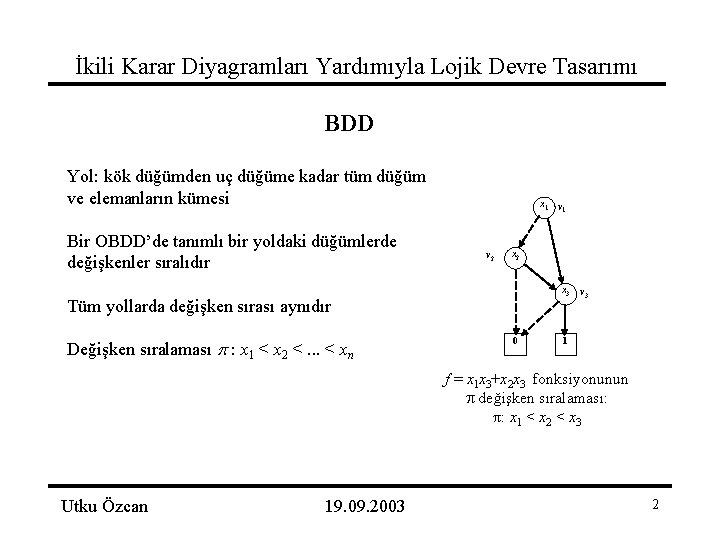

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı BDD Yol: kök düğümden uç düğüme kadar tüm düğüm ve elemanların kümesi Bir OBDD’de tanımlı bir yoldaki düğümlerde değişkenler sıralıdır x 1 v 2 x 3 Tüm yollarda değişken sırası aynıdır Değişken sıralaması : x 1 < x 2 <. . . < xn 0 v 3 1 f = x 1 x 3+x 2 x 3 fonksiyonunun değişken sıralaması: π: x 1 < x 2 < x 3 Utku Özcan 19. 09. 2003 2

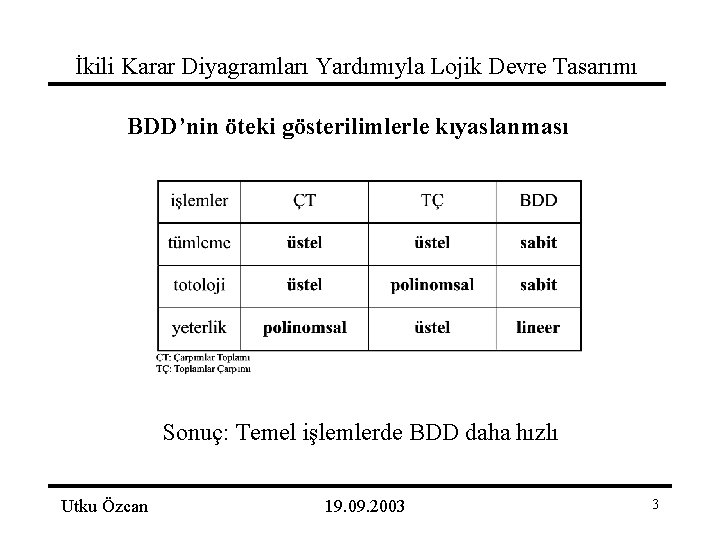

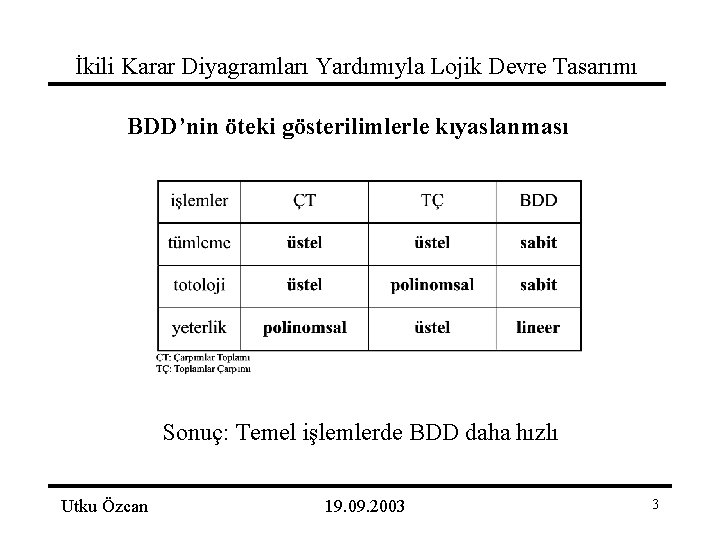

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı BDD’nin öteki gösterilimlerle kıyaslanması Sonuç: Temel işlemlerde BDD daha hızlı Utku Özcan 19. 09. 2003 3

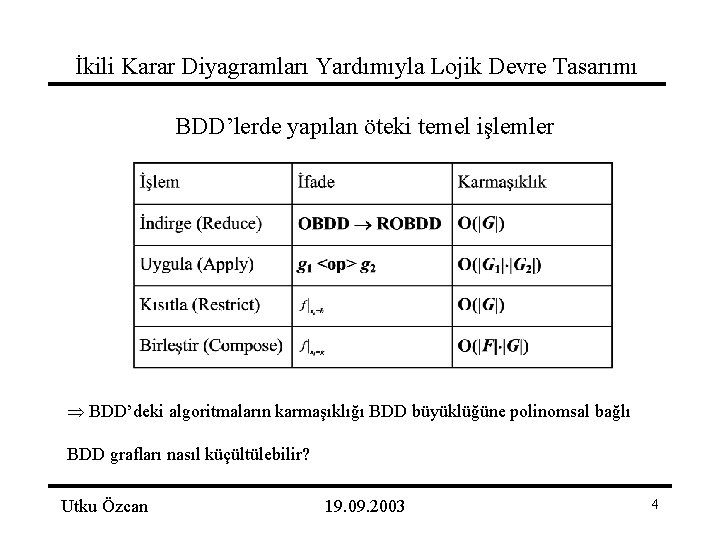

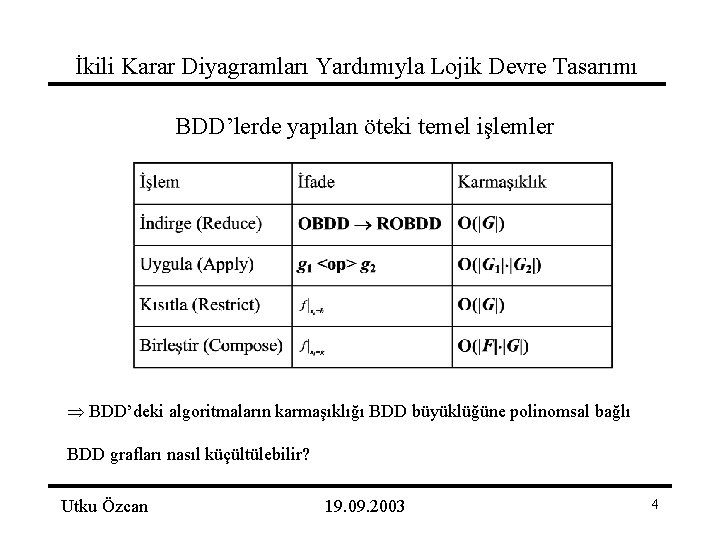

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı BDD’lerde yapılan öteki temel işlemler BDD’deki algoritmaların karmaşıklığı BDD büyüklüğüne polinomsal bağlı BDD grafları nasıl küçültülebilir? Utku Özcan 19. 09. 2003 4

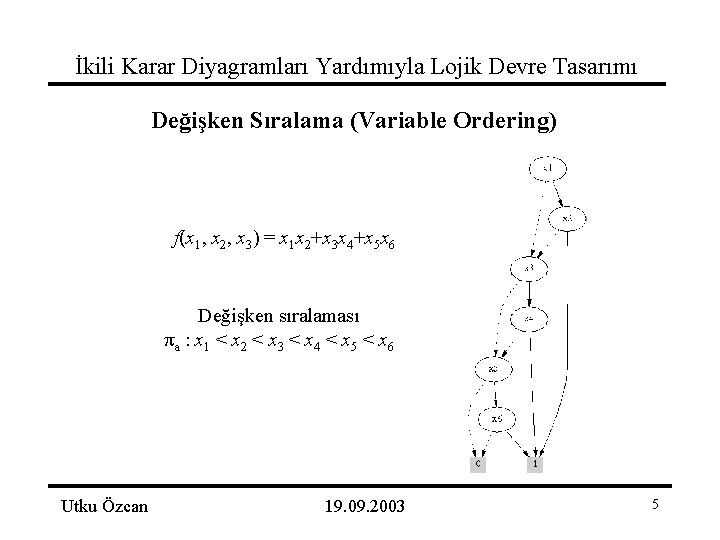

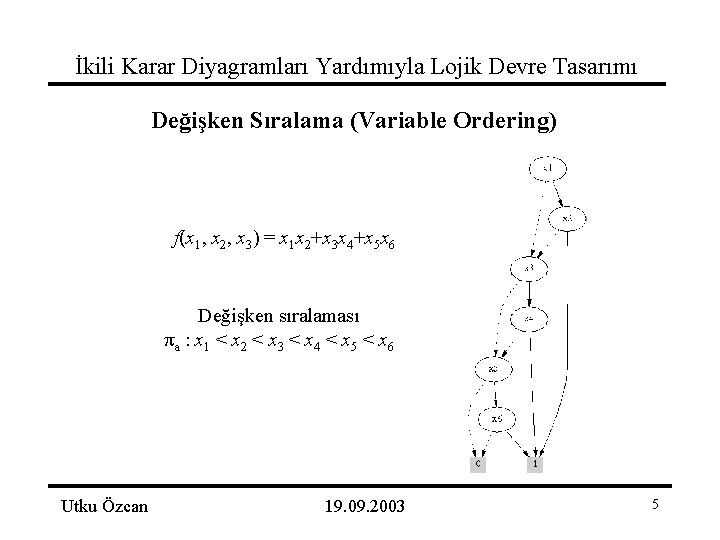

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Değişken Sıralama (Variable Ordering) f(x 1, x 2, x 3) = x 1 x 2+x 3 x 4+x 5 x 6 Değişken sıralaması πa : x 1 < x 2 < x 3 < x 4 < x 5 < x 6 Utku Özcan 19. 09. 2003 5

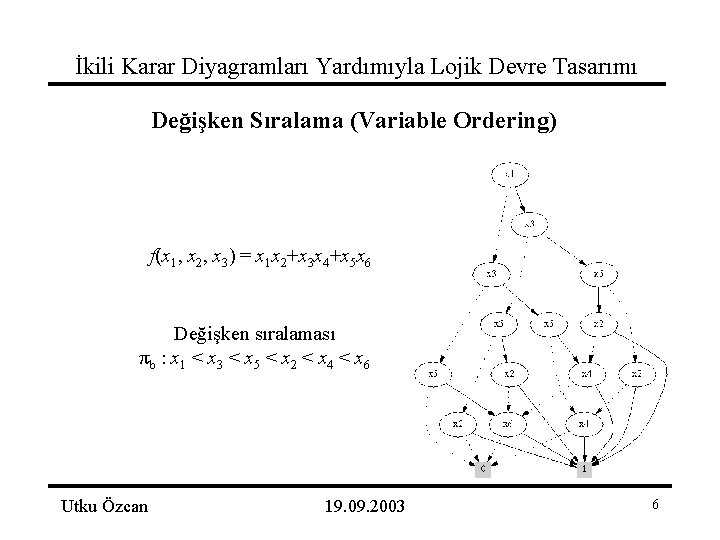

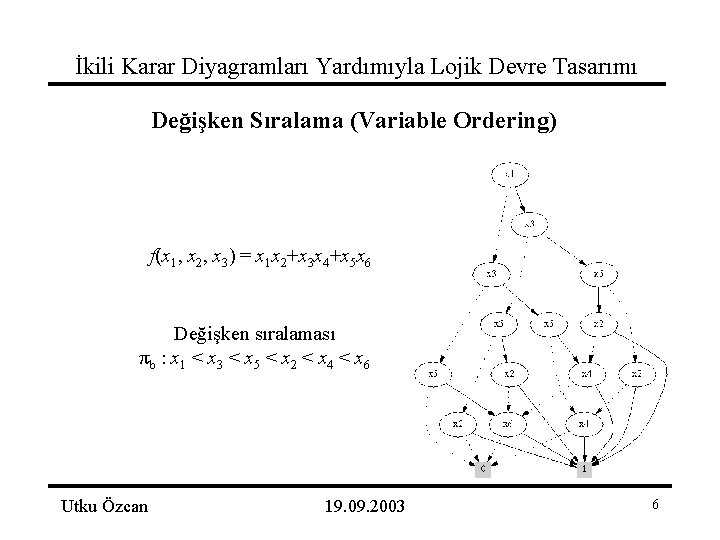

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Değişken Sıralama (Variable Ordering) f(x 1, x 2, x 3) = x 1 x 2+x 3 x 4+x 5 x 6 Değişken sıralaması πb : x 1 < x 3 < x 5 < x 2 < x 4 < x 6 Utku Özcan 19. 09. 2003 6

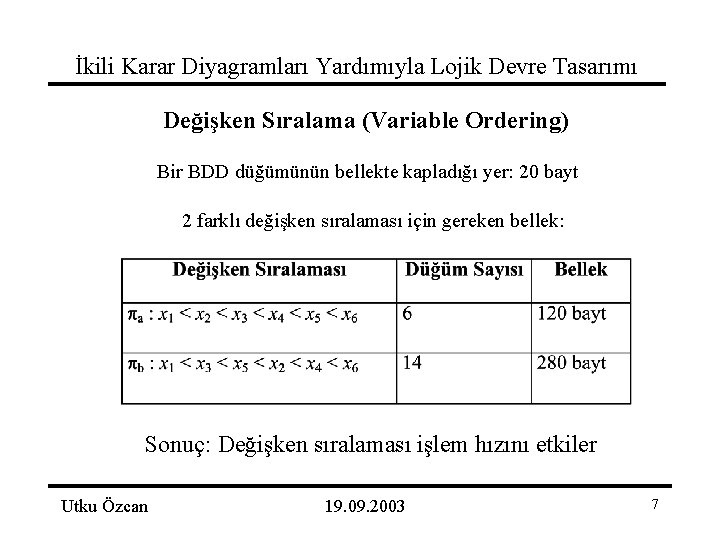

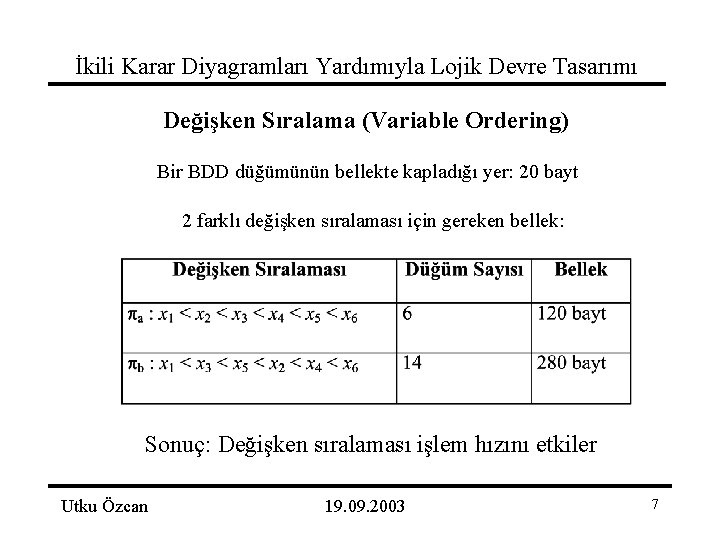

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Değişken Sıralama (Variable Ordering) Bir BDD düğümünün bellekte kapladığı yer: 20 bayt 2 farklı değişken sıralaması için gereken bellek: Sonuç: Değişken sıralaması işlem hızını etkiler Utku Özcan 19. 09. 2003 7

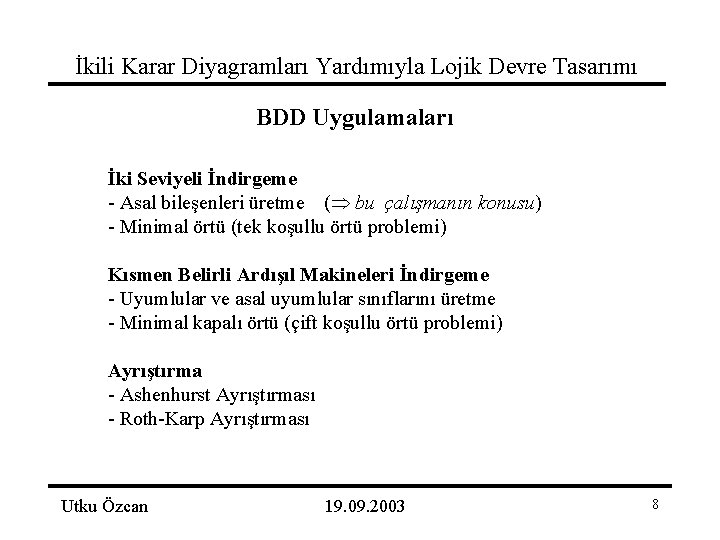

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı BDD Uygulamaları İki Seviyeli İndirgeme - Asal bileşenleri üretme ( bu çalışmanın konusu) - Minimal örtü (tek koşullu örtü problemi) Kısmen Belirli Ardışıl Makineleri İndirgeme - Uyumlular ve asal uyumlular sınıflarını üretme - Minimal kapalı örtü (çift koşullu örtü problemi) Ayrıştırma - Ashenhurst Ayrıştırması - Roth-Karp Ayrıştırması Utku Özcan 19. 09. 2003 8

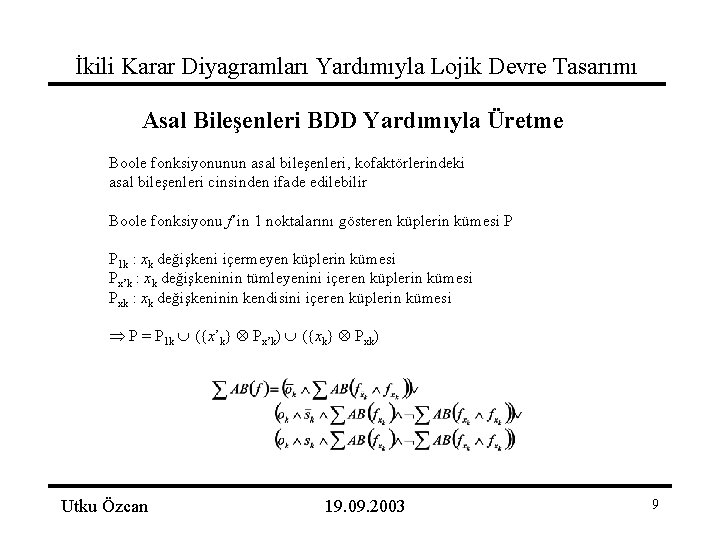

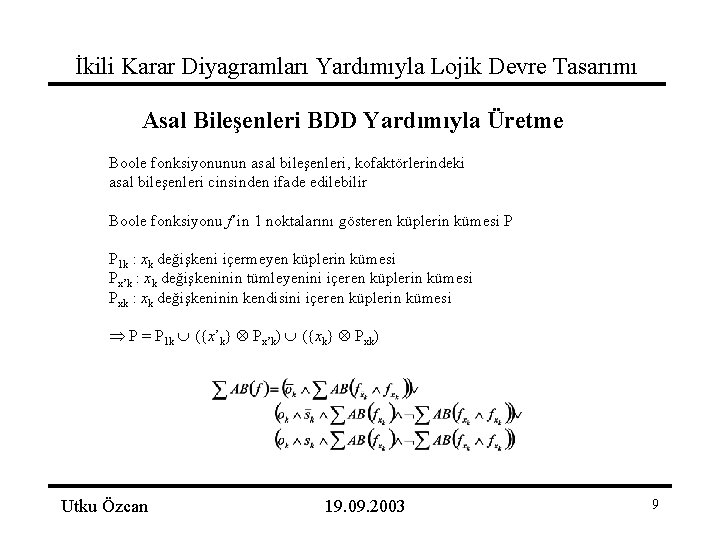

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Asal Bileşenleri BDD Yardımıyla Üretme Boole fonksiyonunun asal bileşenleri, kofaktörlerindeki asal bileşenleri cinsinden ifade edilebilir Boole fonksiyonu f’in 1 noktalarını gösteren küplerin kümesi P P 1 k : xk değişkeni içermeyen küplerin kümesi Px’k : xk değişkeninin tümleyenini içeren küplerin kümesi Pxk : xk değişkeninin kendisini içeren küplerin kümesi P = P 1 k ({x’k} Px’k) ({xk} Pxk) Utku Özcan 19. 09. 2003 9

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Asal Bileşenleri BDD Yardımıyla Üretme Boole fonksiyonunun asal bileşen kümesi AB 3 alt kümeyle ifade edilir: - xk değişkenini içermeyen asal bileşenlerin kümesi - xk değişkenini içeren asal bileşenlerini kümesi ok xk sk Herhangi bir BDD grafının kök düğümü Boole fonksiyonunu temsil eder Utku Özcan Herhangi bir AB BDD’sinin kök düğümü, Boole fonksiyonunun tüm AB’lerini gösterir 19. 09. 2003 10

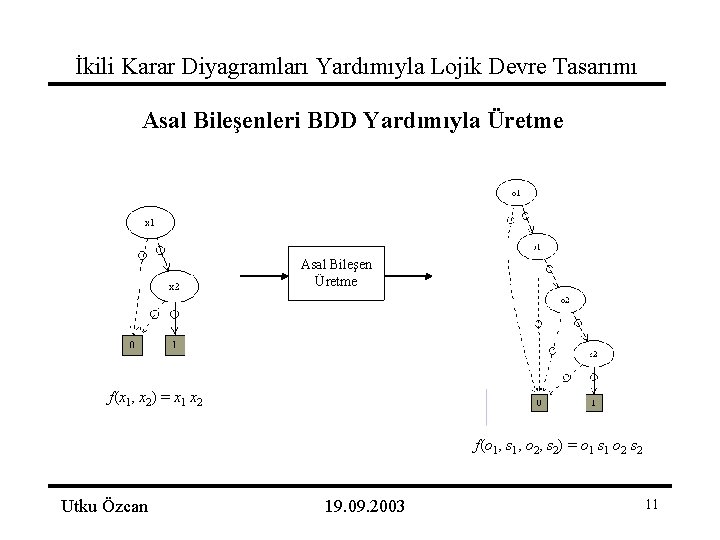

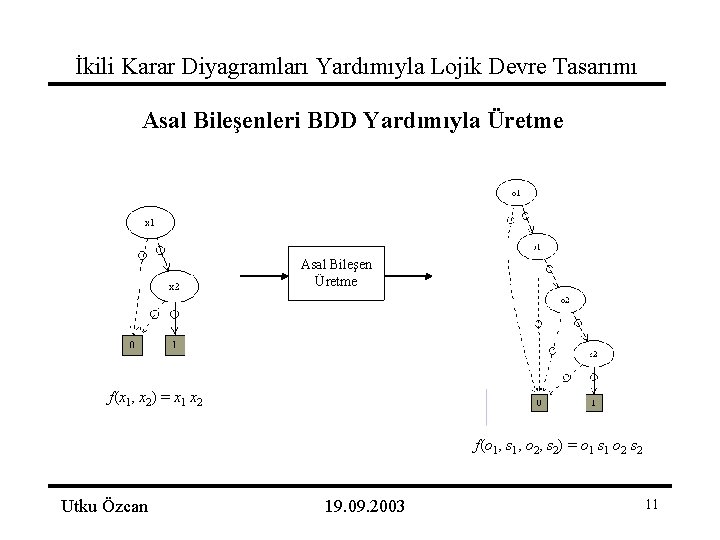

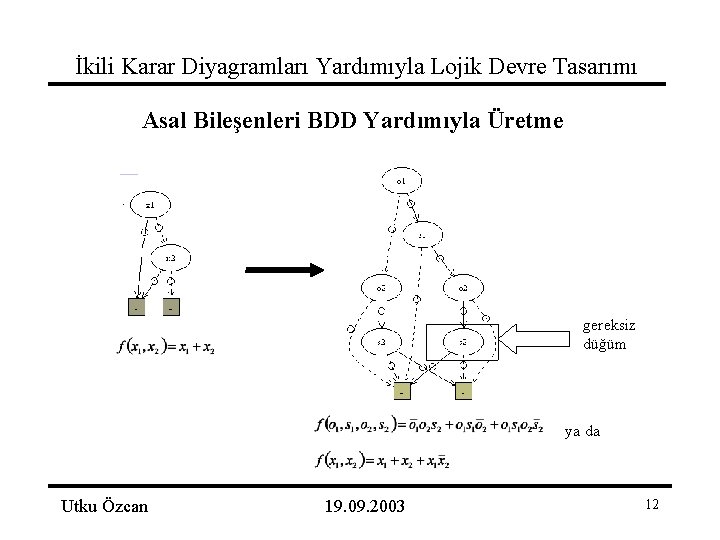

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Asal Bileşenleri BDD Yardımıyla Üretme Asal Bileşen Üretme f(x 1, x 2) = x 1 x 2 f(o 1, s 1, o 2, s 2) = o 1 s 1 o 2 s 2 Utku Özcan 19. 09. 2003 11

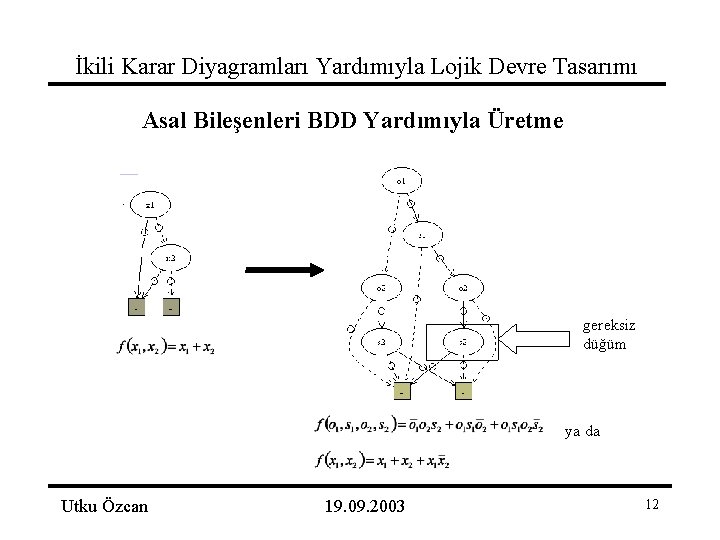

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Asal Bileşenleri BDD Yardımıyla Üretme gereksiz düğüm ya da Utku Özcan 19. 09. 2003 12

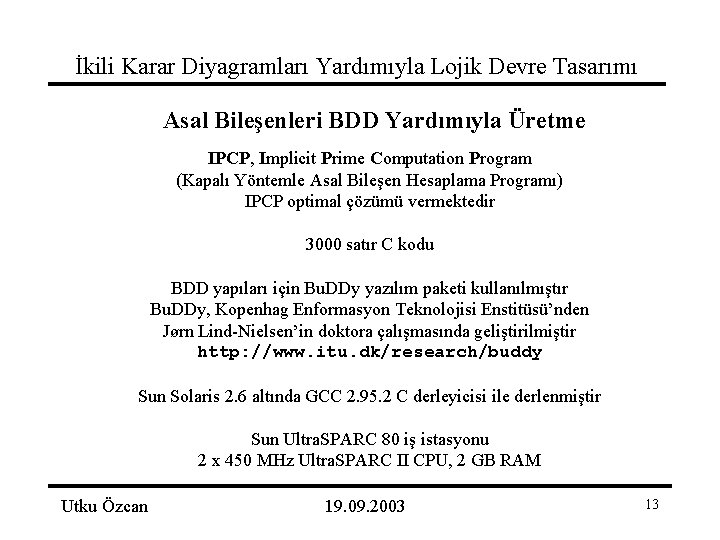

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Asal Bileşenleri BDD Yardımıyla Üretme IPCP, Implicit Prime Computation Program (Kapalı Yöntemle Asal Bileşen Hesaplama Programı) IPCP optimal çözümü vermektedir 3000 satır C kodu BDD yapıları için Bu. DDy yazılım paketi kullanılmıştır Bu. DDy, Kopenhag Enformasyon Teknolojisi Enstitüsü’nden Jørn Lind-Nielsen’in doktora çalışmasında geliştirilmiştir http: //www. itu. dk/research/buddy Sun Solaris 2. 6 altında GCC 2. 95. 2 C derleyicisi ile derlenmiştir Sun Ultra. SPARC 80 iş istasyonu 2 x 450 MHz Ultra. SPARC II CPU, 2 GB RAM Utku Özcan 19. 09. 2003 13

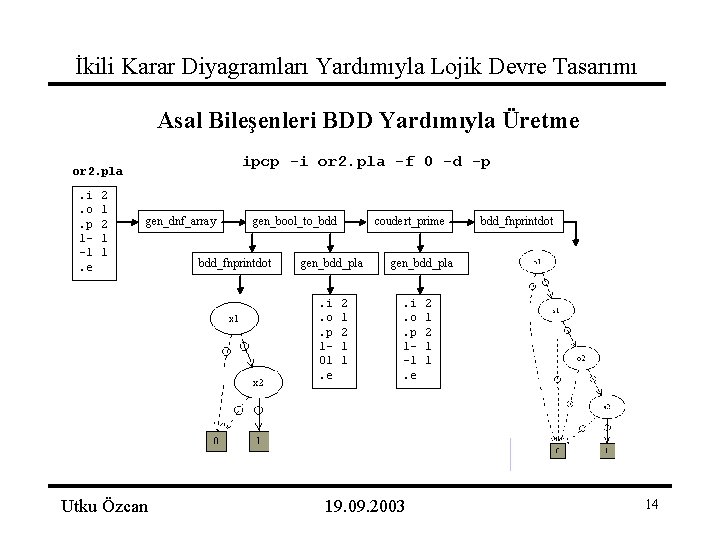

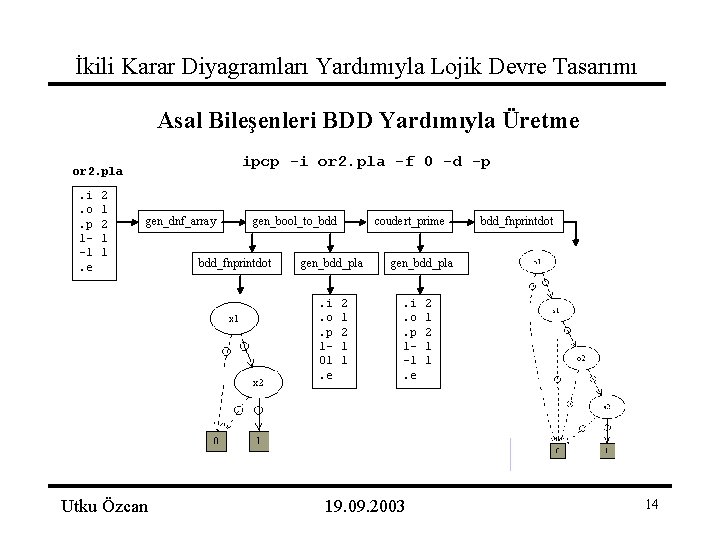

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Asal Bileşenleri BDD Yardımıyla Üretme ipcp -i or 2. pla -f 0 -d -p or 2. pla. i. o. p 1 -1. e 2 1 1 gen_dnf_array gen_bool_to_bdd bdd_fnprintdot gen_bdd_pla. i. o. p 101. e Utku Özcan coudert_prime 2 1 1 bdd_fnprintdot gen_bdd_pla. i. o. p 1 -1. e 19. 09. 2003 2 1 1 14

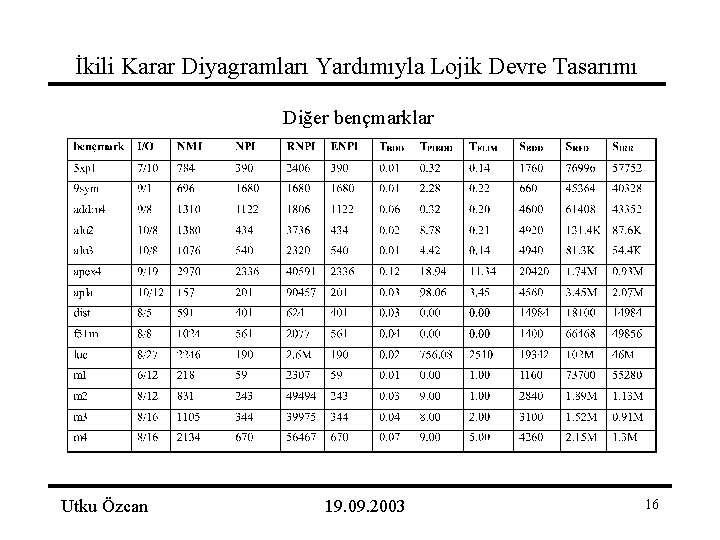

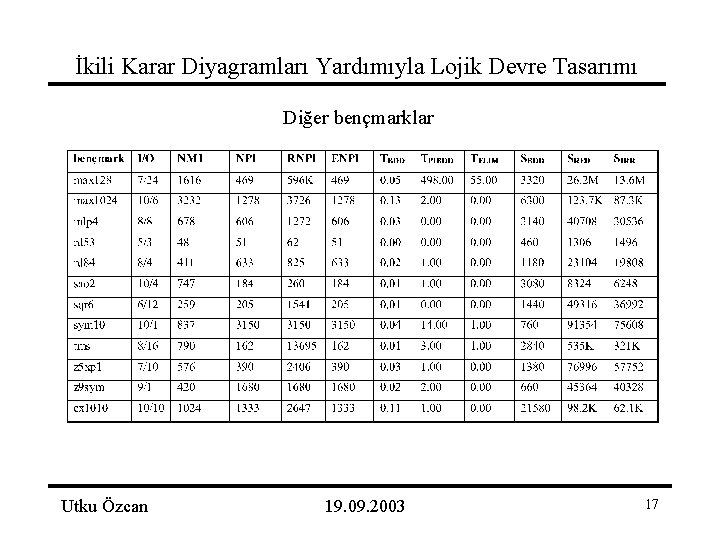

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı IPCP’nin Değişik Bençmarklarla Testi Zor bençmarklar I/O: I: Giriş değişken sayısı, O: çıkış fonksiyon sayısı NMI: Minterm sayısı NPI: Eerçekteki asal bileşen sayısı RNPI: BDD yardımıyla hesaplanan asal bileşen sayısı ENPI: Eleme sonucunda elde edilen asal bileşen sayısı TBDD: BDD graflarını oluşturma süresi [saniye] TPIBDD: Asal bileşenleri gösteren BDD graflarını oluşturma ve tüm asal bileşenleri elde süresi [saniye] TELIM: gereksiz asal bileşenleri eleme süresi [saniye] SBDD: BDD grafının bellekte kapladığı alan [bayt, megabayt] SRED: elenmemiş asal bileşenlerin karakter formatında bellekte kapladığı alan [bayt, megabayt] SIRR: elenmemiş asal bileşenlerin bit formatında bellekte kapladığı alan [bayt, megabayt] Utku Özcan 19. 09. 2003 15

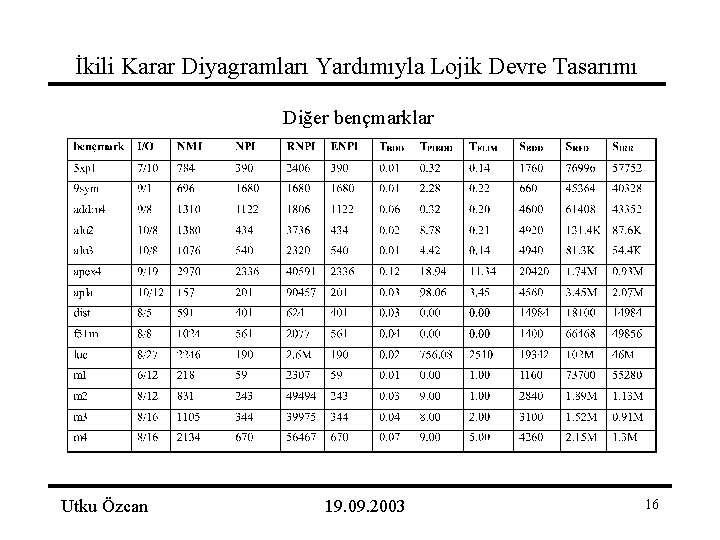

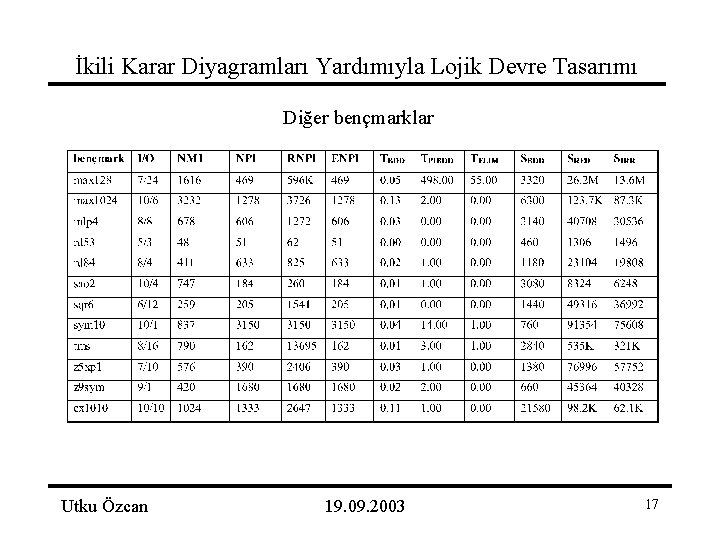

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Diğer bençmarklar Utku Özcan 19. 09. 2003 16

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı Diğer bençmarklar Utku Özcan 19. 09. 2003 17

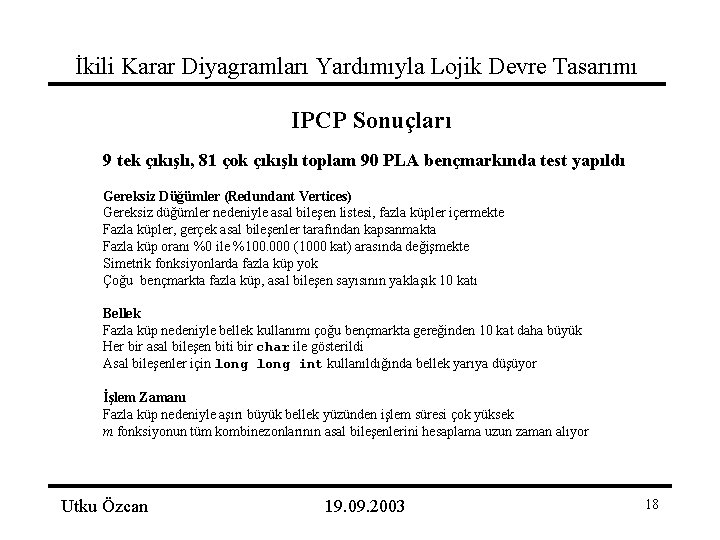

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı IPCP Sonuçları 9 tek çıkışlı, 81 çok çıkışlı toplam 90 PLA bençmarkında test yapıldı Gereksiz Düğümler (Redundant Vertices) Gereksiz düğümler nedeniyle asal bileşen listesi, fazla küpler içermekte Fazla küpler, gerçek asal bileşenler tarafından kapsanmakta Fazla küp oranı %0 ile %100. 000 (1000 kat) arasında değişmekte Simetrik fonksiyonlarda fazla küp yok Çoğu bençmarkta fazla küp, asal bileşen sayısının yaklaşık 10 katı Bellek Fazla küp nedeniyle bellek kullanımı çoğu bençmarkta gereğinden 10 kat daha büyük Her bir asal bileşen biti bir char ile gösterildi Asal bileşenler için long int kullanıldığında bellek yarıya düşüyor İşlem Zamanı Fazla küp nedeniyle aşırı büyük bellek yüzünden işlem süresi çok yüksek m fonksiyonun tüm kombinezonlarının asal bileşenlerini hesaplama uzun zaman alıyor Utku Özcan 19. 09. 2003 18

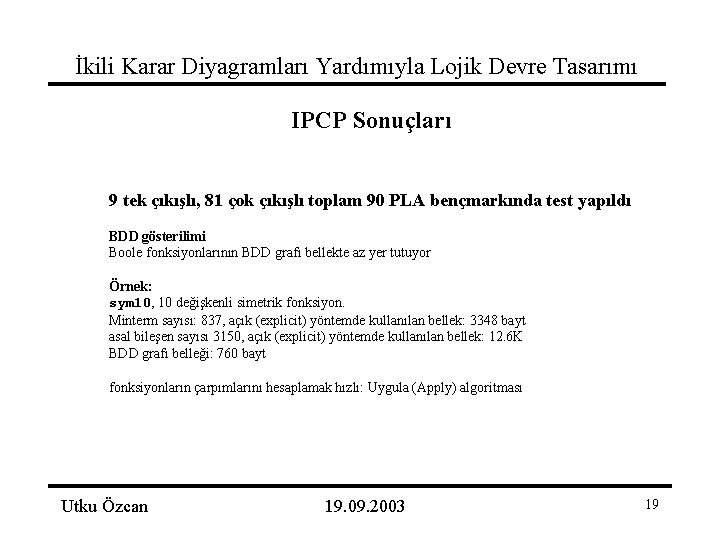

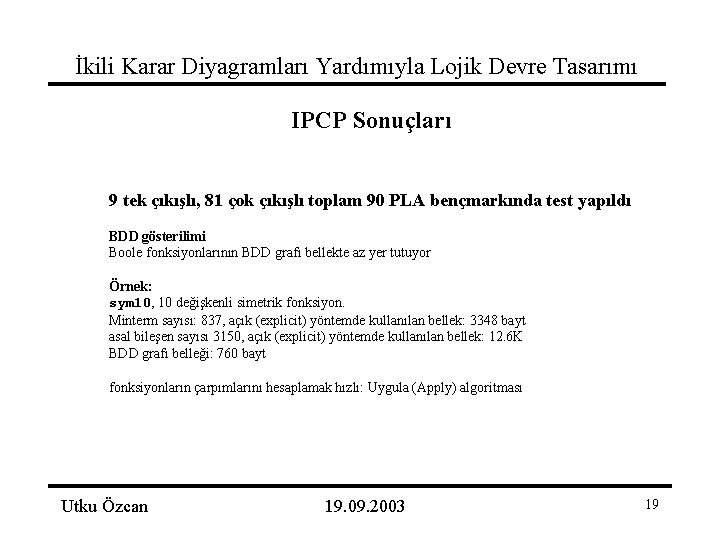

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı IPCP Sonuçları 9 tek çıkışlı, 81 çok çıkışlı toplam 90 PLA bençmarkında test yapıldı BDD gösterilimi Boole fonksiyonlarının BDD grafı bellekte az yer tutuyor Örnek: sym 10, 10 değişkenli simetrik fonksiyon. Minterm sayısı: 837, açık (explicit) yöntemde kullanılan bellek: 3348 bayt asal bileşen sayısı 3150, açık (explicit) yöntemde kullanılan bellek: 12. 6 K BDD grafı belleği: 760 bayt fonksiyonların çarpımlarını hesaplamak hızlı: Uygula (Apply) algoritması Utku Özcan 19. 09. 2003 19

İkili Karar Diyagramları Yardımıyla Lojik Devre Tasarımı SONUÇ BDD’lerle ilgili Türkçe bir çalışmaya rastlanmamıştır Literatürde herhangi bir BDD paketi için PLA arayüzüne rastlanmamıştır BDD’lerle ilgili Türkçe bir uygulamaya rastlanmamıştır Literatürde Bu. DDy paketinde asal bileşen bulma uygulamasına rastlanmamıştır BDD’lerle Ardışıl Makinelerin İndirgenmesi uygulaması yapılabilir BDD’lerle Roth-Karp Ayrıştırması uygulaması yapılabilir Utku Özcan 19. 09. 2003 20