Keyboard Controller Design By Tamas Kasza Presentation for

Keyboard Controller Design By Tamas Kasza Presentation for Digital System Design 2 (ECE 5572) Summer 2003 1

Content n n n Overview of design goals Available devices and software background PS 2 Interface: n n n LCD Interface: n n PS 2 interface controller keyboard codes on Seven Segment Display Structure Program modules, communicating state machines Operation of the code itself - presentation Summary 2

Design Goals: n n n Attach a keyboard to the DIO 2 device through PS/2 type of port; Design a logic which can detect and display a pushed character on the LCD display of the I/O device; Use VHDL during the development process. 3

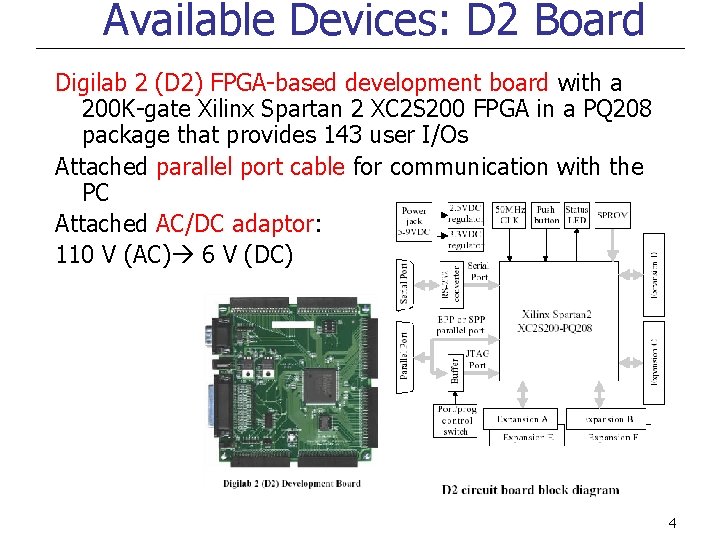

Available Devices: D 2 Board Digilab 2 (D 2) FPGA-based development board with a 200 K-gate Xilinx Spartan 2 XC 2 S 200 FPGA in a PQ 208 package that provides 143 user I/Os Attached parallel port cable for communication with the PC Attached AC/DC adaptor: 110 V (AC) 6 V (DC) 4

Available Devices: DIO 2 Digilab Digital I/O board 2 n 16 x 2 character LCD n Four seven segment displays n 16 LEDs in three colors n 8 switches n 15 pushbutton keypad n 8 -bit VGA port n PS/2 port 5

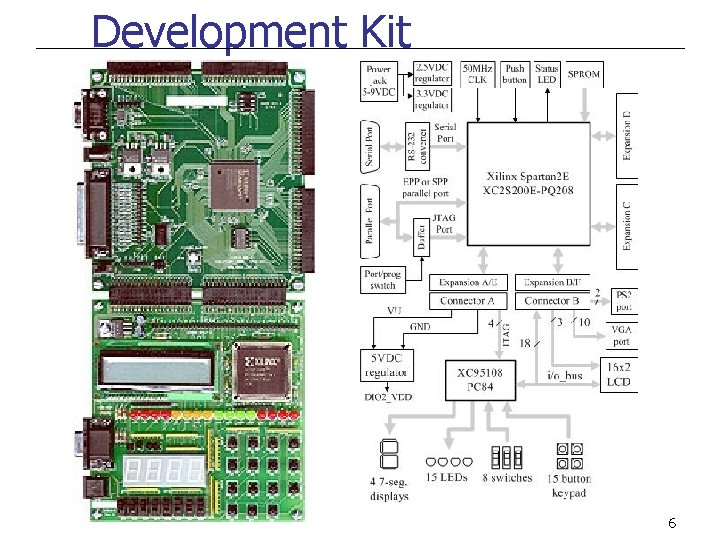

Development Kit 6

Available Devices: Keyboard with PS/2 port 7

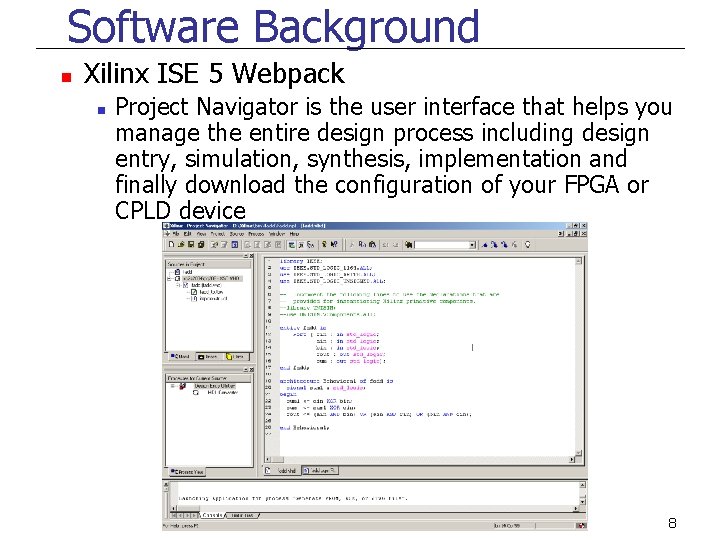

Software Background n Xilinx ISE 5 Webpack n Project Navigator is the user interface that helps you manage the entire design process including design entry, simulation, synthesis, implementation and finally download the configuration of your FPGA or CPLD device 8

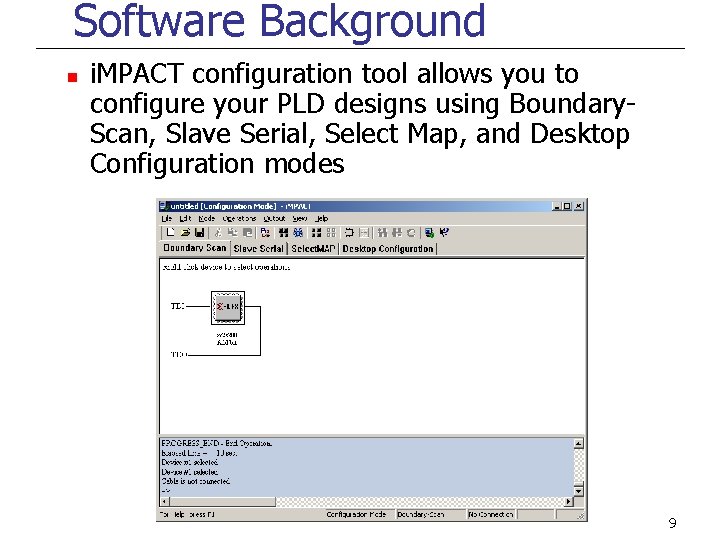

Software Background n i. MPACT configuration tool allows you to configure your PLD designs using Boundary. Scan, Slave Serial, Select Map, and Desktop Configuration modes 9

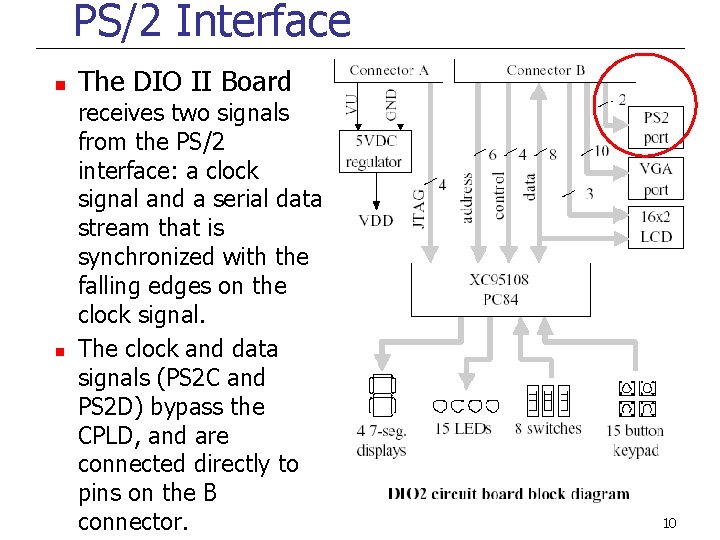

PS/2 Interface n n The DIO II Board receives two signals from the PS/2 interface: a clock signal and a serial data stream that is synchronized with the falling edges on the clock signal. The clock and data signals (PS 2 C and PS 2 D) bypass the CPLD, and are connected directly to pins on the B connector. 10

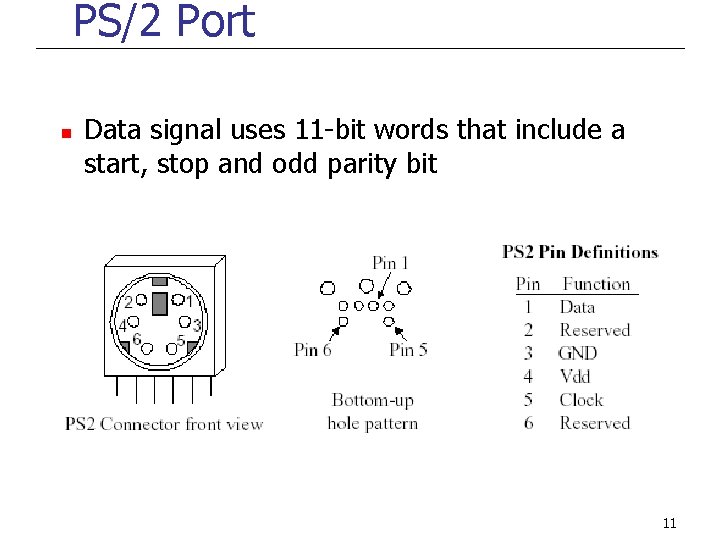

PS/2 Port n Data signal uses 11 -bit words that include a start, stop and odd parity bit 11

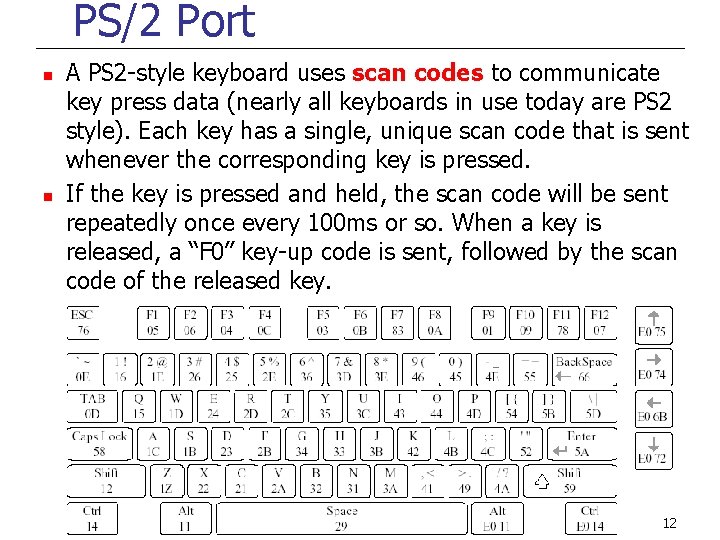

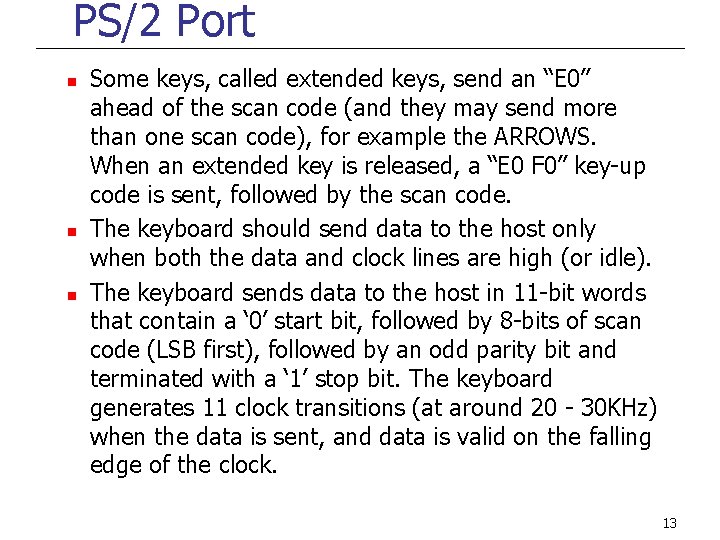

PS/2 Port n n A PS 2 -style keyboard uses scan codes to communicate key press data (nearly all keyboards in use today are PS 2 style). Each key has a single, unique scan code that is sent whenever the corresponding key is pressed. If the key is pressed and held, the scan code will be sent repeatedly once every 100 ms or so. When a key is released, a “F 0” key-up code is sent, followed by the scan code of the released key. 12

PS/2 Port n n n Some keys, called extended keys, send an “E 0” ahead of the scan code (and they may send more than one scan code), for example the ARROWS. When an extended key is released, a “E 0 F 0” key-up code is sent, followed by the scan code. The keyboard should send data to the host only when both the data and clock lines are high (or idle). The keyboard sends data to the host in 11 -bit words that contain a ‘ 0’ start bit, followed by 8 -bits of scan code (LSB first), followed by an odd parity bit and terminated with a ‘ 1’ stop bit. The keyboard generates 11 clock transitions (at around 20 - 30 KHz) when the data is sent, and data is valid on the falling edge of the clock. 13

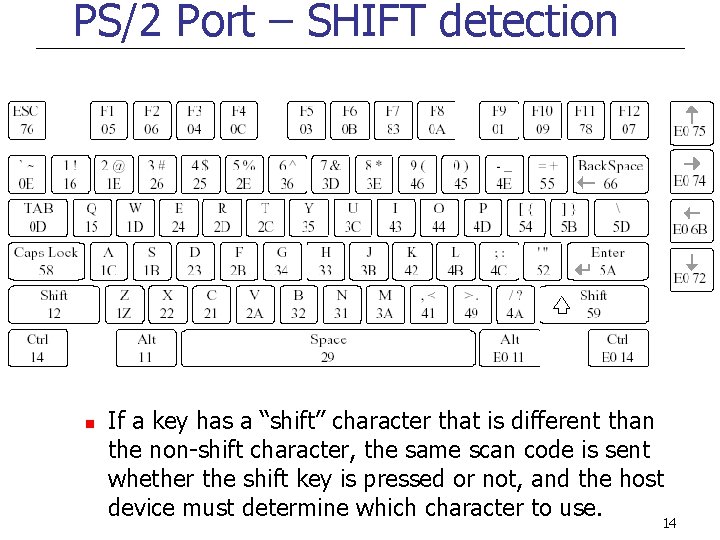

PS/2 Port – SHIFT detection n If a key has a “shift” character that is different than the non-shift character, the same scan code is sent whether the shift key is pressed or not, and the host device must determine which character to use. 14

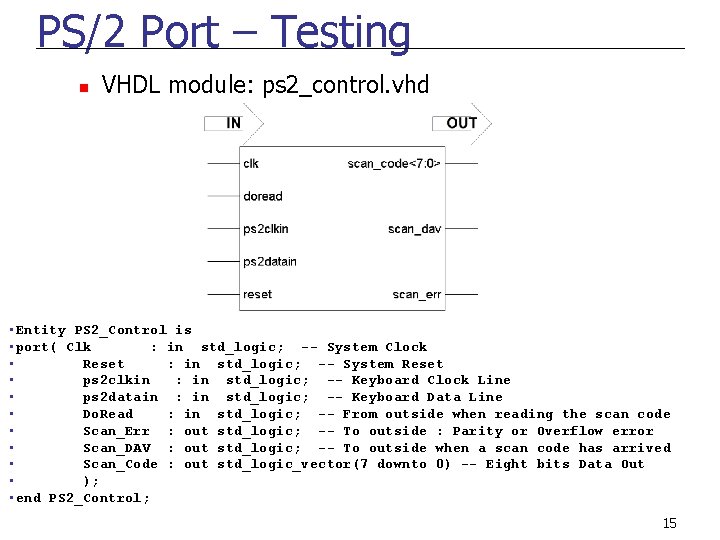

PS/2 Port – Testing n VHDL module: ps 2_control. vhd • Entity PS 2_Control is • port( Clk : in std_logic; -- System Clock • Reset : in std_logic; -- System Reset • ps 2 clkin : in std_logic; -- Keyboard Clock Line • ps 2 datain : in std_logic; -- Keyboard Data Line • Do. Read : in std_logic; -- From outside when reading the scan code • Scan_Err : out std_logic; -- To outside : Parity or Overflow error • Scan_DAV : out std_logic; -- To outside when a scan code has arrived • Scan_Code : out std_logic_vector(7 downto 0) -- Eight bits Data Out • ); • end PS 2_Control; 15

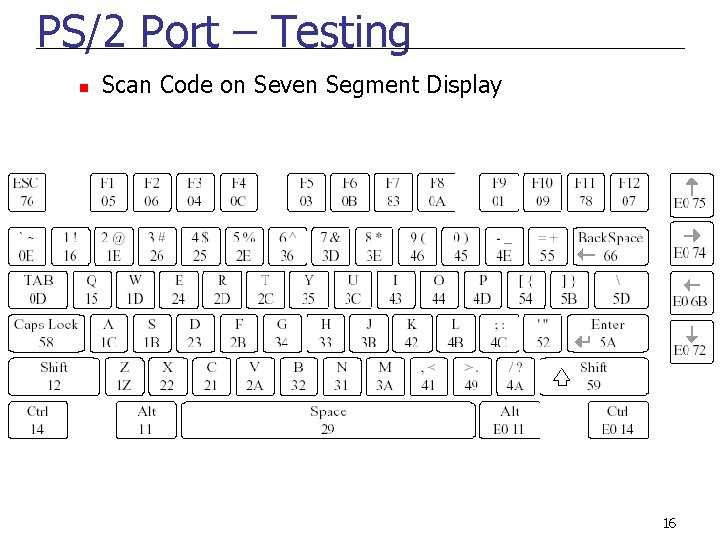

PS/2 Port – Testing n Scan Code on Seven Segment Display 16

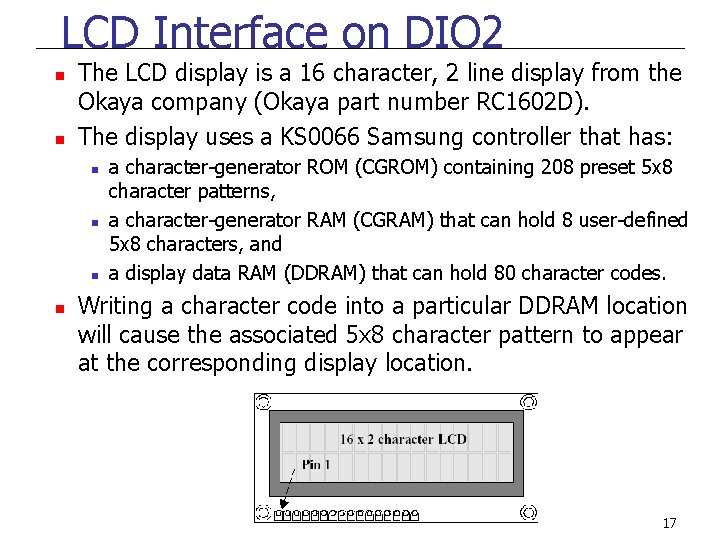

LCD Interface on DIO 2 n n The LCD display is a 16 character, 2 line display from the Okaya company (Okaya part number RC 1602 D). The display uses a KS 0066 Samsung controller that has: n n a character-generator ROM (CGROM) containing 208 preset 5 x 8 character patterns, a character-generator RAM (CGRAM) that can hold 8 user-defined 5 x 8 characters, and a display data RAM (DDRAM) that can hold 80 character codes. Writing a character code into a particular DDRAM location will cause the associated 5 x 8 character pattern to appear at the corresponding display location. 17

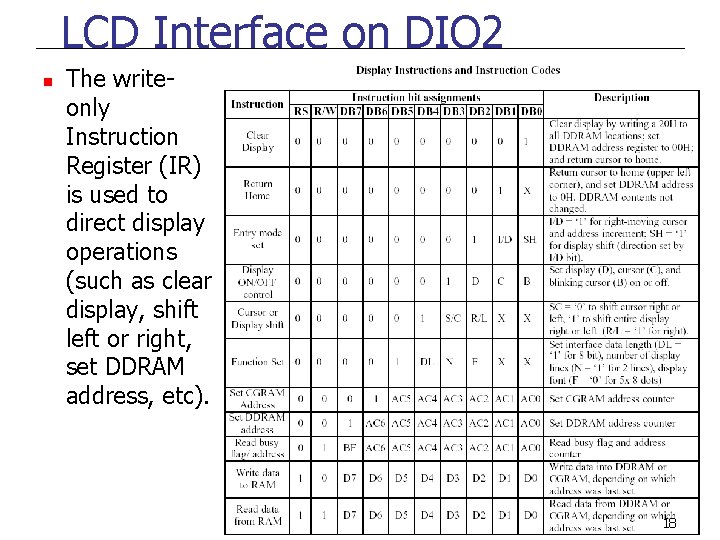

LCD Interface on DIO 2 n The writeonly Instruction Register (IR) is used to direct display operations (such as clear display, shift left or right, set DDRAM address, etc). 18

LCD Interface on DIO 2 n n A busy flag is available to indicate whether the display has competed the last requested operation; prior to initiating a new operation, the flag can be checked to see whether the previous operation has been completed. The LCD display uses ASCII character codes: n n Codes up through 7 F are standard ASCII (which includes all “normal” alphanumeric characters). Codes above 7 F produce various international characters. 19

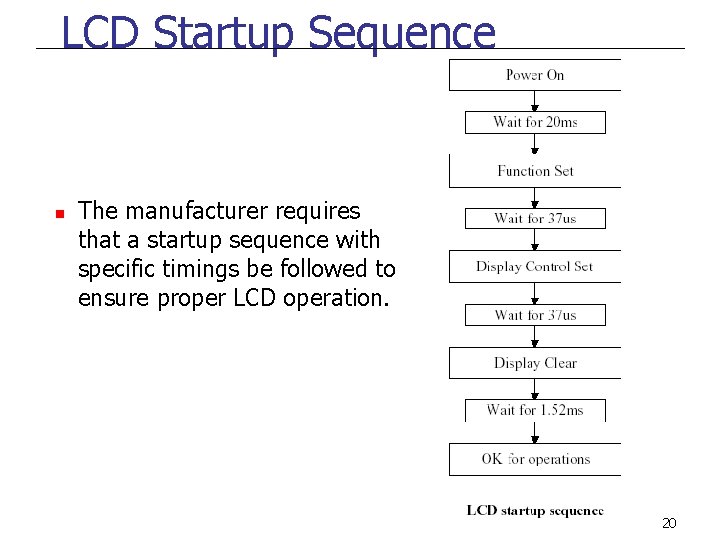

LCD Startup Sequence n The manufacturer requires that a startup sequence with specific timings be followed to ensure proper LCD operation. 20

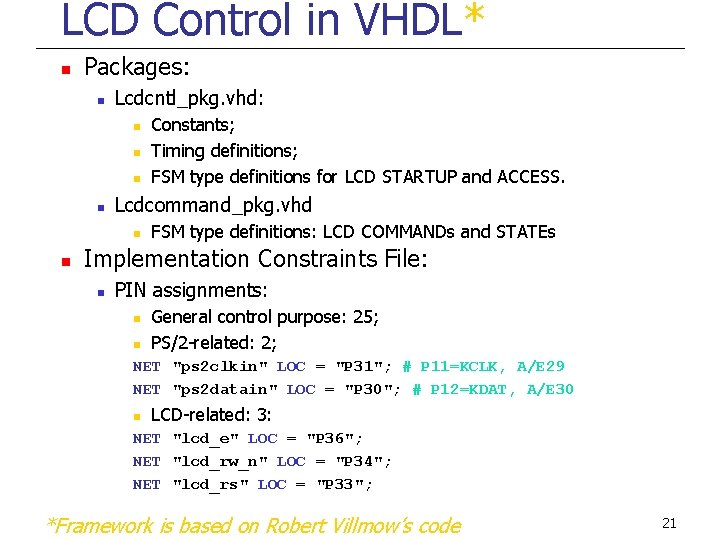

LCD Control in VHDL* n Packages: n Lcdcntl_pkg. vhd: n n Lcdcommand_pkg. vhd n n Constants; Timing definitions; FSM type definitions for LCD STARTUP and ACCESS. FSM type definitions: LCD COMMANDs and STATEs Implementation Constraints File: n PIN assignments: n n General control purpose: 25; PS/2 -related: 2; NET "ps 2 clkin" LOC = "P 31"; # P 11=KCLK, A/E 29 NET "ps 2 datain" LOC = "P 30"; # P 12=KDAT, A/E 30 n LCD-related: 3: NET "lcd_e" LOC = "P 36"; NET "lcd_rw_n" LOC = "P 34"; NET "lcd_rs" LOC = "P 33"; *Framework is based on Robert Villmow’s code 21

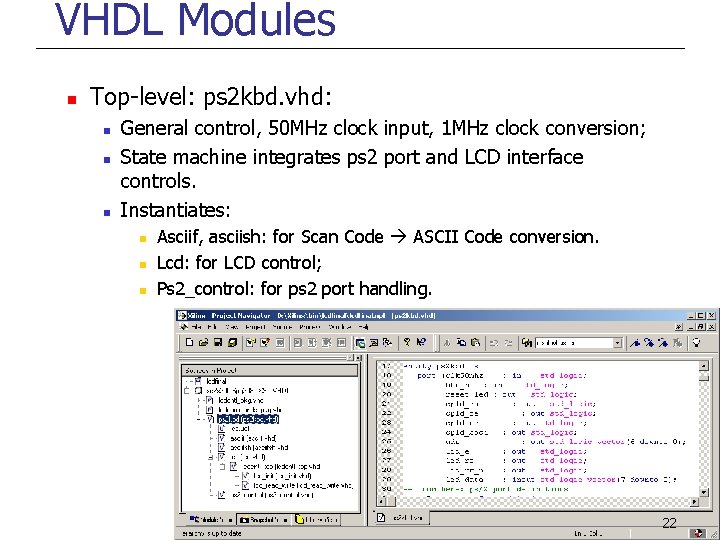

VHDL Modules n Top-level: ps 2 kbd. vhd: n n n General control, 50 MHz clock input, 1 MHz clock conversion; State machine integrates ps 2 port and LCD interface controls. Instantiates: n n n Asciif, asciish: for Scan Code ASCII Code conversion. Lcd: for LCD control; Ps 2_control: for ps 2 port handling. 22

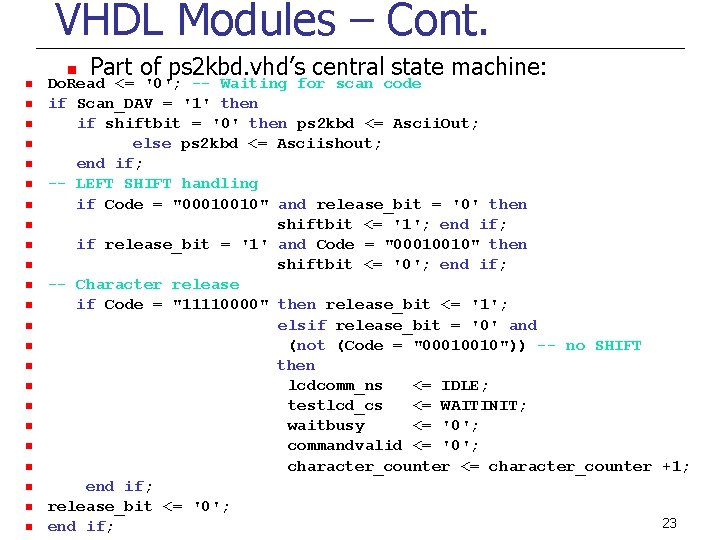

VHDL Modules – Cont. n n n n n n Part of ps 2 kbd. vhd’s central state machine: Do. Read <= '0'; -- Waiting for scan code if Scan_DAV = '1' then if shiftbit = '0' then ps 2 kbd <= Ascii. Out; else ps 2 kbd <= Asciishout; end if; -- LEFT SHIFT handling if Code = "00010010" and release_bit = '0' then shiftbit <= '1'; end if; if release_bit = '1' and Code = "00010010" then shiftbit <= '0'; end if; -- Character release if Code = "11110000" then release_bit <= '1'; elsif release_bit = '0' and (not (Code = "00010010")) -- no SHIFT then lcdcomm_ns <= IDLE; testlcd_cs <= WAITINIT; waitbusy <= '0'; commandvalid <= '0'; character_counter <= character_counter +1; end if; release_bit <= '0'; 23 end if;

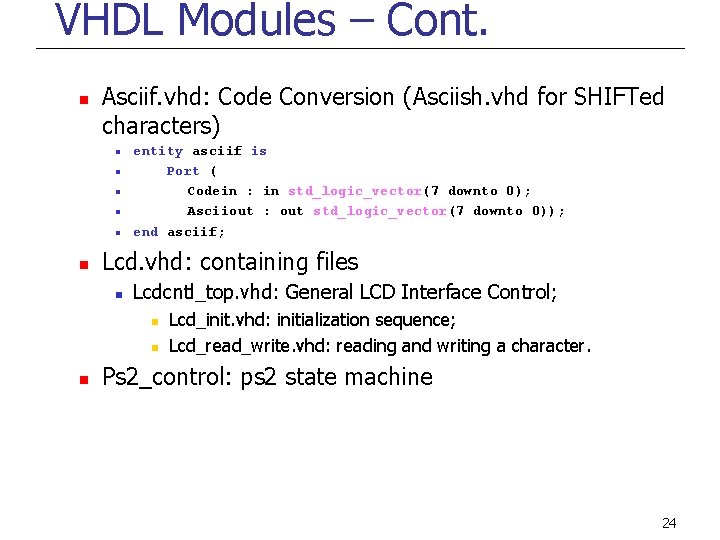

VHDL Modules – Cont. n Asciif. vhd: Code Conversion (Asciish. vhd for SHIFTed characters) n n n entity asciif is Port ( Codein : in std_logic_vector(7 downto 0); Asciiout : out std_logic_vector(7 downto 0)); end asciif; Lcd. vhd: containing files n Lcdcntl_top. vhd: General LCD Interface Control; n n n Lcd_init. vhd: initialization sequence; Lcd_read_write. vhd: reading and writing a character. Ps 2_control: ps 2 state machine 24

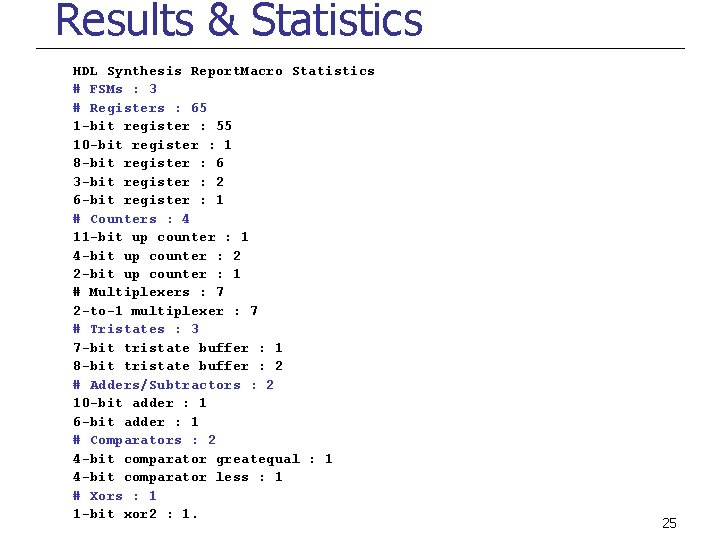

Results & Statistics HDL Synthesis Report. Macro Statistics # FSMs : 3 # Registers : 65 1 -bit register : 55 10 -bit register : 1 8 -bit register : 6 3 -bit register : 2 6 -bit register : 1 # Counters : 4 11 -bit up counter : 1 4 -bit up counter : 2 2 -bit up counter : 1 # Multiplexers : 7 2 -to-1 multiplexer : 7 # Tristates : 3 7 -bit tristate buffer : 1 8 -bit tristate buffer : 2 # Adders/Subtractors : 2 10 -bit adder : 1 6 -bit adder : 1 # Comparators : 2 4 -bit comparator greatequal : 1 4 -bit comparator less : 1 # Xors : 1 1 -bit xor 2 : 1. 25

Summary n n n The VHDL program detects pushed characters and displays them in the first line of LCD display. After 16 characters it clears the screen and sets the cursor back. LEFT SHIFT function is also implemented for displaying: n n Capital letters; Special characters (for example !@#$%^&, etc. ). 26

Comments n Digilent specifications are sometimes inaccurate and do not match with each other or other documents: n n n Scan code for Z is 1 A and not 1 Z as it is indicated in dio 2_rm. pdf. Okaya documentation for LCD is different to Digilents documents. PS/2 port signals can be bidirectional in case of keyboard PS/2 port. 27

Thank You for Your Attention! 28

- Slides: 28