Jan 2005 doc IEEE 802 15 05 0103

- Slides: 14

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Project: IEEE P 802. 15 Working Group for Wireless Personal Area Networks (WPANs) Submission Title: [Enhanced DSSS Code Sequence with Offset QPSK for 802. 15. 4 b High Rate Alt-PHY] Date Submitted: [13 Jan, 2004] Source: [Liang Zhang, Hongyu Gu, Liang Li, Yafei Tian, Chenyang Yang, Zhijian Hu, Yong Gu] Company: [WXZJ] Address: [2 Xinxi St, Building D, Haidian District, Beijing, China 100085 ] Voice: [86 -10 -139 -11895301], E-Mail: [liang_1@yahoo. com] Re: [Response to the call for proposal of IEEE 802. 15. 4 b] Abstract: [This presentation compares all proposals for the IEEE 802. 15. 4 b PHY standard. ] Purpose: [Proposal to IEEE 802. 15. 4 b Task Group] Notice: This document has been prepared to assist the IEEE P 802. 15. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein. Release: The contributor acknowledges and accepts that this contribution becomes the property of IEEE and may be made publicly available by P 802. 15. Submission 1 Liang Li, WXZJ

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Motivation It is desirable choose a code sequences that will lead to efficient transmission and low implementation complexity. In particular, it should: 1. Avoid spikes in frequency spectrum 2. Simplify correlation operations 3. Enable simple frequency offset and DC compensation Submission 2 Liang Li, WXZJ

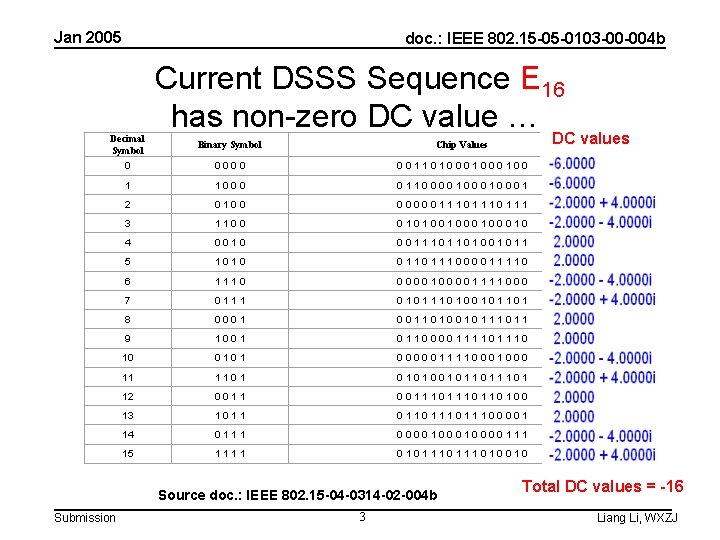

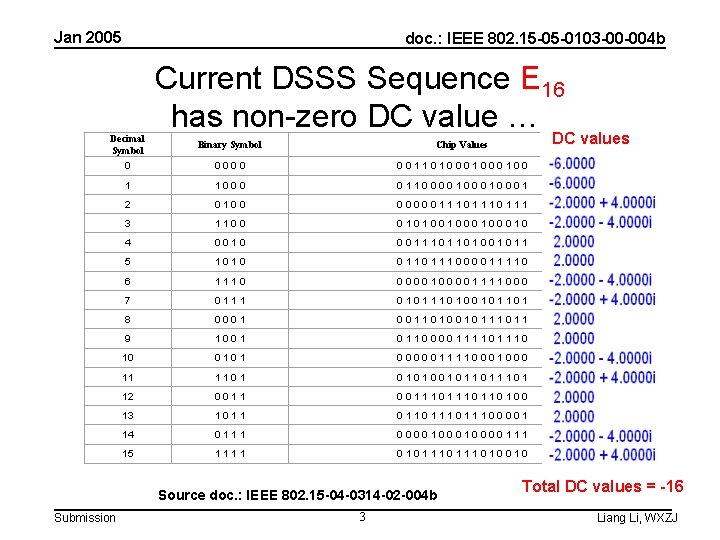

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Decimal Symbol Current DSSS Sequence E 16 has non-zero DC value …. Chip Values 0 0000 001101000100 1 1000 011000010001 2 0100 000001110111 3 1100 010100100010 4 0010 0011101101001011 5 1010 0110111000011110 6 1110 00001111000 7 0111 0101110100101101 8 0001 001101001011 9 1001 011000011110 10 0101 000001111000 11 1101 010100101101 12 001110110100 13 1011 011011100001 14 0111 000010000111 15 1111 010111010010 Source doc. : IEEE 802. 15 -04 -0314 -02 -004 b Submission DC values Binary Symbol 3 Total DC values = -16 Liang Li, WXZJ

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Motivation As such, it is desirable that the code sequences have the following properties: 1. All sequences contain an equal number of ones and zeros in total 2. All sequences contain an equal number of ones and zeros in the even numbered chips (I phase) 3. All sequences contain an equal number of ones and zeros in the odd numbered chips (Q phase) 4. Total phase rotation in I / Q plane accumulates to 0 degree over the complete symbol 5. The first 8 symbols are shifted versions of each other 6. The last 8 symbols have inverted odd numbered chips (Q phase); when compared to the 8 first symbols, have the exact inverted baseband phase Submission 4 Liang Li, WXZJ

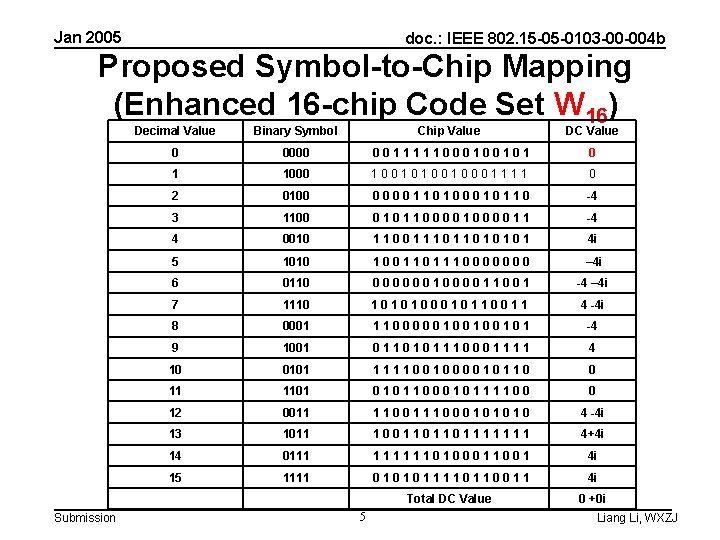

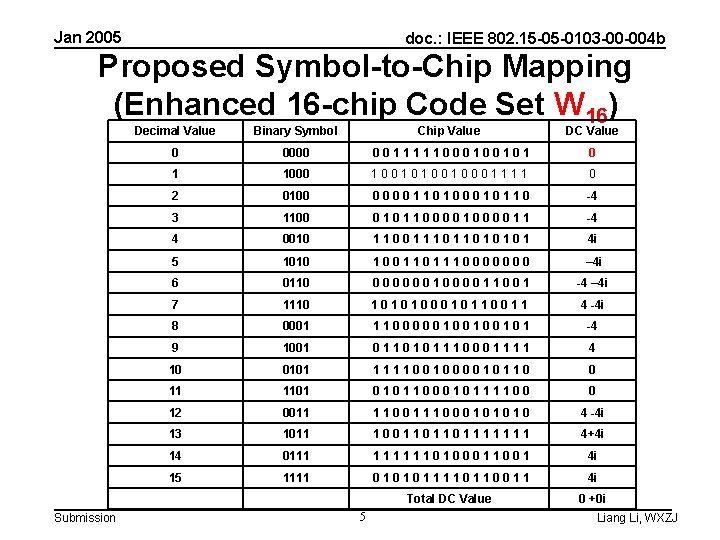

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Proposed Symbol-to-Chip Mapping (Enhanced 16 -chip Code Set W 16) Submission Decimal Value Binary Symbol Chip Value DC Value 0 0000 0011111000100101 0 1 1000 10010001111 0 2 0100 0000110100010110 -4 3 1100 01011000011 -4 4 0010 1100111011010101 4 i 5 1010 1001101110000000 – 4 i 6 0110 00000011001 -4 – 4 i 7 1110 1010100010110011 4 -4 i 8 0001 1100000100100101 -4 9 1001 0110101110001111 4 10 0101 1111001000010110 0 11 1101 0101100010111100 0 12 0011 1100111000101010 4 -4 i 13 1011 1001101101111111 4+4 i 14 0111 1111110100011001 4 i 15 1111 0101011110110011 4 i Total DC Value 0 +0 i 5 Liang Li, WXZJ

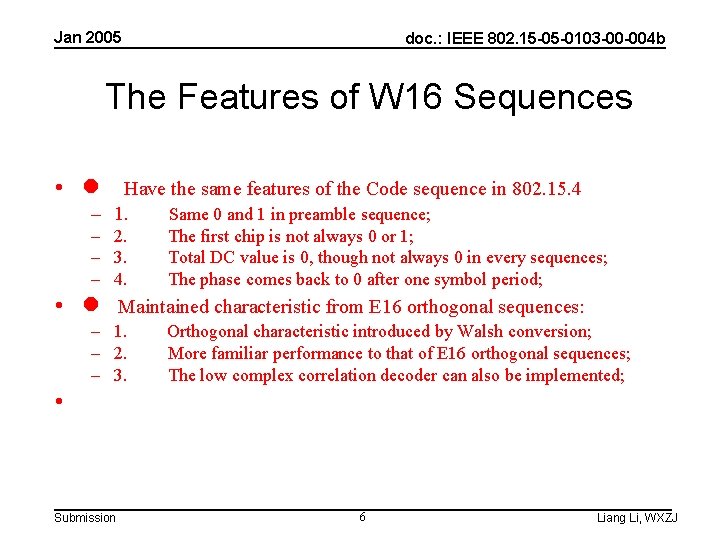

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b The Features of W 16 Sequences • l Have the same features of the Code sequence in 802. 15. 4 – 1. – 2. – 3. – 4. Same 0 and 1 in preamble sequence; The first chip is not always 0 or 1; Total DC value is 0, though not always 0 in every sequences; The phase comes back to 0 after one symbol period; • l Maintained characteristic from E 16 orthogonal sequences: – 1. – 2. – 3. Orthogonal characteristic introduced by Walsh conversion; More familiar performance to that of E 16 orthogonal sequences; The low complex correlation decoder can also be implemented; • Submission 6 Liang Li, WXZJ

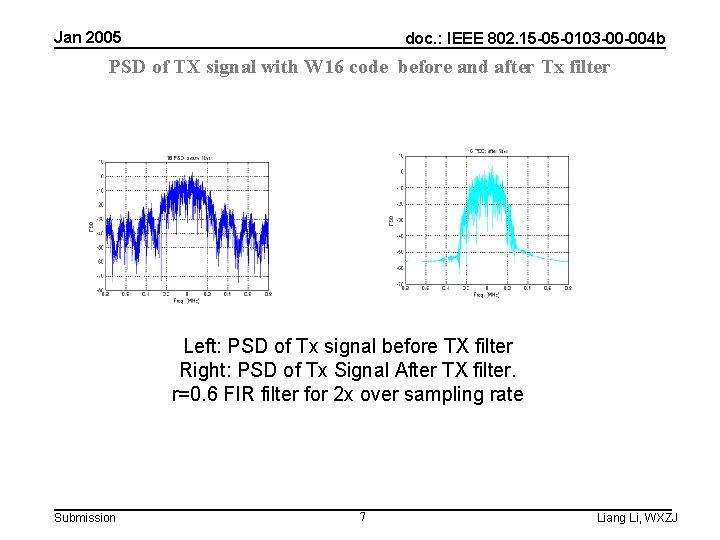

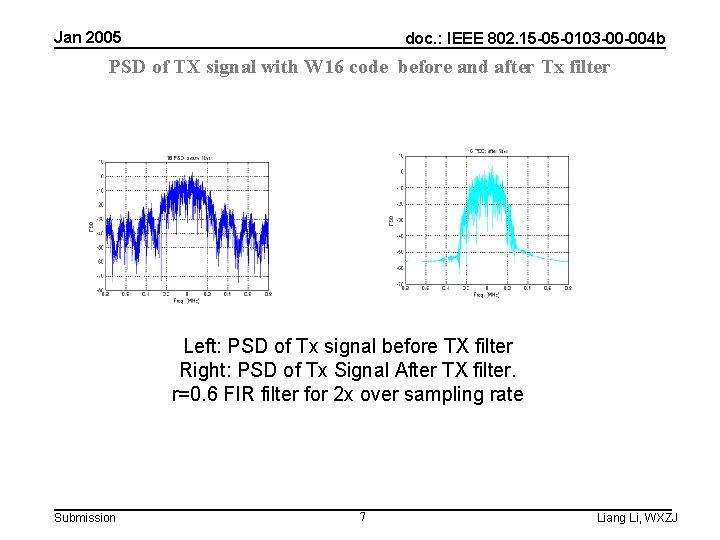

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b PSD of TX signal with W 16 code before and after Tx filter Left: PSD of Tx signal before TX filter Right: PSD of Tx Signal After TX filter. r=0. 6 FIR filter for 2 x over sampling rate Submission 7 Liang Li, WXZJ

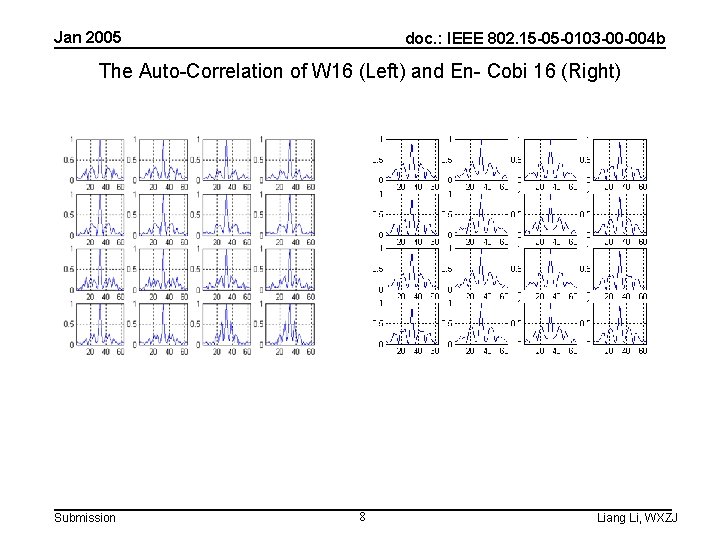

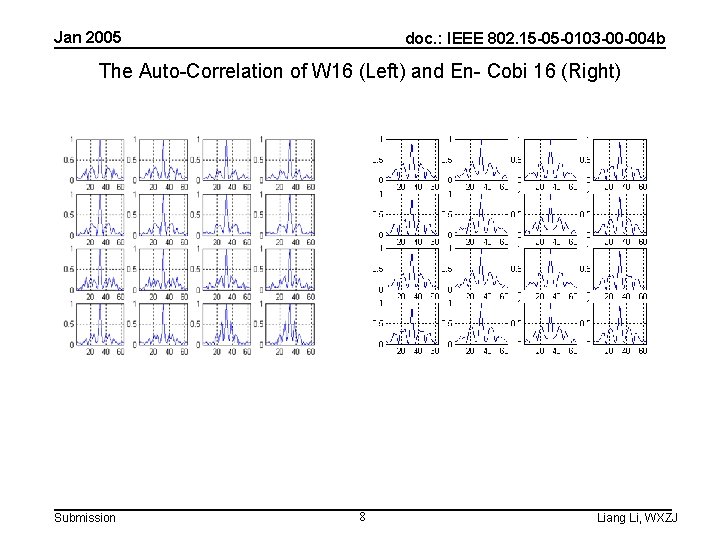

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b The Auto-Correlation of W 16 (Left) and En- Cobi 16 (Right) Submission 8 Liang Li, WXZJ

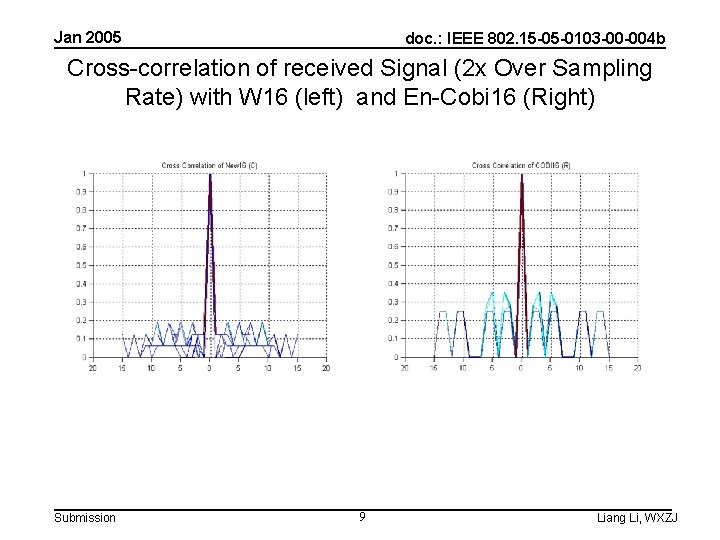

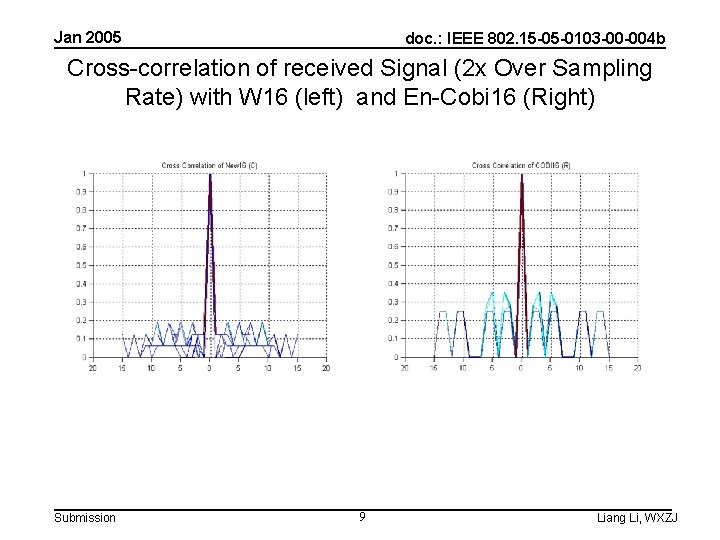

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Cross-correlation of received Signal (2 x Over Sampling Rate) with W 16 (left) and En-Cobi 16 (Right) Submission 9 Liang Li, WXZJ

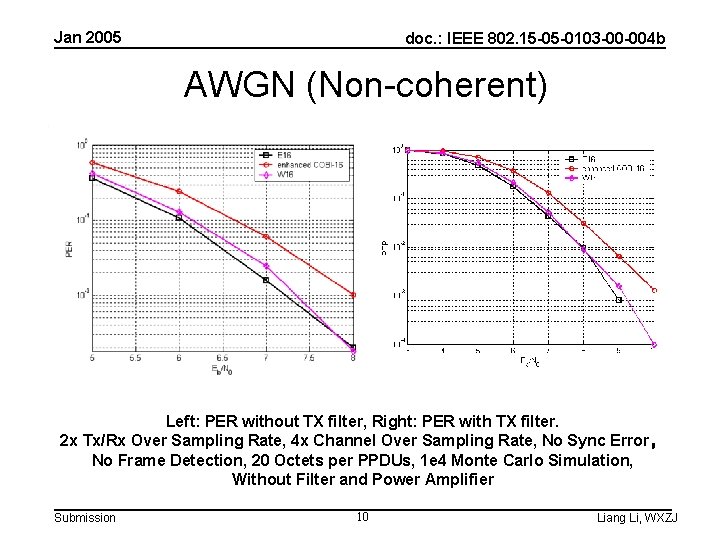

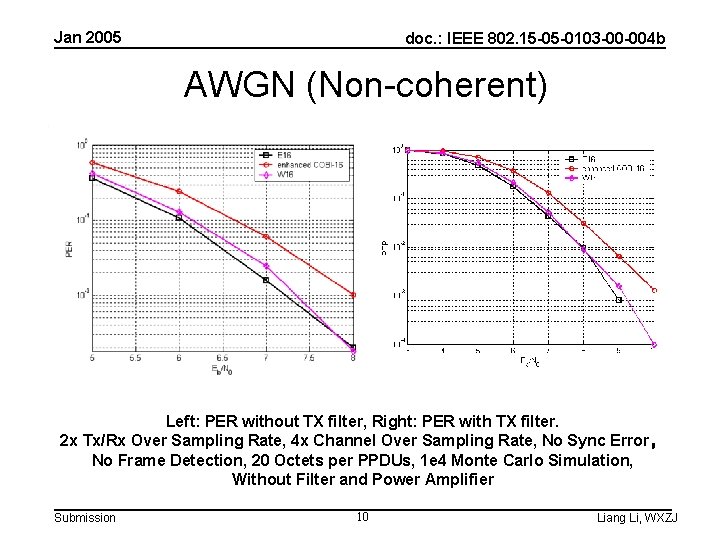

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b AWGN (Non-coherent) Left: PER without TX filter, Right: PER with TX filter. 2 x Tx/Rx Over Sampling Rate, 4 x Channel Over Sampling Rate, No Sync Error, No Frame Detection, 20 Octets per PPDUs, 1 e 4 Monte Carlo Simulation, Without Filter and Power Amplifier Submission 10 Liang Li, WXZJ

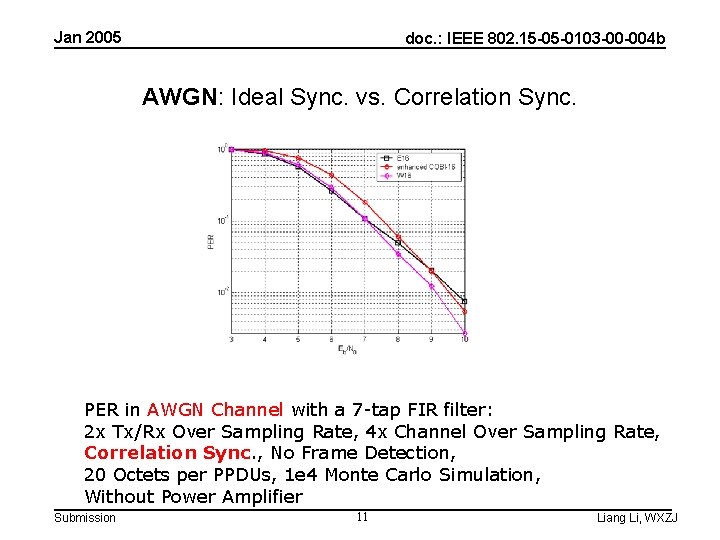

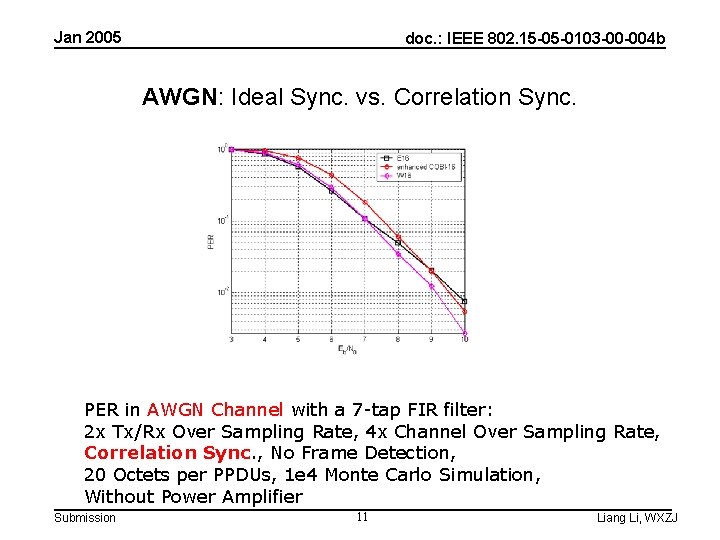

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b AWGN: Ideal Sync. vs. Correlation Sync. PER in AWGN Channel with a 7 -tap FIR filter: 2 x Tx/Rx Over Sampling Rate, 4 x Channel Over Sampling Rate, Correlation Sync. , No Frame Detection, 20 Octets per PPDUs, 1 e 4 Monte Carlo Simulation, Without Power Amplifier Submission 11 Liang Li, WXZJ

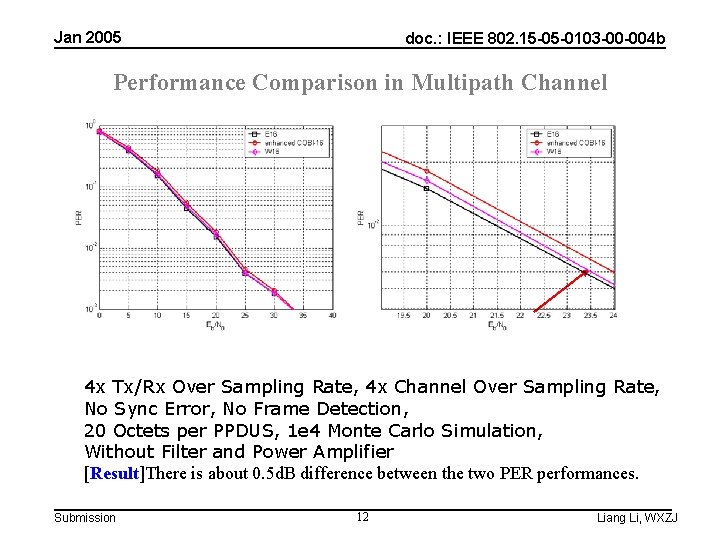

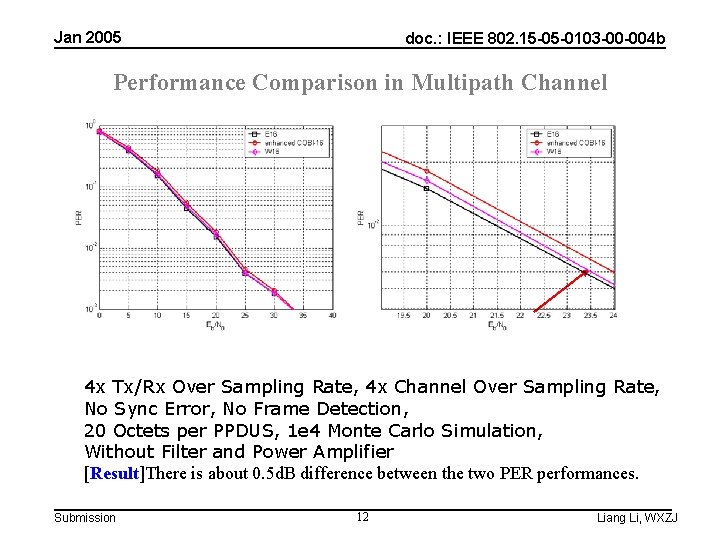

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Performance Comparison in Multipath Channel 4 x Tx/Rx Over Sampling Rate, 4 x Channel Over Sampling Rate, No Sync Error, No Frame Detection, 20 Octets per PPDUS, 1 e 4 Monte Carlo Simulation, Without Filter and Power Amplifier [Result]There is about 0. 5 d. B difference between the two PER performances. Submission 12 Liang Li, WXZJ

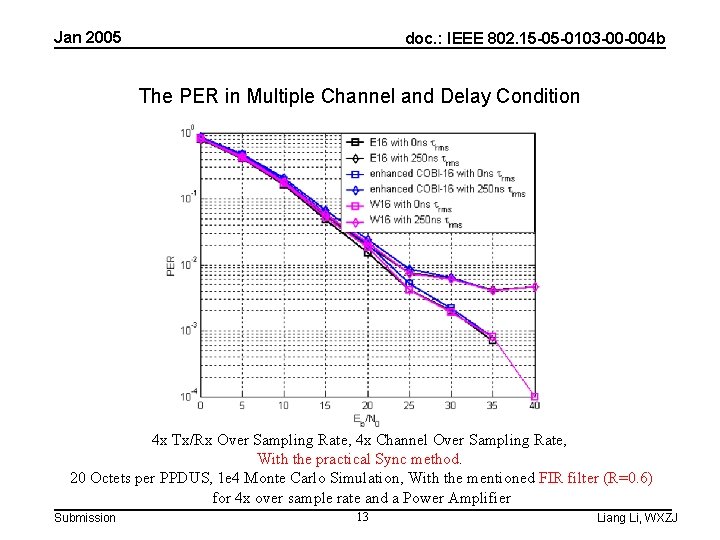

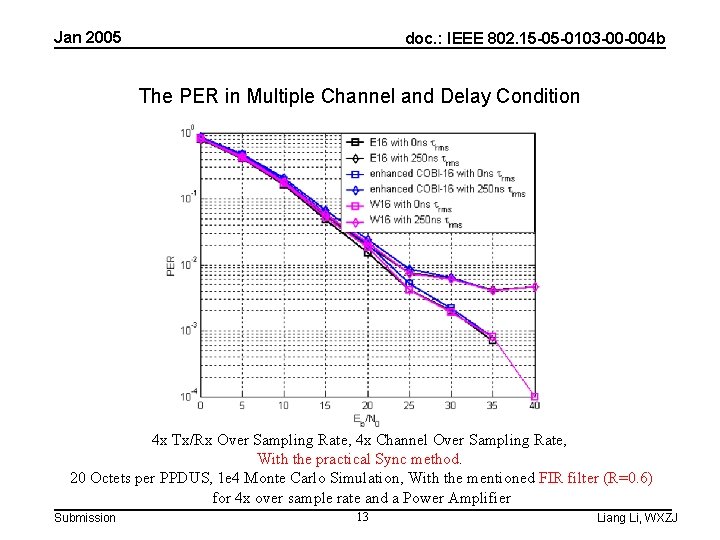

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b The PER in Multiple Channel and Delay Condition 4 x Tx/Rx Over Sampling Rate, 4 x Channel Over Sampling Rate, With the practical Sync method. 20 Octets per PPDUS, 1 e 4 Monte Carlo Simulation, With the mentioned FIR filter (R=0. 6) for 4 x over sample rate and a Power Amplifier Submission 13 Liang Li, WXZJ

Jan 2005 doc. : IEEE 802. 15 -05 -0103 -00 -004 b Summary • Enhanced W 16 can satisfy the stated 6 criteria that will • • Submission Avoid spikes in frequency spectrum Simplify correlation operations Enable simple frequency offset and DC compensation The performance is the same as the DSSS (E 16) 14 Liang Li, WXZJ