ITRS 2003 keff Roadmap Revision Effective Dielectric Constant

- Slides: 9

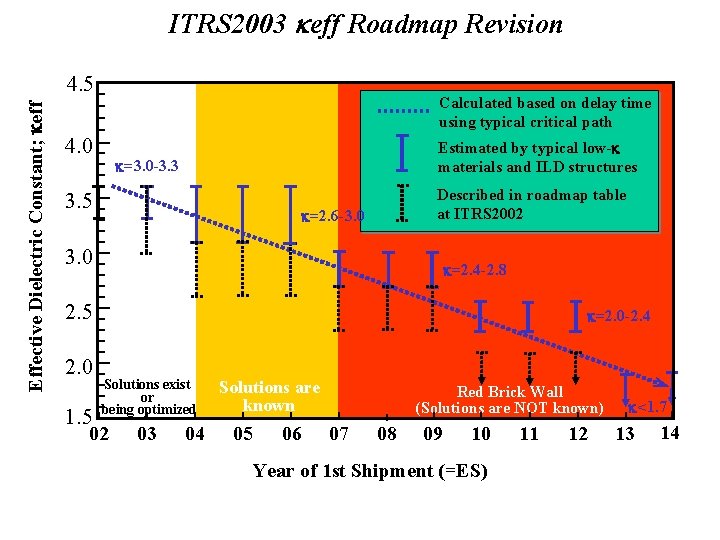

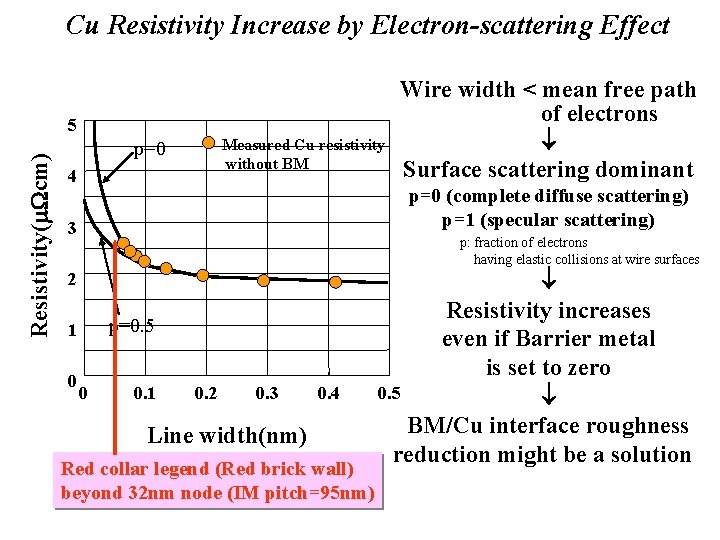

ITRS 2003 keff Roadmap Revision Effective Dielectric Constant; keff 4. 5 Calculated based on delay time using typical critical path 4. 0 Estimated by typical low-k materials and ILD structures k=3. 0 -3. 3 3. 5 Described in roadmap table at ITRS 2002 k=2. 6 -3. 0 k=2. 4 -2. 8 2. 5 2. 0 1. 5 k=2. 0 -2. 4 Solutions exist or being optimized 02 03 04 Solutions are known 05 06 Red Brick Wall (Solutions are NOT known) 07 08 09 10 Year of 1 st Shipment (=ES) 11 12 k<1. 7 13 14

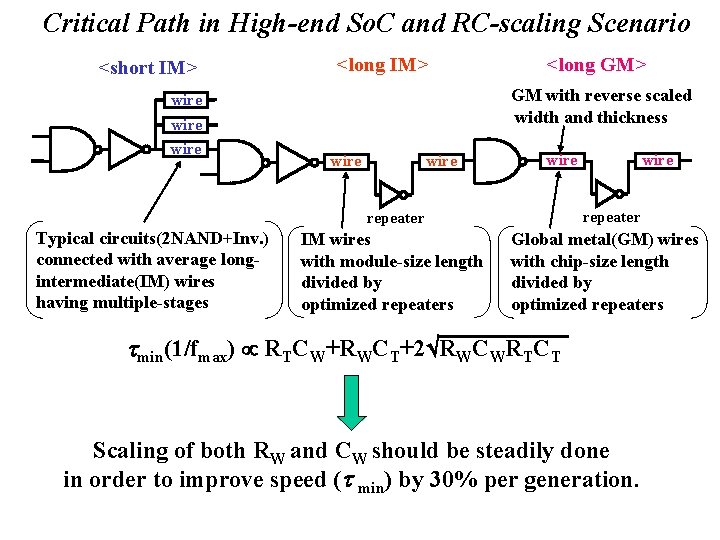

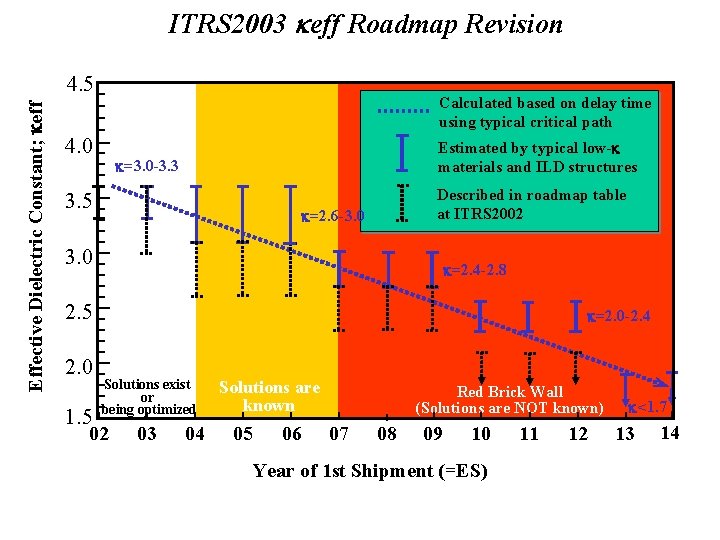

Critical Path in High-end So. C and RC-scaling Scenario <short IM> <long IM> GM with reverse scaled width and thickness wire <long GM> wire repeater Typical circuits(2 NAND+Inv. ) connected with average longintermediate(IM) wires having multiple-stages IM wires with module-size length divided by optimized repeaters wire Global metal(GM) wires with chip-size length divided by optimized repeaters tmin(1/fmax) µ RTCW+RWCT+2ÖRWCWRTCT Scaling of both RW and CW should be steadily done in order to improve speed (t min) by 30% per generation.

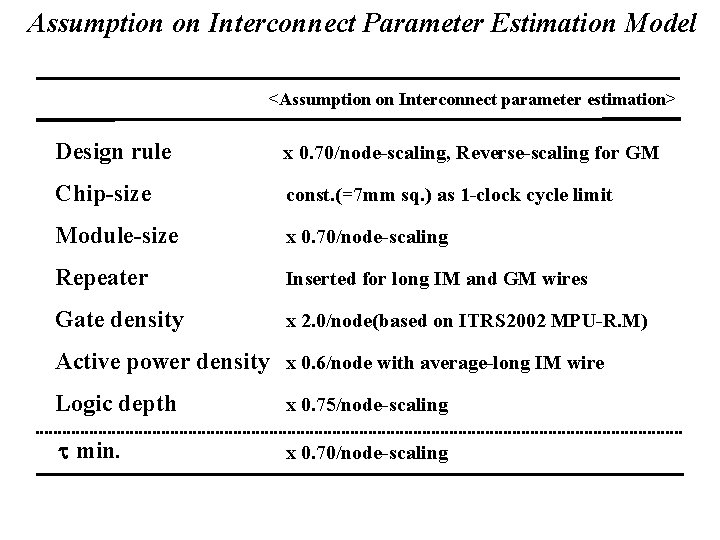

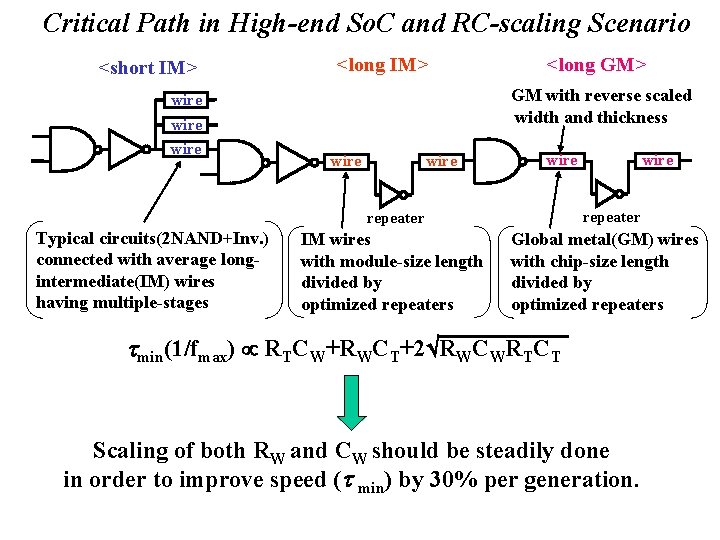

Assumption on Interconnect Parameter Estimation Model <Assumption on Interconnect parameter estimation> Design rule x 0. 70/node-scaling, Reverse-scaling for GM Chip-size const. (=7 mm sq. ) as 1 -clock cycle limit Module-size x 0. 70/node-scaling Repeater Inserted for long IM and GM wires Gate density x 2. 0/node(based on ITRS 2002 MPU-R. M) Active power density x 0. 6/node with average-long IM wire Logic depth x 0. 75/node-scaling t min. x 0. 70/node-scaling

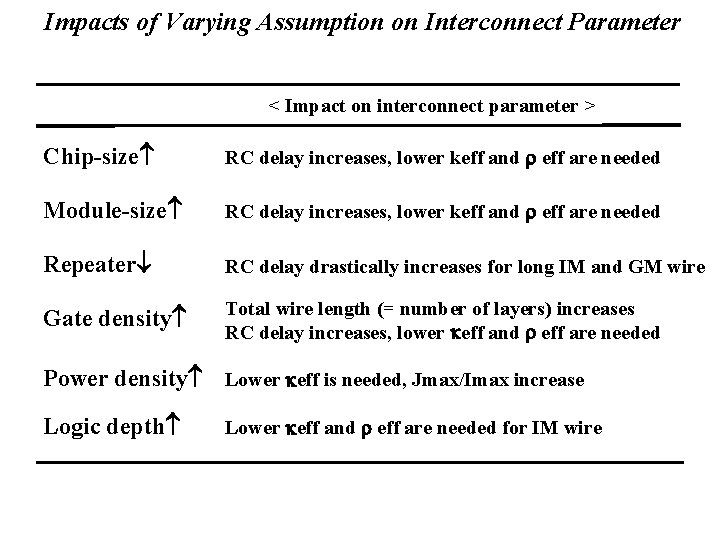

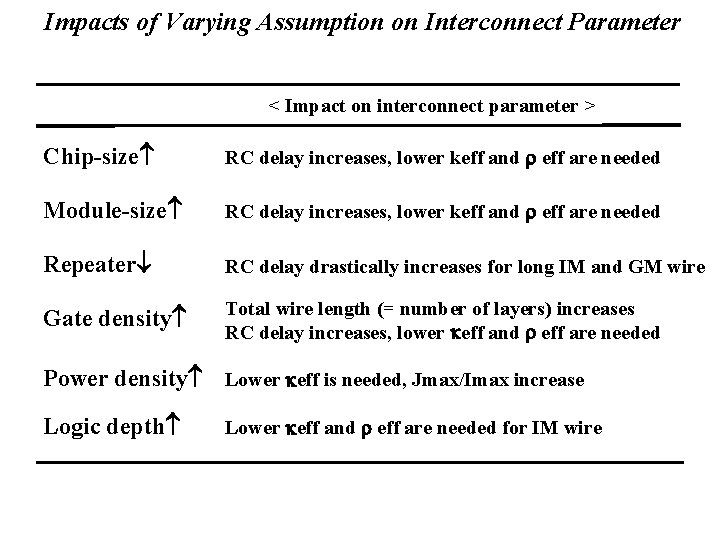

Impacts of Varying Assumption on Interconnect Parameter < Impact on interconnect parameter > Chip-size RC delay increases, lower keff and r eff are needed Module-size RC delay increases, lower keff and r eff are needed Repeater¯ RC delay drastically increases for long IM and GM wire Gate density Total wire length (= number of layers) increases RC delay increases, lower keff and r eff are needed Power density Lower keff is needed, Jmax/Imax increase Logic depth Lower keff and r eff are needed for IM wire

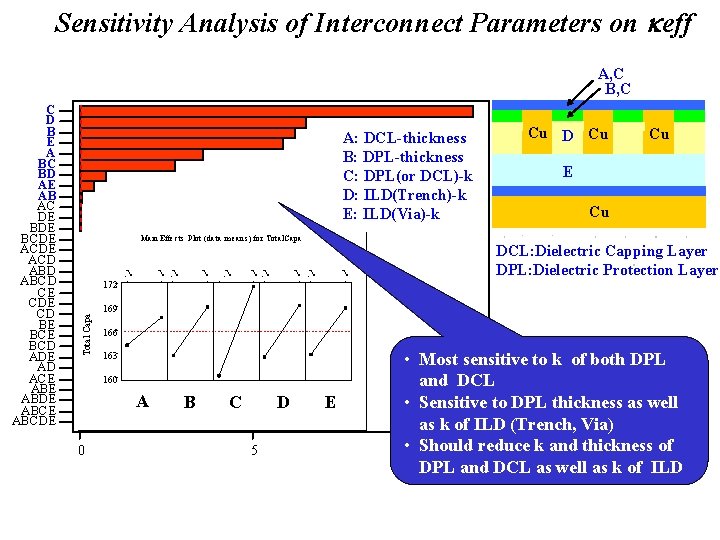

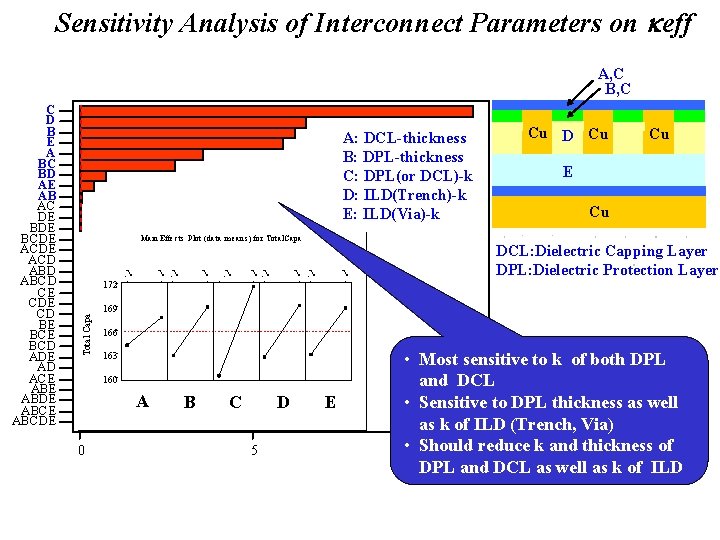

Sensitivity Analysis of Interconnect Parameters on keff A, C B, C A: DCL-thickness B: DPL-thickness C: DPL(or DCL)-k D: ILD(Trench)-k E: ILD(Via)-k Ma in Effe cts P lot (da ta me a ns ) for Tota l. Ca pa 172 Total Capa C D B E A BC BD AE AB AC DE BCDE ACD ABCD CE CD BE BCD ADE AD ACE ABDE ABCDE -1 1 -1 1 Cu E Cu DCL: Dielectric Capping Layer DPL: Dielectric Protection Layer 169 166 163 160 Bf_t A 0 1 Cu D Cu Cap_t B Cap_k Tr_ILD_k Via_ILD_k C D 5 E • Most sensitive to k of both DPL and DCL • Sensitive to DPL thickness as well as k of ILD (Trench, Via) • Should reduce k and thickness of 10 DPL and DCL as well as k of ILD

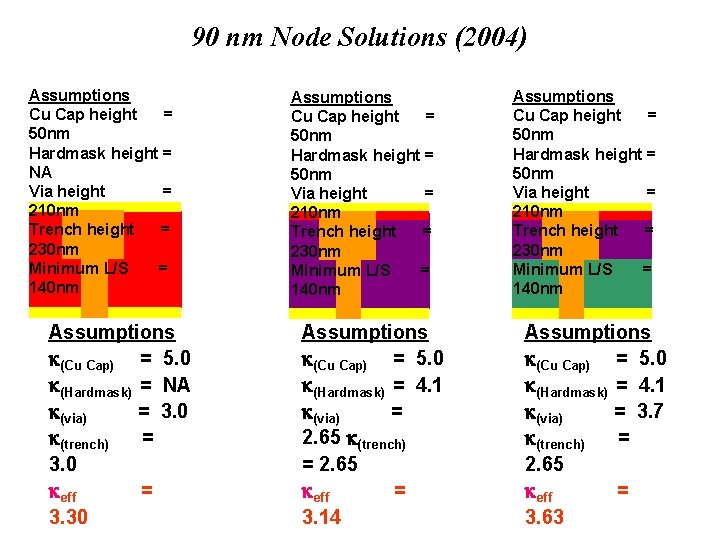

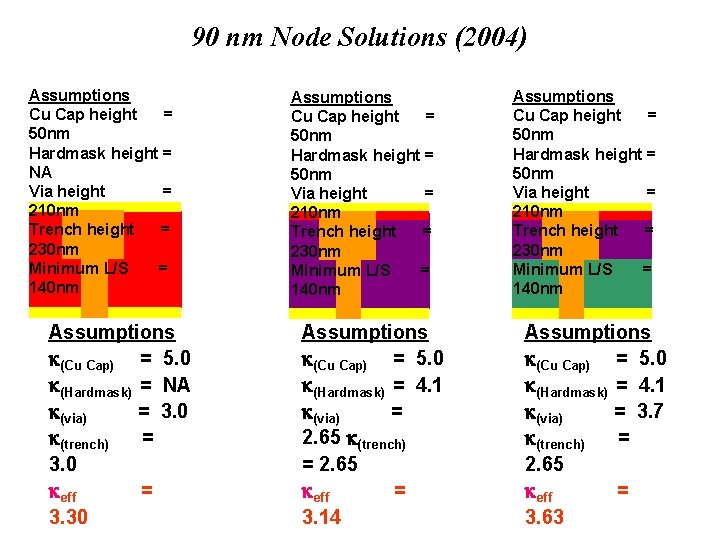

90 nm Node Solutions (2004) Assumptions Cu Cap height = 50 nm Hardmask height = NA Via height = 210 nm Trench height = 230 nm Minimum L/S = 140 nm Assumptions k(Cu Cap) = 5. 0 k(Hardmask) = NA k(via) = 3. 0 k(trench) = 3. 0 keff = 3. 30 Assumptions Cu Cap height = 50 nm Hardmask height = 50 nm Via height = 210 nm Trench height = 230 nm Minimum L/S = 140 nm Assumptions k(Cu Cap) = 5. 0 k(Hardmask) = 4. 1 k(via) = 2. 65 k(trench) = 2. 65 keff = 3. 14 Assumptions Cu Cap height = 50 nm Hardmask height = 50 nm Via height = 210 nm Trench height = 230 nm Minimum L/S = 140 nm Assumptions k(Cu Cap) = 5. 0 k(Hardmask) = 4. 1 k(via) = 3. 7 k(trench) = 2. 65 keff = 3. 63

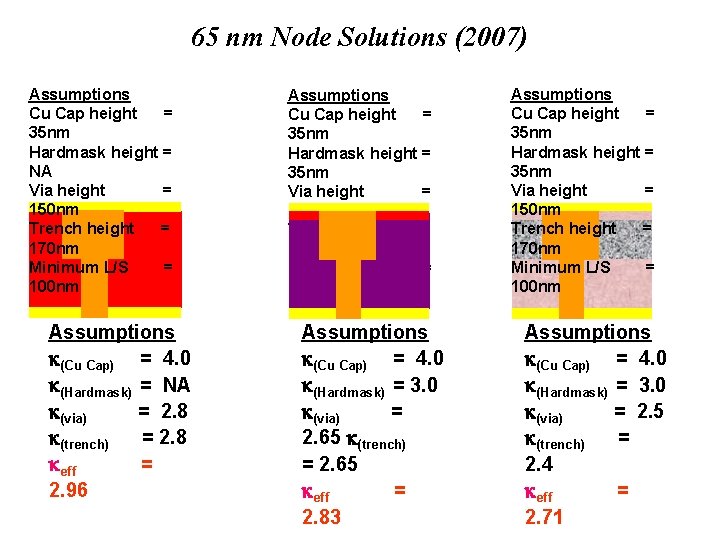

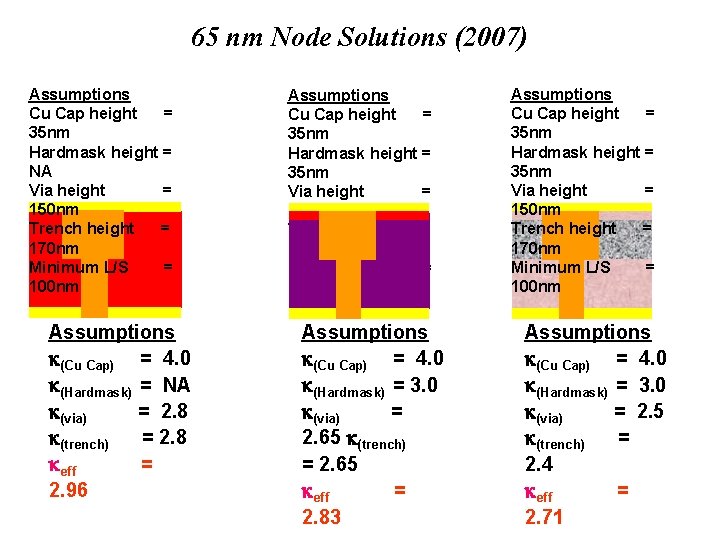

65 nm Node Solutions (2007) Assumptions Cu Cap height = 35 nm Hardmask height = NA Via height = 150 nm Trench height = 170 nm Minimum L/S = 100 nm Assumptions k(Cu Cap) = 4. 0 k(Hardmask) = NA k(via) = 2. 8 k(trench) = 2. 8 keff = 2. 96 Assumptions Cu Cap height = 35 nm Hardmask height = 35 nm Via height = 150 nm Trench height = 170 nm Minimum L/S = 100 nm Assumptions k(Cu Cap) = 4. 0 k(Hardmask) = 3. 0 k(via) = 2. 65 k(trench) = 2. 65 keff = 2. 83 Assumptions Cu Cap height = 35 nm Hardmask height = 35 nm Via height = 150 nm Trench height = 170 nm Minimum L/S = 100 nm Assumptions k(Cu Cap) = 4. 0 k(Hardmask) = 3. 0 k(via) = 2. 5 k(trench) = 2. 4 keff = 2. 71

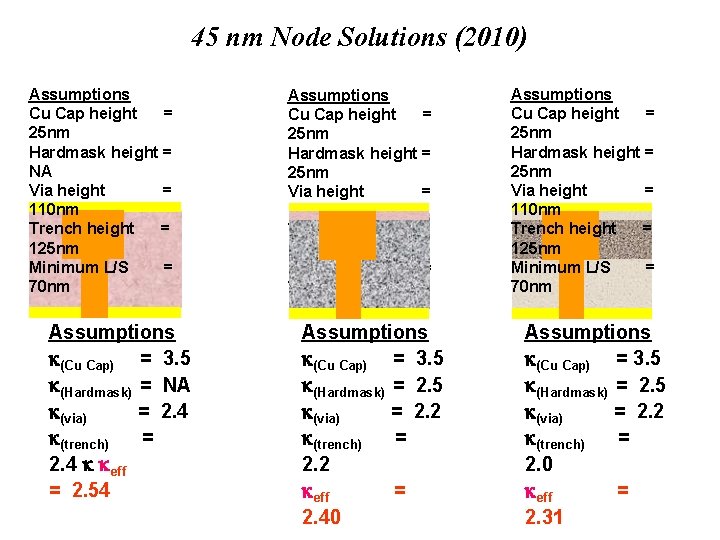

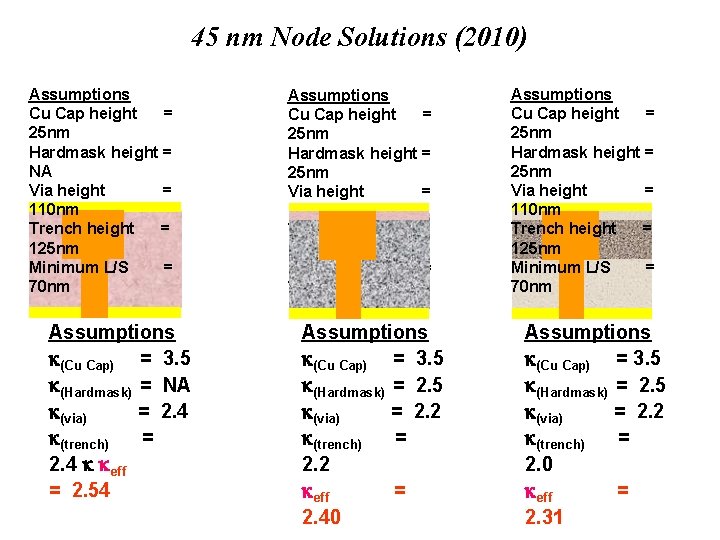

45 nm Node Solutions (2010) Assumptions Cu Cap height = 25 nm Hardmask height = NA Via height = 110 nm Trench height = 125 nm Minimum L/S = 70 nm Assumptions k(Cu Cap) = 3. 5 k(Hardmask) = NA k(via) = 2. 4 k(trench) = 2. 4 k keff = 2. 54 Assumptions Cu Cap height = 25 nm Hardmask height = 25 nm Via height = 110 nm Trench height = 125 nm Minimum L/S = 70 nm Assumptions k(Cu Cap) = 3. 5 k(Hardmask) = 2. 5 k(via) = 2. 2 k(trench) = 2. 2 keff = 2. 40 Assumptions Cu Cap height = 25 nm Hardmask height = 25 nm Via height = 110 nm Trench height = 125 nm Minimum L/S = 70 nm Assumptions k(Cu Cap) = 3. 5 k(Hardmask) = 2. 5 k(via) = 2. 2 k(trench) = 2. 0 keff = 2. 31

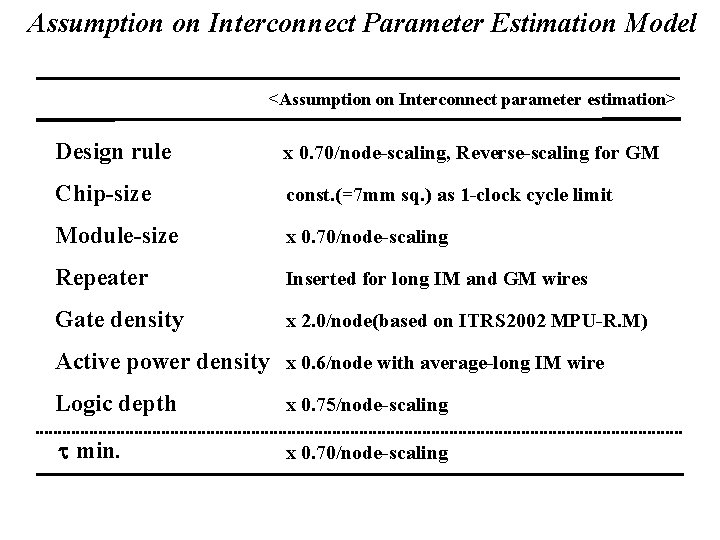

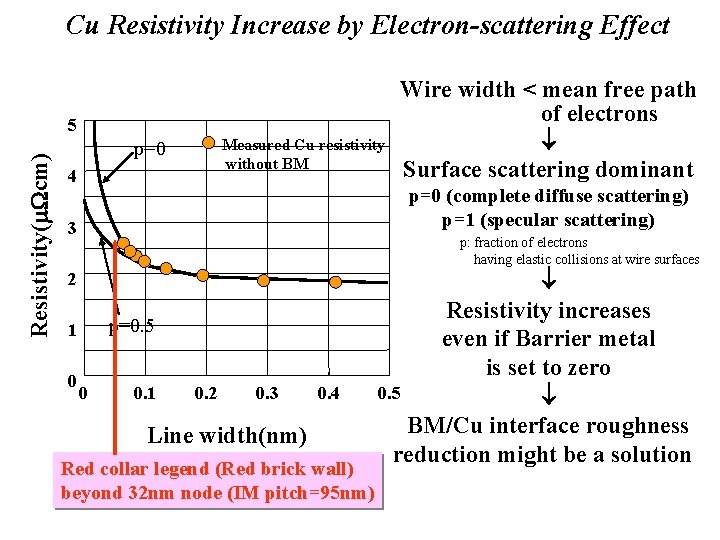

Cu Resistivity Increase by Electron-scattering Effect Resistivity(m. Wcm) 5 Measured Cu resistivity without BM p=0 4 p=0 (complete diffuse scattering) p=1 (specular scattering) 3 p: fraction of electrons having elastic collisions at wire surfaces 2 p=0. 5 1 0 Wire width < mean free path of electrons ¯ Surface scattering dominant 0 0. 1 0. 2 0. 3 0. 4 Line width(nm) Red collar legend (Red brick wall) beyond 32 nm node (IM pitch=95 nm) ¯ Resistivity increases even if Barrier metal is set to zero 0. 5 ¯ BM/Cu interface roughness reduction might be a solution