itl Dragon circuit placement tool Kirill Kornyakov January

- Slides: 12

itl. Dragon circuit placement tool Kirill Kornyakov January, 2007

About project Since summer 2005 Team Meyerov Iosif Kirill Kornyakov Nina Kurina Artem Zhivoderov mentor team leader researcher Email itlab. sa@cs. vmk. unn. ru 2/7/2007 2 / 12

Project goals Our team conducts a research on Very Large Scale Integration placement – a classical problem in IC physical design. Aims of activity • • Investigation of existing placement algorithms Algorithm design and implementation Innovative activity Experiments, analysis and results publication 2/7/2007 3 / 12

Collaboration aspects • Our research can contribute to Intel IC design tools development. • Demonstration of Intel products efficiency and superiority (whitepaper publication, flashdemo creation). • Potential interest of third-party researchers dealing with VLSI CAD. 2/7/2007 4 / 12

Problem relevance Placement is the key step in IC design. Quality of placement determines: • Clock rate • Delay • Power consumption Wire length minimization is a traditional optimization objective. 2/7/2007 5 / 12

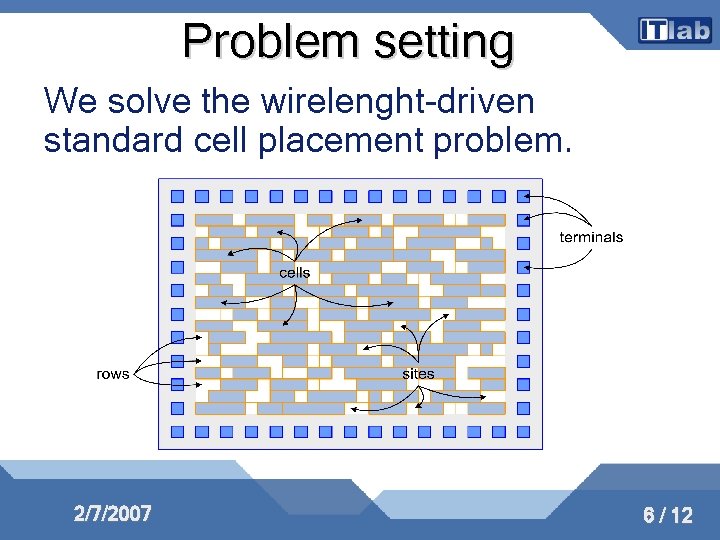

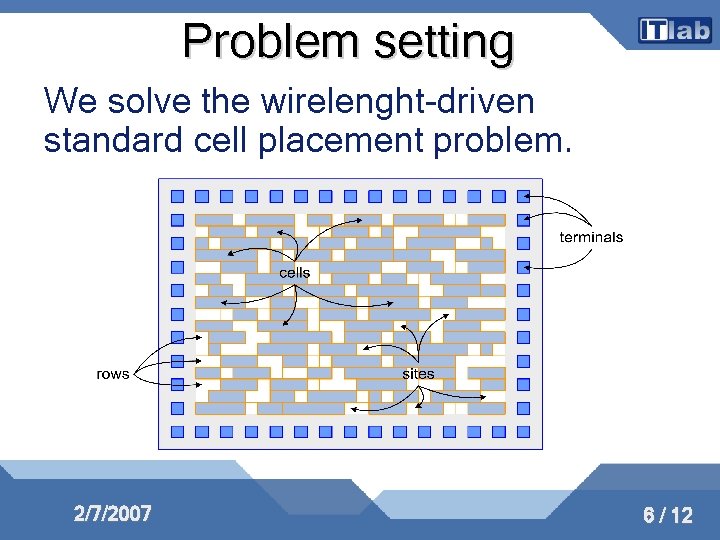

Problem setting We solve the wirelenght-driven standard cell placement problem. 2/7/2007 6 / 12

Placement flow 2/7/2007 7 / 12

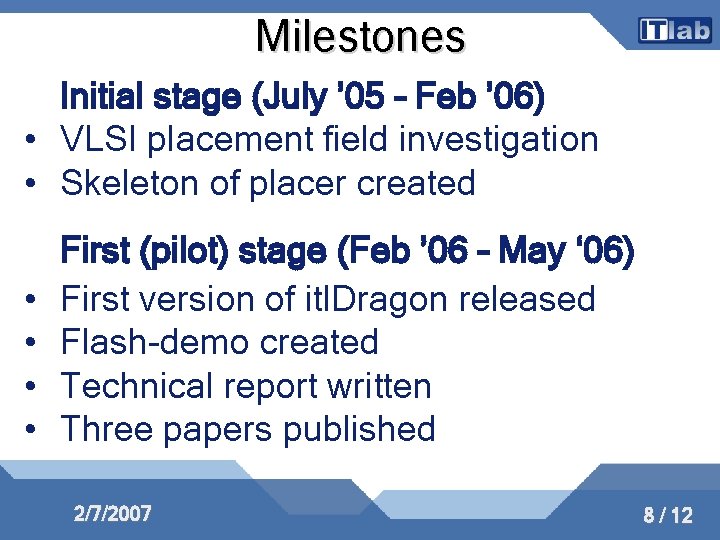

Milestones Initial stage (July ’ 05 – Feb ’ 06) • VLSI placement field investigation • Skeleton of placer created • • First (pilot) stage (Feb ’ 06 – May ‘ 06) First version of itl. Dragon released Flash-demo created Technical report written Three papers published 2/7/2007 8 / 12

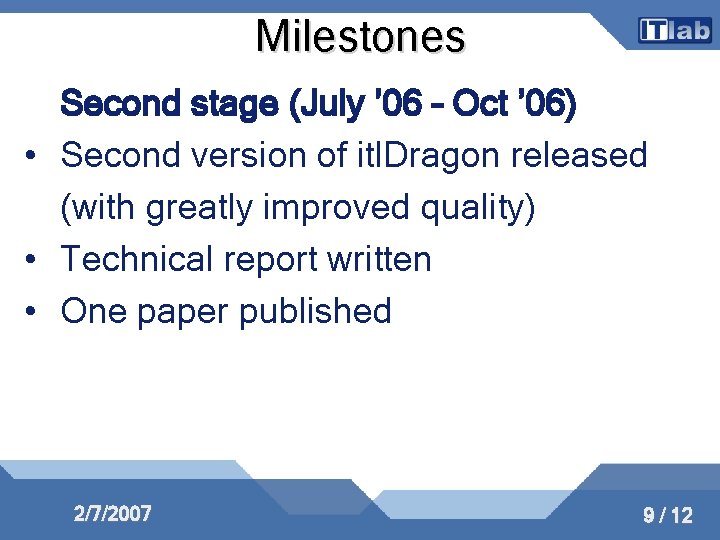

Milestones Second stage (July ’ 06 – Oct ’ 06) • Second version of itl. Dragon released (with greatly improved quality) • Technical report written • One paper published 2/7/2007 9 / 12

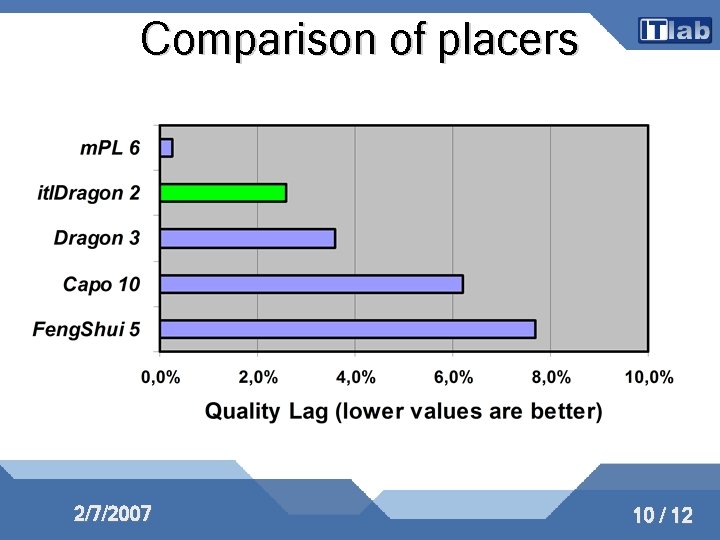

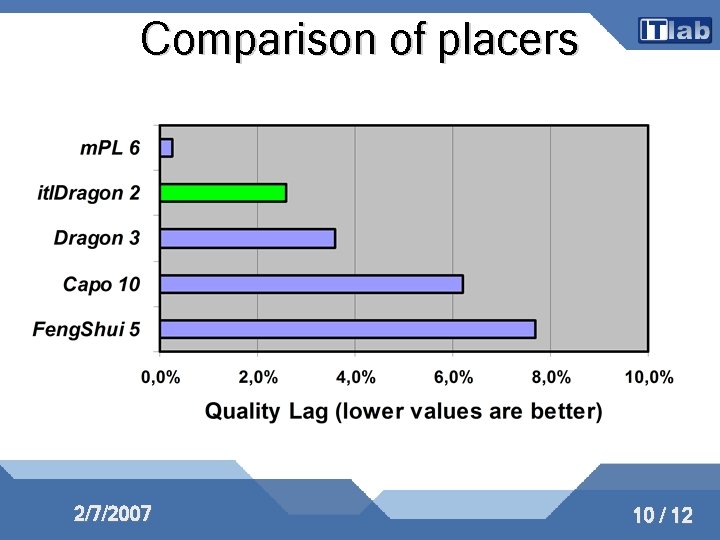

Comparison of placers 2/7/2007 10 / 12

Current activities • Mixed-sized placement. • Publications (algorithm enhancement and complexity analysis). • Placer improvement. 2/7/2007 11 / 12

Questions?