ITk Strips CMOS DAQ The charge Define the

- Slides: 11

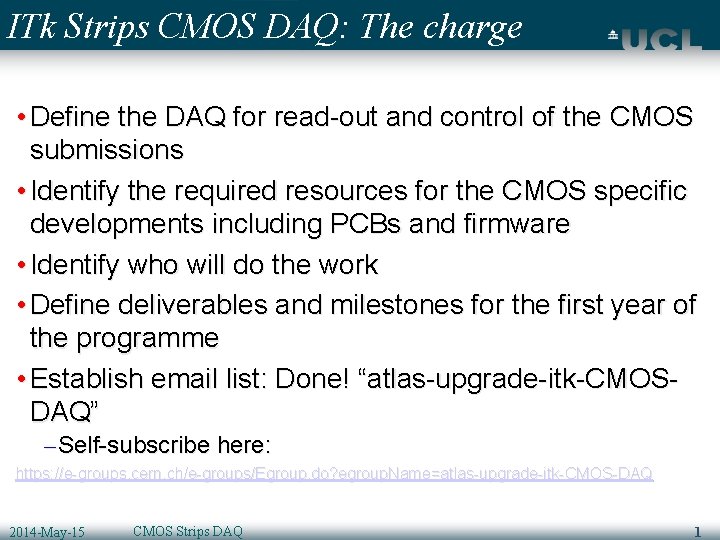

ITk Strips CMOS DAQ: The charge • Define the DAQ for read-out and control of the CMOS submissions • Identify the required resources for the CMOS specific developments including PCBs and firmware • Identify who will do the work • Define deliverables and milestones for the first year of the programme • Establish email list: Done! “atlas-upgrade-itk-CMOSDAQ” – Self-subscribe here: https: //e-groups. cern. ch/e-groups/Egroup. do? egroup. Name=atlas-upgrade-itk-CMOS-DAQ 2014 -May-15 CMOS Strips DAQ 1

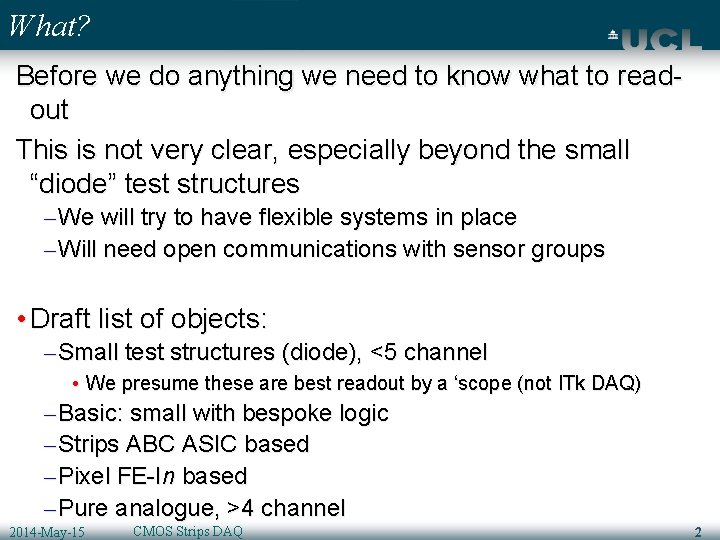

What? Before we do anything we need to know what to readout This is not very clear, especially beyond the small “diode” test structures – We will try to have flexible systems in place – Will need open communications with sensor groups • Draft list of objects: – Small test structures (diode), <5 channel • We presume these are best readout by a ‘scope (not ITk DAQ) – Basic: small with bespoke logic – Strips ABC ASIC based – Pixel FE-In based – Pure analogue, >4 channel 2014 -May-15 CMOS Strips DAQ 2

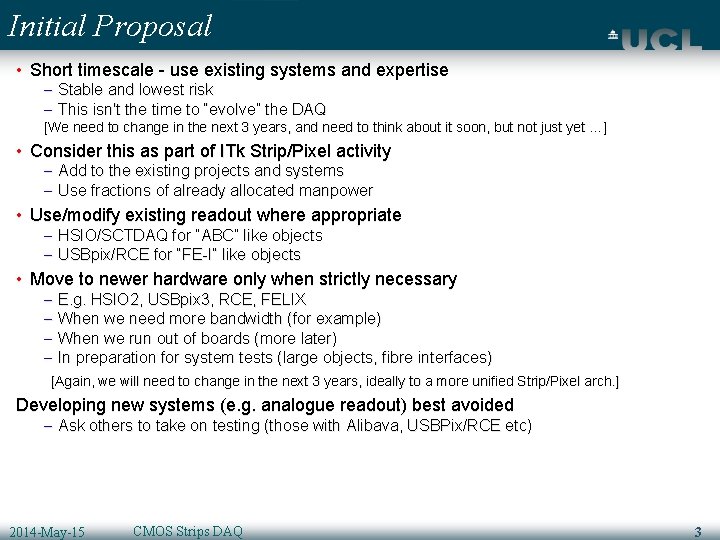

Initial Proposal • Short timescale - use existing systems and expertise – Stable and lowest risk – This isn't the time to “evolve” the DAQ [We need to change in the next 3 years, and need to think about it soon, but not just yet …] • Consider this as part of ITk Strip/Pixel activity – Add to the existing projects and systems – Use fractions of already allocated manpower • Use/modify existing readout where appropriate – HSIO/SCTDAQ for “ABC” like objects – USBpix/RCE for “FE-I” like objects • Move to newer hardware only when strictly necessary – – E. g. HSIO 2, USBpix 3, RCE, FELIX When we need more bandwidth (for example) When we run out of boards (more later) In preparation for system tests (large objects, fibre interfaces) [Again, we will need to change in the next 3 years, ideally to a more unified Strip/Pixel arch. ] Developing new systems (e. g. analogue readout) best avoided – Ask others to take on testing (those with Alibava, USBPix/RCE etc) 2014 -May-15 CMOS Strips DAQ 3

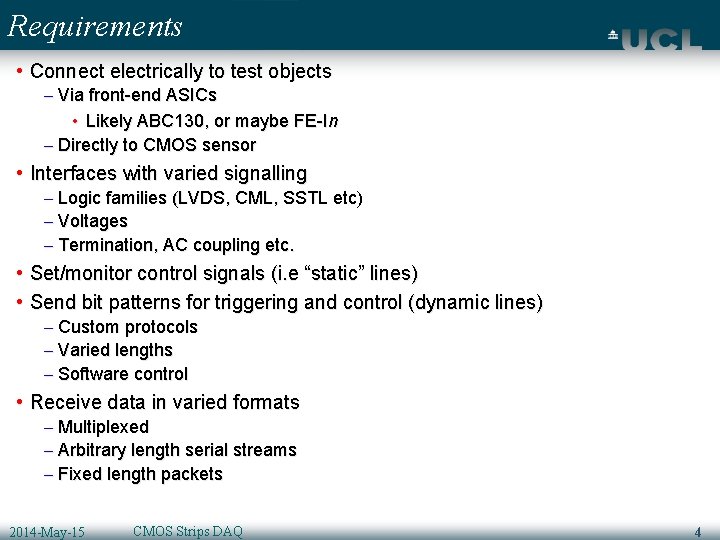

Requirements • Connect electrically to test objects – Via front-end ASICs • Likely ABC 130, or maybe FE-In – Directly to CMOS sensor • Interfaces with varied signalling – Logic families (LVDS, CML, SSTL etc) – Voltages – Termination, AC coupling etc. • Set/monitor control signals (i. e “static” lines) • Send bit patterns for triggering and control (dynamic lines) – Custom protocols – Varied lengths – Software control • Receive data in varied formats – Multiplexed – Arbitrary length serial streams – Fixed length packets 2014 -May-15 CMOS Strips DAQ 4

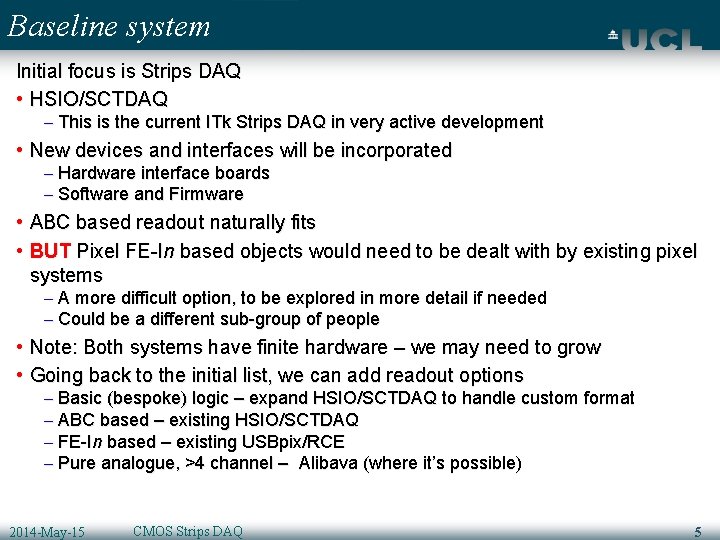

Baseline system Initial focus is Strips DAQ • HSIO/SCTDAQ – This is the current ITk Strips DAQ in very active development • New devices and interfaces will be incorporated – Hardware interface boards – Software and Firmware • ABC based readout naturally fits • BUT Pixel FE-In based objects would need to be dealt with by existing pixel systems – A more difficult option, to be explored in more detail if needed – Could be a different sub-group of people • Note: Both systems have finite hardware – we may need to grow • Going back to the initial list, we can add readout options – Basic (bespoke) logic – expand HSIO/SCTDAQ to handle custom format – ABC based – existing HSIO/SCTDAQ – FE-In based – existing USBpix/RCE – Pure analogue, >4 channel – Alibava (where it’s possible) 2014 -May-15 CMOS Strips DAQ 5

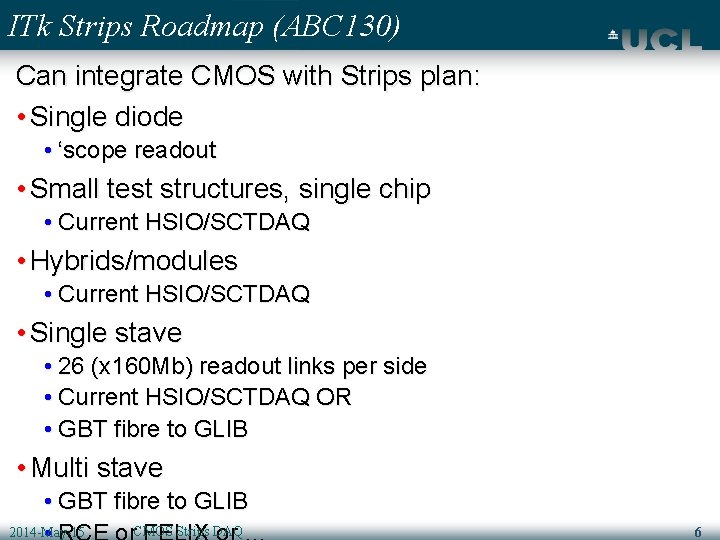

ITk Strips Roadmap (ABC 130) Can integrate CMOS with Strips plan: • Single diode • ‘scope readout • Small test structures, single chip • Current HSIO/SCTDAQ • Hybrids/modules • Current HSIO/SCTDAQ • Single stave • 26 (x 160 Mb) readout links per side • Current HSIO/SCTDAQ OR • GBT fibre to GLIB • Multi stave • GBT fibre to GLIB 2014 -May-15 CMOS Strips DAQ 6

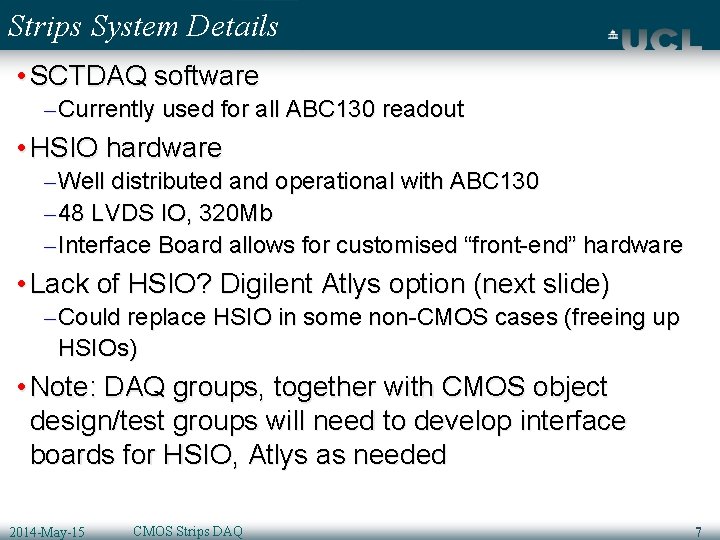

Strips System Details • SCTDAQ software – Currently used for all ABC 130 readout • HSIO hardware – Well distributed and operational with ABC 130 – 48 LVDS IO, 320 Mb – Interface Board allows for customised “front-end” hardware • Lack of HSIO? Digilent Atlys option (next slide) – Could replace HSIO in some non-CMOS cases (freeing up HSIOs) • Note: DAQ groups, together with CMOS object design/test groups will need to develop interface boards for HSIO, Atlys as needed 2014 -May-15 CMOS Strips DAQ 7

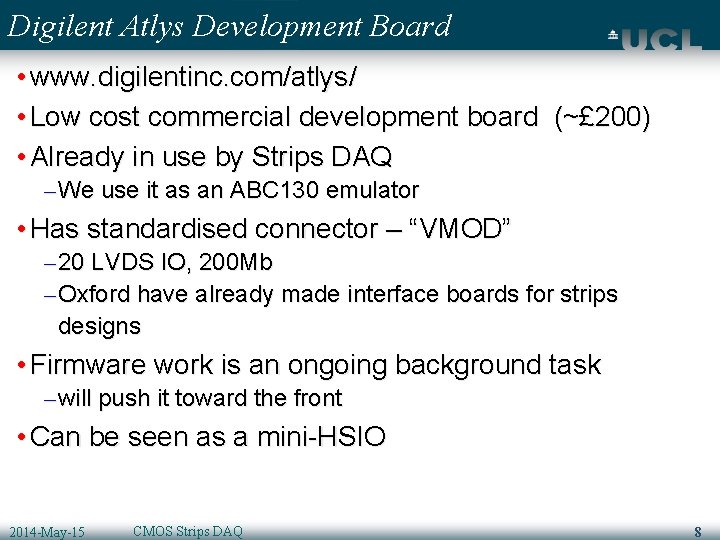

Digilent Atlys Development Board • www. digilentinc. com/atlys/ • Low cost commercial development board (~£ 200) • Already in use by Strips DAQ – We use it as an ABC 130 emulator • Has standardised connector – “VMOD” – 20 LVDS IO, 200 Mb – Oxford have already made interface boards for strips designs • Firmware work is an ongoing background task – will push it toward the front • Can be seen as a mini-HSIO 2014 -May-15 CMOS Strips DAQ 8

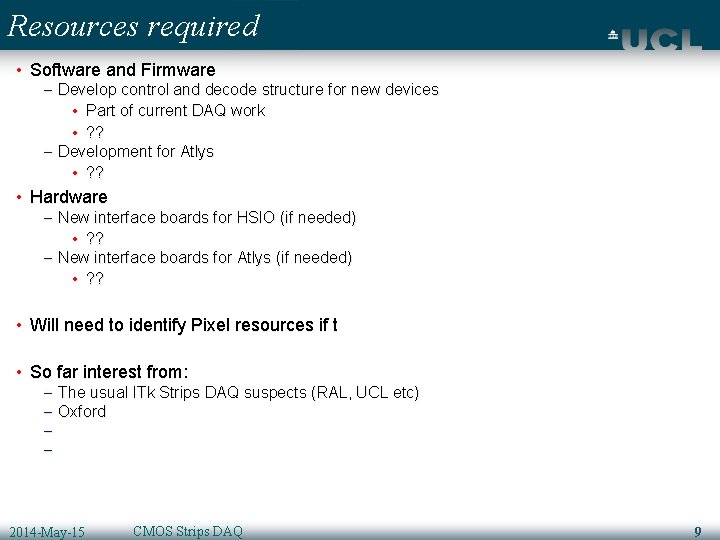

Resources required • Software and Firmware – Develop control and decode structure for new devices • Part of current DAQ work • ? ? – Development for Atlys • ? ? • Hardware – New interface boards for HSIO (if needed) • ? ? – New interface boards for Atlys (if needed) • ? ? • Will need to identify Pixel resources if t • So far interest from: – The usual ITk Strips DAQ suspects (RAL, UCL etc) – Oxford – – 2014 -May-15 CMOS Strips DAQ 9

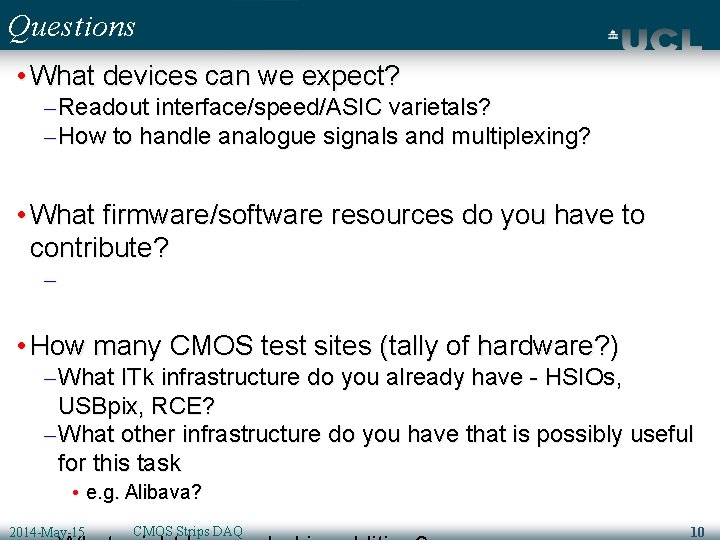

Questions • What devices can we expect? – Readout interface/speed/ASIC varietals? – How to handle analogue signals and multiplexing? • What firmware/software resources do you have to contribute? – • How many CMOS test sites (tally of hardware? ) – What ITk infrastructure do you already have - HSIOs, USBpix, RCE? – What other infrastructure do you have that is possibly useful for this task • e. g. Alibava? 2014 -May-15 CMOS Strips DAQ 10

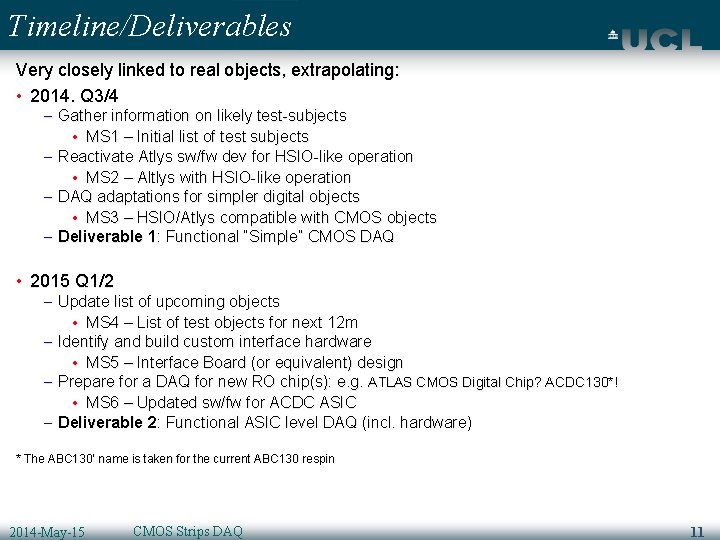

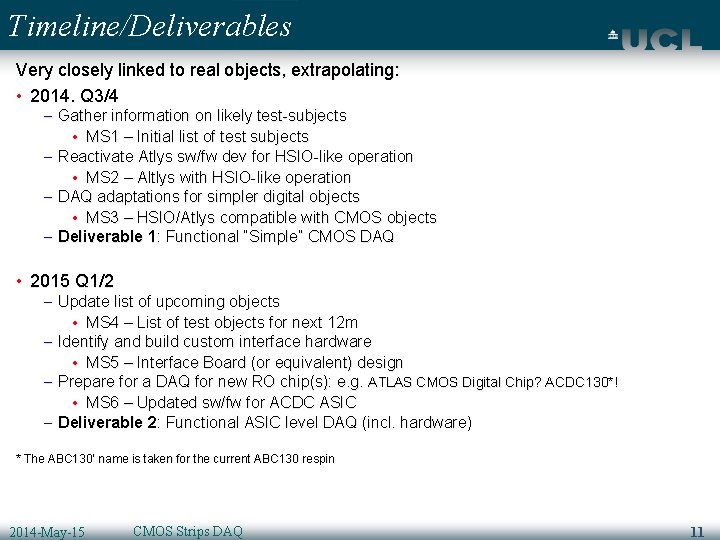

Timeline/Deliverables Very closely linked to real objects, extrapolating: • 2014. Q 3/4 – Gather information on likely test-subjects • MS 1 – Initial list of test subjects – Reactivate Atlys sw/fw dev for HSIO-like operation • MS 2 – Altlys with HSIO-like operation – DAQ adaptations for simpler digital objects • MS 3 – HSIO/Atlys compatible with CMOS objects – Deliverable 1: Functional “Simple” CMOS DAQ • 2015 Q 1/2 – Update list of upcoming objects • MS 4 – List of test objects for next 12 m – Identify and build custom interface hardware • MS 5 – Interface Board (or equivalent) design – Prepare for a DAQ for new RO chip(s): e. g. ATLAS CMOS Digital Chip? ACDC 130*! • MS 6 – Updated sw/fw for ACDC ASIC – Deliverable 2: Functional ASIC level DAQ (incl. hardware) * The ABC 130’ name is taken for the current ABC 130 respin 2014 -May-15 CMOS Strips DAQ 11