ITEC 352 Lecture 20 JVM Intro Review Questions

![Examples • Consider the following two usages of the load (ld) instruction: ld [x], Examples • Consider the following two usages of the load (ld) instruction: ld [x],](https://slidetodoc.com/presentation_image/30663857bd7f2cbd7ab52a23d33ced19/image-11.jpg)

![Assembly to machine code translation • Given an instruction: ld [x], %r 1 The Assembly to machine code translation • Given an instruction: ld [x], %r 1 The](https://slidetodoc.com/presentation_image/30663857bd7f2cbd7ab52a23d33ced19/image-14.jpg)

- Slides: 21

ITEC 352 Lecture 20 JVM Intro

Review • Questions? • Project due today • Activation record – How is it used? Functions + Assembly

Outline • Functions in assembly • Intro to JVM Functions + Assembly

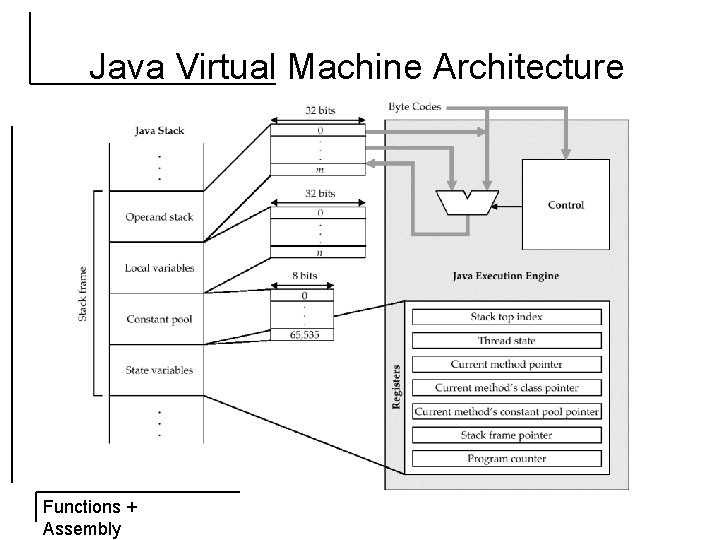

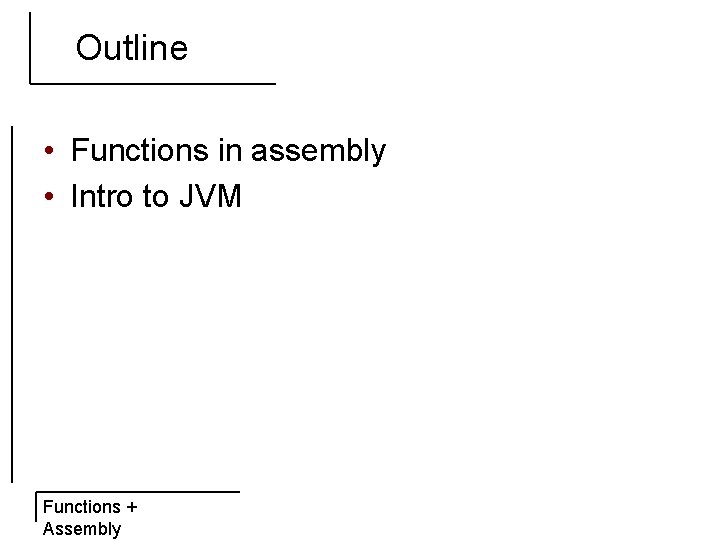

Java Virtual Machine Architecture Functions + Assembly

Functions + Assembly

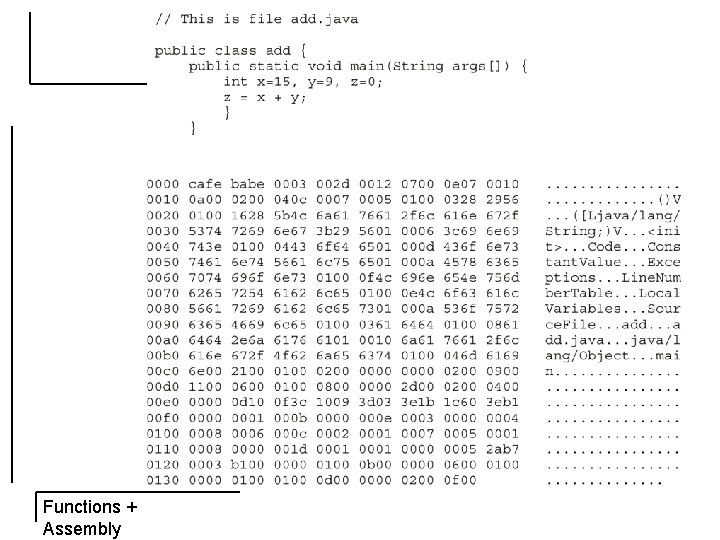

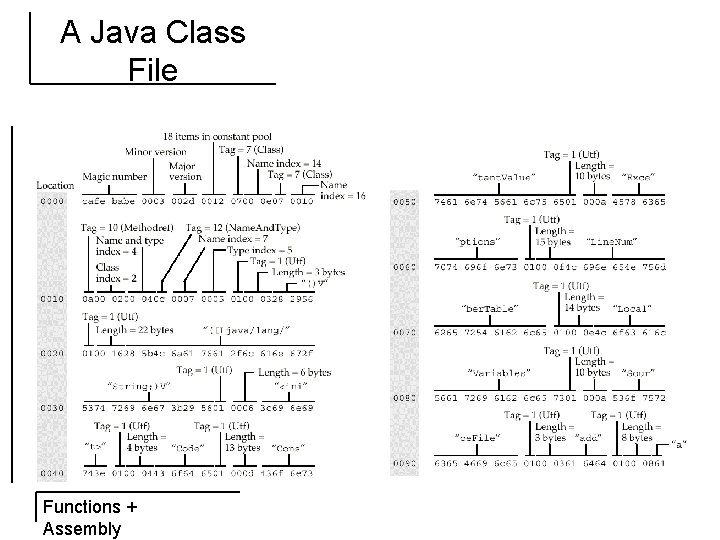

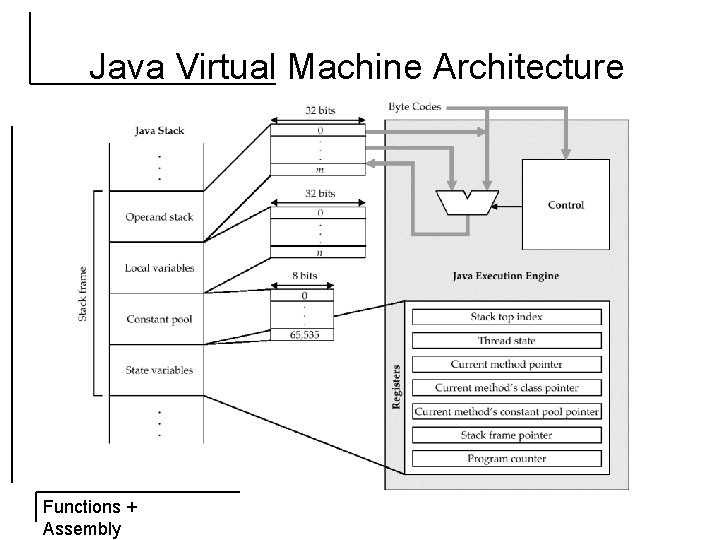

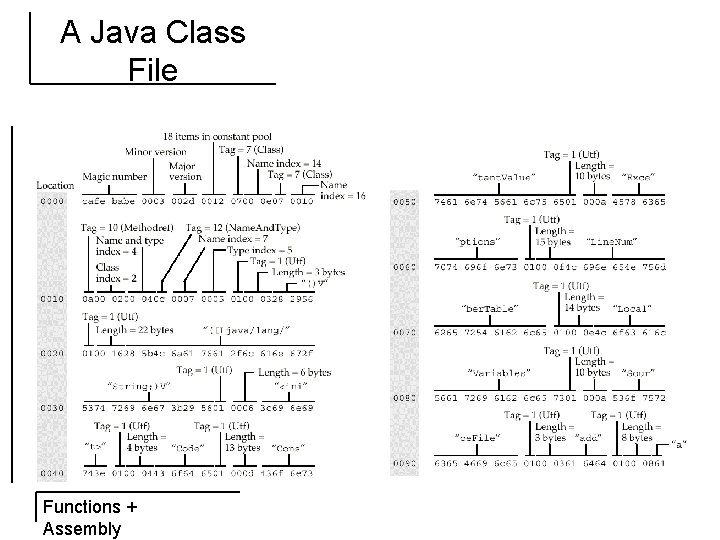

A Java Class File Functions + Assembly

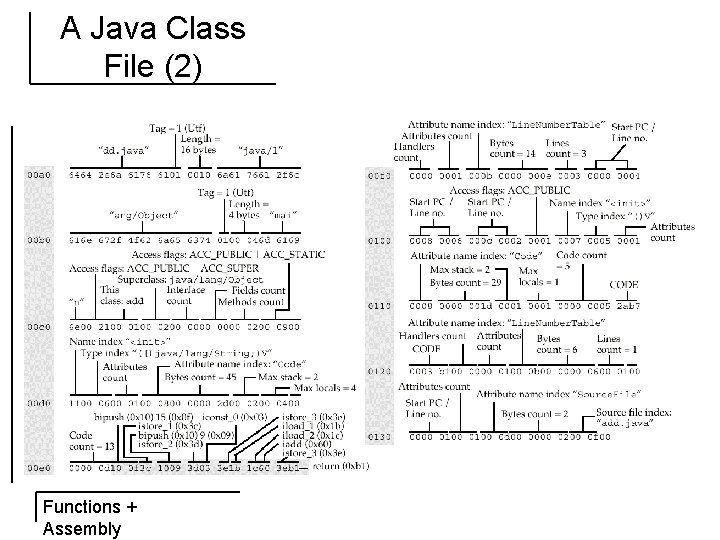

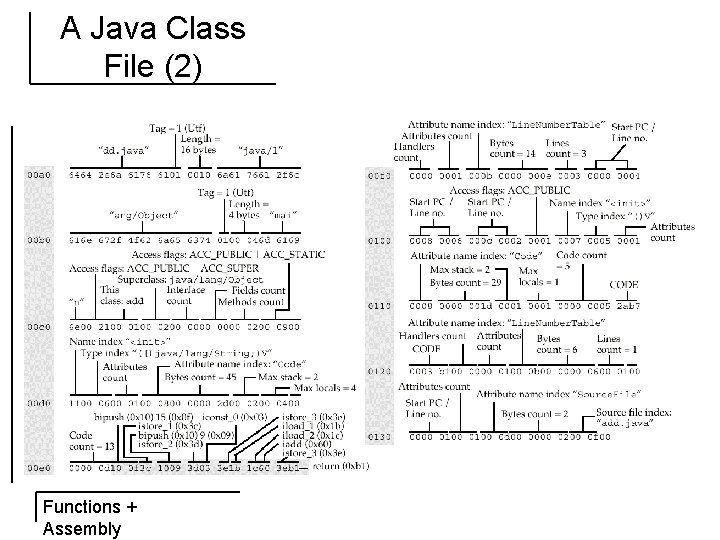

A Java Class File (2) Functions + Assembly

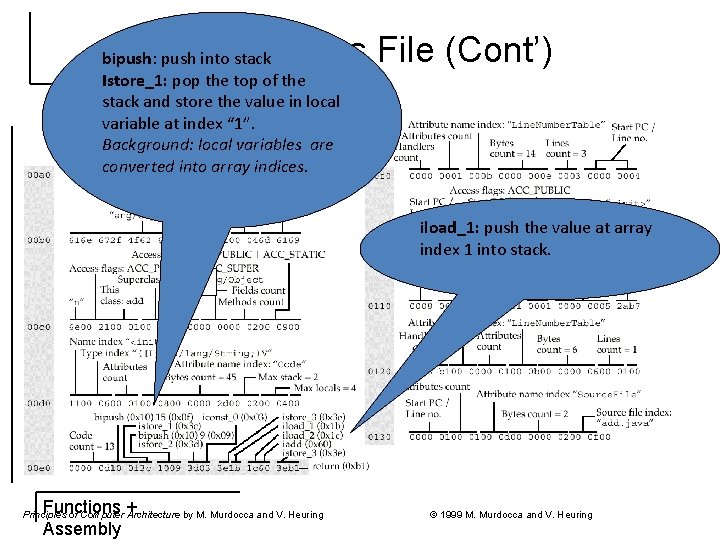

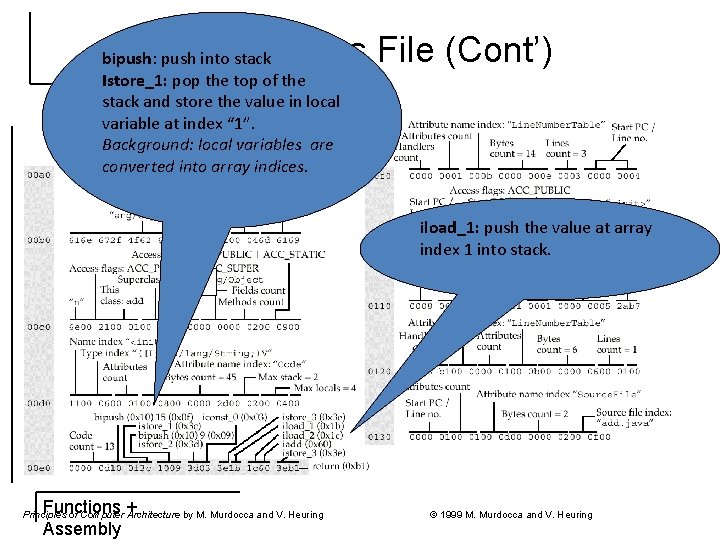

A Java Class File (Cont’) bipush: push into stack Istore_1: pop the top of the stack and store the value in local variable at index “ 1”. Background: local variables are converted into array indices. iload_1: push the value at array index 1 into stack. 0 Functions + Assembly Principles of Computer Architecture by M. Murdocca and V. Heuring © 1999 M. Murdocca and V. Heuring

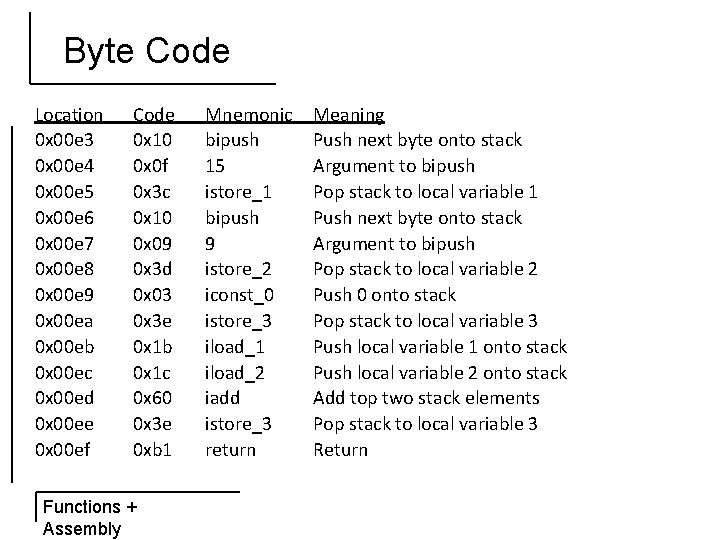

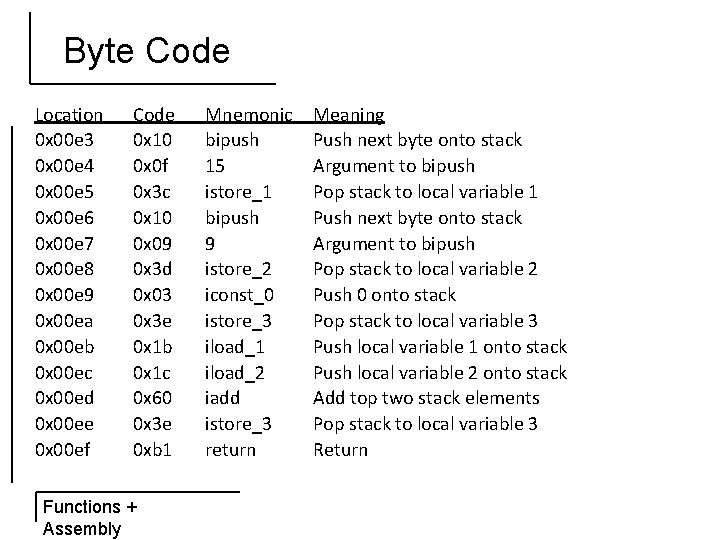

Byte Code Location 0 x 00 e 3 0 x 00 e 4 0 x 00 e 5 0 x 00 e 6 0 x 00 e 7 0 x 00 e 8 0 x 00 e 9 0 x 00 ea 0 x 00 eb 0 x 00 ec 0 x 00 ed 0 x 00 ee 0 x 00 ef Code 0 x 10 0 x 0 f 0 x 3 c 0 x 10 0 x 09 0 x 3 d 0 x 03 0 x 3 e 0 x 1 b 0 x 1 c 0 x 60 0 x 3 e 0 xb 1 Functions + Assembly Mnemonic bipush 15 istore_1 bipush 9 istore_2 iconst_0 istore_3 iload_1 iload_2 iadd istore_3 return Meaning Push next byte onto stack Argument to bipush Pop stack to local variable 1 Push next byte onto stack Argument to bipush Pop stack to local variable 2 Push 0 onto stack Pop stack to local variable 3 Push local variable 1 onto stack Push local variable 2 onto stack Add top two stack elements Pop stack to local variable 3 Return

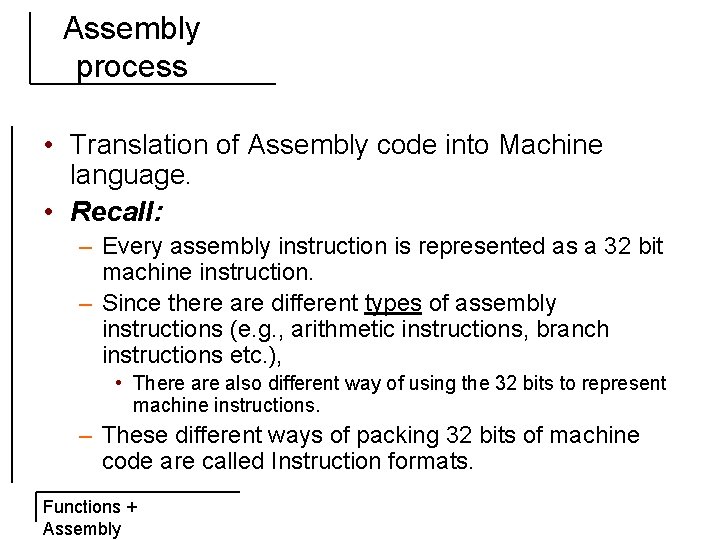

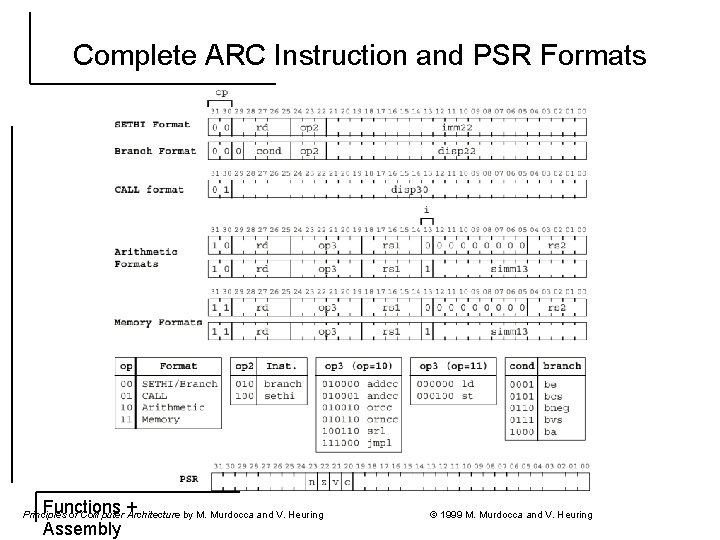

Assembly process • Translation of Assembly code into Machine language. • Recall: – Every assembly instruction is represented as a 32 bit machine instruction. – Since there are different types of assembly instructions (e. g. , arithmetic instructions, branch instructions etc. ), • There also different way of using the 32 bits to represent machine instructions. – These different ways of packing 32 bits of machine code are called Instruction formats. Functions + Assembly

![Examples Consider the following two usages of the load ld instruction ld x Examples • Consider the following two usages of the load (ld) instruction: ld [x],](https://slidetodoc.com/presentation_image/30663857bd7f2cbd7ab52a23d33ced19/image-11.jpg)

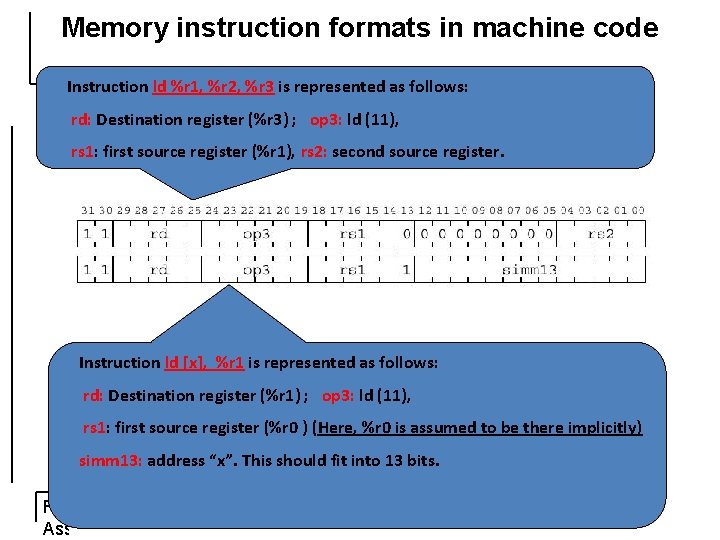

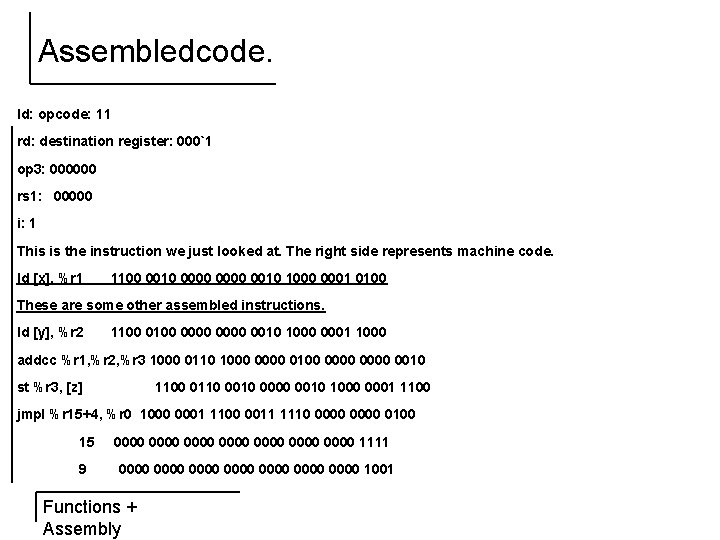

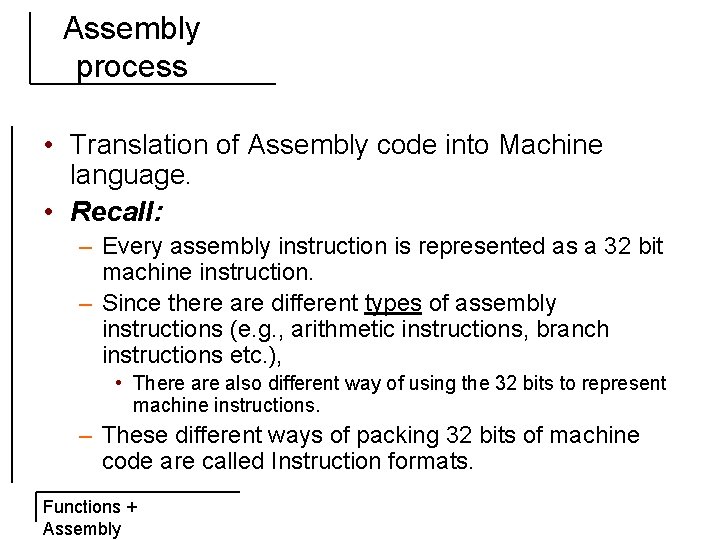

Examples • Consider the following two usages of the load (ld) instruction: ld [x], %r 1 Meaning: Load from a memory address specified as a constant value (in this case x) plus the contents of register %r 0 into register %r 1. ld %r 1, %r 2, %r 3 Meaning: Load from memory address obtained by adding the values of registers %r 1 and %r 2 into the register %r 3 In the first instruction we are using a constant value (memory address x). Whereas in the second we are using registers. Hence, there are two memory instruction formats in Machine code. (on next slide) Functions + Assembly

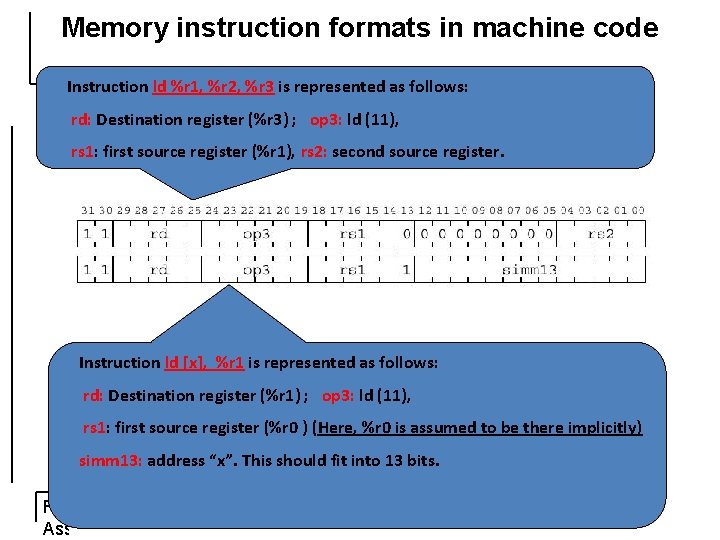

Memory instruction formats in machine code Instruction ld %r 1, %r 2, %r 3 is represented as follows: rd: Destination register (%r 3) ; op 3: ld (11), rs 1: first source register (%r 1), rs 2: second source register. Instruction ld [x], %r 1 is represented as follows: rd: Destination register (%r 1) ; op 3: ld (11), rs 1: first source register (%r 0 ) (Here, %r 0 is assumed to be there implicitly) simm 13: address “x”. This should fit into 13 bits. Functions + Assembly

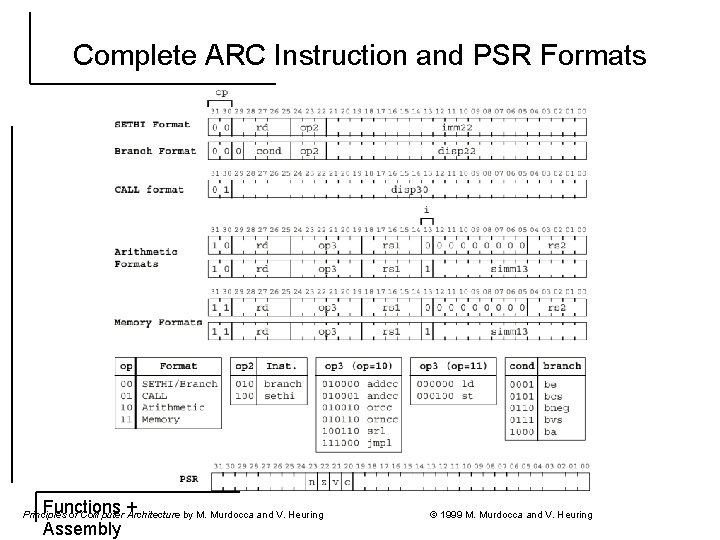

Complete ARC Instruction and PSR Formats Functions + Assembly Principles of Computer Architecture by M. Murdocca and V. Heuring © 1999 M. Murdocca and V. Heuring

![Assembly to machine code translation Given an instruction ld x r 1 The Assembly to machine code translation • Given an instruction: ld [x], %r 1 The](https://slidetodoc.com/presentation_image/30663857bd7f2cbd7ab52a23d33ced19/image-14.jpg)

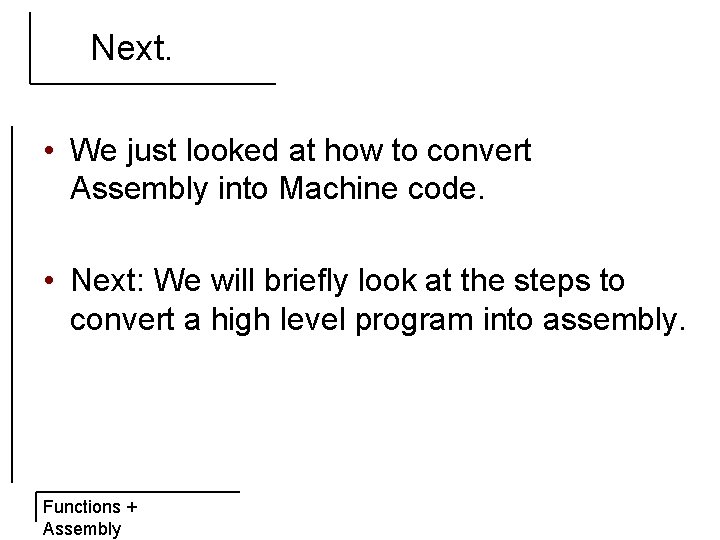

Assembly to machine code translation • Given an instruction: ld [x], %r 1 The assembly process pattern matches this instruction with machine formats to obtain the machine code. E. g. , After it sees the instruction, it maps it to the second memory format (the one with simm 13). It then converts the instruction as follows: ld op 3: 11 (op 3 = 11) [x] simm 13: Memory address x. If. org 2048, then x = 2048. In binary = 0100000 %r 0 rs 1 ( source register) (address = 00000) 5 bits to address a register. %r 1 rd (destination register) (address = 00001) Other fields: In the previous slide, notice that there is an “i” field to distinguish between the two memory formats. Here, i = 1.

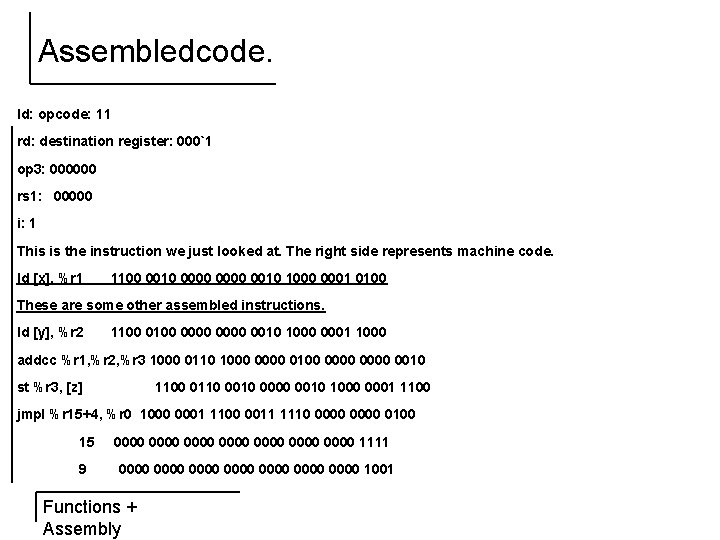

Assembledcode. ld: opcode: 11 rd: destination register: 000`1 op 3: 000000 rs 1: 00000 i: 1 This is the instruction we just looked at. The right side represents machine code. ld [x], %r 1 1100 0010 0000 0010 1000 0001 0100 These are some other assembled instructions. ld [y], %r 2 1100 0000 0010 1000 0001 1000 addcc %r 1, %r 2, %r 3 1000 0110 1000 0100 0000 0010 st %r 3, [z] 1100 0110 0000 0010 1000 0001 1100 jmpl %r 15+4, %r 0 1000 0001 1100 0011 1110 0000 0100 15 9 0000 0000 1111 0000 0000 1001 Functions + Assembly

Next. • We just looked at how to convert Assembly into Machine code. • Next: We will briefly look at the steps to convert a high level program into assembly. Functions + Assembly

Summary so far … • We looked at – Stages of a compiler (briefly) – Assembly instructions – Translating assembly into machine code … • Next: speeding up processing … Functions + Assembly

CPU Performanc e • E. g. , will a 4. 1 Ghz CPU be faster than a 2. 0 Ghz CPU? – So is the CPU cycle time a measure of performance? • How about amount of cache? • Anything else? • Next: performance due to pipelining. Functions + Assembly

Pipelining Speeding up the computation process Complex and Reduced Instruction Sets: Complex Instruction Set Computer (CISC) Reduced Instruction Set Computer (RISC) Next: the differences? Functions + Assembly

CISC Vs. RISC • A long time back when memory costed – The focus of most computer architects • (E. g. , Intel and Motorola) • Support fewer instructions that performed more complicated computations. • E. g. , addld [a], [b], [c] would be a complex instruction that replaced: ld [a], %r 1 ld [b], %r 2 addcc %r 1, %r 2, %r 3 st %r 3, [c] Why? Complex instructions Shorter programs Smaller memory needed. However, memory became cheaper. So architects started thinking about techniques to use more memory that would speed up computations. Functions + Assembly

Review • JVM + Bytecode Functions + Assembly