IRAM Vision Microprocessor DRAM on a single chip

- Slides: 8

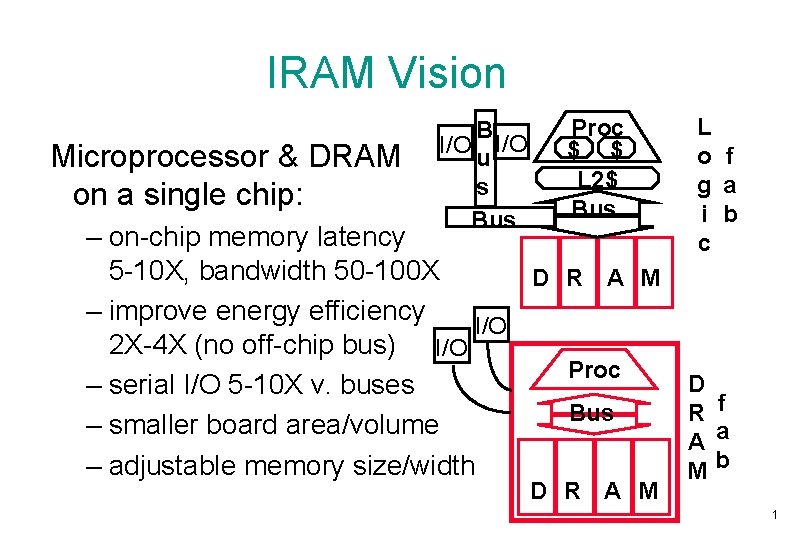

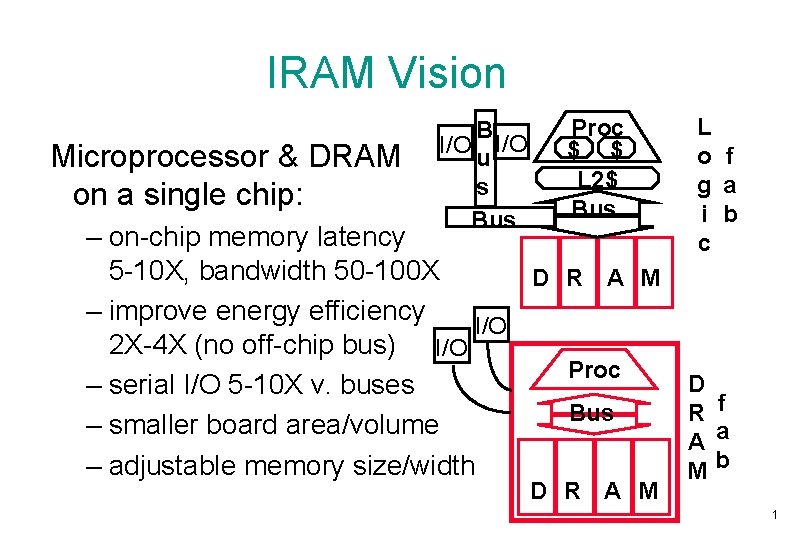

IRAM Vision Microprocessor & DRAM on a single chip: B I/O u s Bus Proc $ $ L 2$ Bus L o f g a i b c – on-chip memory latency 5 -10 X, bandwidth 50 -100 X D R A M – improve energy efficiency I/O 2 X-4 X (no off-chip bus) I/O Proc D – serial I/O 5 -10 X v. buses Bus R f – smaller board area/volume A a – adjustable memory size/width Mb D R A M 1

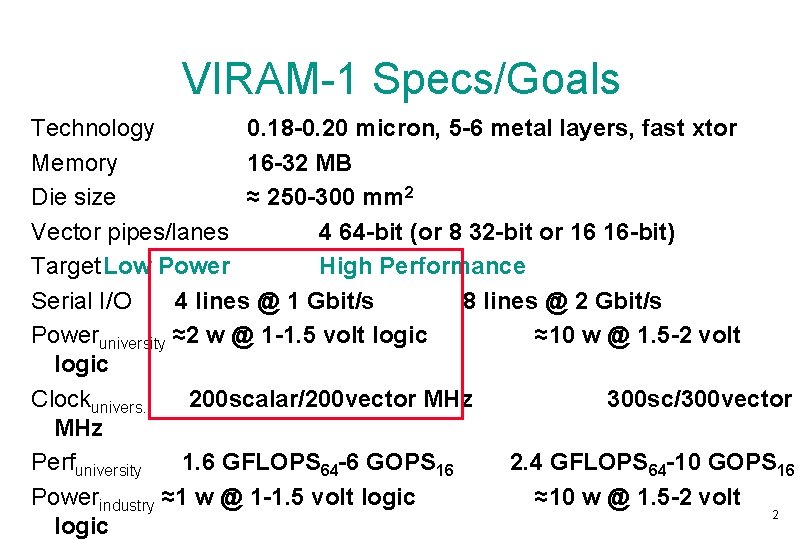

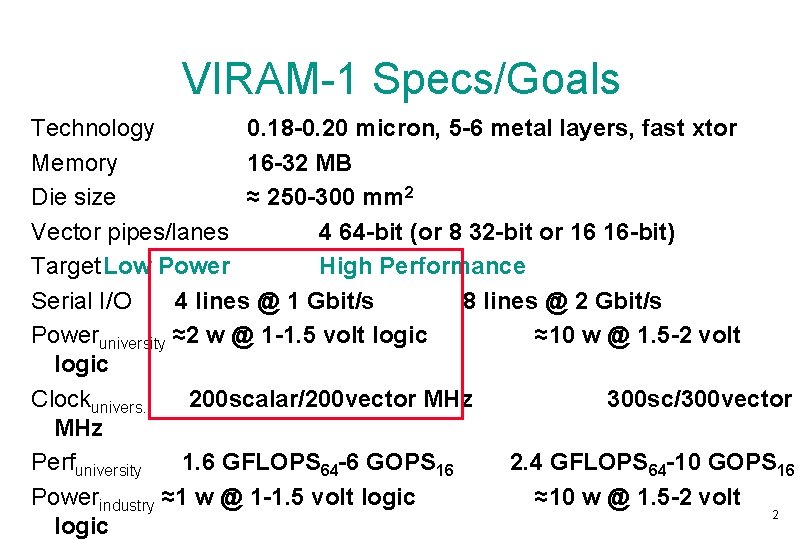

VIRAM-1 Specs/Goals Technology 0. 18 -0. 20 micron, 5 -6 metal layers, fast xtor Memory 16 -32 MB Die size ≈ 250 -300 mm 2 Vector pipes/lanes 4 64 -bit (or 8 32 -bit or 16 16 -bit) Target Low Power High Performance Serial I/O 4 lines @ 1 Gbit/s 8 lines @ 2 Gbit/s Poweruniversity ≈2 w @ 1 -1. 5 volt logic ≈10 w @ 1. 5 -2 volt logic Clockunivers. 200 scalar/200 vector MHz 300 sc/300 vector MHz Perfuniversity 1. 6 GFLOPS 64 -6 GOPS 16 2. 4 GFLOPS 64 -10 GOPS 16 Powerindustry ≈1 w @ 1 -1. 5 volt logic ≈10 w @ 1. 5 -2 volt 2 logic

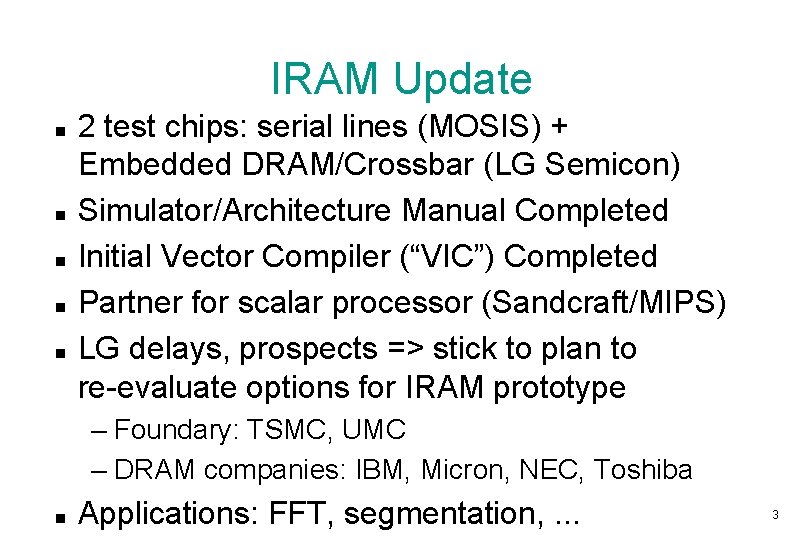

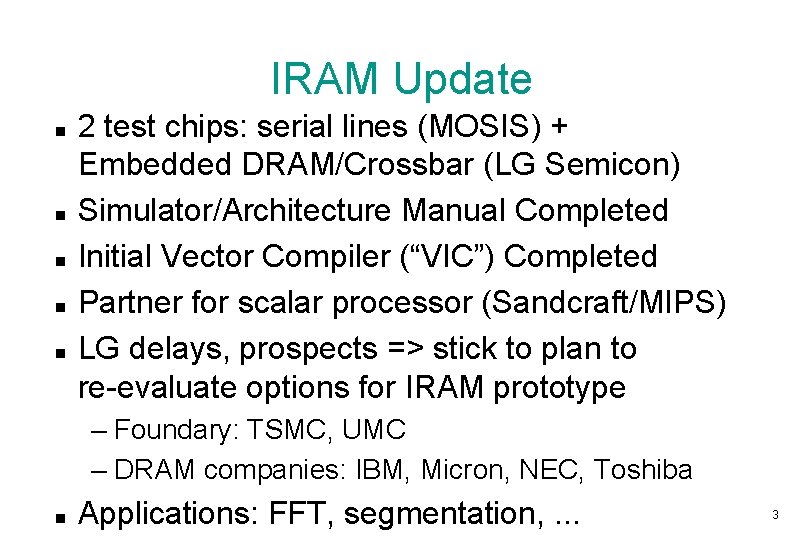

IRAM Update 2 test chips: serial lines (MOSIS) + Embedded DRAM/Crossbar (LG Semicon) Simulator/Architecture Manual Completed Initial Vector Compiler (“VIC”) Completed Partner for scalar processor (Sandcraft/MIPS) LG delays, prospects => stick to plan to re-evaluate options for IRAM prototype – Foundary: TSMC, UMC – DRAM companies: IBM, Micron, NEC, Toshiba Applications: FFT, segmentation, . . . 3

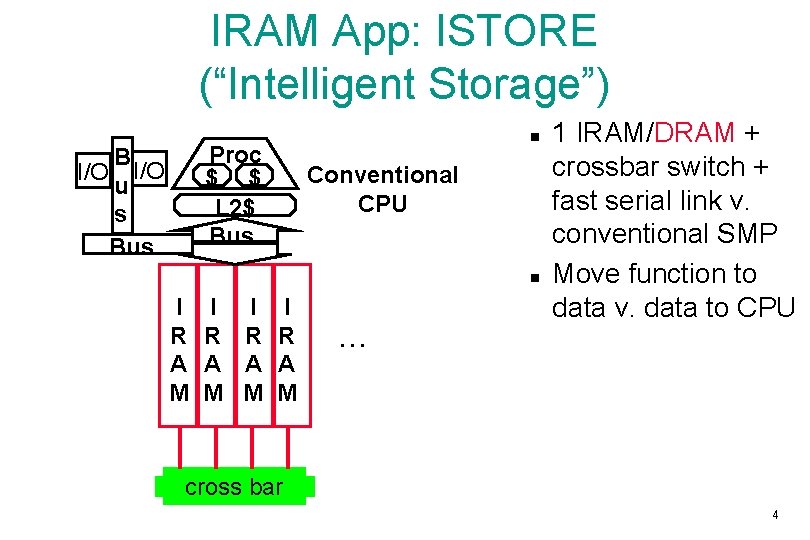

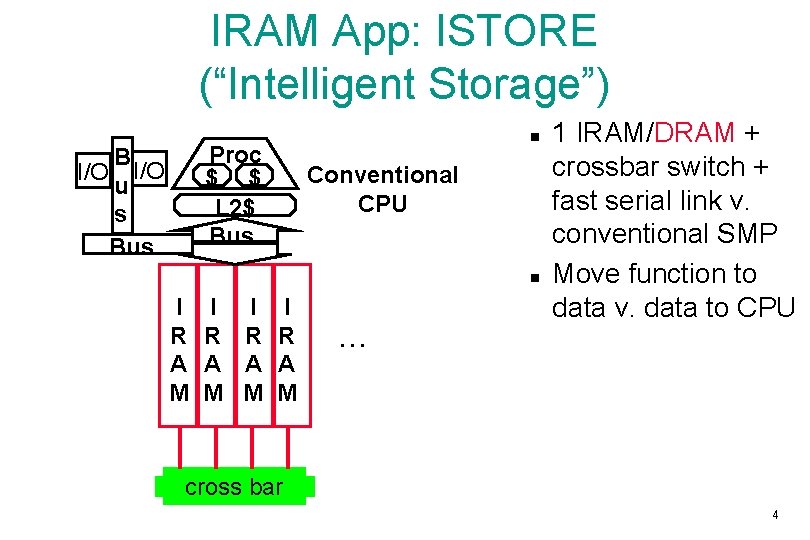

IRAM App: ISTORE (“Intelligent Storage”) Proc $ $ L 2$ Bus B I/O u s Bus Conventional CPU I R A M I I I R R R A A A M M M … 1 IRAM/DRAM + crossbar switch + fast serial link v. conventional SMP Move function to data v. data to CPU cross bar 4

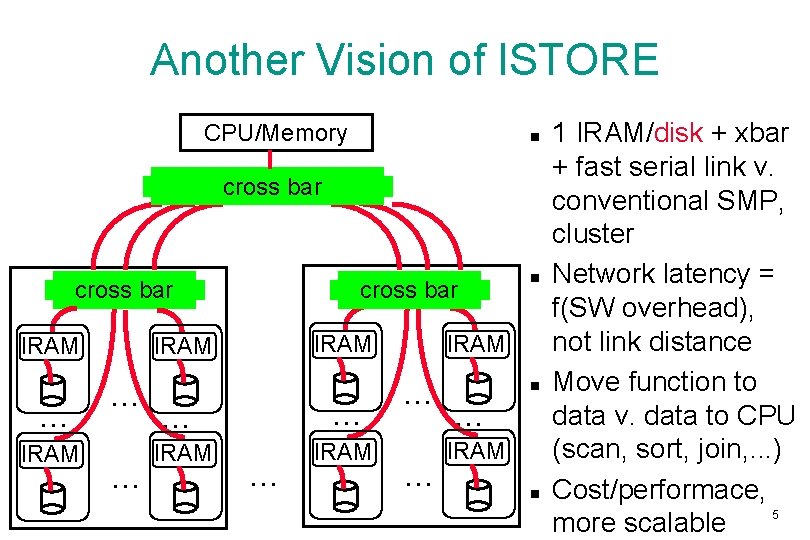

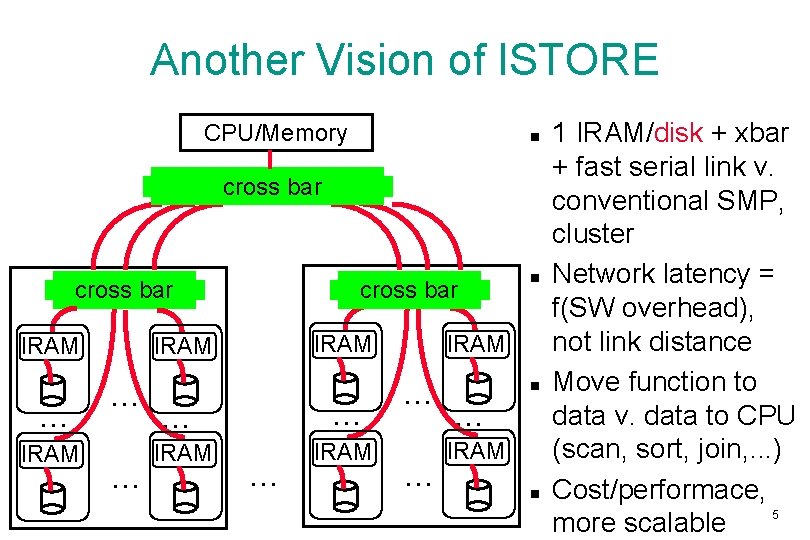

Another Vision of ISTORE CPU/Memory cross bar IRAM … IRAM cross bar IRAM … … IRAM … … … IRAM 1 IRAM/disk + xbar + fast serial link v. conventional SMP, cluster Network latency = f(SW overhead), not link distance Move function to data v. data to CPU (scan, sort, join, . . . ) Cost/performace, 5 more scalable

ISTORE Update Build prototypes to gain experience, develop software before IRAM chips arrive – Replace with IRAM chips once available ISTORE-0: 2 Sandcraft Development boards + Fast Ethernet + Real-time OS (Vx. Works/QNX) ISTORE-1: “Intelligent SIMM” module based on Mitsubishi M 32 RXD (DRAM interface+CPU) 6

IRAM/ISTORE Schedule IRAM ISTORE/OS Compiler 7

1998 IRAM/ISTORE Presentations – Micro. Design Resources Dinner Meeting, 1/8/98 – Embedded Memory Workshop, Japan, 3/15/98 – Stanford Computer Science Colloquim, 5/6/98 – University of Virginia Distinguished Lecture, 5/19/98 – SIGMOD 98 Keynote Address, 6/3/98 Articles – “New Processor Paradigm: V-IRAM”, Microprocessor Report, 3/9/98, 17 -19. – “A perfect match. ” New Scientist, 4/18/98, 36 -39. – "Professor's Idea for Speedy Chip Could Be More 8 Than Academic , " Wall Street Journal, 8/28/98, B 1, B 4.