IP for Xilinx Academy Training Core Solutions Products

- Slides: 20

IP for Xilinx Academy Training Core Solutions: Products: Xilinx Academy 1 http: //www. xilinx. com/products/logicore. htm http: //www. xilinx. com/products/logicore/tblcores. htm

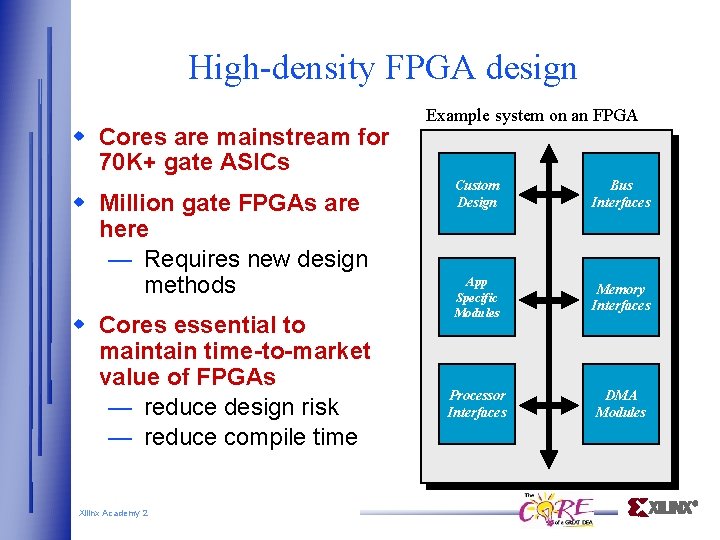

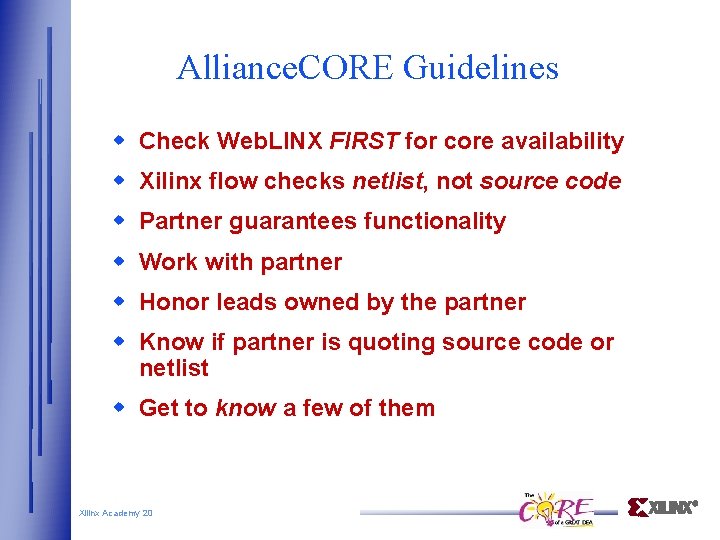

High-density FPGA design Cores are mainstream for 70 K+ gate ASICs Million gate FPGAs are here — Requires new design methods Cores essential to maintain time-to-market value of FPGAs — reduce design risk — reduce compile time Xilinx Academy 2 Example system on an FPGA Custom Design Bus Interfaces App Specific Modules Memory Interfaces Processor Interfaces DMA Modules

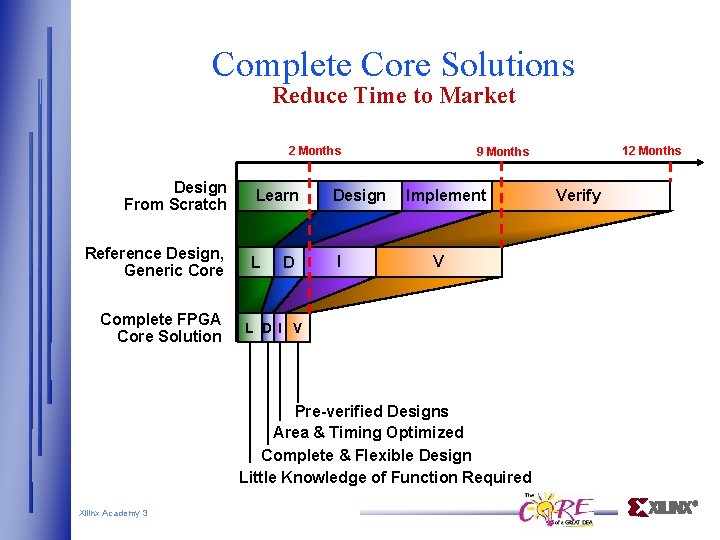

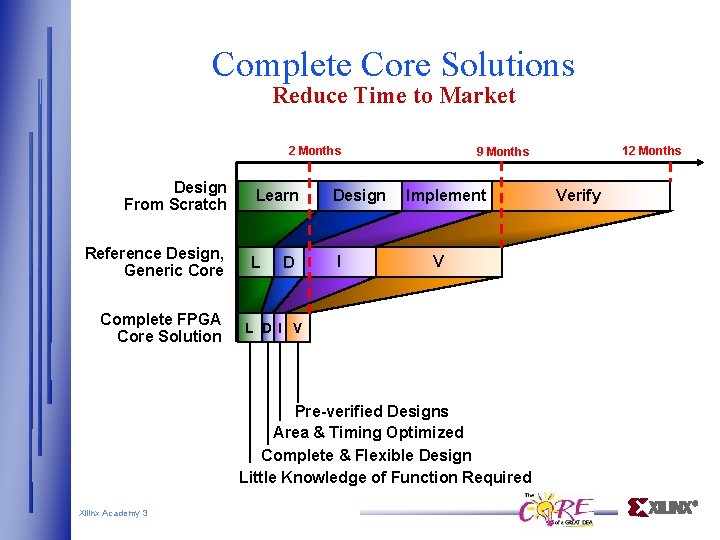

Complete Core Solutions Reduce Time to Market 2 Months Design From Scratch Reference Design, Generic Core Complete FPGA Core Solution Learn L D Design I Implement V L DI V Pre-verified Designs Area & Timing Optimized Complete & Flexible Design Little Knowledge of Function Required Xilinx Academy 3 12 Months 9 Months Verify

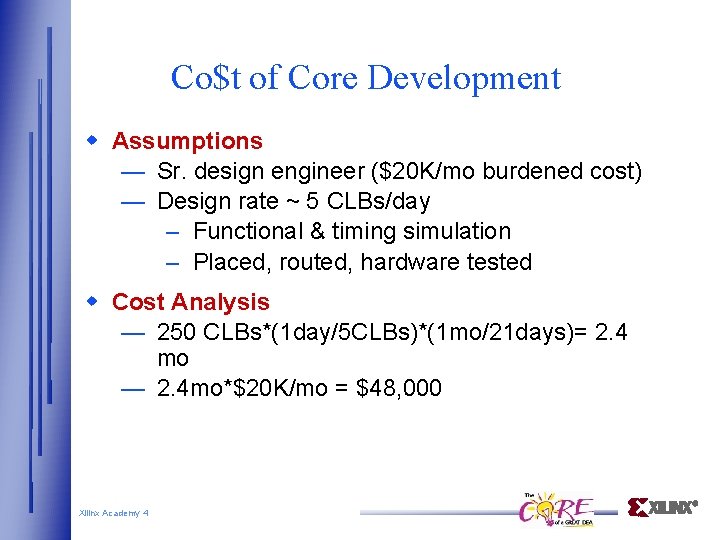

Co$t of Core Development Assumptions — Sr. design engineer ($20 K/mo burdened cost) — Design rate ~ 5 CLBs/day – Functional & timing simulation – Placed, routed, hardware tested Cost Analysis — 250 CLBs*(1 day/5 CLBs)*(1 mo/21 days)= 2. 4 mo — 2. 4 mo*$20 K/mo = $48, 000 Xilinx Academy 4

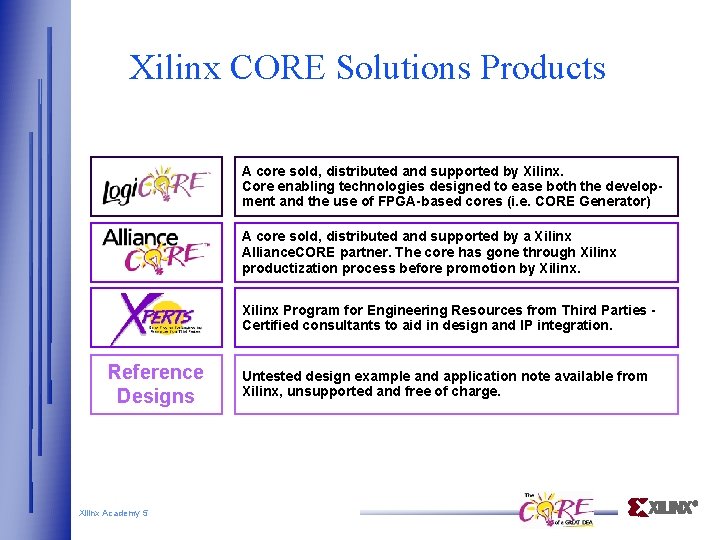

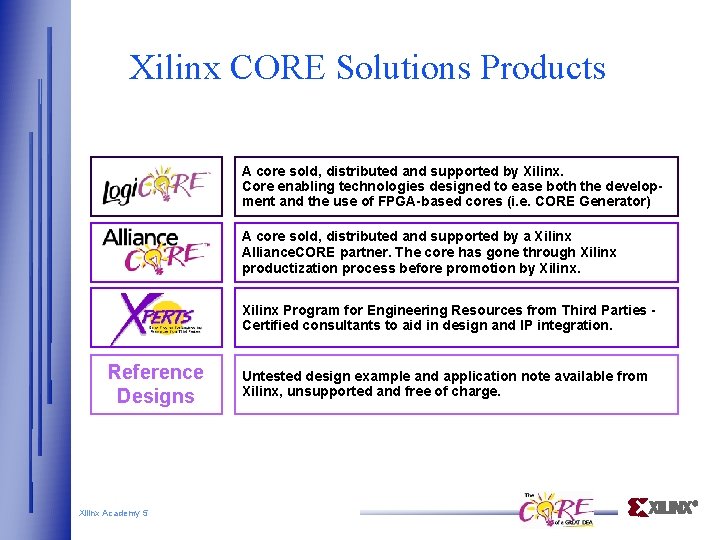

Xilinx CORE Solutions Products A core sold, distributed and supported by Xilinx. Core enabling technologies designed to ease both the development and the use of FPGA-based cores (i. e. CORE Generator) A core sold, distributed and supported by a Xilinx Alliance. CORE partner. The core has gone through Xilinx productization process before promotion by Xilinx Program for Engineering Resources from Third Parties Certified consultants to aid in design and IP integration. Reference Designs Xilinx Academy 5 Untested design example and application note available from Xilinx, unsupported and free of charge.

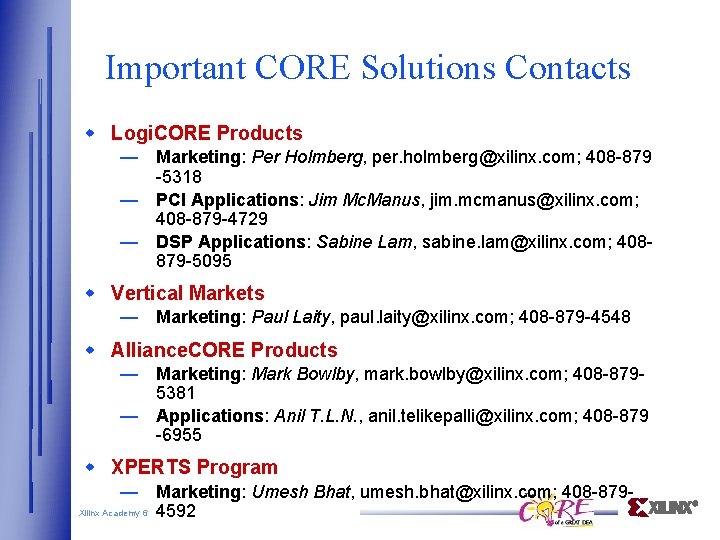

Important CORE Solutions Contacts Logi. CORE Products — Marketing: Per Holmberg, per. holmberg@xilinx. com; 408 -879 -5318 — PCI Applications: Jim Mc. Manus, jim. mcmanus@xilinx. com; 408 -879 -4729 — DSP Applications: Sabine Lam, sabine. lam@xilinx. com; 408879 -5095 Vertical Markets — Marketing: Paul Laity, paul. laity@xilinx. com; 408 -879 -4548 Alliance. CORE Products — Marketing: Mark Bowlby, mark. bowlby@xilinx. com; 408 -8795381 — Applications: Anil T. L. N. , anil. telikepalli@xilinx. com; 408 -879 -6955 XPERTS Program — Marketing: Umesh Bhat, umesh. bhat@xilinx. com; 408 -879 Xilinx Academy 6 4592

Partnerships for Complete Programmable Logic Solutions Program Info: http: //www. xilinx. com/products/logicore/alliance/tblpart. htm Xilinx Academy 7

An Alliance. CORE $uccess! Reed Solomon Customer: Wavtrace — Existing Altera user - not Xilinx PARTNER: — Looking at LSI Logic for Reed Solomon Core — Altera and Xilinx both offered ISS core — Under pricing pressure, Altera offered own core The Result - Xilinx and ISS Win! — Communication was key — Complete solution = Hard. Wire + ISS cores — 8 software seats + 20 sockets — 4 month process What Can We Learn? — Win the core, win the war — ISS solution better than LSI’s Xilinx Academy 8

Partners* Merged with… G V & Associates *As of November, 1998 Xilinx Academy 9

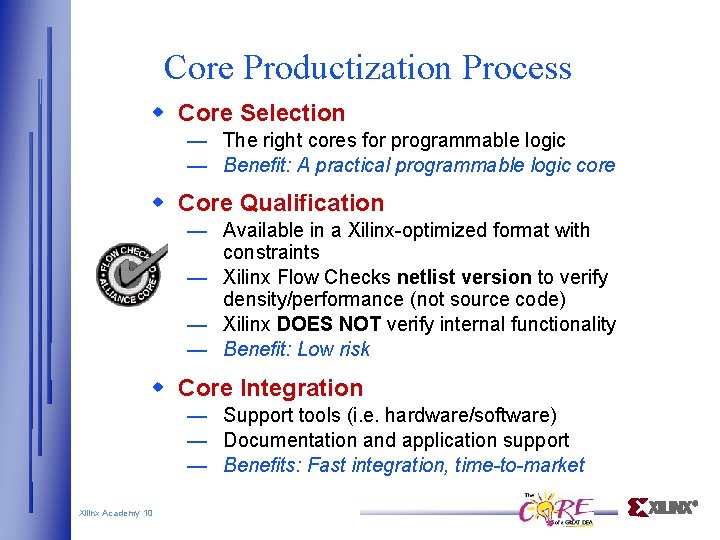

Core Productization Process Core Selection — The right cores for programmable logic — Benefit: A practical programmable logic core Core Qualification — Available in a Xilinx-optimized format with constraints — Xilinx Flow Checks netlist version to verify density/performance (not source code) — Xilinx DOES NOT verify internal functionality — Benefit: Low risk Core Integration — Support tools (i. e. hardware/software) — Documentation and application support — Benefits: Fast integration, time-to-market Xilinx Academy 10

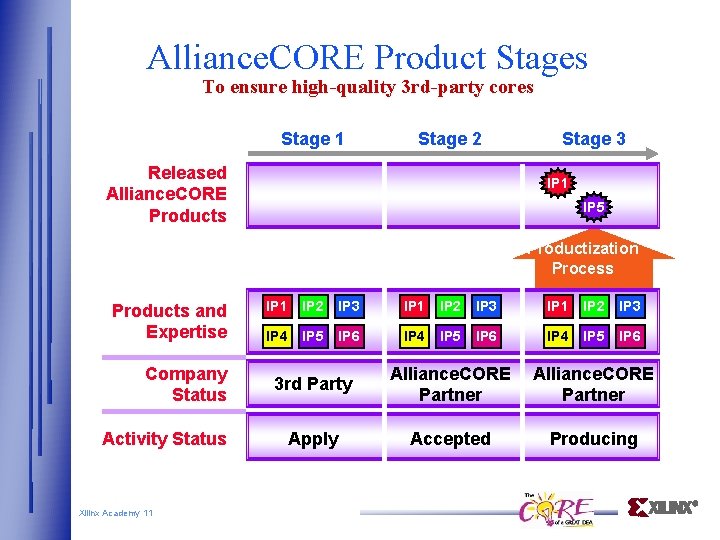

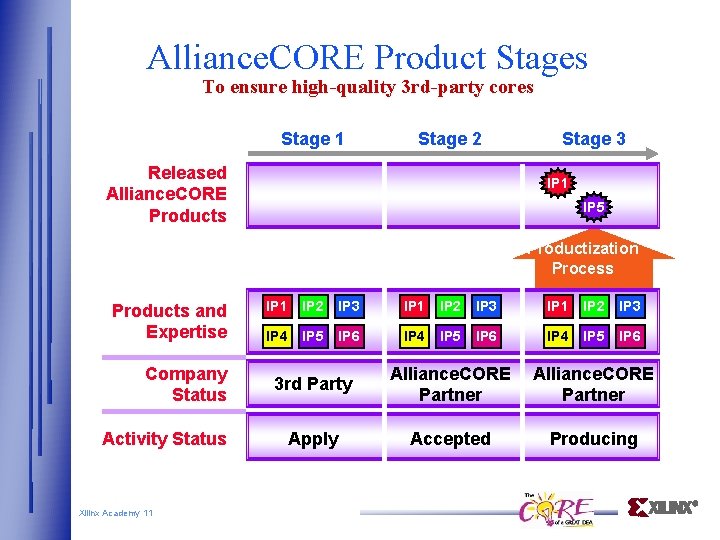

Alliance. CORE Product Stages To ensure high-quality 3 rd-party cores Stage 1 Stage 2 Released Alliance. CORE Products Stage 3 IP 1 IP 5 Productization Process Products and Expertise Company Status Activity Status Xilinx Academy 11 IP 2 IP 3 IP 4 IP 5 IP 6 IP 4 IP 5 IP 6 3 rd Party Alliance. CORE Partner Apply Accepted Producing

Basics of Using the Program Core Partnerships are Relatively New — It’s natural to have questions The Time to Start is Now — We sell time-to-market — Big devices need (many) cores — Cannot continue to, without 3 rdparty cores — Customers are interested We Learn to use this Together — Field, factory and partners Xilinx Academy 12

First Sales Scenario You and customer identify a need 1. Download Data Sheet from Web. LINX www. xilinx. com/products/logicore/tblpart. htm — Call factory if needed 2. Contact Partner — Identify yourself as Xilinx representative — Describe opportunity — Decide if there is a fit 3. Set up a Conference Call 4. Stay Involved and Communicate Xilinx Academy 13

Second Sales Scenario Customer has already contacted partner Insert Yourself into the Process — Find out the status Introduce Yourself to Partner — Begin and maintain communication Stay Involved and Communicate Xilinx Academy 14

Lead Registration Guidelines Rules for Partners and Xilinx Whoever Brings Lead First (Xilinx or Partner), Owns It — First requested vendor is co-owner Only offer requested solution(s) — Get other party(s) involved — Tell if customer later asks for competing solution — Open game if original request not vendorspecific Cooperate and Communicate — Help us learn as we go Xilinx Academy 15

Acquiring Alliance. CORE Products Purchase made directly with Partner Xilinx Netlist version $ < Source Code $ — Netlist restricted for use in Xilinx — Always ask which version the partner is quoting Partner guarantees functionality Licensing varies — Single use — Multi-use site license Xilinx Academy 16

Recommendations Analyze the needs of your customer base Find partners with expertise in those areas Get to know two or three proactively — Call or visit them — Which one are in your area? — Start a relationship — 25+ partners is too many Xilinx Academy 17

Virtex Status Many Partners are trained on Virtex — Partner-specific training occurred December 1998 — Ongoing training of others Virtex is becoming a de-facto IP platform All NEW partner core development is on Virtex — Always ASK partner about Virtex availability of a core — Current 4 K cores being converted Xilinx Academy 18

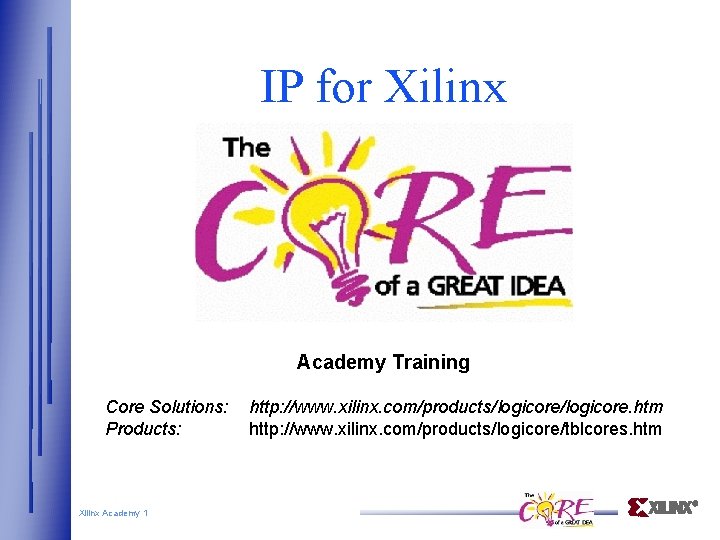

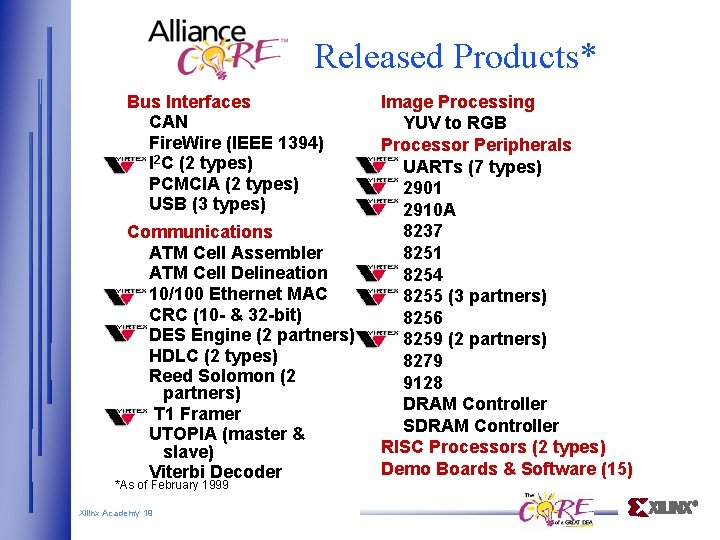

Released Products* Bus Interfaces CAN Fire. Wire (IEEE 1394) I 2 C (2 types) PCMCIA (2 types) USB (3 types) Communications ATM Cell Assembler ATM Cell Delineation 10/100 Ethernet MAC CRC (10 - & 32 -bit) DES Engine (2 partners) HDLC (2 types) Reed Solomon (2 partners) T 1 Framer UTOPIA (master & slave) Viterbi Decoder *As of February 1999 Xilinx Academy 19 Image Processing YUV to RGB Processor Peripherals UARTs (7 types) 2901 2910 A 8237 8251 8254 8255 (3 partners) 8256 8259 (2 partners) 8279 9128 DRAM Controller SDRAM Controller RISC Processors (2 types) Demo Boards & Software (15)

Alliance. CORE Guidelines Check Web. LINX FIRST for core availability Xilinx flow checks netlist, not source code Partner guarantees functionality Work with partner Honor leads owned by the partner Know if partner is quoting source code or netlist Get to know a few of them Xilinx Academy 20