IO TECHNIQUES INTERFACING Most topics discussed experiments assigned

- Slides: 30

I/O TECHNIQUES INTERFACING Most topics discussed & experiments assigned in lab 2/16 IO Interfacing. 1

Overview I/O hardware ports, buses, devices, controllers I/O Software Interrupt Handlers, Device Driver, Device Independent Software, User Space I/O Software Three I/O mechanisms Polling, interrupt and DMAs 2/16 IO Interfacing. 2

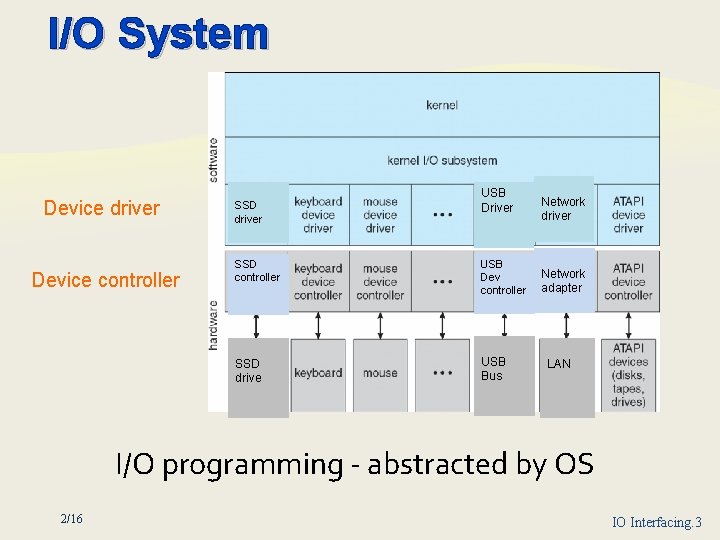

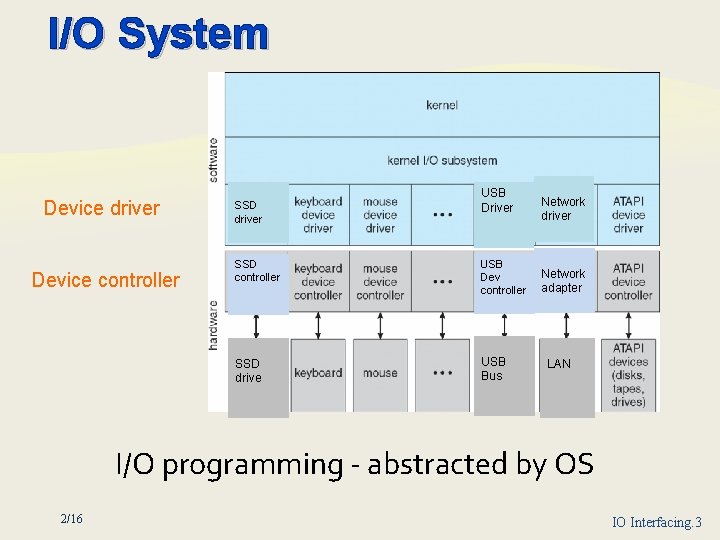

I/O System Device driver Device controller SSD driver USB Driver SSD controller USB Dev controller SSD drive USB Bus Network driver Network adapter LAN I/O programming abstracted by OS 2/16 IO Interfacing. 3

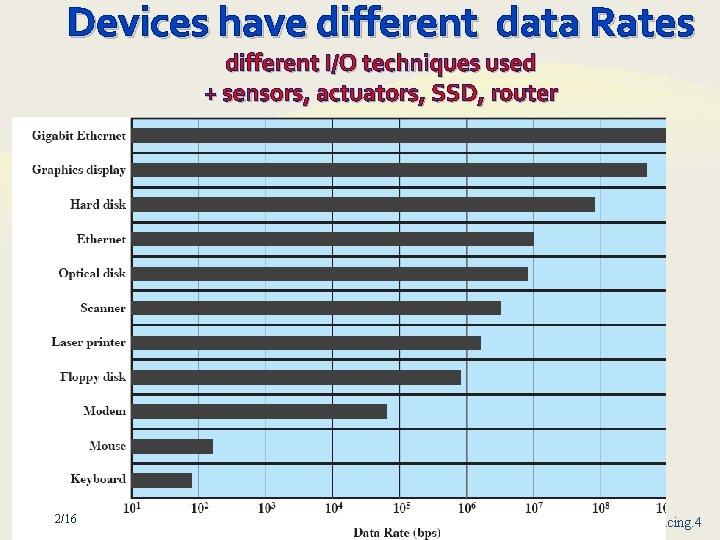

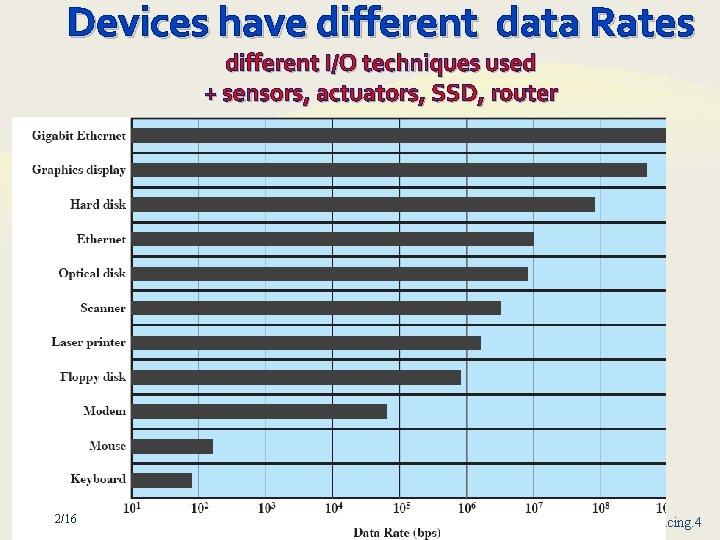

Devices have different data Rates different I/O techniques used + sensors, actuators, SSD, router 2/16 IO Interfacing. 4

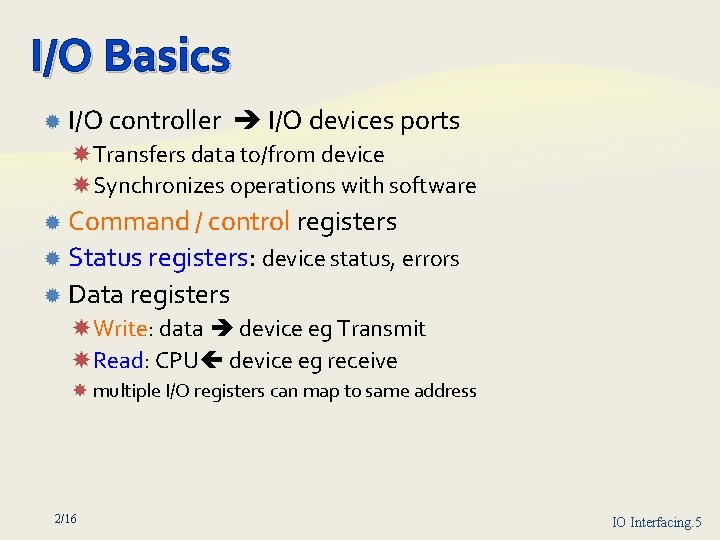

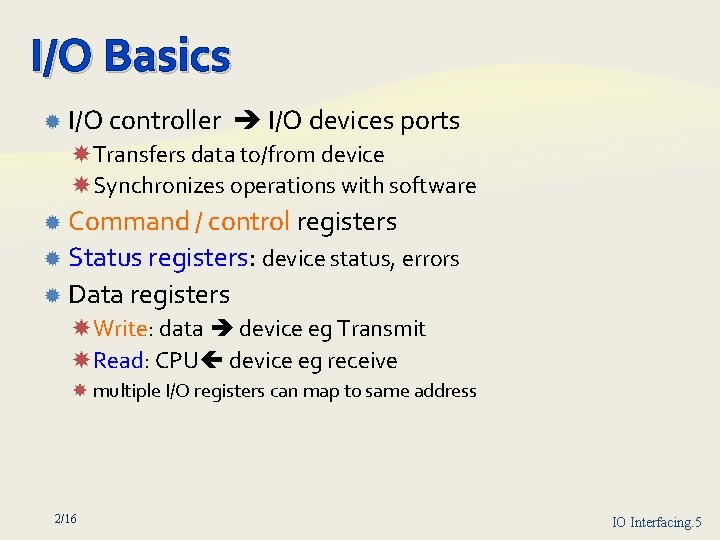

I/O Basics I/O controller I/O devices ports Transfers data to/from device Synchronizes operations with software Command / control registers Status registers: device status, errors Data registers Write: data device eg Transmit Read: CPU device eg receive multiple I/O registers can map to same address 2/16 IO Interfacing. 5

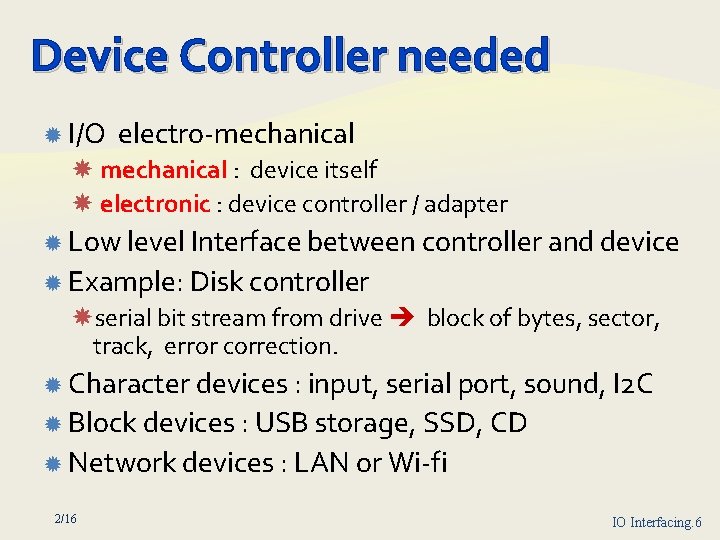

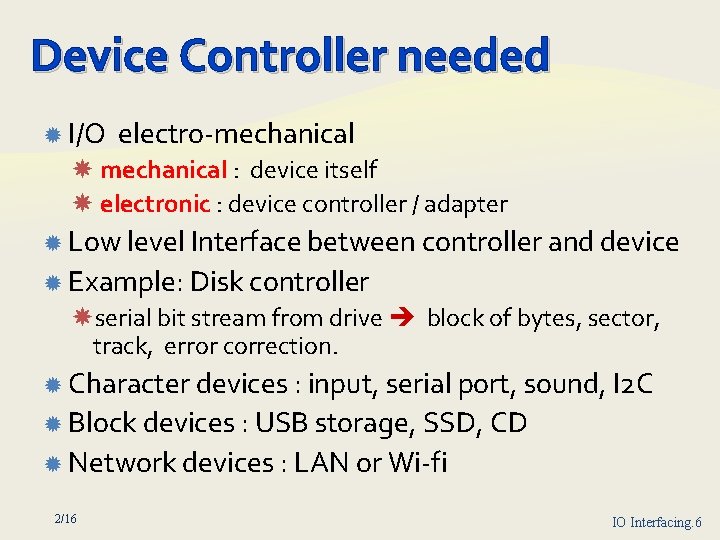

Device Controller needed I/O electro mechanical : device itself electronic : device controller / adapter Low level Interface between controller and device Example: Disk controller serial bit stream from drive block of bytes, sector, track, error correction. Character devices : input, serial port, sound, I 2 C Block devices : USB storage, SSD, CD Network devices : LAN or Wi fi 2/16 IO Interfacing. 6

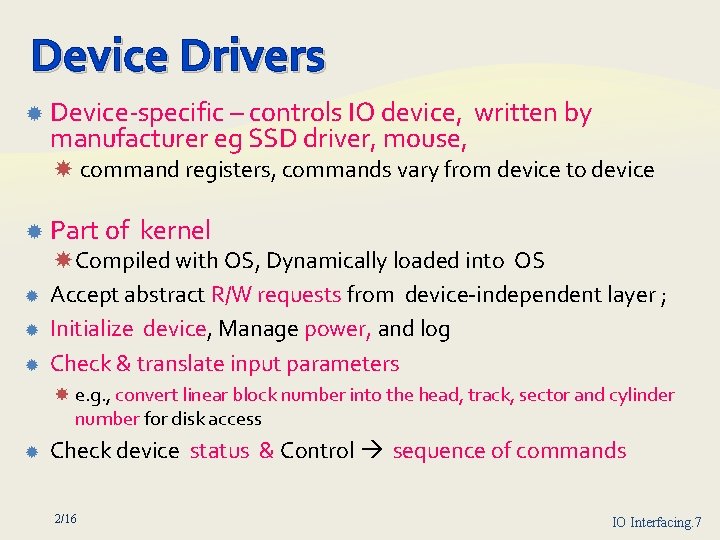

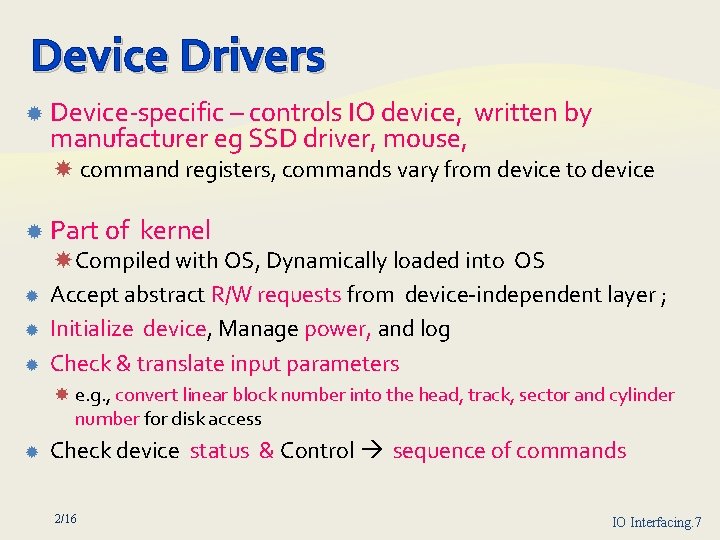

Device Drivers Device specific – controls IO device, written by manufacturer eg SSD driver, mouse, command registers, commands vary from device to device Part of kernel Compiled with OS, Dynamically loaded into OS Accept abstract R/W requests from device independent layer ; Initialize device, Manage power, and log Check & translate input parameters e. g. , convert linear block number into the head, track, sector and cylinder number for disk access Check device status & Control sequence of commands 2/16 IO Interfacing. 7

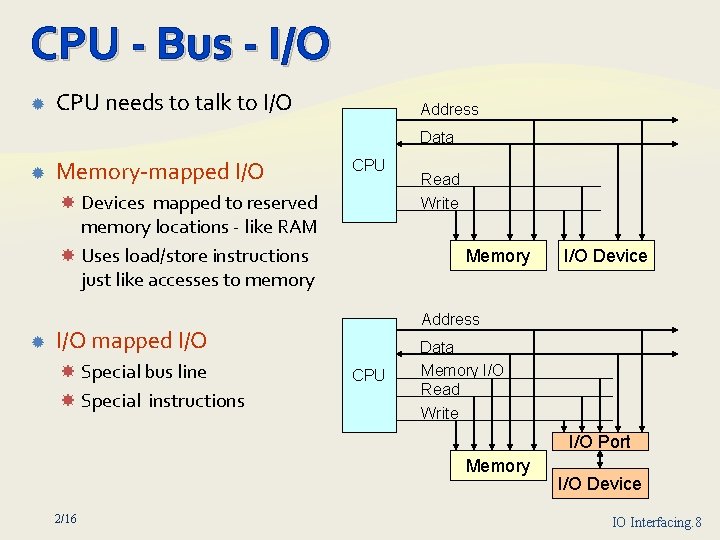

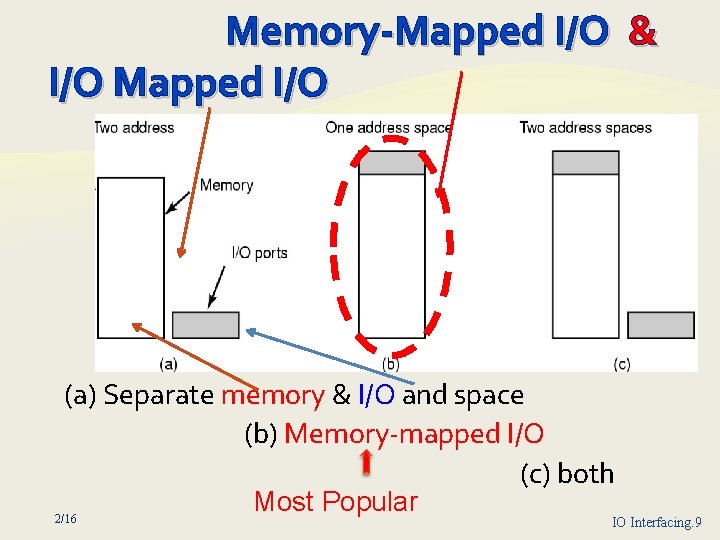

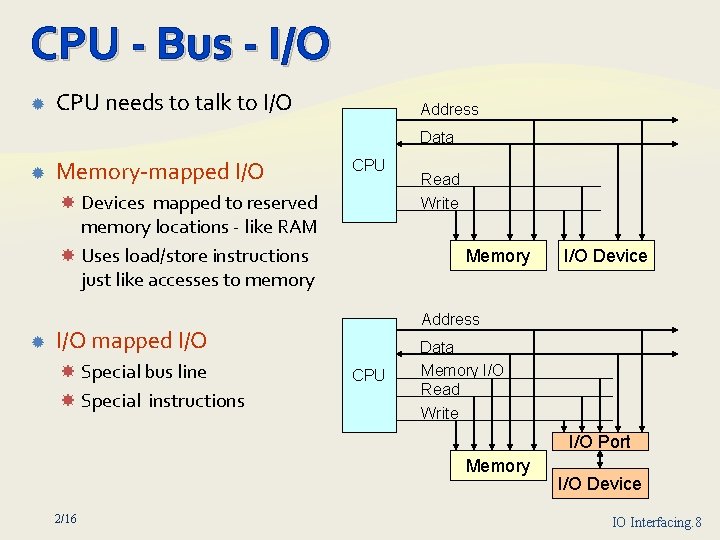

CPU Bus I/O CPU needs to talk to I/O Address Data Memory mapped I/O CPU Devices mapped to reserved memory locations like RAM Uses load/store instructions just like accesses to memory Memory I/O Device Address I/O mapped I/O Special bus line Special instructions Read Write CPU Data Memory I/O Read Write I/O Port Memory 2/16 I/O Device IO Interfacing. 8

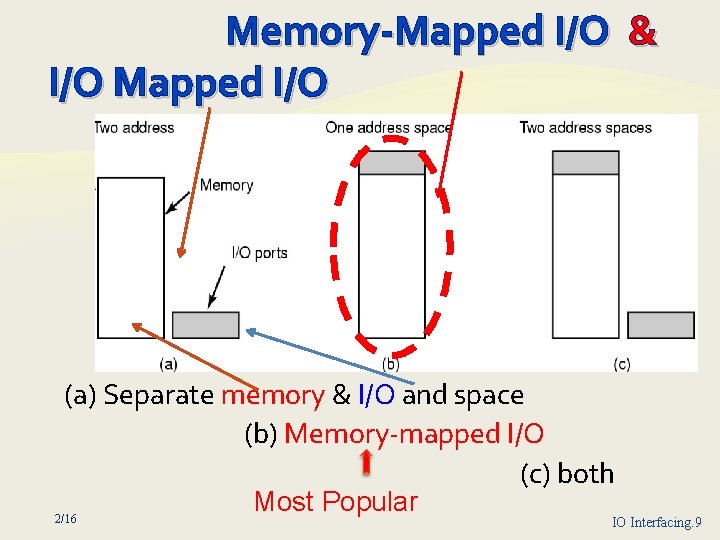

Memory Mapped I/O & I/O Mapped I/O (a) Separate memory & I/O and space (b) Memory mapped I/O (c) both 2/16 Most Popular IO Interfacing. 9

I/O Register Mapping summary Memory mapped I/O Device Registers addressed similar to memory OS only accessible to kernel OR I/O instructions Separate instructions to access I/O kernel mode Example: x 86 2/16 IO Interfacing. 10

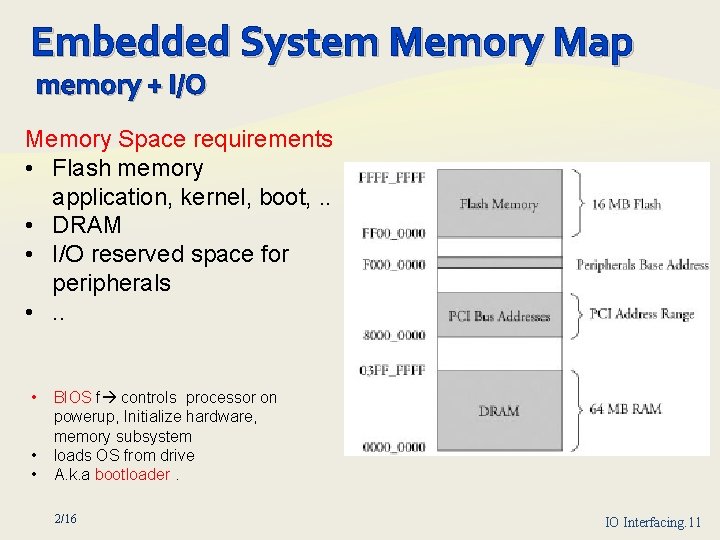

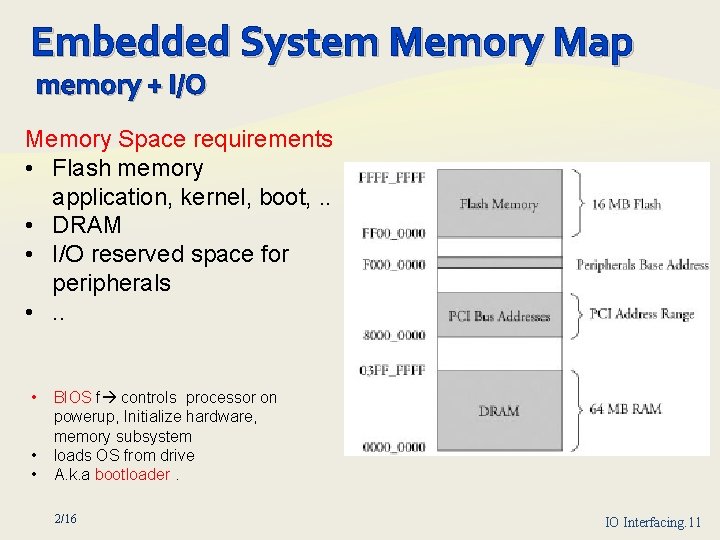

Embedded System Memory Map memory + I/O Memory Space requirements • Flash memory application, kernel, boot, . . • DRAM • I/O reserved space for peripherals • . . • • • BIOS f controls processor on powerup, Initialize hardware, memory subsystem loads OS from drive A. k. a bootloader. 2/16 IO Interfacing. 11

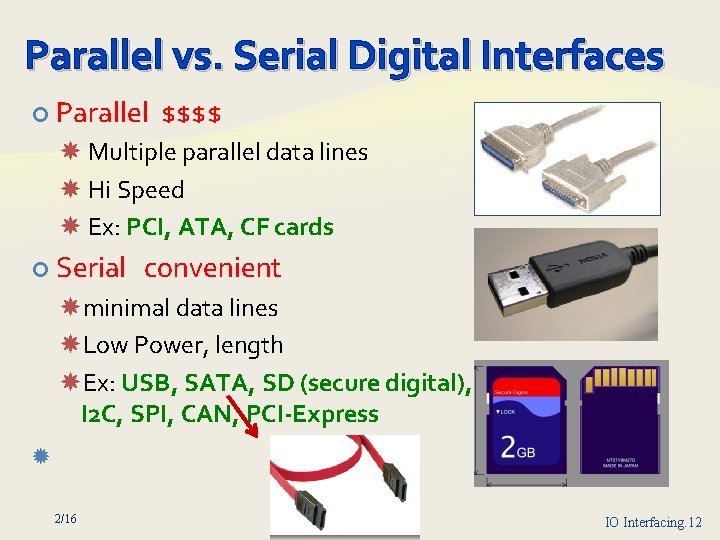

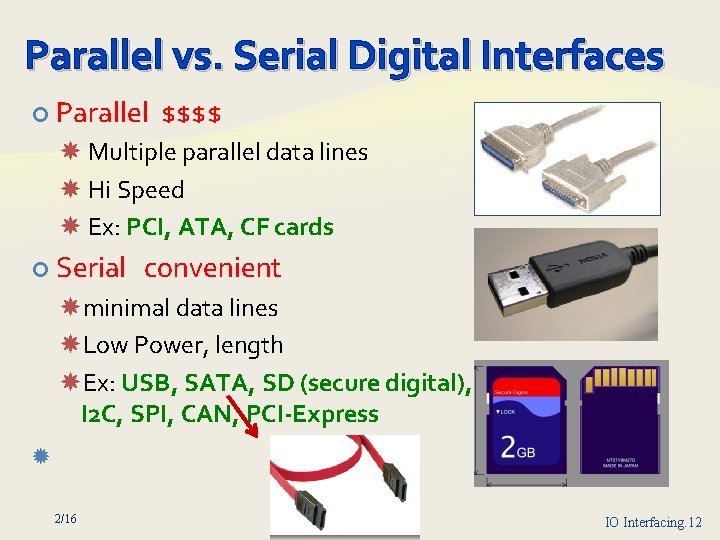

Parallel vs. Serial Digital Interfaces ¢ Parallel $$$$ Multiple parallel data lines Hi Speed Ex: PCI, ATA, CF cards ¢ Serial convenient minimal data lines Low Power, length Ex: USB, SATA, SD (secure digital), I 2 C, SPI, CAN, PCI Express 2/16 IO Interfacing. 12

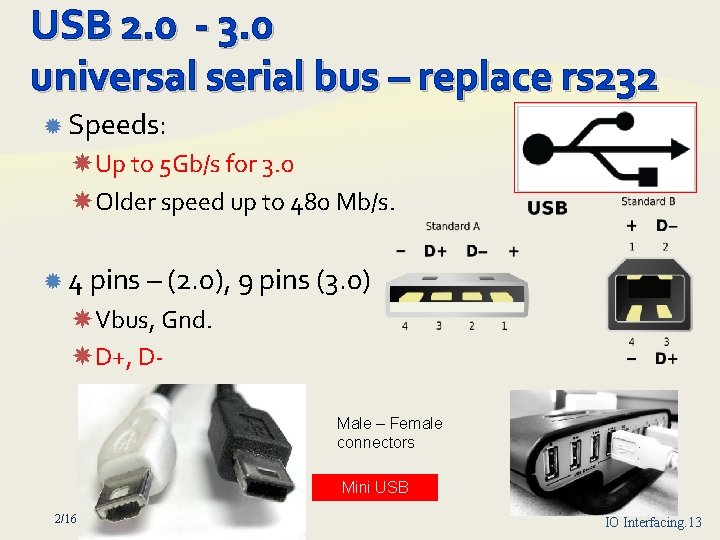

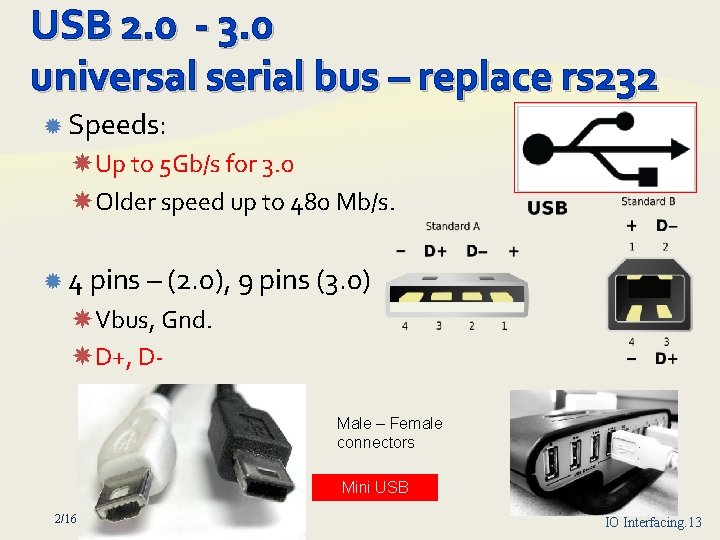

USB 2. 0 3. 0 universal serial bus – replace rs 232 Speeds: Up to 5 Gb/s for 3. 0 Older speed up to 480 Mb/s. 4 pins – (2. 0), 9 pins (3. 0) Vbus, Gnd. D+, D Male – Female connectors Mini USB 2/16 IO Interfacing. 13

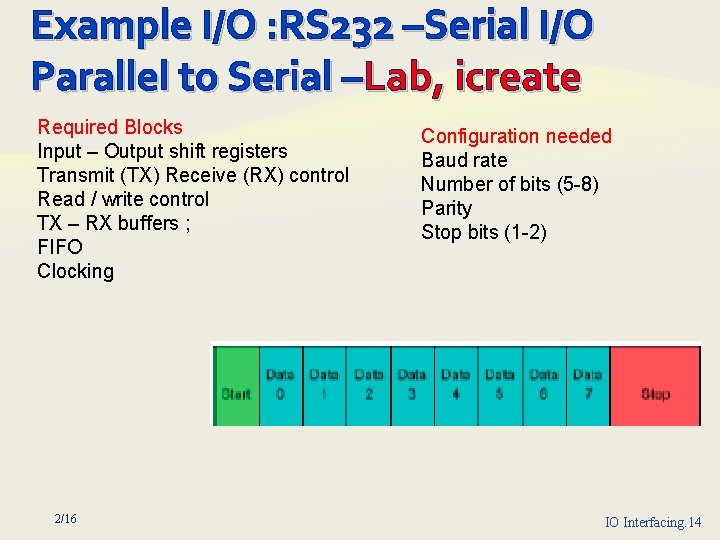

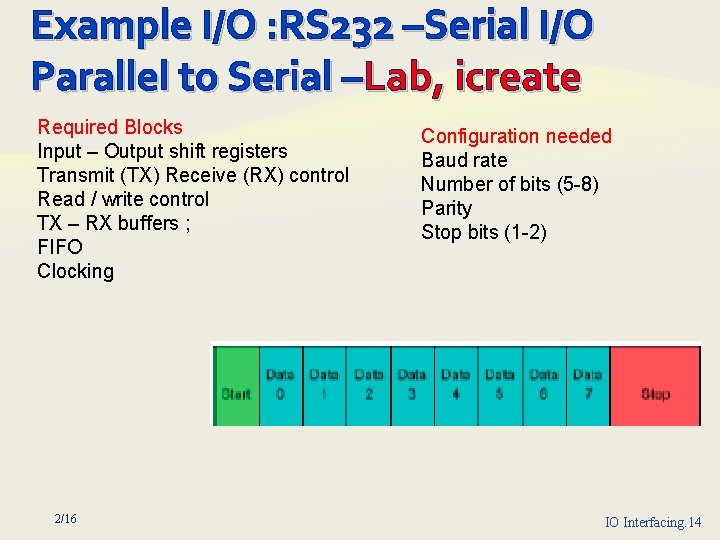

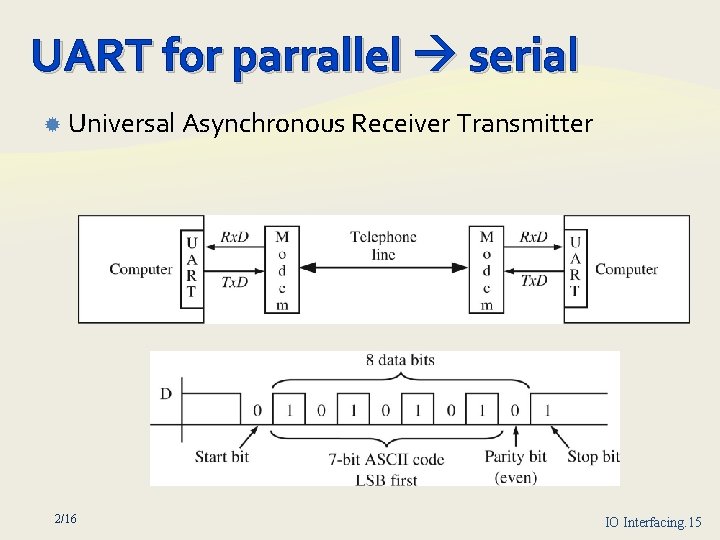

Example I/O : RS 232 –Serial I/O Parallel to Serial –Lab, icreate Required Blocks Input – Output shift registers Transmit (TX) Receive (RX) control Read / write control TX – RX buffers ; FIFO Clocking 2/16 Configuration needed Baud rate Number of bits (5 -8) Parity Stop bits (1 -2) IO Interfacing. 14

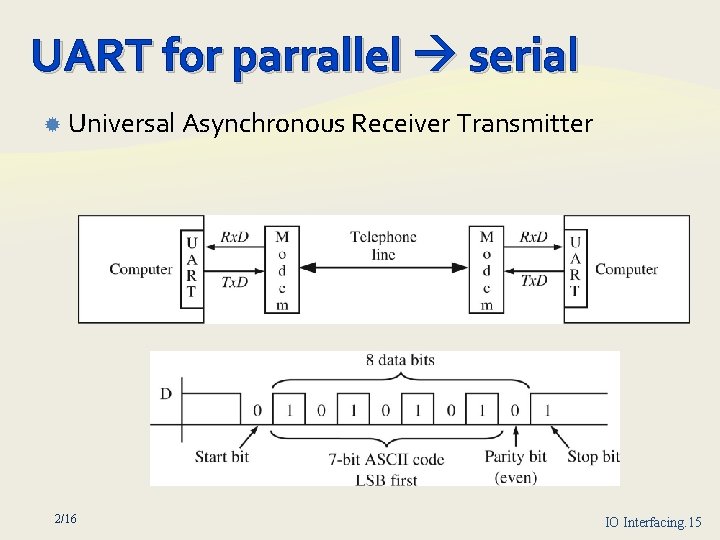

UART for parrallel serial Universal Asynchronous Receiver Transmitter 2/16 IO Interfacing. 15

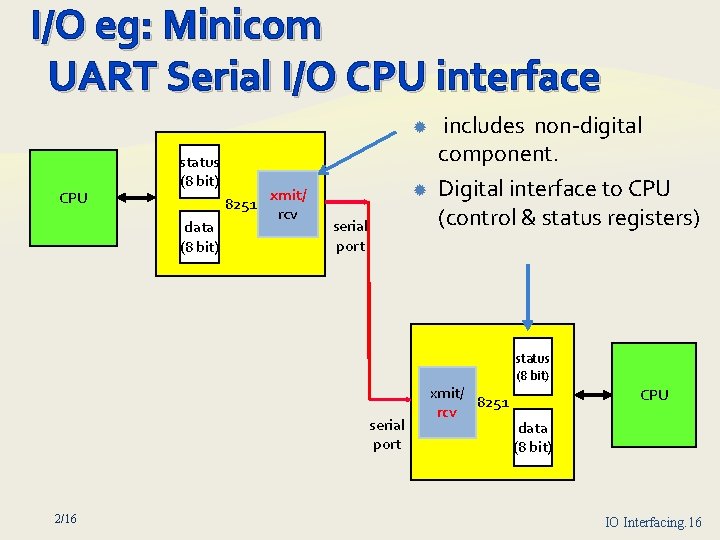

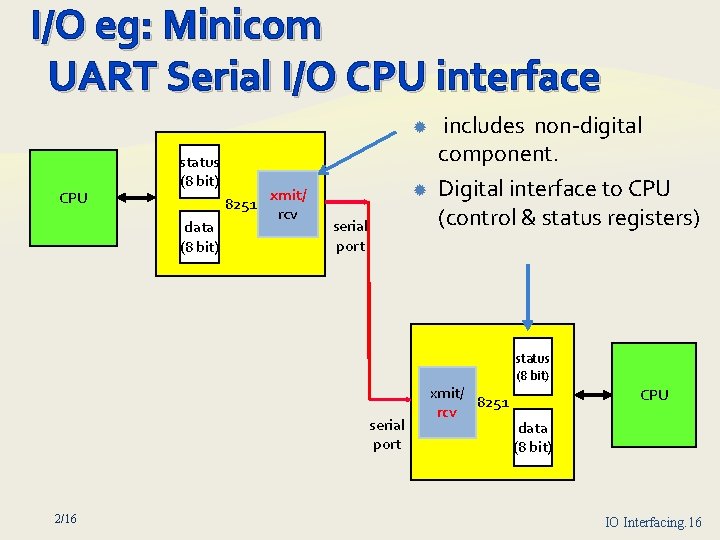

I/O eg: Minicom UART Serial I/O CPU interface CPU status (8 bit) data (8 bit) xmit/ 8251 rcv serial port 2/16 includes non digital component. Digital interface to CPU (control & status registers) xmit/ 8251 rcv status (8 bit) CPU data (8 bit) IO Interfacing. 16

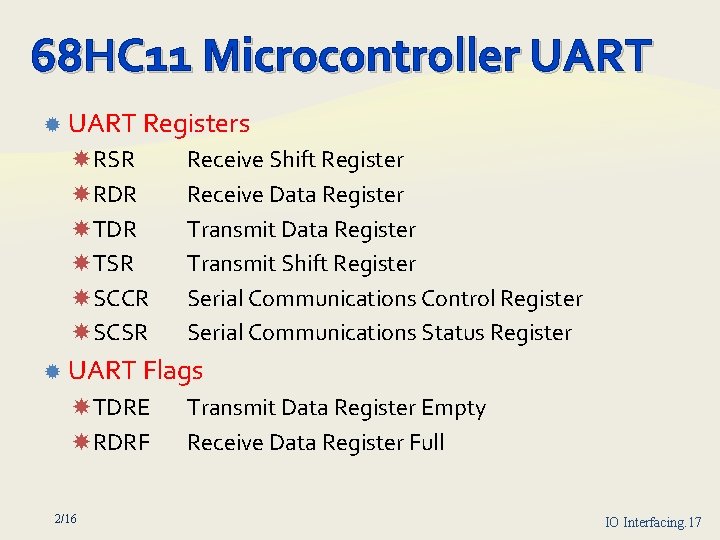

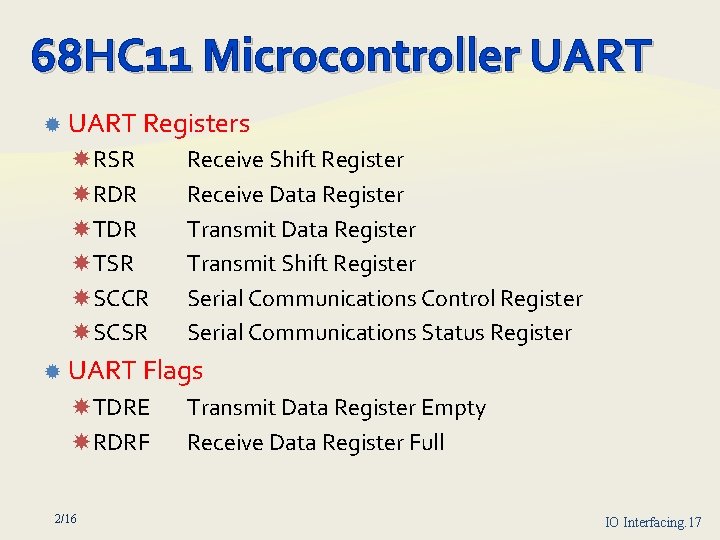

68 HC 11 Microcontroller UART Registers RSR RDR TSR SCCR SCSR Receive Shift Register Receive Data Register Transmit Shift Register Serial Communications Control Register Serial Communications Status Register UART Flags TDRE RDRF 2/16 Transmit Data Register Empty Receive Data Register Full IO Interfacing. 17

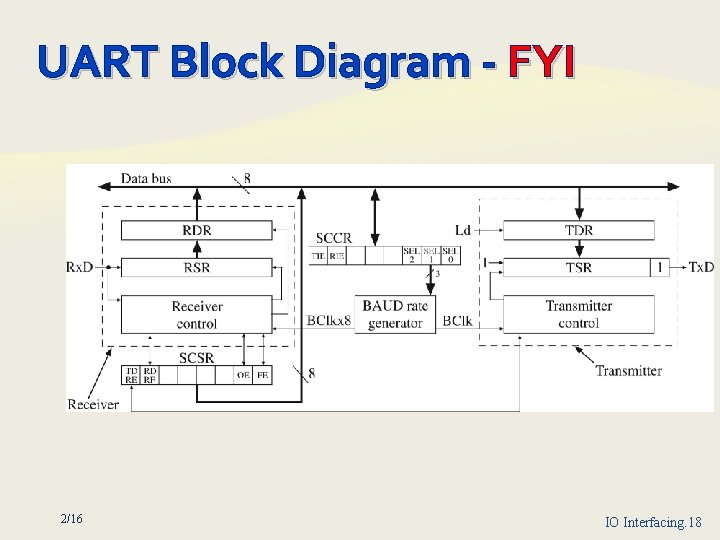

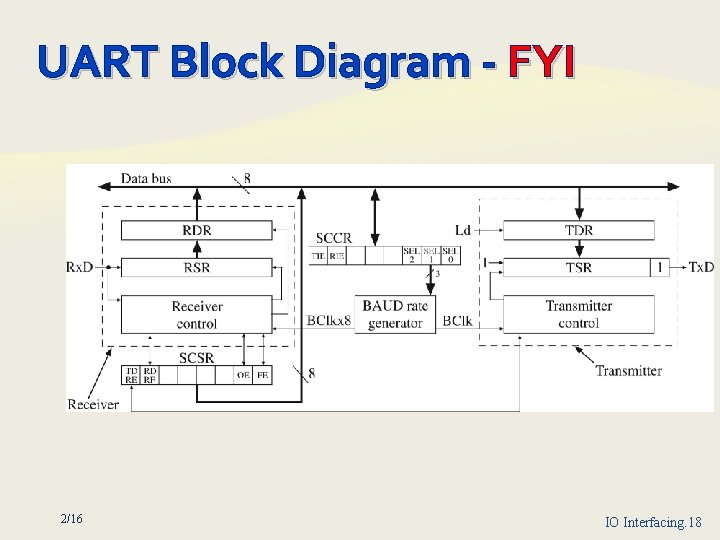

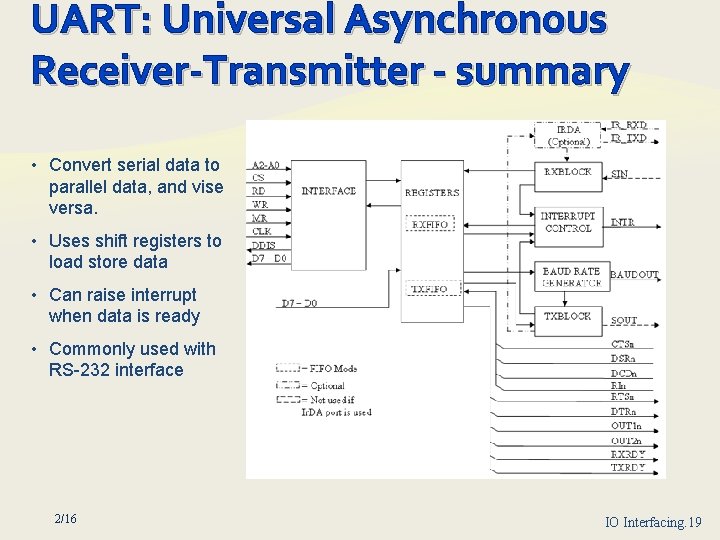

UART Block Diagram FYI 2/16 IO Interfacing. 18

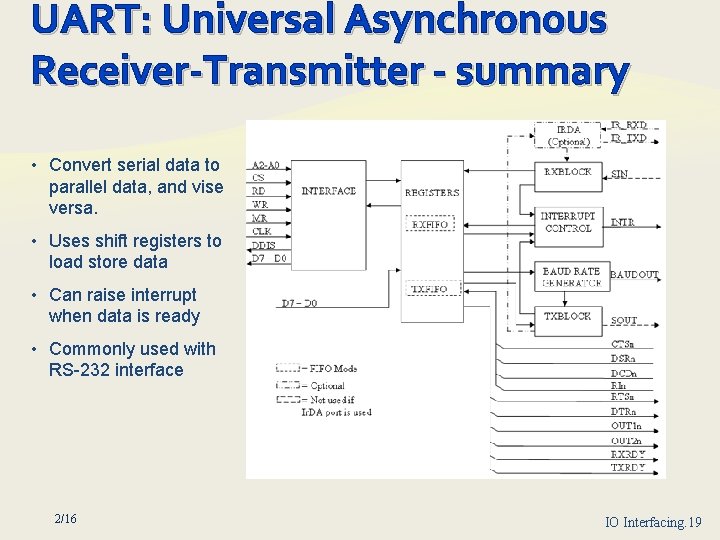

UART: Universal Asynchronous Receiver Transmitter summary • Convert serial data to parallel data, and vise versa. • Uses shift registers to load store data • Can raise interrupt when data is ready • Commonly used with RS-232 interface 2/16 IO Interfacing. 19

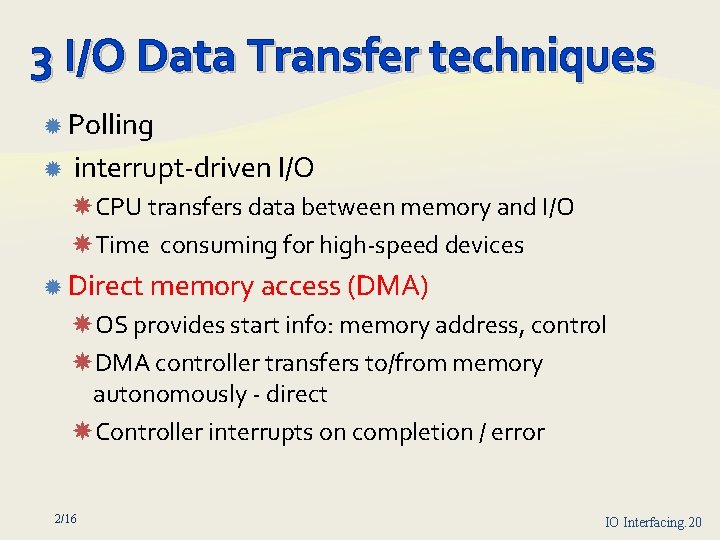

3 I/O Data Transfer techniques Polling interrupt driven I/O CPU transfers data between memory and I/O Time consuming for high speed devices Direct memory access (DMA) OS provides start info: memory address, control DMA controller transfers to/from memory autonomously direct Controller interrupts on completion / error 2/16 IO Interfacing. 20

I/O Mechanisms Polling Periodically check I/O status If device ready, do operation If error, take action small or low performance real time embedded systems Predictable timing Low hardware cost wastes CPU time 2/16 IO Interfacing. 21

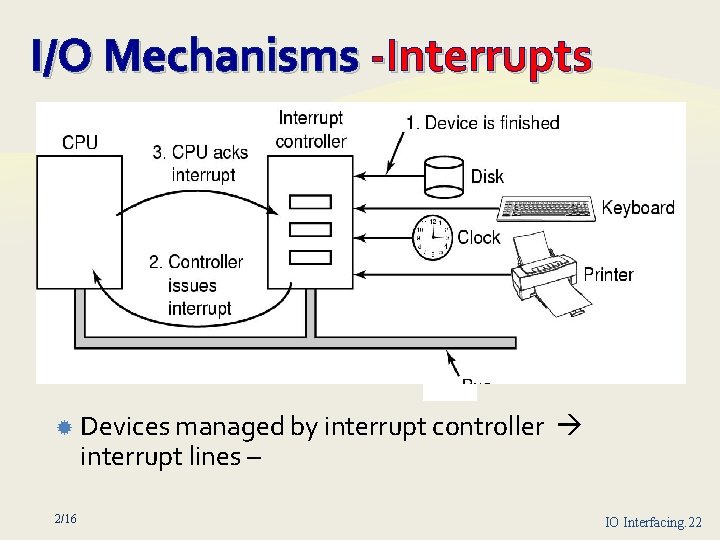

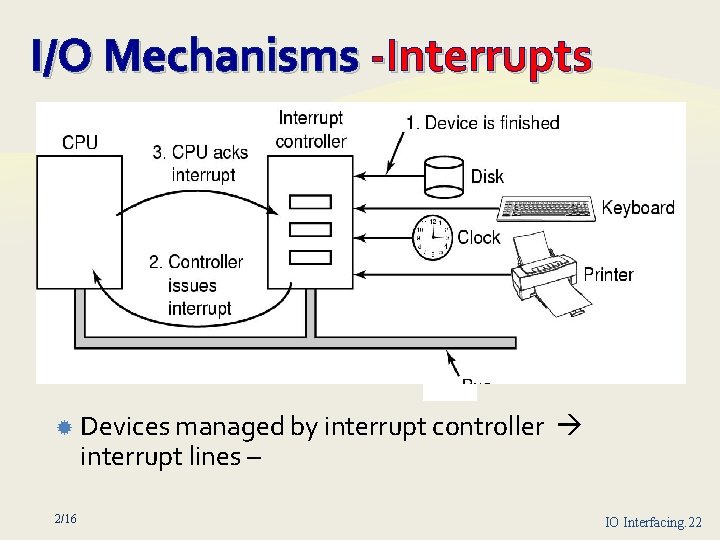

I/O Mechanisms Interrupts 2/16 Devices managed by interrupt controller interrupt lines – IO Interfacing. 22

Interrupts review When device ready or error Interrupt CPU, checked every instruction CPU acknowledges interrupt ; saves the state interrupt handler dispatched determines cause, services the device and clears the interrupt Context switch time Priority interrupts higher priority devices get more attention Can interrupt lower priority device 2/16 IO Interfacing. 23

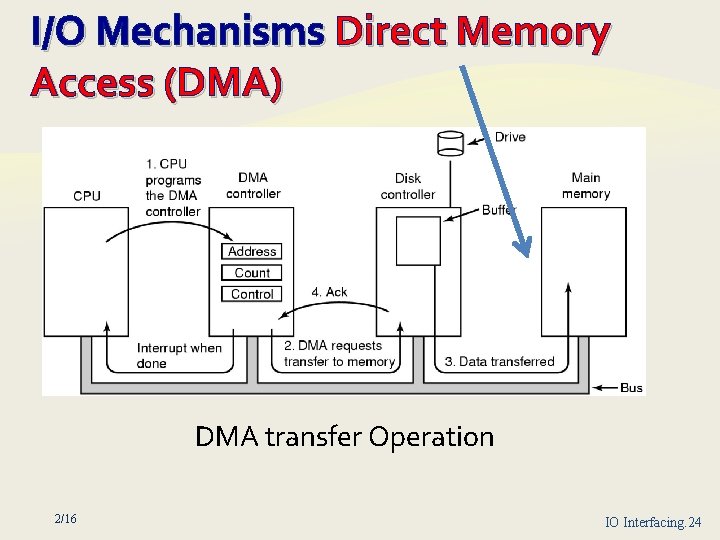

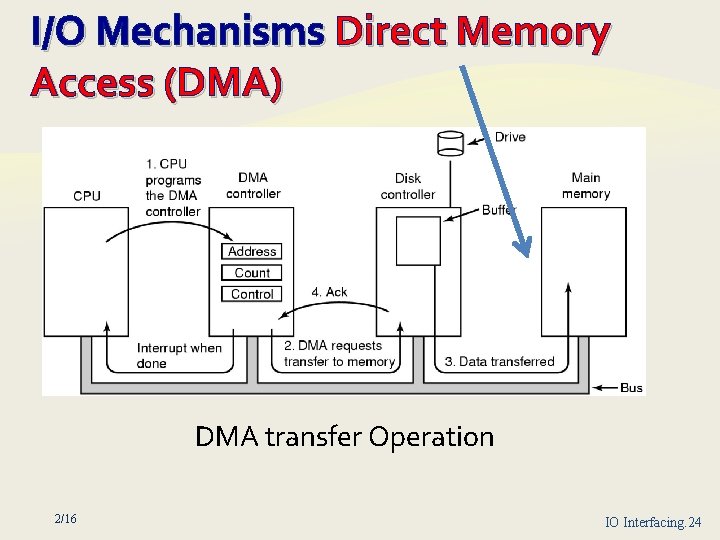

I/O Mechanisms Direct Memory Access (DMA) DMA transfer Operation 2/16 IO Interfacing. 24

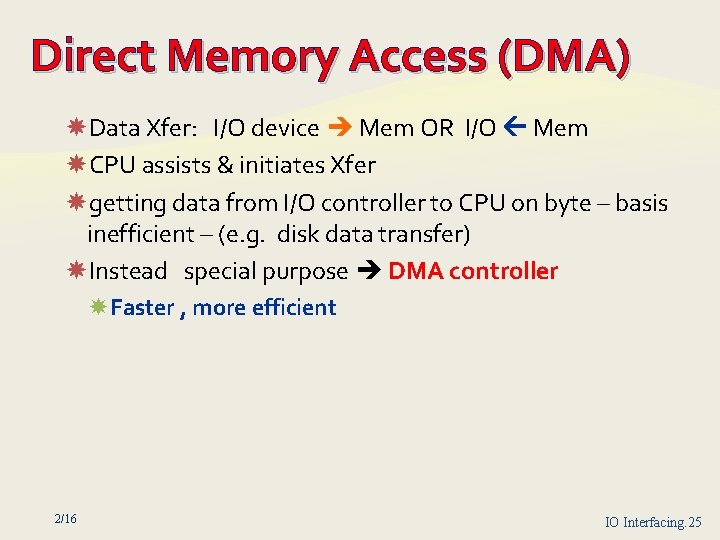

Direct Memory Access (DMA) Data Xfer: I/O device Mem OR I/O Mem CPU assists & initiates Xfer getting data from I/O controller to CPU on byte – basis inefficient – (e. g. disk data transfer) Instead special purpose DMA controller Faster , more efficient 2/16 IO Interfacing. 25

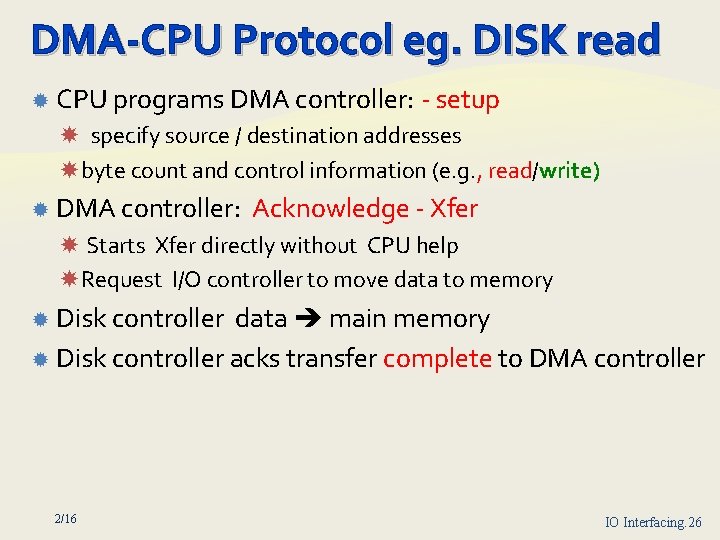

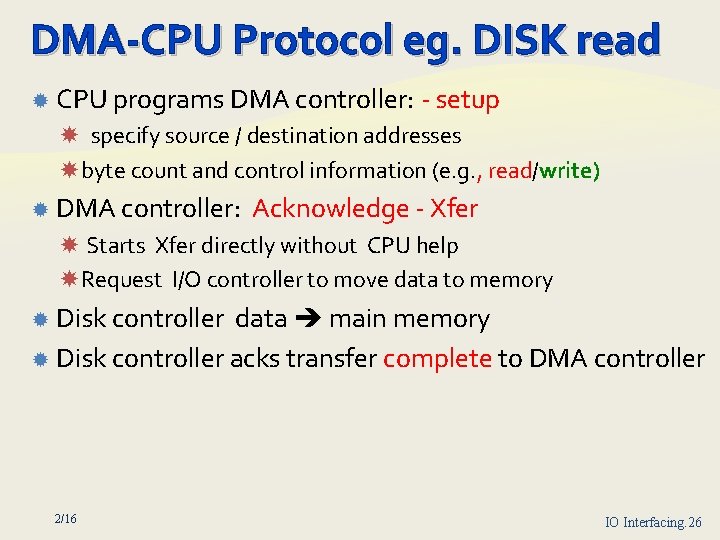

DMA CPU Protocol eg. DISK read CPU programs DMA controller: setup specify source / destination addresses byte count and control information (e. g. , read/write) DMA controller: Acknowledge Xfer Starts Xfer directly without CPU help Request I/O controller to move data to memory Disk controller data main memory Disk controller acks transfer complete to DMA controller 2/16 IO Interfacing. 26

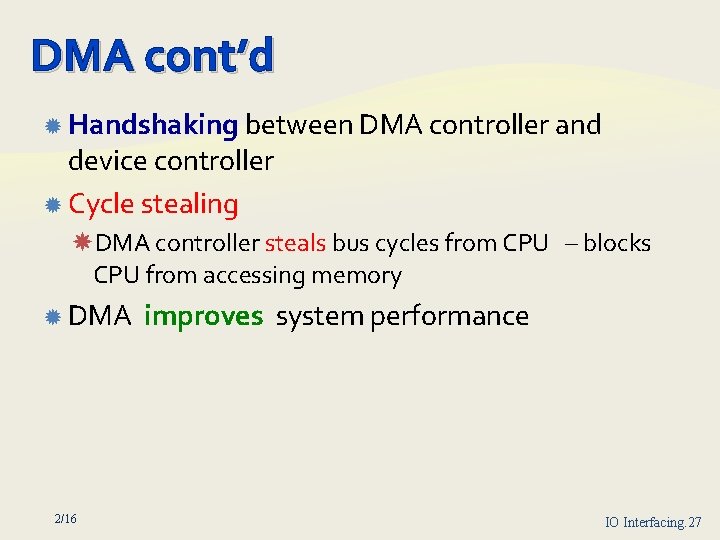

DMA cont’d Handshaking between DMA controller and device controller Cycle stealing DMA controller steals bus cycles from CPU – blocks CPU from accessing memory DMA 2/16 improves system performance IO Interfacing. 27

Choosing I/O method Programmed I/O Interrupt driven I/O using DMA fastest for a single I/O request? highest throughput? Examples of use from each group 2/16 IO Interfacing. 28

I/O Buffer smoothes speed mismatch Buffer: : memory area buffers data device and application. Reasons of buffering: between speed mismatch between producer and consumer of data stream use double buffering Devices have different data transfer sizes application writes to buffer; OS copies to kernel buffer and disk. Unbufferred input strategy ineffective 2/16 IO Interfacing. 29

I/O Errors must be Reported Actual IO Errors at device level (e. g. , damaged disk block, switched off camera ) IO Programming Errors e. g. , write to keyboard, read from printer). device independent IO software detects / responds to errors; report user space IO software. 2/16 IO Interfacing. 30