INVENTIVE Modeling USB 2 0 EHCI TLM 2

INVENTIVE Modeling USB 2. 0 EHCI TLM 2 development using Cadence VSP Tools Praveen Wadikar

Agenda • • Introduction to Virtual Platforms Introduction to EHCI/USB 2. 0 Challenges faced in developing model Cadence VSP tools and its application in tackling challenges during model development • Q&A 2 June 12, 2021

Virtual Platforms for Early Software Development • Virtual Platforms are being used more and more to develop software before hardware is available – Shorten time to market – Increase quality • OSCI/IEEE Standards – Supported by all major EDA vendors – Preserve investments in model IP across tools – Implemented as C++ class libraries (full power of C++) • System. C TLM-2. 0 – Abstract modeling of memory-mapped buses – Allows modeling hardware components at varying levels of abstraction 3

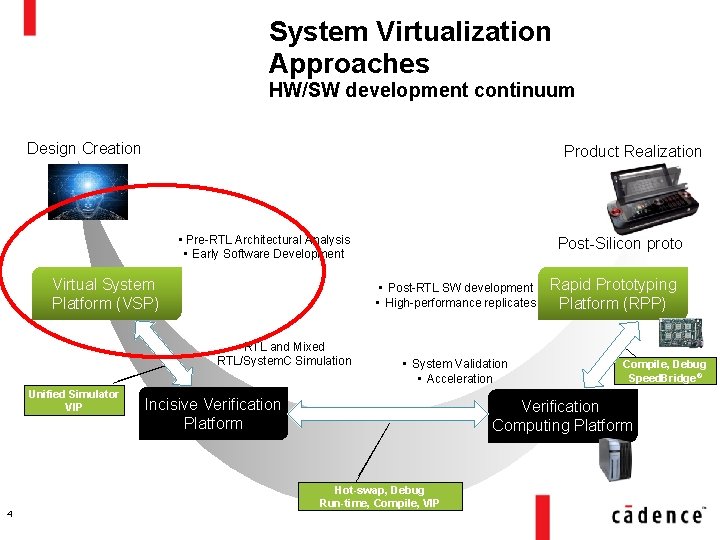

System Virtualization Approaches HW/SW development continuum Design Creation Product Realization • Pre-RTL Architectural Analysis • Early Software Development Virtual System Platform (VSP) • Post-RTL SW development • High-performance replicates RTL and Mixed RTL/System. C Simulation Unified Simulator VIP 4 Post-Silicon proto • System Validation • Acceleration Incisive Verification Platform Rapid Prototyping Platform (RPP) Compile, Debug Speed. Bridge® Verification Computing Platform Hot-swap, Debug Run-time, Compile, VIP

Agenda • Introduction to Virtual Platforms • Introduction to EHCI/USB 2. 0 • • • 5 Challenges faced in developing model Cadence VSP tools and its application in tackling challenges during model development Q&A June 12, 2021

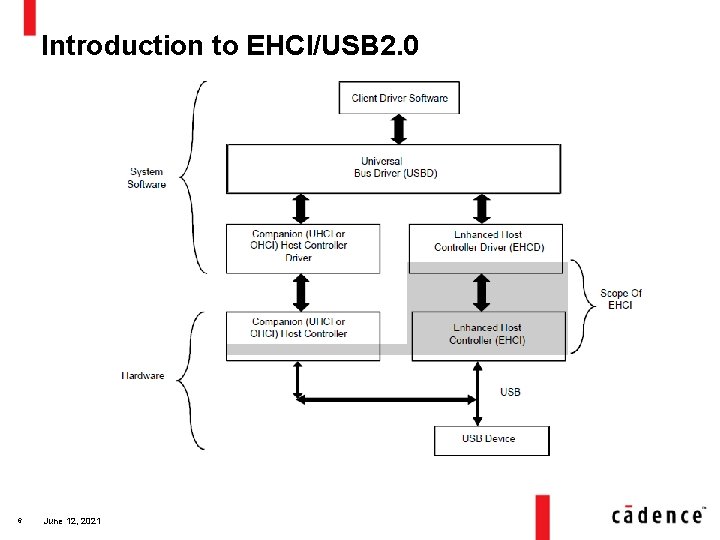

Introduction to EHCI/USB 2. 0 6 June 12, 2021

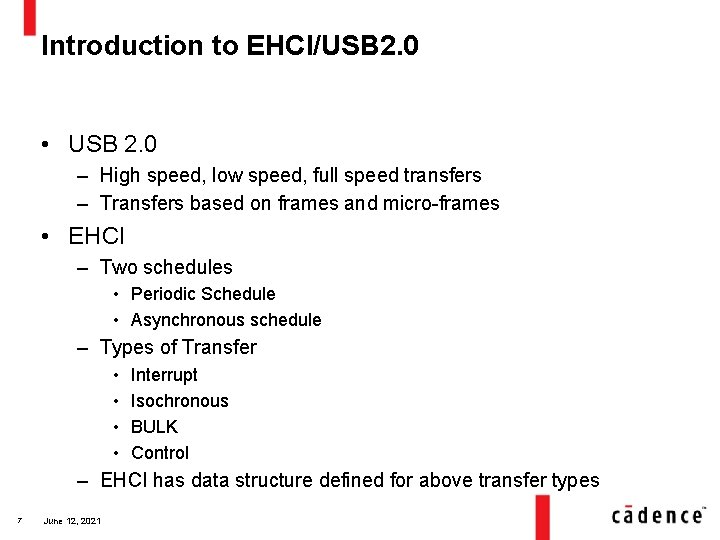

Introduction to EHCI/USB 2. 0 • USB 2. 0 – High speed, low speed, full speed transfers – Transfers based on frames and micro-frames • EHCI – Two schedules • Periodic Schedule • Asynchronous schedule – Types of Transfer • • Interrupt Isochronous BULK Control – EHCI has data structure defined for above transfer types 7 June 12, 2021

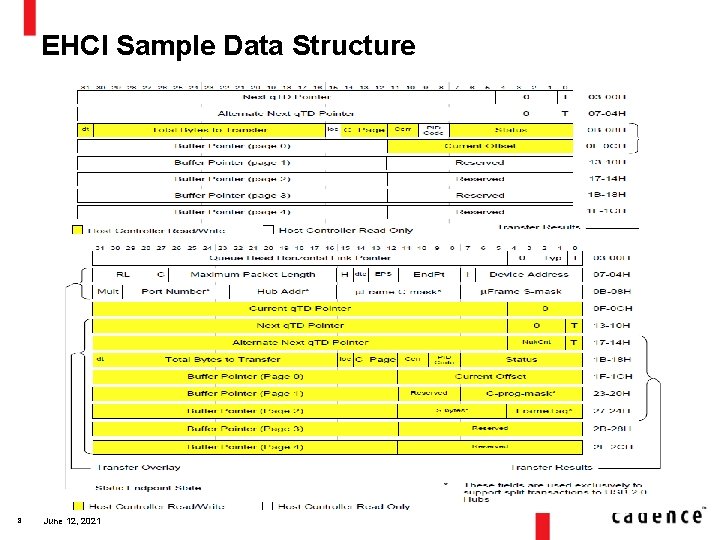

EHCI Sample Data Structure 8 June 12, 2021

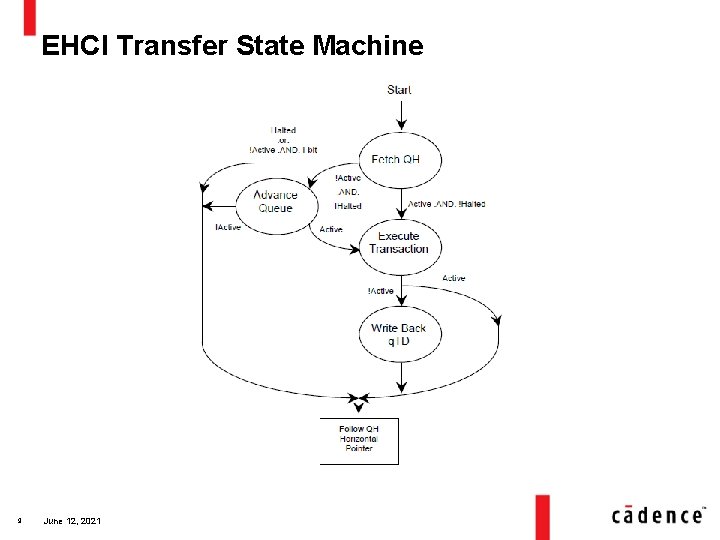

EHCI Transfer State Machine 9 June 12, 2021

Agenda • • Introduction to Virtual Platforms Introduction to EHCI/USB 2. 0 • Challenges faced in developing model • • 10 Cadence VSP tools and its application in tackling challenges during model development Q&A June 12, 2021

Challenges & Issues faced while developing the model • USB PHY is not modeled so faced major challenges in device discovery – Port connection Detection – Port power – Enumeration • Design decisions on modeling the interfaces of the model – Support for usb protocol – NACK/Ack/STALL support – Efficient way to manage data-structures 11 June 12, 2021

Enumeration and Driver Bringup • The basic steps of enumeration – – – – 12 Device connection detect Device debounce stability Reset Device Get descriptor Reset device Set address Get descriptor Register and Load appropriate drivers June 12, 2021

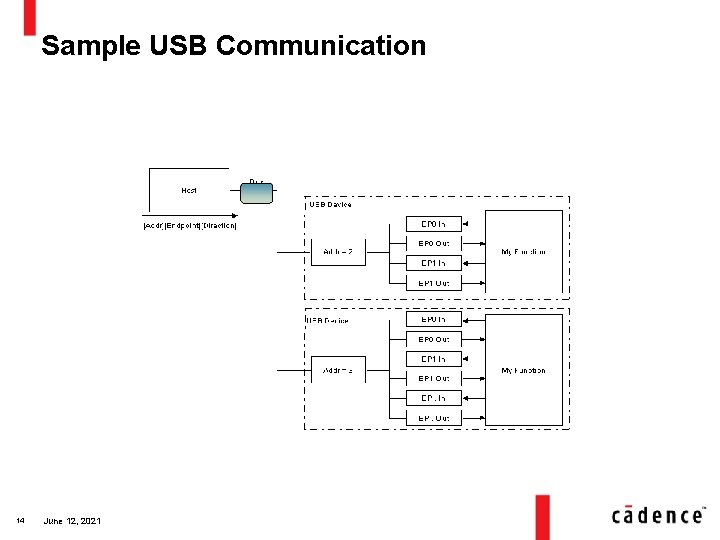

Sample USB transactions during enumeration • • Transfers consists of transactions, and transactions consist of packets Set. Address is an example of a USB transfer. It consists of: – SETUP transaction (->) – IN transaction (<-) – -> means the data flow is from host to device. – <- means the data flow is from device to host. 13 June 12, 2021

Sample USB Communication 14 June 12, 2021

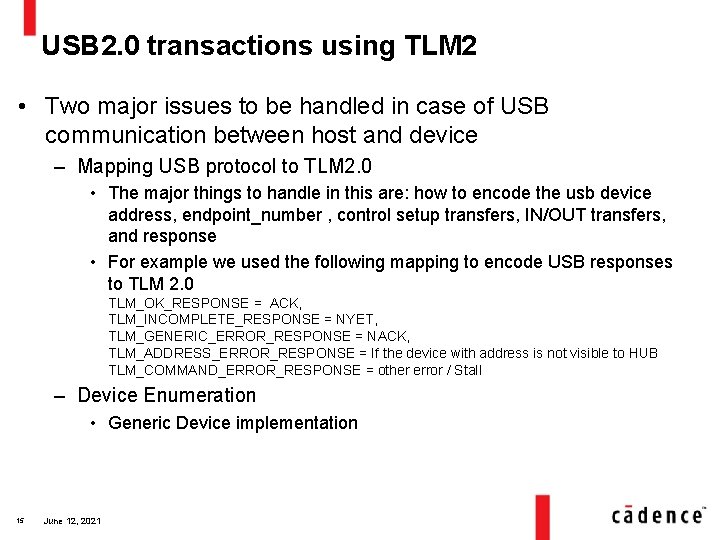

USB 2. 0 transactions using TLM 2 • Two major issues to be handled in case of USB communication between host and device – Mapping USB protocol to TLM 2. 0 • The major things to handle in this are: how to encode the usb device address, endpoint_number , control setup transfers, IN/OUT transfers, and response • For example we used the following mapping to encode USB responses to TLM 2. 0 TLM_OK_RESPONSE = ACK, TLM_INCOMPLETE_RESPONSE = NYET, TLM_GENERIC_ERROR_RESPONSE = NACK, TLM_ADDRESS_ERROR_RESPONSE = If the device with address is not visible to HUB TLM_COMMAND_ERROR_RESPONSE = other error / Stall – Device Enumeration • Generic Device implementation 15 June 12, 2021

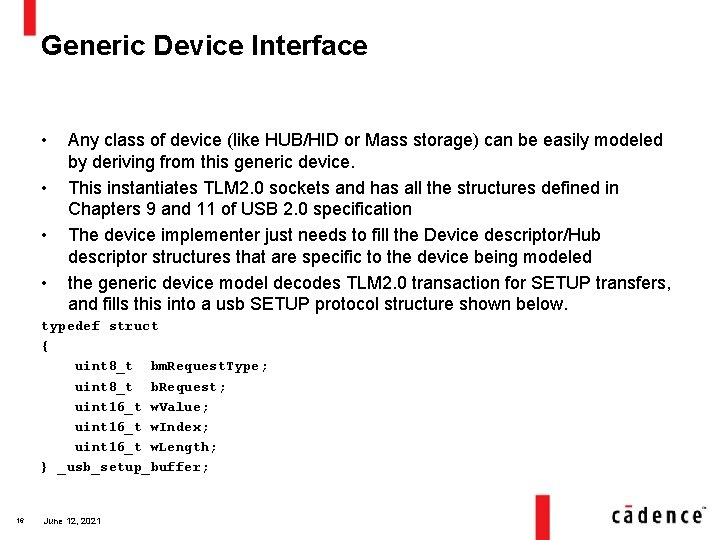

Generic Device Interface • • Any class of device (like HUB/HID or Mass storage) can be easily modeled by deriving from this generic device. This instantiates TLM 2. 0 sockets and has all the structures defined in Chapters 9 and 11 of USB 2. 0 specification The device implementer just needs to fill the Device descriptor/Hub descriptor structures that are specific to the device being modeled the generic device model decodes TLM 2. 0 transaction for SETUP transfers, and fills this into a usb SETUP protocol structure shown below. typedef struct { uint 8_t bm. Request. Type; uint 8_t b. Request; uint 16_t w. Value; uint 16_t w. Index; uint 16_t w. Length; } _usb_setup_buffer; 16 June 12, 2021

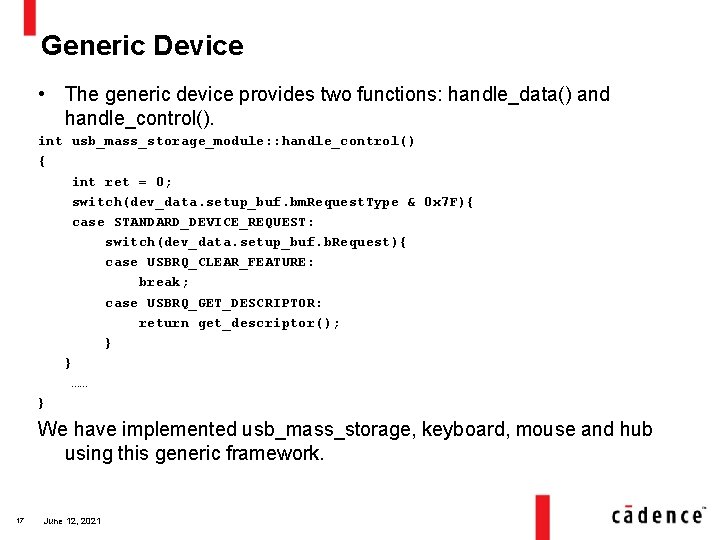

Generic Device • The generic device provides two functions: handle_data() and handle_control(). int usb_mass_storage_module: : handle_control() { int ret = 0; switch(dev_data. setup_buf. bm. Request. Type & 0 x 7 F){ case STANDARD_DEVICE_REQUEST: switch(dev_data. setup_buf. b. Request){ case USBRQ_CLEAR_FEATURE: break; case USBRQ_GET_DESCRIPTOR: return get_descriptor(); } } …… } We have implemented usb_mass_storage, keyboard, mouse and hub using this generic framework. 17 June 12, 2021

Agenda • • Introduction to EHCI/USB 2. 0 Challenges faced in developing model • Cadence VSP tools and its application in tackling challenges during model development • 18 Q&A June 12, 2021

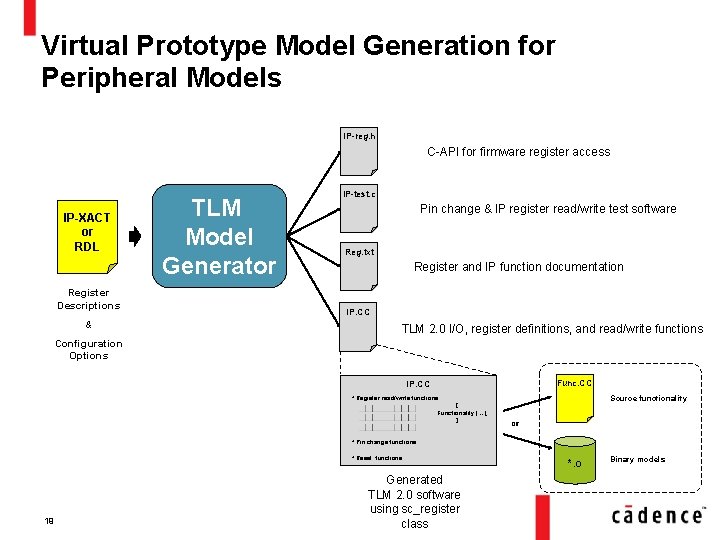

Virtual Prototype Model Generation for Peripheral Models IP-reg. h C-API for firmware register access IP-XACT or RDL Register Descriptions & TLM Model Generator IP-test. c Pin change & IP register read/write test software Reg. txt Register and IP function documentation IP. CC TLM 2. 0 I/O, register definitions, and read/write functions Configuration Options Func. CC IP. CC Source functionality * Register read/write functions { Functionality (…); } OR * Pin change functions * Reset functions 19 Generated TLM 2. 0 software using sc_register class *. o Binary models

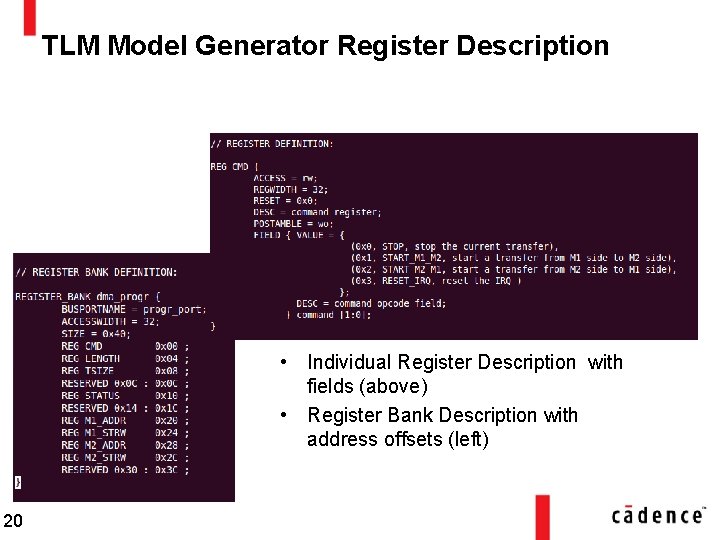

TLM Model Generator Register Description • Individual Register Description with fields (above) • Register Bank Description with address offsets (left) 20

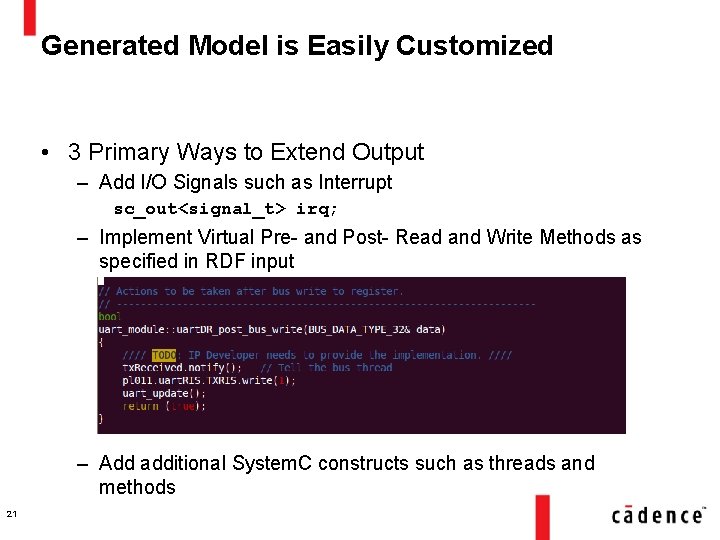

Generated Model is Easily Customized • 3 Primary Ways to Extend Output – Add I/O Signals such as Interrupt sc_out<signal_t> irq; – Implement Virtual Pre- and Post- Read and Write Methods as specified in RDF input – Add additional System. C constructs such as threads and methods 21

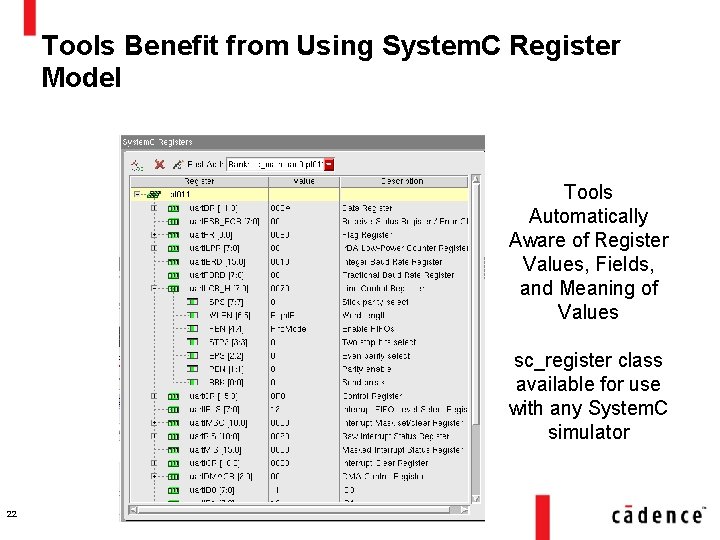

Tools Benefit from Using System. C Register Model Tools Automatically Aware of Register Values, Fields, and Meaning of Values sc_register class available for use with any System. C simulator 22

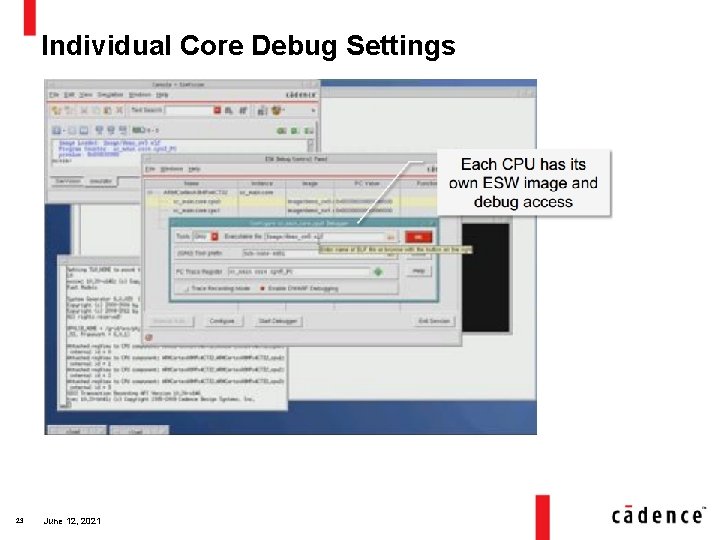

Individual Core Debug Settings 23 June 12, 2021

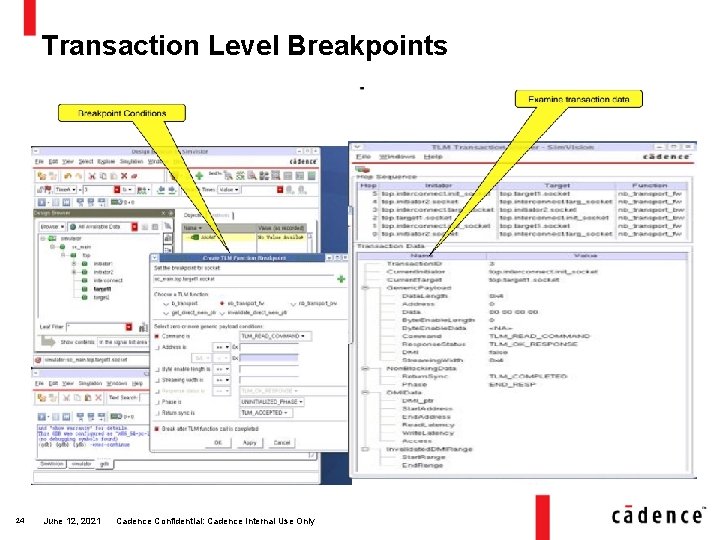

Transaction Level Breakpoints 24 June 12, 2021 Cadence Confidential: Cadence Internal Use Only

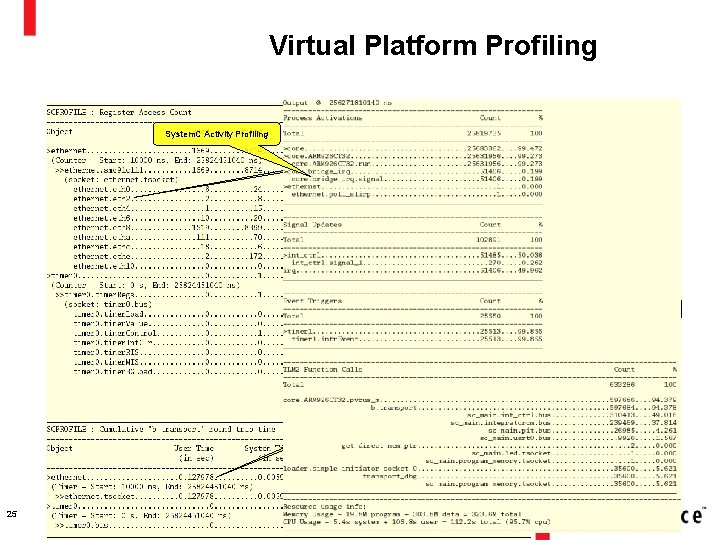

Virtual Platform Profiling Register Read/Write Profiling System. C Activity Profiling Measuring time spent in b_transport 25

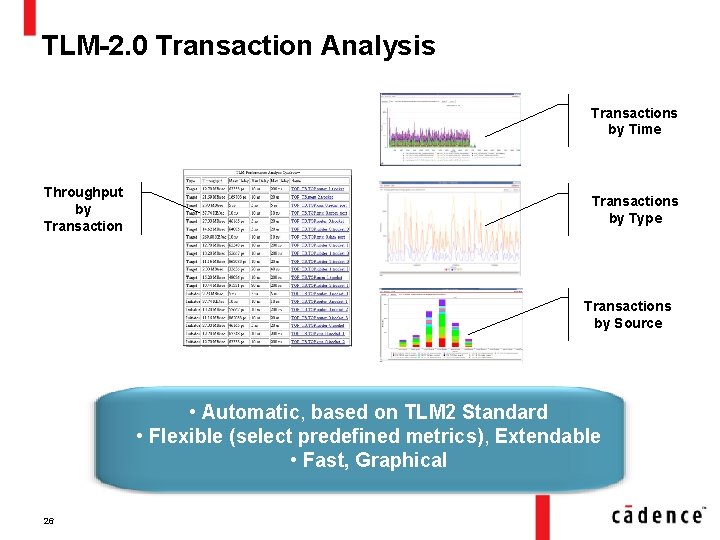

TLM-2. 0 Transaction Analysis Transactions by Time Throughput by Transactions by Type Transactions by Source • Automatic, based on TLM 2 Standard • Flexible (select predefined metrics), Extendable • Fast, Graphical 26

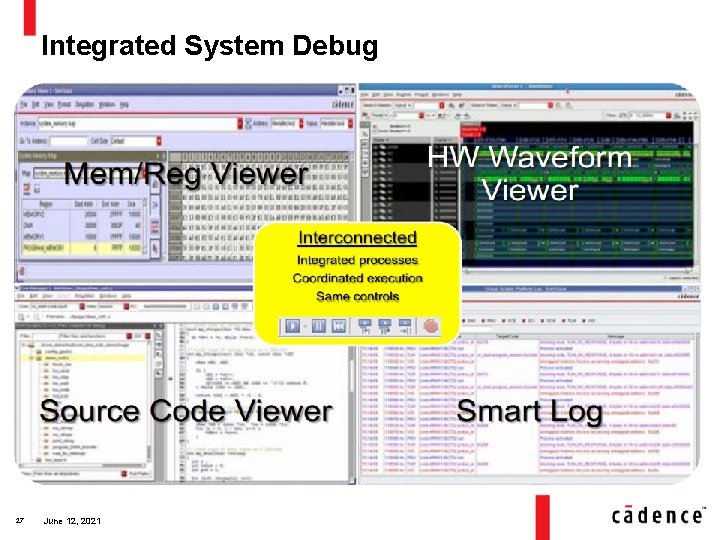

Integrated System Debug 27 June 12, 2021

Challenges Faced in Driver bringup • CONFIGFLAG register – This is a read-write register. But in the IP under development this was made read-only register (because IP Supports only one port) • De-bounce error – Port has to be stabilized for atleast 100 ms – Initial version did not take care of this. Whenever the port connect interrupt was acknowledged it used to reset the bit • First Device Descriptor – model was expecting the address of transfer descriptor to be in “Next transfer Descriptor” but the model had programmed in “Alternate Transfer Descriptor”. 28 June 12, 2021

How Tools Help – ESW debug: Register dumps, breakpoints, function searching. This was very helpful in solving many issues including the Port de-bounce mentioned above. – System. C debug: One of the cool things that can be done is debugging System. C model and software together. This helped in solving problems like the alternate address /next address issue mentioned above – TLM 2. 0 related debug: Helped in identifying the write to read only register. More importantly it helped in endianess decode and LUN decoding. Without this it would have been very difficult to get around the problem. This is because even with ESW debug you would not know where to put the breakpoint to start the debug. 29 June 12, 2021

Questions? 30 June 12, 2021

ACKNOWLEDGEMENTS • Jason Andrews You can read Jason’s Blog @ http: //www. cadence. com/community/posts/jasona. aspx • Bishnupriya Bhattacharya • Neeti Bhatnagar • Naresh Ramachandran • Ajay Goyal 31 June 12, 2021

References • USB 2. 0 Specification http: //www. usb. org/developers/usb 20/ • EHCI specification • System. C and TLM 2. 0 http: //www. accellera. org/activities/committees/systemc-tlm/ • USB in Nutshell http: //www. beyondlogic. org/usbnutshell/usb 1. shtml 32 June 12, 2021

Thank You 33 June 12, 2021

- Slides: 34