Introduction to VHDL Joseph Collins 3 A Software

- Slides: 25

Introduction to VHDL Joseph Collins, 3 A Software Eng. with files from Dr. W. D. Bishop, P. Eng Email: j 4 collin@engmail. uwaterloo. ca

What is VHDL? Very High-Speed Integrated Circuit n Hardware n Description n Language n n A popular tool for designing digital hardware

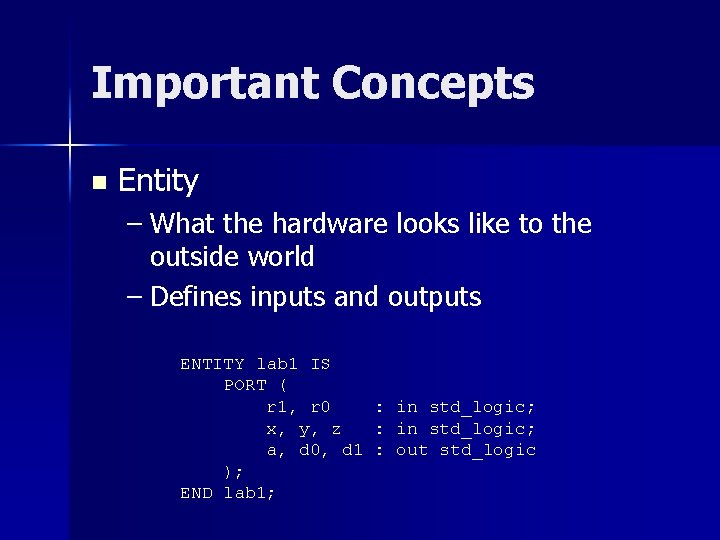

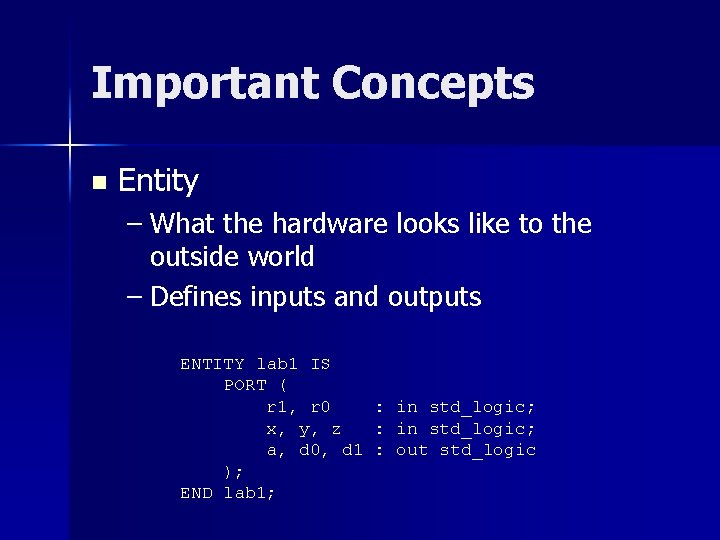

Important Concepts n Entity – What the hardware looks like to the outside world – Defines inputs and outputs ENTITY lab 1 IS PORT ( r 1, r 0 : in std_logic; x, y, z : in std_logic; a, d 0, d 1 : out std_logic ); END lab 1;

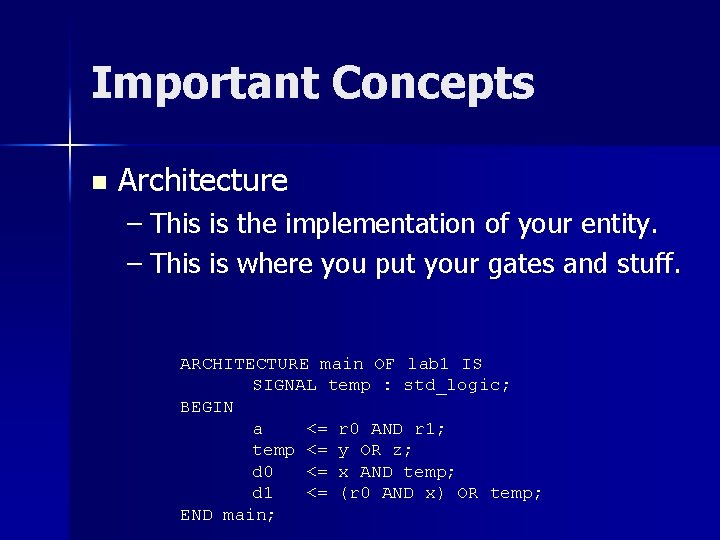

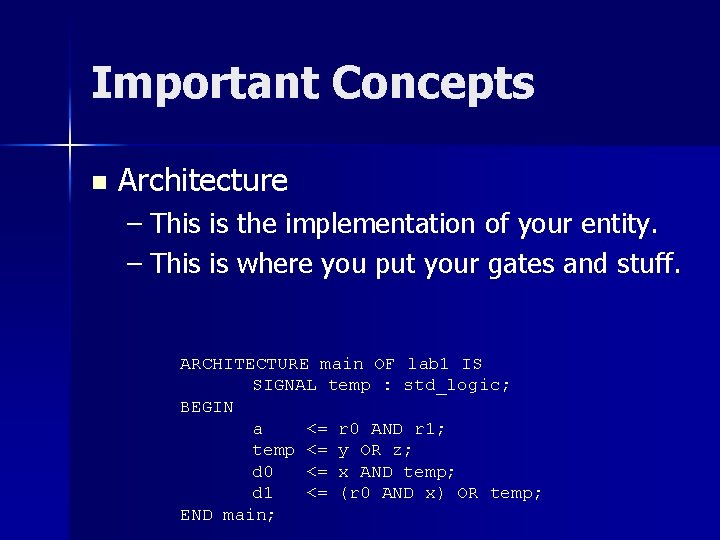

Important Concepts n Architecture – This is the implementation of your entity. – This is where you put your gates and stuff. ARCHITECTURE main OF lab 1 IS SIGNAL temp : std_logic; BEGIN a <= r 0 AND r 1; temp <= y OR z; d 0 <= x AND temp; d 1 <= (r 0 AND x) OR temp; END main;

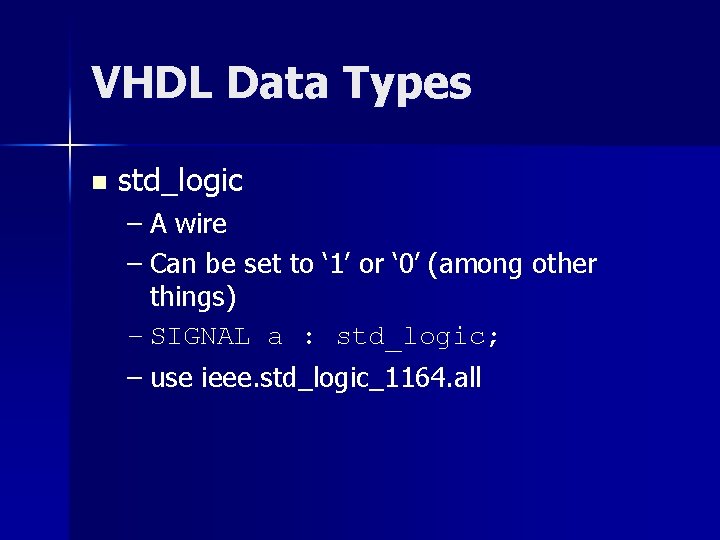

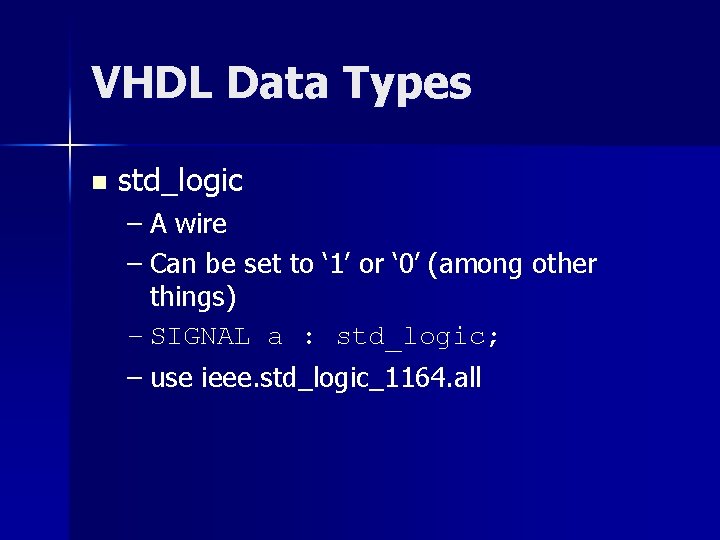

VHDL Data Types n std_logic – A wire – Can be set to ‘ 1’ or ‘ 0’ (among other things) – SIGNAL a : std_logic; – use ieee. std_logic_1164. all

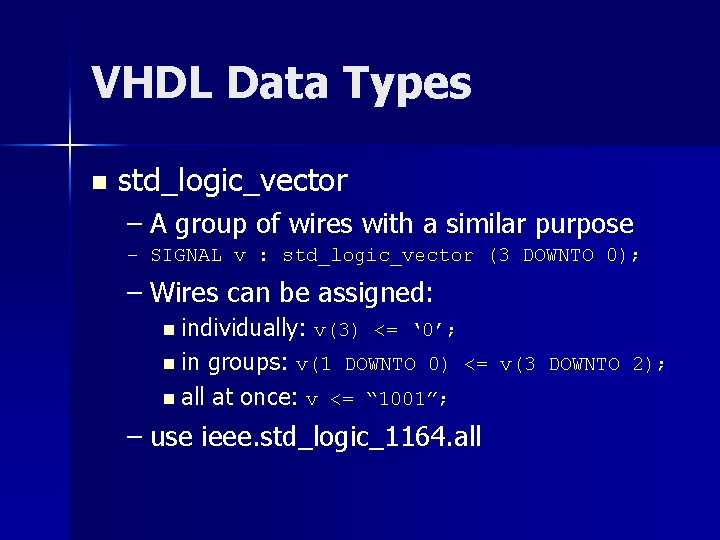

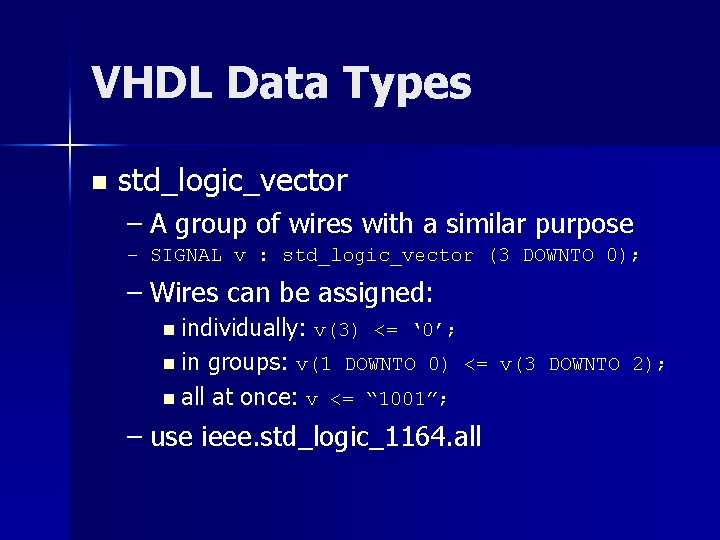

VHDL Data Types n std_logic_vector – A group of wires with a similar purpose – SIGNAL v : std_logic_vector (3 DOWNTO 0); – Wires can be assigned: n individually: v(3) <= ‘ 0’; n in groups: v(1 DOWNTO 0) <= v(3 DOWNTO 2); n all at once: v <= “ 1001”; – use ieee. std_logic_1164. all

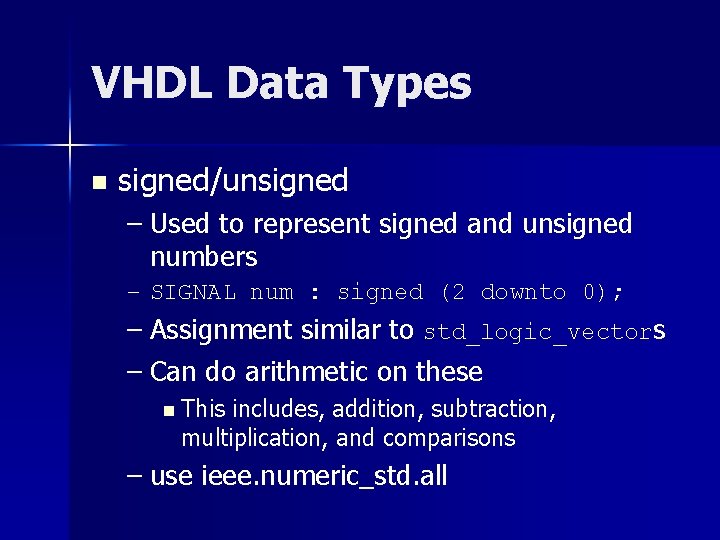

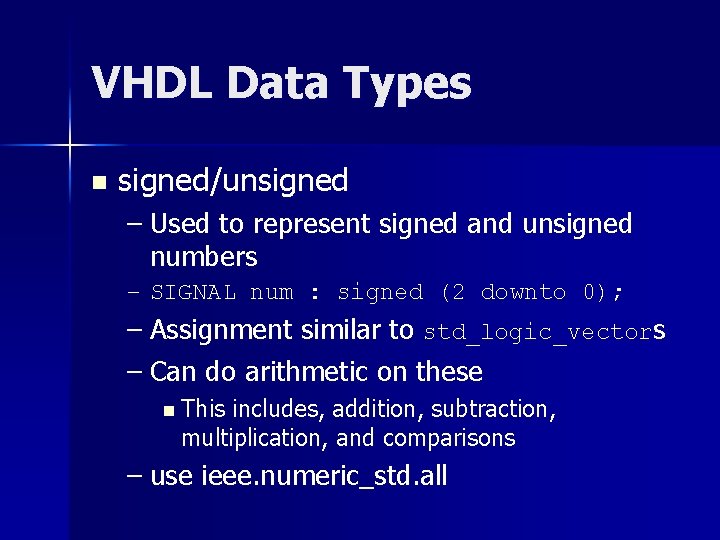

VHDL Data Types n signed/unsigned – Used to represent signed and unsigned numbers – SIGNAL num : signed (2 downto 0); – Assignment similar to std_logic_vectors – Can do arithmetic on these n This includes, addition, subtraction, multiplication, and comparisons – use ieee. numeric_std. all

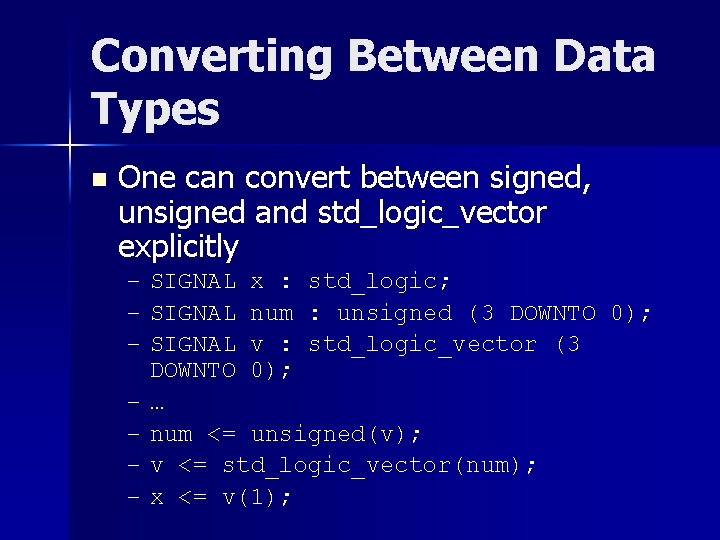

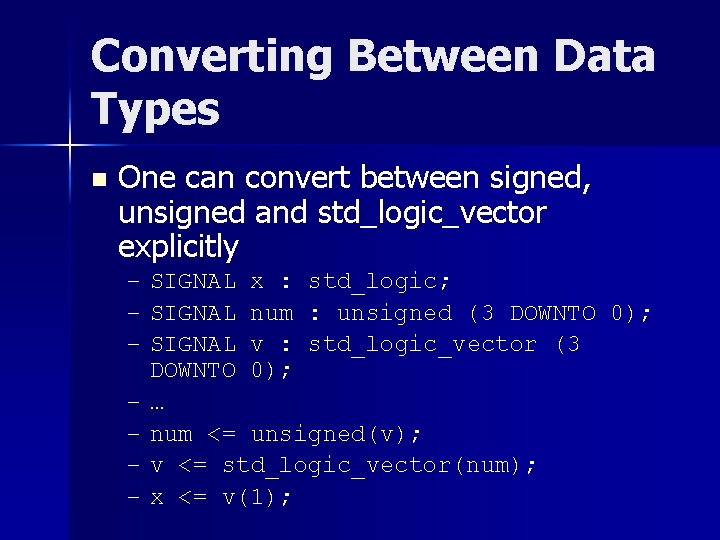

Converting Between Data Types n One can convert between signed, unsigned and std_logic_vector explicitly – SIGNAL x : std_logic; – SIGNAL num : unsigned (3 DOWNTO 0); – SIGNAL v : std_logic_vector (3 DOWNTO 0); –… – num <= unsigned(v); – v <= std_logic_vector(num); – x <= v(1);

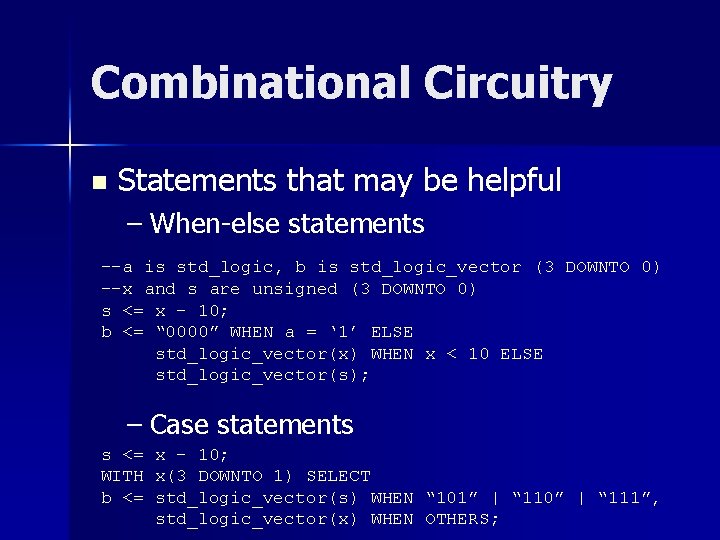

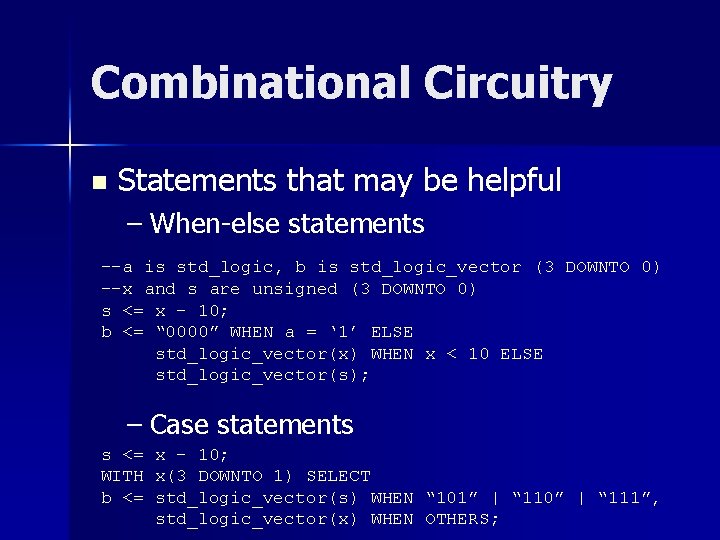

Combinational Circuitry n Statements that may be helpful – When-else statements --a is std_logic, b is std_logic_vector (3 DOWNTO 0) --x and s are unsigned (3 DOWNTO 0) s <= x – 10; b <= “ 0000” WHEN a = ‘ 1’ ELSE std_logic_vector(x) WHEN x < 10 ELSE std_logic_vector(s); – Case statements s <= x – 10; WITH x(3 DOWNTO 1) SELECT b <= std_logic_vector(s) WHEN “ 101” | “ 110” | “ 111”, std_logic_vector(x) WHEN OTHERS;

What questions do you have so far?

Processes So far, we’ve covered basic combinational circuitry n Processes allow for much more human -readable designs n Processes can be combinational or sequential n – Will not cover combinational because they are frowned upon by SE 141 TAs

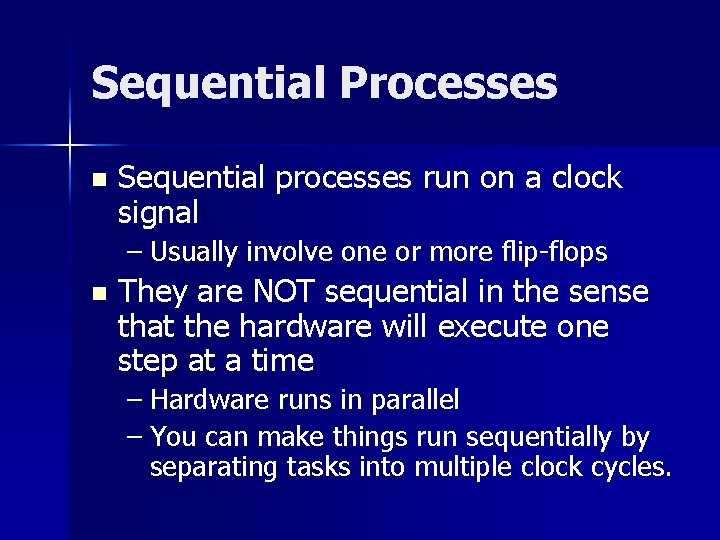

Sequential Processes n Sequential processes run on a clock signal – Usually involve one or more flip-flops n They are NOT sequential in the sense that the hardware will execute one step at a time – Hardware runs in parallel – You can make things run sequentially by separating tasks into multiple clock cycles.

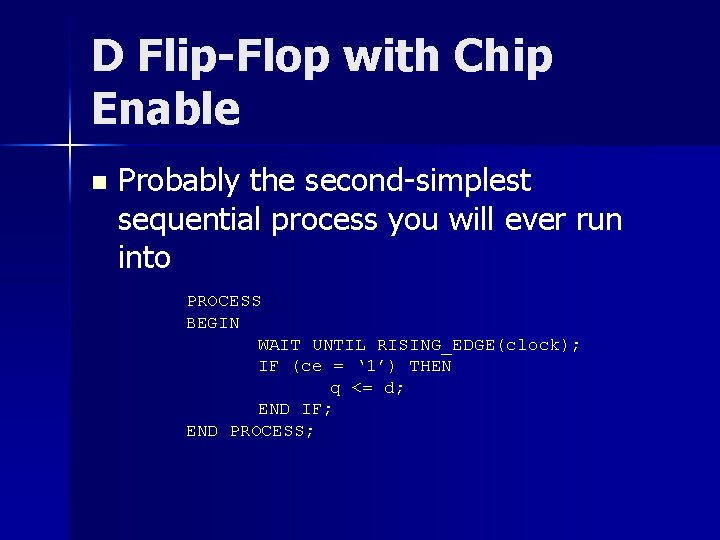

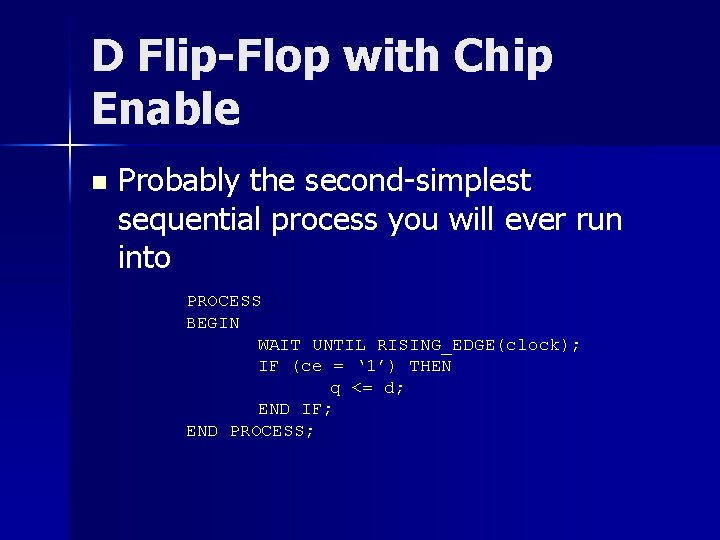

D Flip-Flop with Chip Enable n Probably the second-simplest sequential process you will ever run into PROCESS BEGIN WAIT UNTIL RISING_EDGE(clock); IF (ce = ‘ 1’) THEN q <= d; END IF; END PROCESS;

State Machines Flip Flops that represent a state in your system n Multiple encoding types n – One-hot – Gray – Binary n Usually used in sequential processes

What questions do you have?

Hardware Interfacing n You can easily use a provided piece of hardware as part of a larger circuit – Make sure you understand the specs – You needn’t know the VHDL code behind this piece of hardware n This allows you to work independently on separate parts of your lab

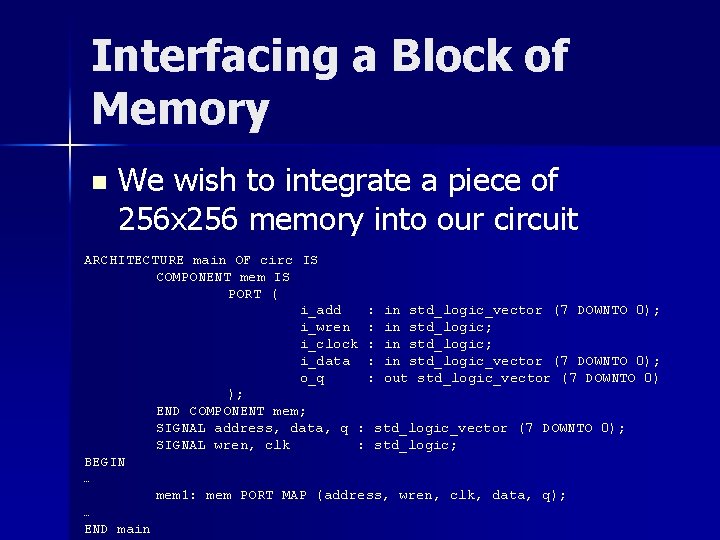

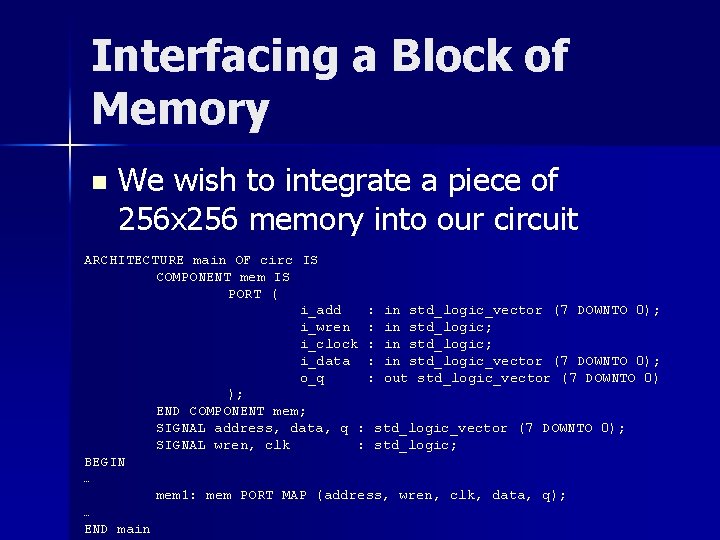

Interfacing a Block of Memory n We wish to integrate a piece of 256 x 256 memory into our circuit ARCHITECTURE main OF circ IS COMPONENT mem IS PORT ( i_add : in std_logic_vector (7 DOWNTO 0); i_wren : in std_logic; i_clock : in std_logic; i_data : in std_logic_vector (7 DOWNTO 0); o_q : out std_logic_vector (7 DOWNTO 0) ); END COMPONENT mem; SIGNAL address, data, q : std_logic_vector (7 DOWNTO 0); SIGNAL wren, clk : std_logic; BEGIN … mem 1: mem PORT MAP (address, wren, clk, data, q); … END main

Simulation We have covered hardware that you can synthesize nicely for use on an FPGA board n VHDL can be used to simulate these circuits n – Note: we will be using non-synthesizable VHDL for doing simulations

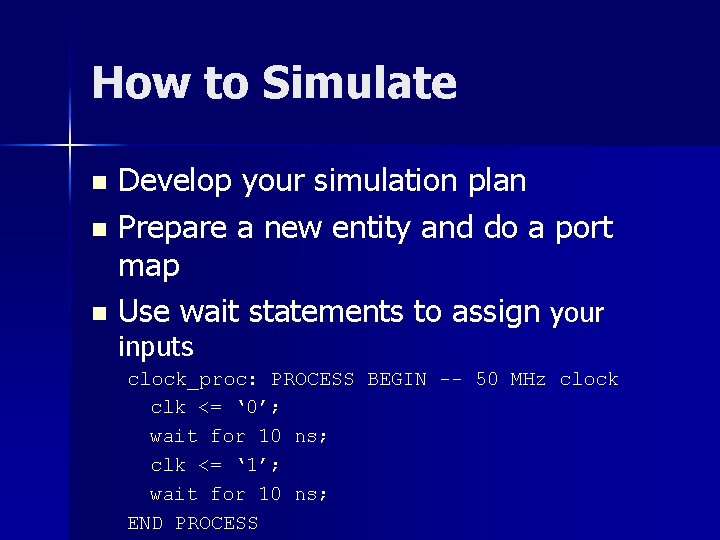

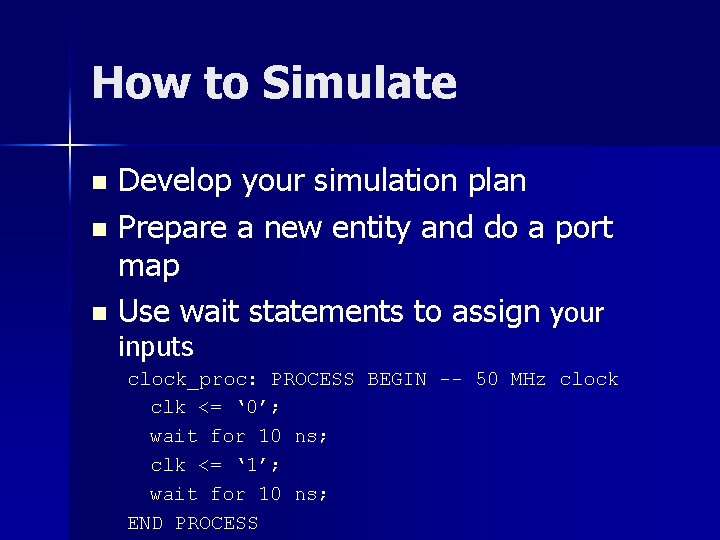

How to Simulate Develop your simulation plan n Prepare a new entity and do a port map n Use wait statements to assign your n inputs clock_proc: PROCESS BEGIN -- 50 MHz clock clk <= ‘ 0’; wait for 10 ns; clk <= ‘ 1’; wait for 10 ns; END PROCESS

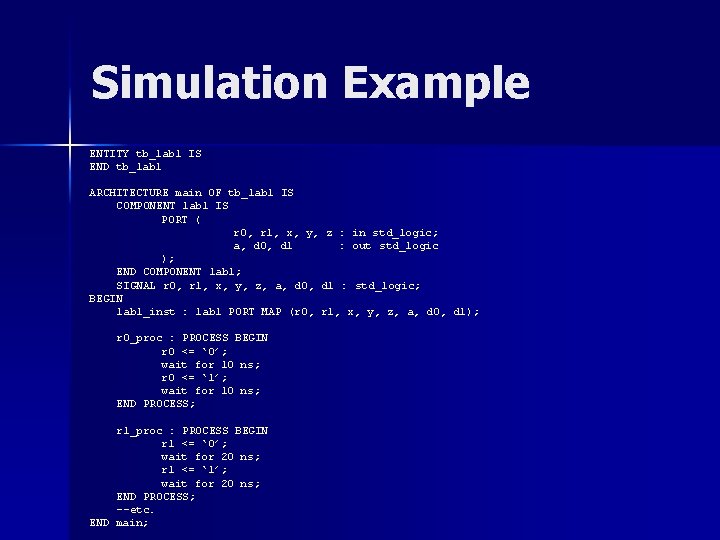

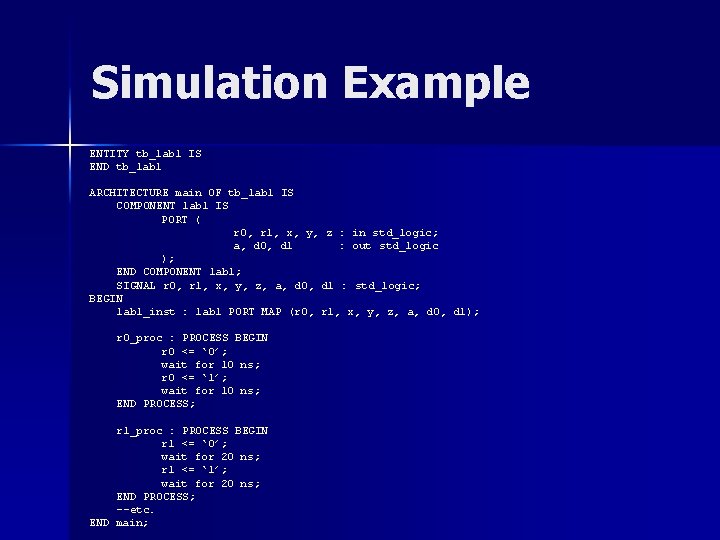

Simulation Example ENTITY tb_lab 1 IS END tb_lab 1 ARCHITECTURE main OF tb_lab 1 IS COMPONENT lab 1 IS PORT ( r 0, r 1, x, y, z : in std_logic; a, d 0, d 1 : out std_logic ); END COMPONENT lab 1; SIGNAL r 0, r 1, x, y, z, a, d 0, d 1 : std_logic; BEGIN lab 1_inst : lab 1 PORT MAP (r 0, r 1, x, y, z, a, d 0, d 1); r 0_proc : PROCESS BEGIN r 0 <= ‘ 0’; wait for 10 ns; r 0 <= ‘ 1’; wait for 10 ns; END PROCESS; r 1_proc : PROCESS BEGIN r 1 <= ‘ 0’; wait for 20 ns; r 1 <= ‘ 1’; wait for 20 ns; END PROCESS; --etc. END main;

What questions do you have?

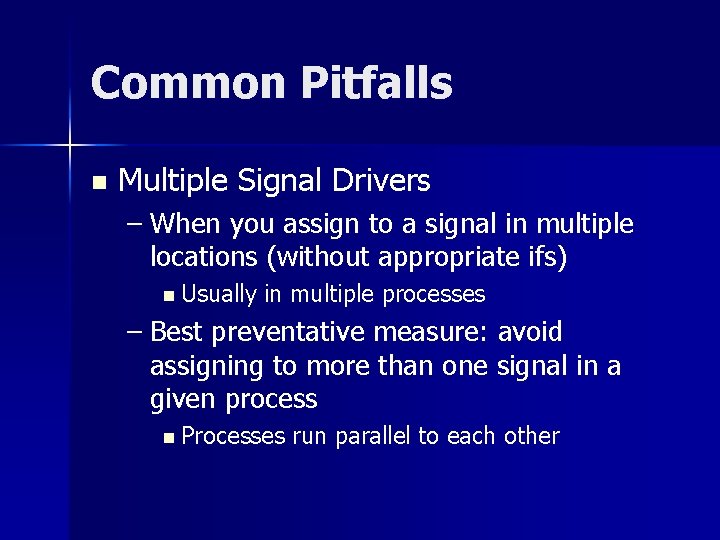

Common Pitfalls n Multiple Signal Drivers – When you assign to a signal in multiple locations (without appropriate ifs) n Usually in multiple processes – Best preventative measure: avoid assigning to more than one signal in a given process n Processes run parallel to each other

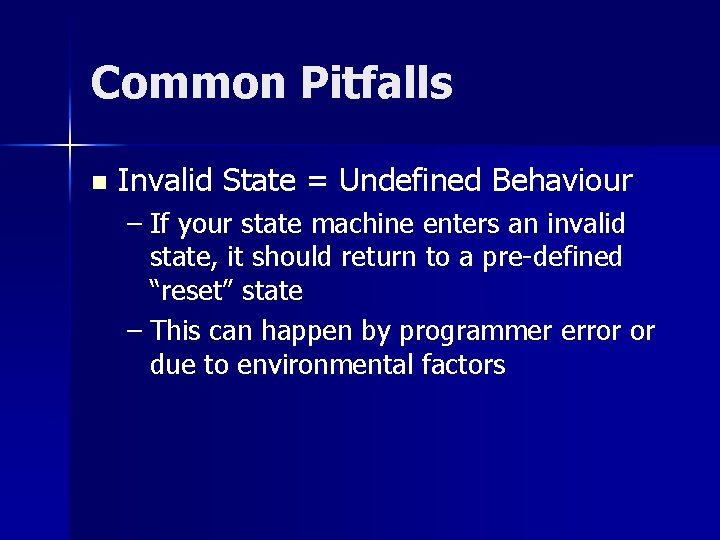

Common Pitfalls n Invalid State = Undefined Behaviour – If your state machine enters an invalid state, it should return to a pre-defined “reset” state – This can happen by programmer error or due to environmental factors

What questions do you have? This is about all I have.

Do not hesitate to contact me! - Email: j 4 collin@engmail. uwaterloo. ca - I often hang out in SE lounge/lab and/or Math. Soc (MC 3038) - Have a good Pi Day tomorrow