Introduction to very deep submicron CMOS processes the

Introduction to very deep submicron CMOS processes: the 65 nm CMOS technology for mixed mode analog-digital circuits Valerio Re Università di Bergamo Dipartimento di Ingegneria INFN Sezione di Pavia V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

CMOS scaling and nuclear microelectronics Industrial microelectronic technologies are today well beyond the 100 nm frontier bringing CMOS into the nanoscale world 65 nm CMOS has attracted a wide interest in view of the design of very compact front-end systems with advanced integrated functionalities, such as required by semiconductor pixel sensors with low pitch for applications in high energy physics (silicon vertex trackers) and photon science experiments (high resolution imagers) Digital figures of merit (speed, density, power dissipation) are driving the evolution of CMOS technologies. What about analog performance? For analog applications in which speed and density are important, scaling can be in principle beneficial, but what about critical performance parameters such as noise, gain, radiation hardness…? V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 2

Advanced pixel detectors and readout microelectronics Particle tracking at LHC- Phase II: • Very high hit rates (1 -2 GHz/cm 2), need of an intelligent pixel-level data processing • Very high radiation levels (1 Grad Total Ionizing Dose, 10 16 neutrons/cm 2) • Small pixel cells to increase resolution and reduce occupancy (~50 x 50µm 2 or 25 x 100 µm 2) Large chips: > 2 cm x 2 cm, ½ - 1 Billion transistors X-ray imaging at free electron laser facilities: § Reduction of pixel size (100 x 100 m 2 or even less), presently limited by the need of complex electronic functions in the pixel cell § Larger memory capacity to store more images (at XFEL, ideally, 2700 frames at 4. 5 MHz every 100 ms) § Advanced pixel-level processing (1 – 10000 photons dynamic range, 10 -bit ADC, 5 MHz operation) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 3

Microelectronics-oriented collaborative efforts in the high energy physics community: the AIDA project • AIDA Work. Package 3 (ending in January 2015) had the goal of facilitating the access of our community to advanced semiconductor technologies, from nanoscale CMOS to innovative interconnection processes. • This included 65 nm CMOS for new mixed-signal integrated circuits with high density and high performance readout functions • Design work was started at various institutions to develop blocks for analog and digital needs in HEP with full documentation and laboratory tests. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 4

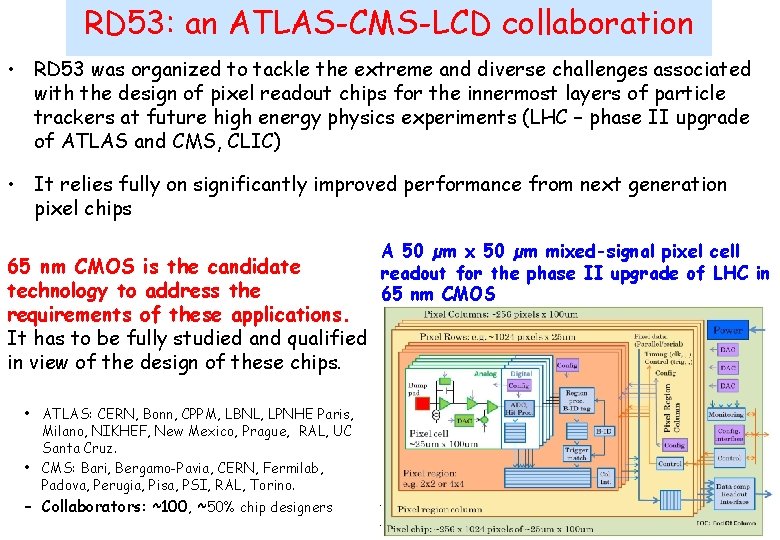

RD 53: an ATLAS-CMS-LCD collaboration • RD 53 was organized to tackle the extreme and diverse challenges associated with the design of pixel readout chips for the innermost layers of particle trackers at future high energy physics experiments (LHC – phase II upgrade of ATLAS and CMS, CLIC) • It relies fully on significantly improved performance from next generation pixel chips 65 nm CMOS is the candidate technology to address the requirements of these applications. It has to be fully studied and qualified in view of the design of these chips. A 50 µm x 50 µm mixed-signal pixel cell readout for the phase II upgrade of LHC in 65 nm CMOS • ATLAS: CERN, Bonn, CPPM, LBNL, LPNHE Paris, Milano, NIKHEF, New Mexico, Prague, RAL, UC Santa Cruz. • CMS: Bari, Bergamo-Pavia, CERN, Fermilab, Padova, Perugia, Pisa, PSI, RAL, Torino. – Collaborators: ~100, ~50% chip designers V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 5

LHC- Phase II pixel challenges • ATLAS and CMS phase 2 pixel upgrades very challenging – – Very high particle rates: 500 MHz/cm 2 • Hit rates: 1 -2 GHz/cm 2 (factor ~16 higher than current pixel detectors) Smaller pixels: ~¼ (~50 x 50 um 2 or 25 x 100 um 2) • • • Increased resolution Improved two track separation (jets) Outer layers can be larger pixels, using same pixel chip – Participation in first/second level trigger ? (no) – Increased readout rates: 100 k. Hz -> ~1 MHz A. 40 MHz extracted clusters (outer layers) ? B. Region of interest readout for second level trigger ? • Data rate: 10 x trigger X >10 x hit rate = >100 x ! – Low mass -> Low power Very similar requirements (and uncertainties) for ATLAS & CMS • Unprecedented hostile radiation: 1 Grad, 1016 Neu/cm 2 – Hybrid pixel detector with separate readout chip and sensor. • Monolithic seems unfeasible for this very high rate hostile radiation environment – Phase 2 pixel will get in 1 year what we now get in 10 years (10. 000 x more radiation than space/mil !) • Pixel sensor(s) not yet determined – Planar, 3 D, Diamond, HV CMOS, … – Possibility of using different sensors in different layers Complex, high rate and radiation hard pixel chips required V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 6

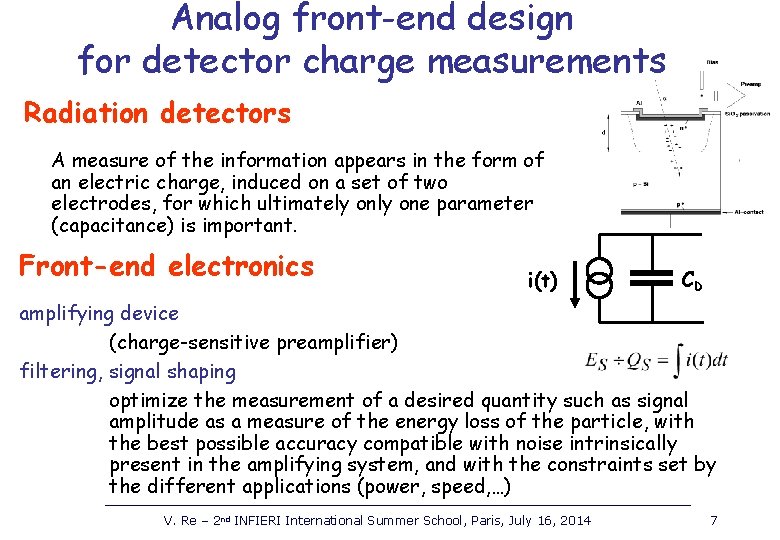

Analog front-end design for detector charge measurements Radiation detectors A measure of the information appears in the form of an electric charge, induced on a set of two electrodes, for which ultimately one parameter (capacitance) is important. Front-end electronics i(t) CD amplifying device (charge-sensitive preamplifier) filtering, signal shaping optimize the measurement of a desired quantity such as signal amplitude as a measure of the energy loss of the particle, with the best possible accuracy compatible with noise intrinsically present in the amplifying system, and with the constraints set by the different applications (power, speed, …) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 7

Effect of electronic noise on charge measurements Inherent to the conduction of current in an amplifying device is a random component, depending on the principle of operation of the device. This random component (noise) associated with amplification gives an uncertainty in the measurement of the charge delivered by the detector or of other parameters such as the position of particle incidence on the detector. Compromises must be made in very large and complex detector systems such as modern silicon trackers. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 8

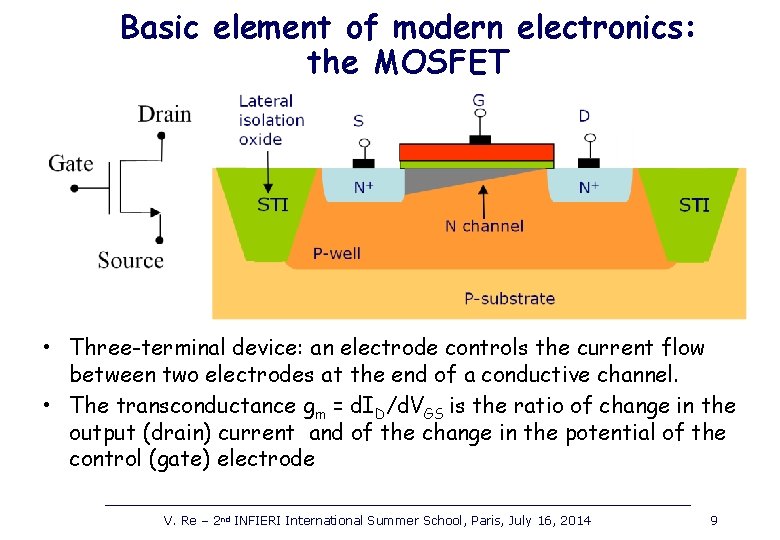

Basic element of modern electronics: the MOSFET • Three-terminal device: an electrode controls the current flow between two electrodes at the end of a conductive channel. • The transconductance gm = d. ID/d. VGS is the ratio of change in the output (drain) current and of the change in the potential of the control (gate) electrode V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 9

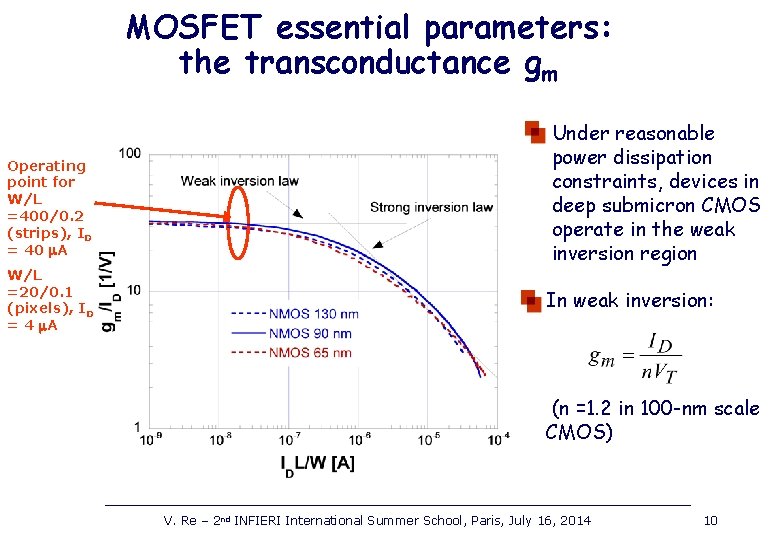

MOSFET essential parameters: the transconductance gm Operating point for W/L =400/0. 2 (strips), ID = 40 m. A W/L =20/0. 1 (pixels), ID = 4 m. A Under reasonable power dissipation constraints, devices in deep submicron CMOS operate in the weak inversion region In weak inversion: (n =1. 2 in 100 -nm scale CMOS) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 10

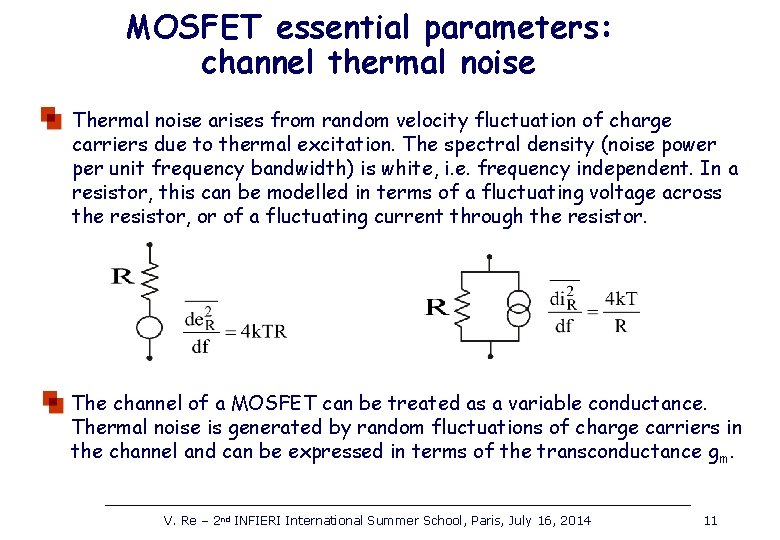

MOSFET essential parameters: channel thermal noise Thermal noise arises from random velocity fluctuation of charge carriers due to thermal excitation. The spectral density (noise power per unit frequency bandwidth) is white, i. e. frequency independent. In a resistor, this can be modelled in terms of a fluctuating voltage across the resistor, or of a fluctuating current through the resistor. The channel of a MOSFET can be treated as a variable conductance. Thermal noise is generated by random fluctuations of charge carriers in the channel and can be expressed in terms of the transconductance g m. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 11

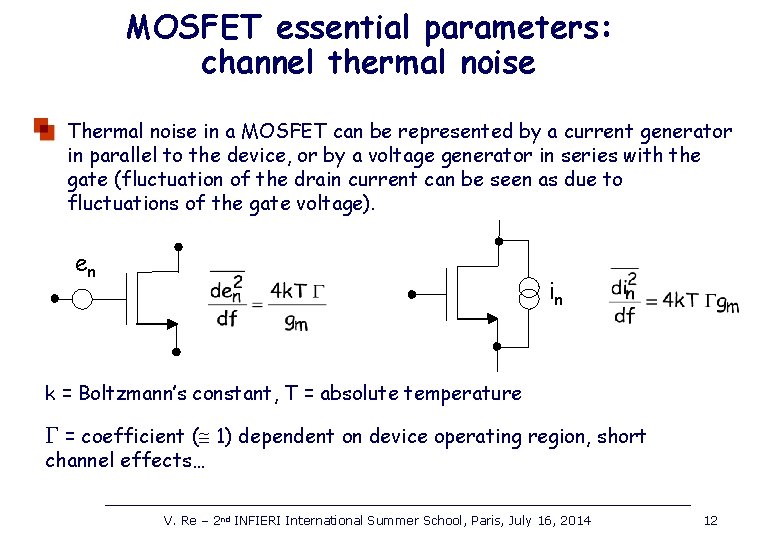

MOSFET essential parameters: channel thermal noise Thermal noise in a MOSFET can be represented by a current generator in parallel to the device, or by a voltage generator in series with the gate (fluctuation of the drain current can be seen as due to fluctuations of the gate voltage). en in k = Boltzmann’s constant, T = absolute temperature G = coefficient ( 1) dependent on device operating region, short channel effects… V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 12

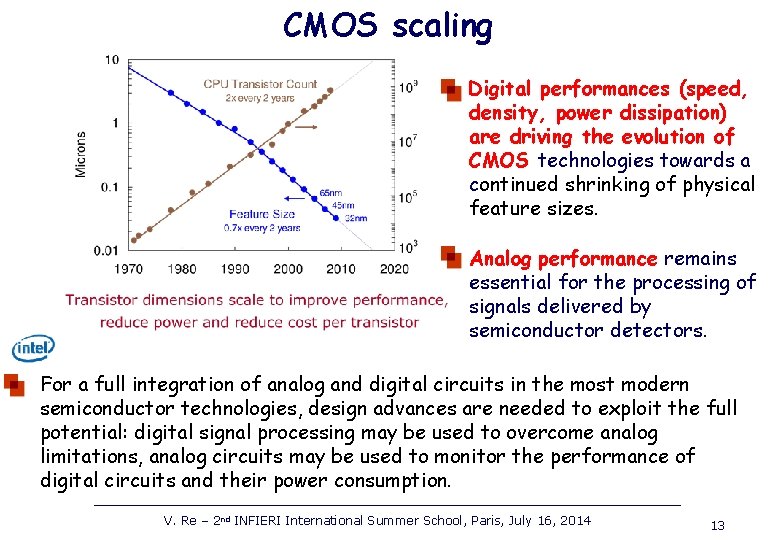

CMOS scaling Digital performances (speed, density, power dissipation) are driving the evolution of CMOS technologies towards a continued shrinking of physical feature sizes. Analog performance remains essential for the processing of signals delivered by semiconductor detectors. For a full integration of analog and digital circuits in the most modern semiconductor technologies, design advances are needed to exploit the full potential: digital signal processing may be used to overcome analog limitations, analog circuits may be used to monitor the performance of digital circuits and their power consumption. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 13

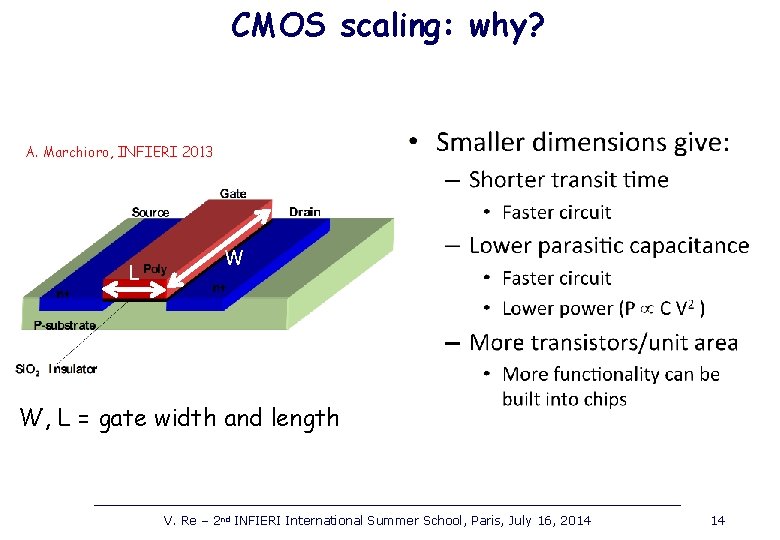

CMOS scaling: why? A. Marchioro, INFIERI 2013 L W W, L = gate width and length V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 14

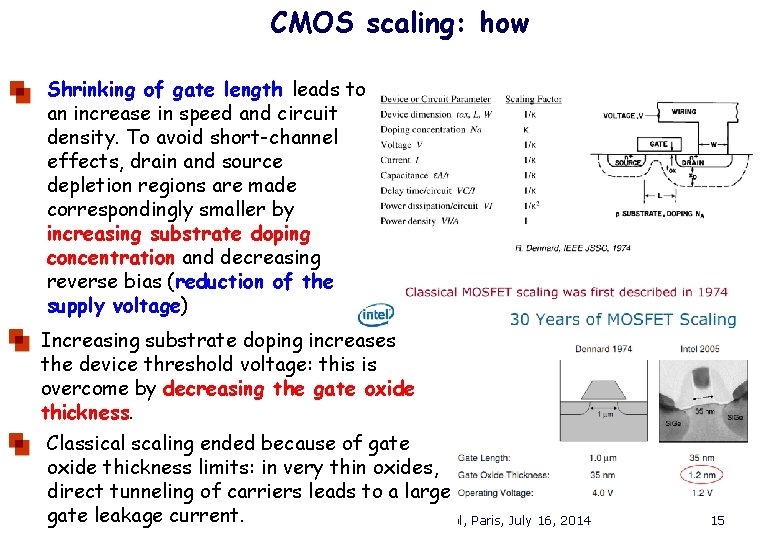

CMOS scaling: how Shrinking of gate length leads to an increase in speed and circuit density. To avoid short-channel effects, drain and source depletion regions are made correspondingly smaller by increasing substrate doping concentration and decreasing reverse bias (reduction of the supply voltage) Increasing substrate doping increases the device threshold voltage: this is overcome by decreasing the gate oxide thickness. Classical scaling ended because of gate oxide thickness limits: in very thin oxides, direct tunneling of carriers leads to a large gate leakage V. current. Re – 2 INFIERI International Summer School, Paris, July 16, 2014 nd 15

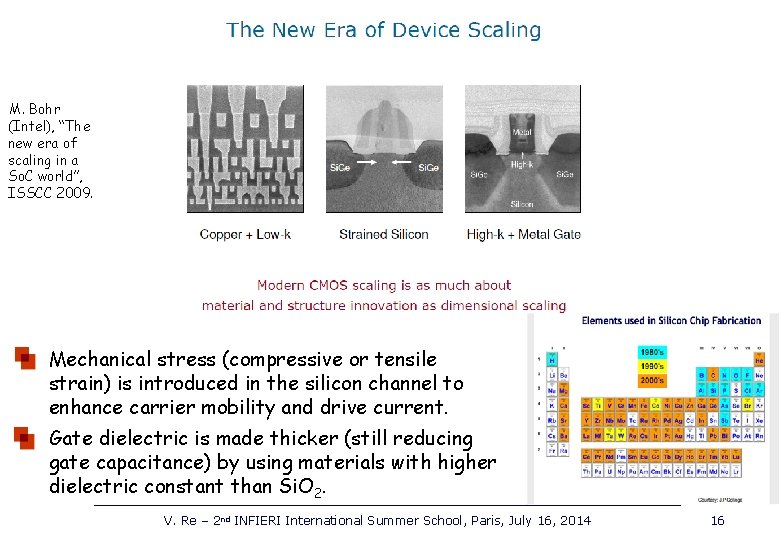

M. Bohr (Intel), “The new era of scaling in a So. C world”, ISSCC 2009. Mechanical stress (compressive or tensile strain) is introduced in the silicon channel to enhance carrier mobility and drive current. Gate dielectric is made thicker (still reducing gate capacitance) by using materials with higher dielectric constant than Si. O 2. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 16

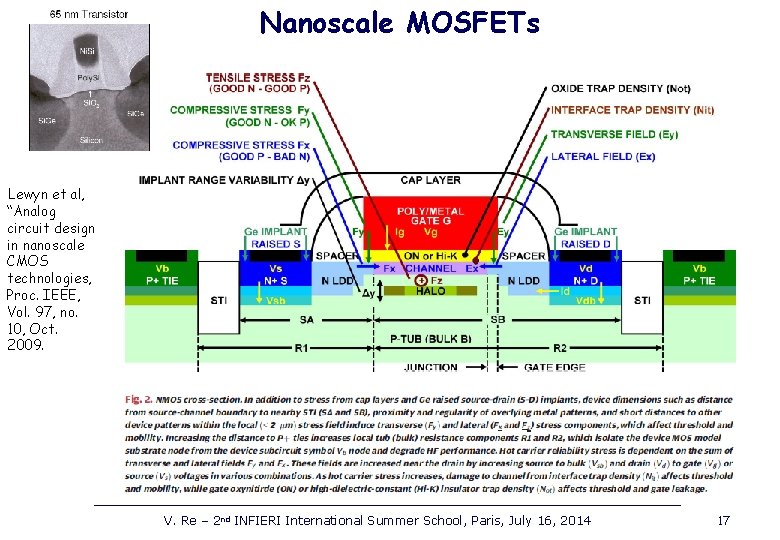

Nanoscale MOSFETs Lewyn et al, “Analog circuit design in nanoscale CMOS technologies, Proc. IEEE, Vol. 97, no. 10, Oct. 2009. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 17

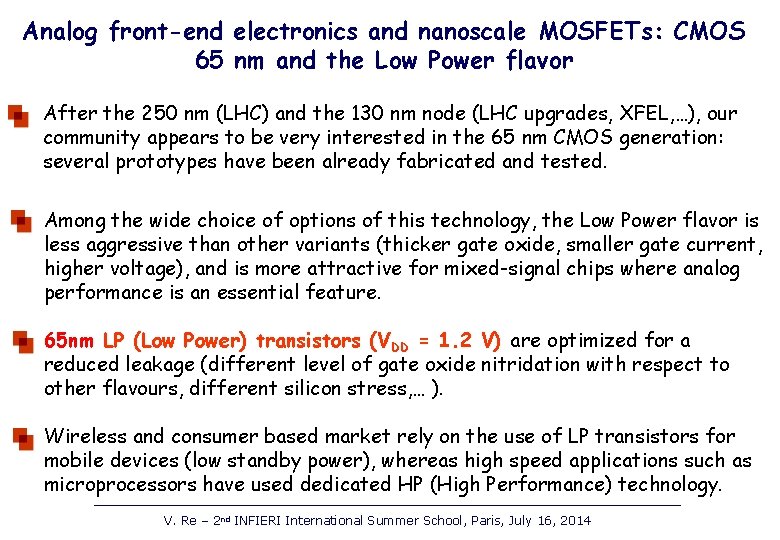

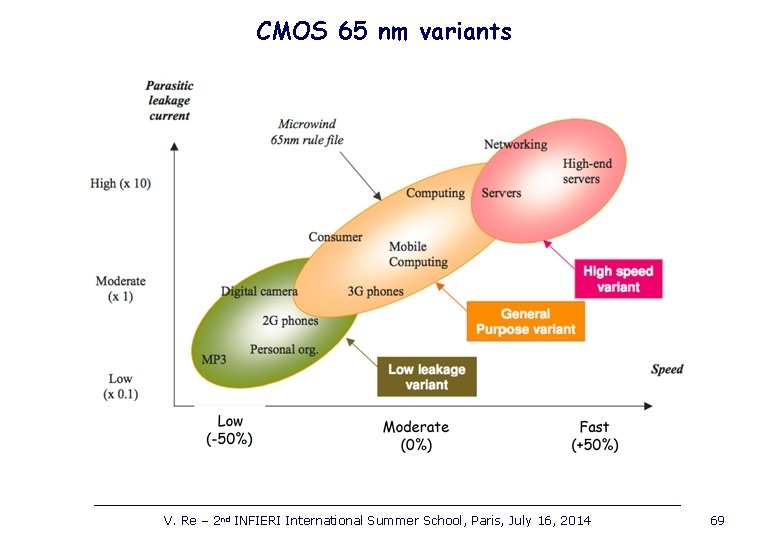

Analog front-end electronics and nanoscale MOSFETs: CMOS 65 nm and the Low Power flavor After the 250 nm (LHC) and the 130 nm node (LHC upgrades, XFEL, …), our community appears to be very interested in the 65 nm CMOS generation: several prototypes have been already fabricated and tested. Among the wide choice of options of this technology, the Low Power flavor is less aggressive than other variants (thicker gate oxide, smaller gate current, higher voltage), and is more attractive for mixed-signal chips where analog performance is an essential feature. 65 nm LP (Low Power) transistors (VDD = 1. 2 V) are optimized for a reduced leakage (different level of gate oxide nitridation with respect to other flavours, different silicon stress, … ). Wireless and consumer based market rely on the use of LP transistors for mobile devices (low standby power), whereas high speed applications such as microprocessors have used dedicated HP (High Performance) technology. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

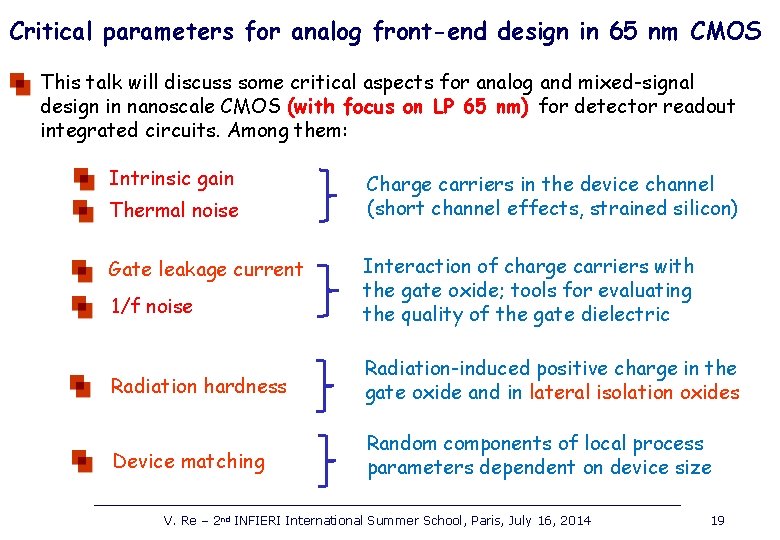

Critical parameters for analog front-end design in 65 nm CMOS This talk will discuss some critical aspects for analog and mixed-signal design in nanoscale CMOS (with focus on LP 65 nm) for detector readout integrated circuits. Among them: Intrinsic gain Thermal noise Charge carriers in the device channel (short channel effects, strained silicon) 1/f noise Interaction of charge carriers with the gate oxide; tools for evaluating the quality of the gate dielectric Radiation hardness Radiation-induced positive charge in the gate oxide and in lateral isolation oxides Device matching Random components of local process parameters dependent on device size Gate leakage current V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 19

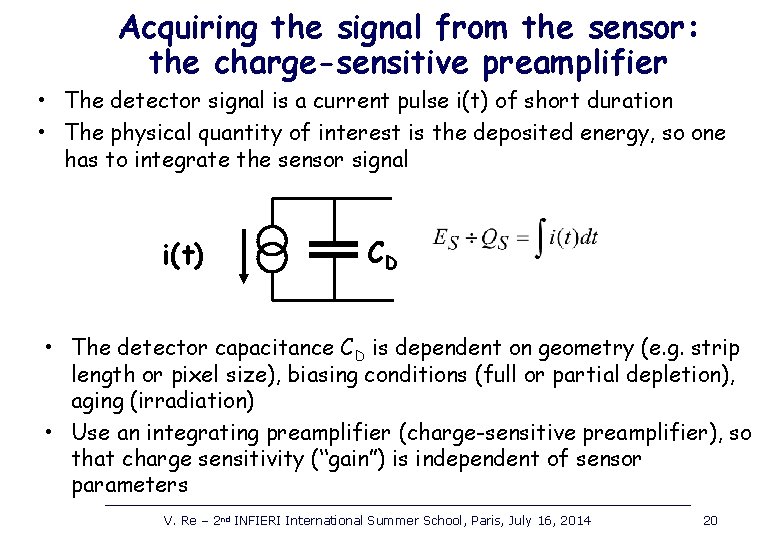

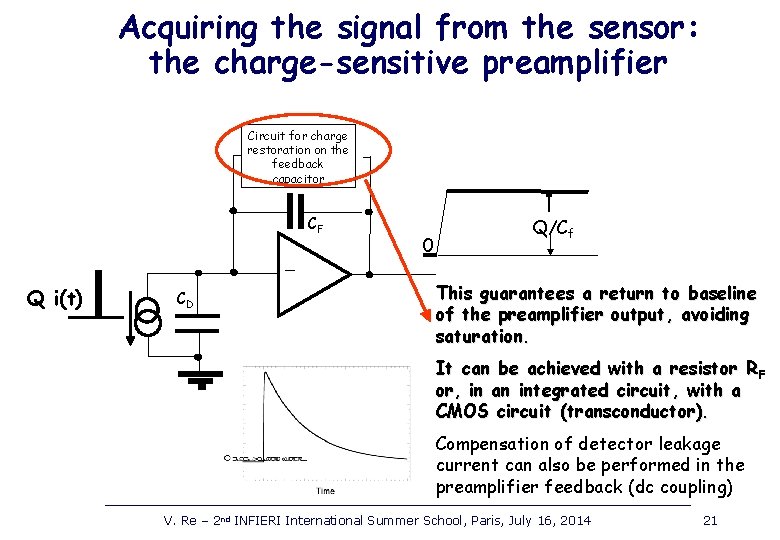

Acquiring the signal from the sensor: the charge-sensitive preamplifier • The detector signal is a current pulse i(t) of short duration • The physical quantity of interest is the deposited energy, so one has to integrate the sensor signal i(t) CD • The detector capacitance CD is dependent on geometry (e. g. strip length or pixel size), biasing conditions (full or partial depletion), aging (irradiation) • Use an integrating preamplifier (charge-sensitive preamplifier), so that charge sensitivity (“gain”) is independent of sensor parameters V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 20

Acquiring the signal from the sensor: the charge-sensitive preamplifier Circuit for charge restoration on the feedback capacitor CF _ Q i(t) CD 0 Q/Cf This guarantees a return to baseline of the preamplifier output, avoiding saturation. It can be achieved with a resistor RF or, in an integrated circuit, with a CMOS circuit (transconductor). Compensation of detector leakage current can also be performed in the preamplifier feedback (dc coupling) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 21

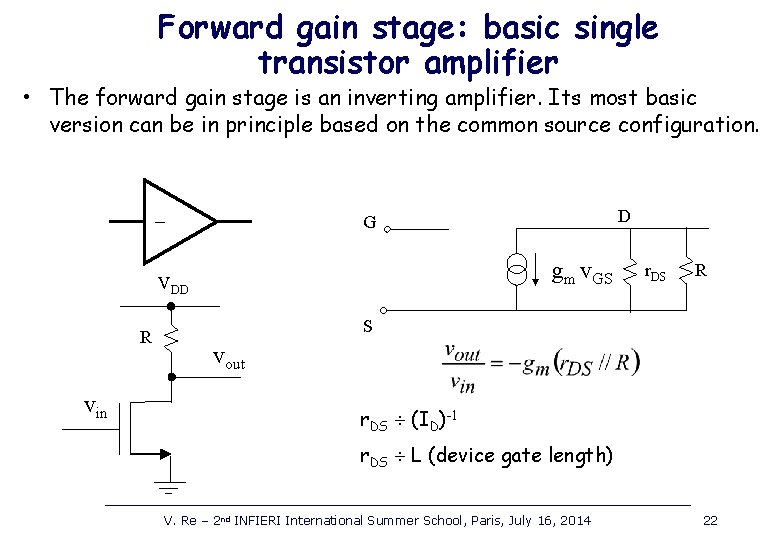

Forward gain stage: basic single transistor amplifier • The forward gain stage is an inverting amplifier. Its most basic version can be in principle based on the common source configuration. _ gm v. GS VDD R vin D G r. DS R S vout r. DS (ID)-1 r. DS L (device gate length) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 22

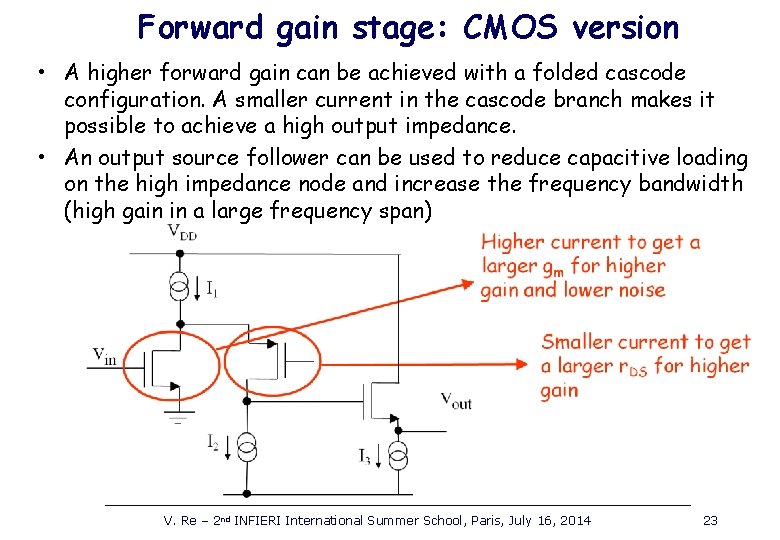

Forward gain stage: CMOS version • A higher forward gain can be achieved with a folded cascode configuration. A smaller current in the cascode branch makes it possible to achieve a high output impedance. • An output source follower can be used to reduce capacitive loading on the high impedance node and increase the frequency bandwidth (high gain in a large frequency span) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 23

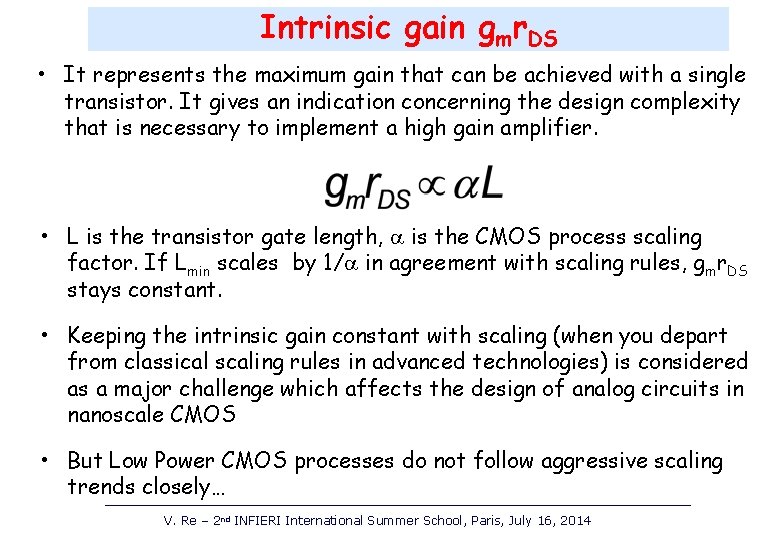

Intrinsic gain gmr. DS • It represents the maximum gain that can be achieved with a single transistor. It gives an indication concerning the design complexity that is necessary to implement a high gain amplifier. • L is the transistor gate length, a is the CMOS process scaling factor. If Lmin scales by 1/a in agreement with scaling rules, gmr. DS stays constant. • Keeping the intrinsic gain constant with scaling (when you depart from classical scaling rules in advanced technologies) is considered as a major challenge which affects the design of analog circuits in nanoscale CMOS • But Low Power CMOS processes do not follow aggressive scaling trends closely… V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

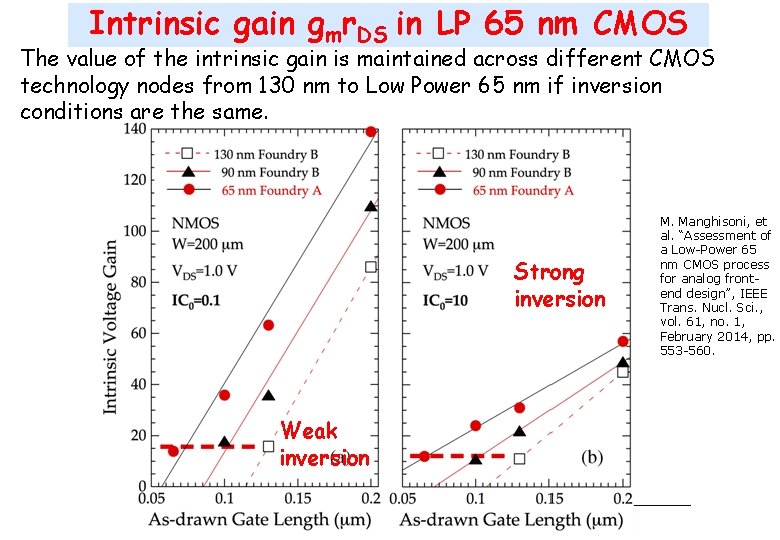

Intrinsic gain gmr. DS in LP 65 nm CMOS The value of the intrinsic gain is maintained across different CMOS technology nodes from 130 nm to Low Power 65 nm if inversion conditions are the same. Strong inversion Weak inversion V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 M. Manghisoni, et al. “Assessment of a Low-Power 65 nm CMOS process for analog frontend design”, IEEE Trans. Nucl. Sci. , vol. 61, no. 1, February 2014, pp. 553 -560.

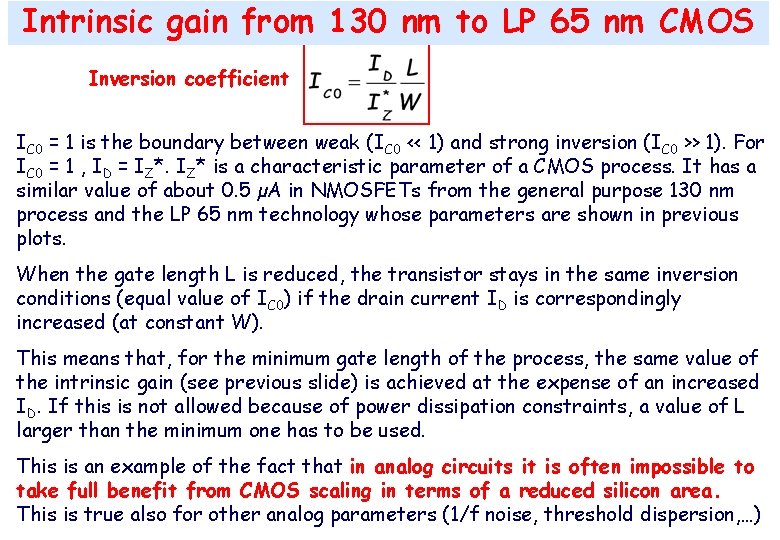

Intrinsic gain from 130 nm to LP 65 nm CMOS Inversion coefficient IC 0 = 1 is the boundary between weak (IC 0 << 1) and strong inversion (IC 0 >> 1). For IC 0 = 1 , ID = IZ* is a characteristic parameter of a CMOS process. It has a similar value of about 0. 5 µA in NMOSFETs from the general purpose 130 nm process and the LP 65 nm technology whose parameters are shown in previous plots. When the gate length L is reduced, the transistor stays in the same inversion conditions (equal value of IC 0) if the drain current ID is correspondingly increased (at constant W). This means that, for the minimum gate length of the process, the same value of the intrinsic gain (see previous slide) is achieved at the expense of an increased ID. If this is not allowed because of power dissipation constraints, a value of L larger than the minimum one has to be used. This is an example of the fact that in analog circuits it is often impossible to take full benefit from CMOS scaling in terms of a reduced silicon area. This is true also. V. for analog parameters (1/f. Paris, noise, threshold dispersion, …) Re –other 2 INFIERI International Summer School, July 16, 2014 nd

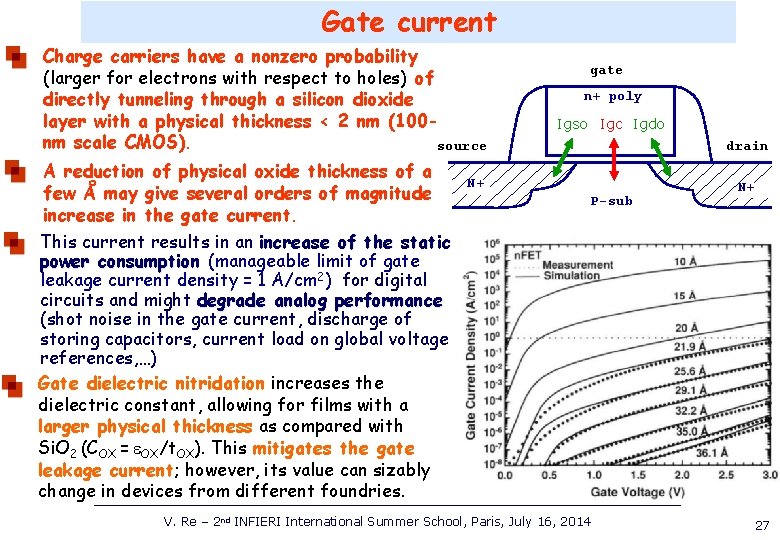

Gate current Charge carriers have a nonzero probability (larger for electrons with respect to holes) of directly tunneling through a silicon dioxide layer with a physical thickness < 2 nm (100 nm scale CMOS). source A reduction of physical oxide thickness of a few Å may give several orders of magnitude increase in the gate current. gate n+ poly Igso Igc Igdo drain N+ P-sub N+ This current results in an increase of the static power consumption (manageable limit of gate leakage current density = 1 A/cm 2) for digital circuits and might degrade analog performance (shot noise in the gate current, discharge of storing capacitors, current load on global voltage references, …) Gate dielectric nitridation increases the dielectric constant, allowing for films with a larger physical thickness as compared with Si. O 2 (COX = e. OX/t. OX). This mitigates the gate leakage current; however, its value can sizably change in devices from different foundries. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 27

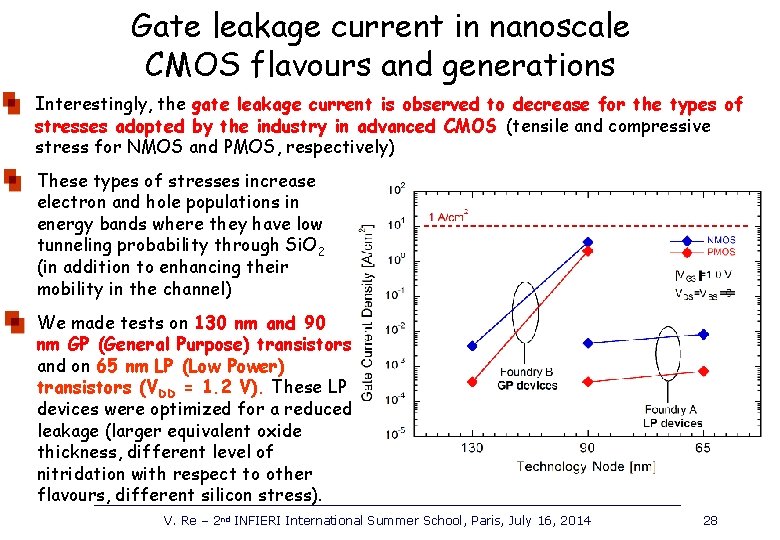

Gate leakage current in nanoscale CMOS flavours and generations Interestingly, the gate leakage current is observed to decrease for the types of stresses adopted by the industry in advanced CMOS (tensile and compressive stress for NMOS and PMOS, respectively) These types of stresses increase electron and hole populations in energy bands where they have low tunneling probability through Si. O 2 (in addition to enhancing their mobility in the channel) We made tests on 130 nm and 90 nm GP (General Purpose) transistors and on 65 nm LP (Low Power) transistors (VDD = 1. 2 V). These LP devices were optimized for a reduced leakage (larger equivalent oxide thickness, different level of nitridation with respect to other flavours, different silicon stress). V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 28

Gate current in LP 65 nm CMOS The value of the gate current is maintained across different CMOS technology nodes from 130 nm to 65 nm (Low Power version) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

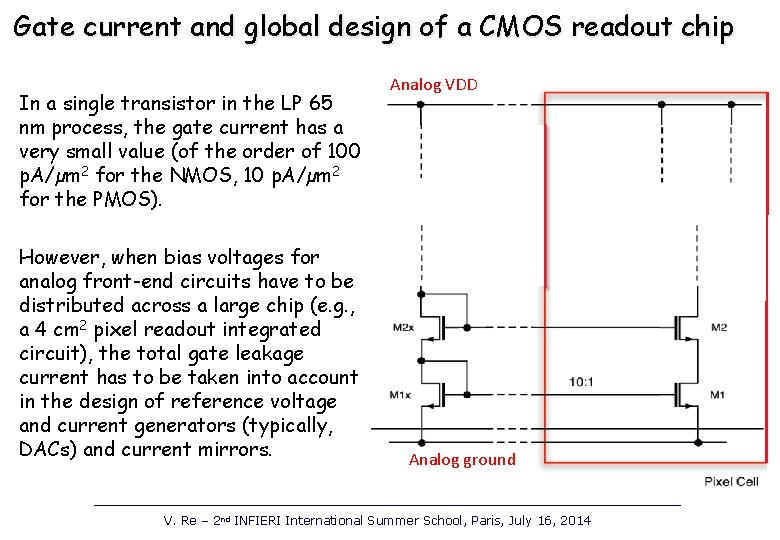

Gate current and global design of a CMOS readout chip In a single transistor in the LP 65 nm process, the gate current has a very small value (of the order of 100 p. A/µm 2 for the NMOS, 10 p. A/µm 2 for the PMOS). However, when bias voltages for analog front-end circuits have to be distributed across a large chip (e. g. , a 4 cm 2 pixel readout integrated circuit), the total gate leakage current has to be taken into account in the design of reference voltage and current generators (typically, DACs) and current mirrors. Analog VDD Analog ground V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

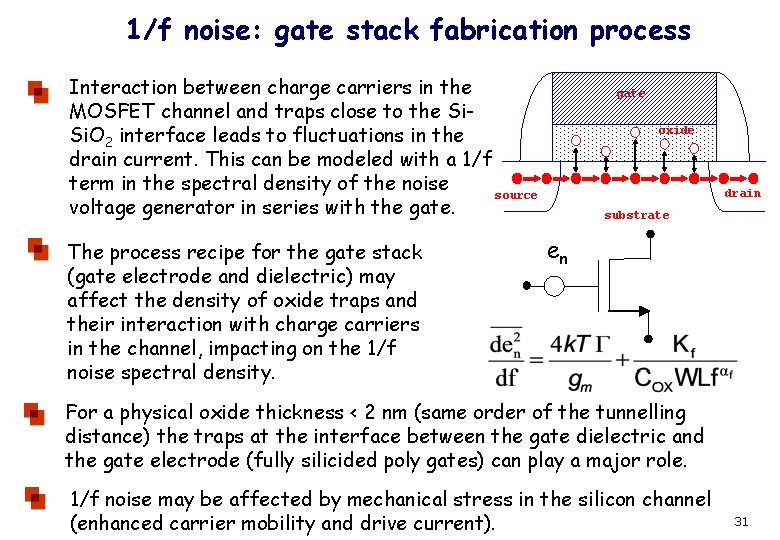

1/f noise: gate stack fabrication process Interaction between charge carriers in the MOSFET channel and traps close to the Si. O 2 interface leads to fluctuations in the drain current. This can be modeled with a 1/f term in the spectral density of the noise source voltage generator in series with the gate. The process recipe for the gate stack (gate electrode and dielectric) may affect the density of oxide traps and their interaction with charge carriers in the channel, impacting on the 1/f noise spectral density. gate oxide drain substrate en For a physical oxide thickness < 2 nm (same order of the tunnelling distance) the traps at the interface between the gate dielectric and the gate electrode (fully silicided poly gates) can play a major role. 1/f noise may be affected by mechanical stress in the silicon channel Re – 2 INFIERI International Summercurrent). School, Paris, July 16, 2014 (enhanced V. carrier mobility and drive nd 31

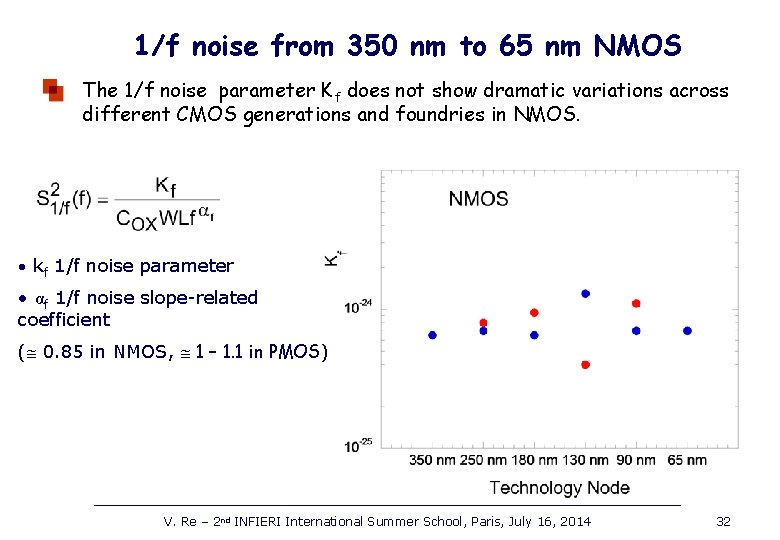

1/f noise from 350 nm to 65 nm NMOS The 1/f noise parameter Kf does not show dramatic variations across different CMOS generations and foundries in NMOS. • kf 1/f noise parameter • αf 1/f noise slope-related coefficient ( 0. 85 in NMOS, 1 – 1. 1 in PMOS) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 32

1/f noise in PMOS: CMOS generations from 250 nm to 90 nm 1/f noise appears to increase (for a same WLCOX) with CMOS scaling V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 33

1/f noise: NMOS vs PMOS In bulk CMOS, the fact that PMOSFETs feature a smaller 1/f noise with respect to equally sized NMOSFETs was generally related to buried channel conduction. In deep submicron processes, it was expected that the PMOS would behave as a surface channel device, rather than a buried channel one as in older CMOS generations. With an inversion layer closer to the oxide interface, 1/f noise is expected to increase. Ultimately, PMOSFETs should feature the same 1/f noise properties as NMOSFETs. However, this was not observed in CMOS generations down to 130 nm and 90 nm. A possible interpretation can be related to the different interaction of electrons (NMOS) and holes (PMOS) with traps in the gate dielectric (different barrier energies experienced by holes and electrons across the Si/Si. O 2 interface). V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 34

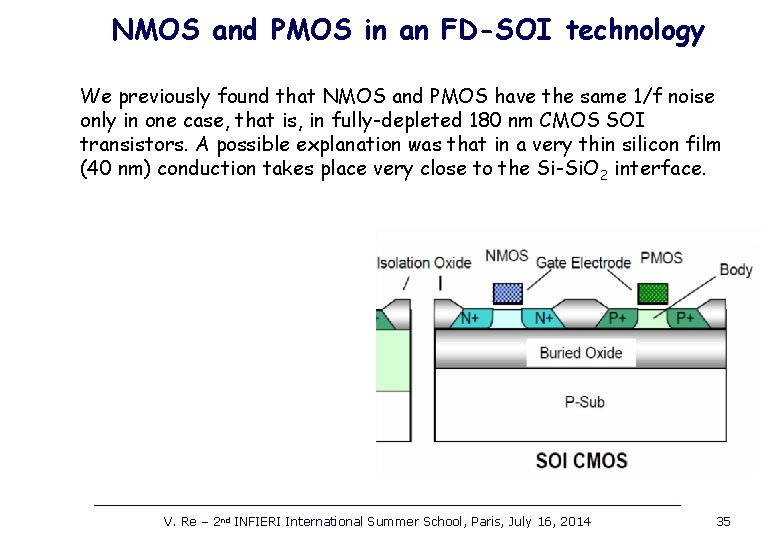

NMOS and PMOS in an FD-SOI technology We previously found that NMOS and PMOS have the same 1/f noise only in one case, that is, in fully-depleted 180 nm CMOS SOI transistors. A possible explanation was that in a very thin silicon film (40 nm) conduction takes place very close to the Si-Si. O 2 interface. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 35

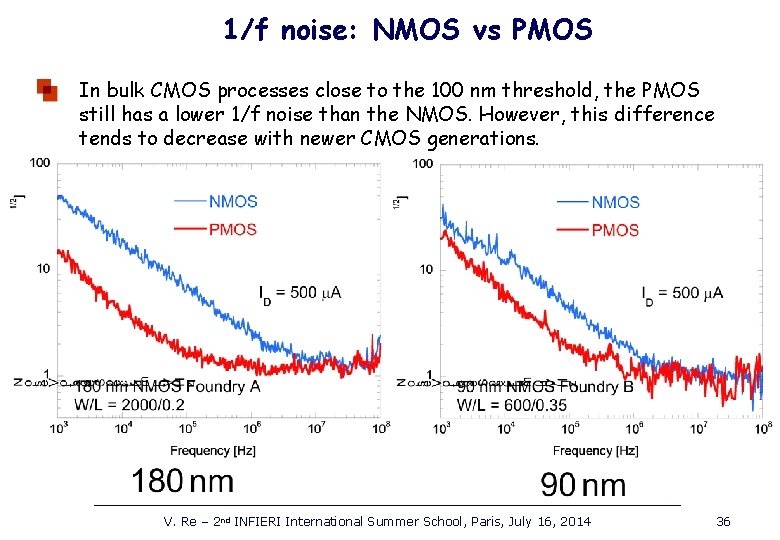

1/f noise: NMOS vs PMOS In bulk CMOS processes close to the 100 nm threshold, the PMOS still has a lower 1/f noise than the NMOS. However, this difference tends to decrease with newer CMOS generations. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 36

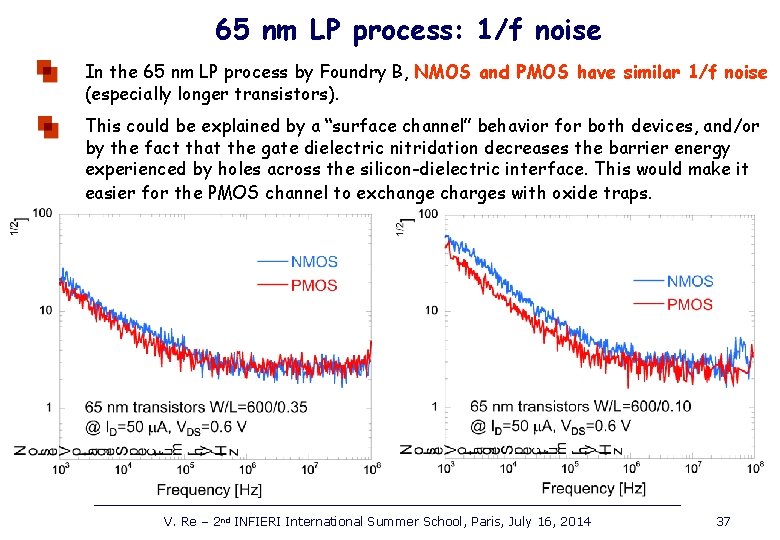

65 nm LP process: 1/f noise In the 65 nm LP process by Foundry B, NMOS and PMOS have similar 1/f noise (especially longer transistors). This could be explained by a “surface channel” behavior for both devices, and/or by the fact that the gate dielectric nitridation decreases the barrier energy experienced by holes across the silicon-dielectric interface. This would make it easier for the PMOS channel to exchange charges with oxide traps. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 37

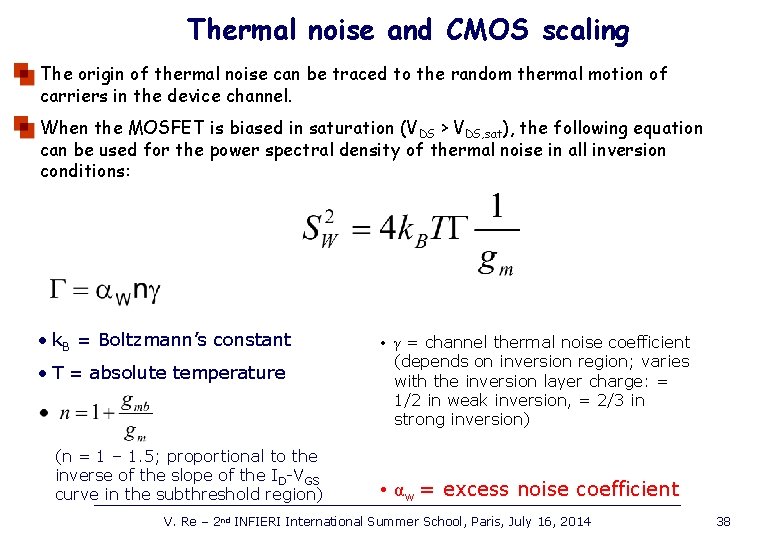

Thermal noise and CMOS scaling The origin of thermal noise can be traced to the random thermal motion of carriers in the device channel. When the MOSFET is biased in saturation (VDS > VDS, sat), the following equation can be used for the power spectral density of thermal noise in all inversion conditions: • k. B = Boltzmann’s constant • T = absolute temperature (n = 1 – 1. 5; proportional to the inverse of the slope of the ID-VGS curve in the subthreshold region) • γ = channel thermal noise coefficient (depends on inversion region; varies with the inversion layer charge: = 1/2 in weak inversion, = 2/3 in strong inversion) • αw = excess noise coefficient V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 38

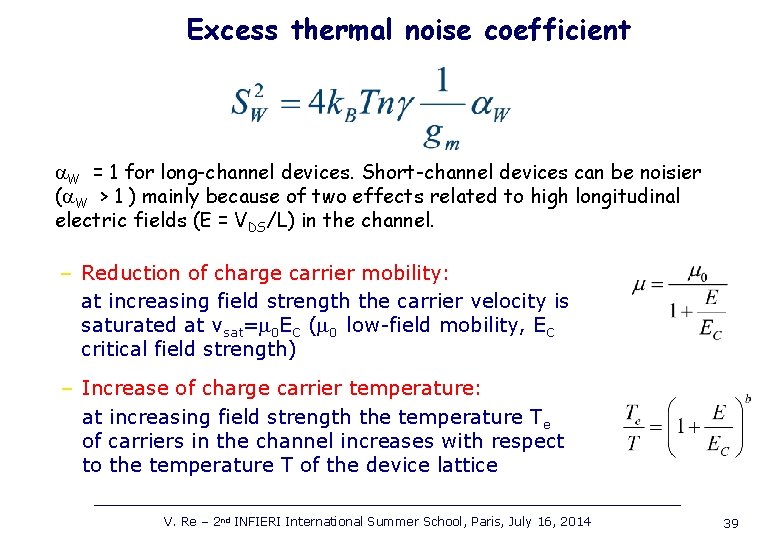

Excess thermal noise coefficient a. W = 1 for long-channel devices. Short-channel devices can be noisier (a. W > 1 ) mainly because of two effects related to high longitudinal electric fields (E = VDS/L) in the channel. – Reduction of charge carrier mobility: at increasing field strength the carrier velocity is saturated at vsat= 0 EC ( 0 low-field mobility, EC critical field strength) – Increase of charge carrier temperature: at increasing field strength the temperature Te of carriers in the channel increases with respect to the temperature T of the device lattice V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 39

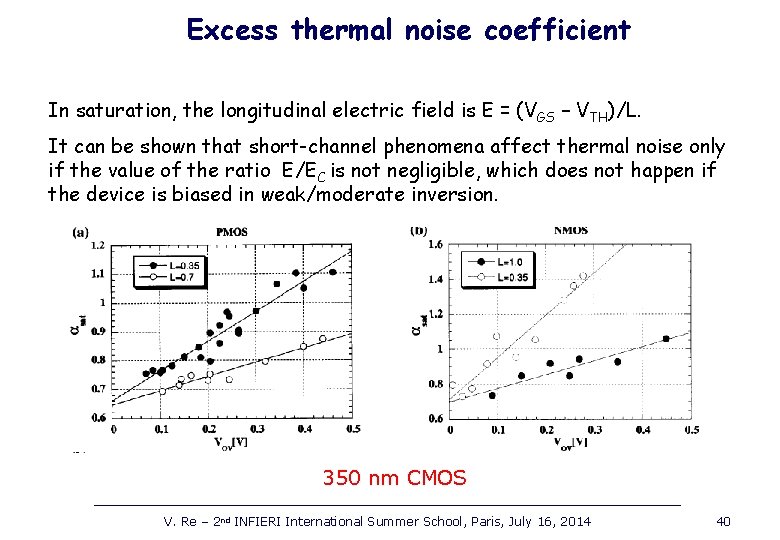

Excess thermal noise coefficient In saturation, the longitudinal electric field is E = (V GS – VTH)/L. It can be shown that short-channel phenomena affect thermal noise only if the value of the ratio E/EC is not negligible, which does not happen if the device is biased in weak/moderate inversion. 350 nm CMOS V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 40

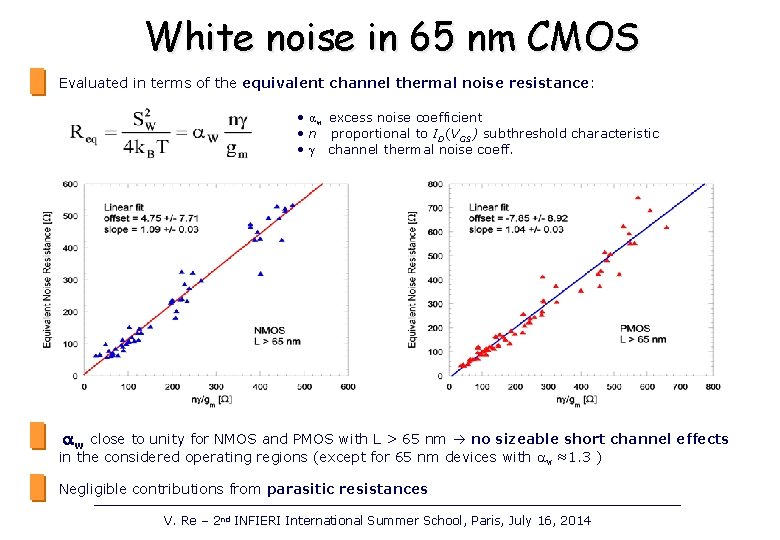

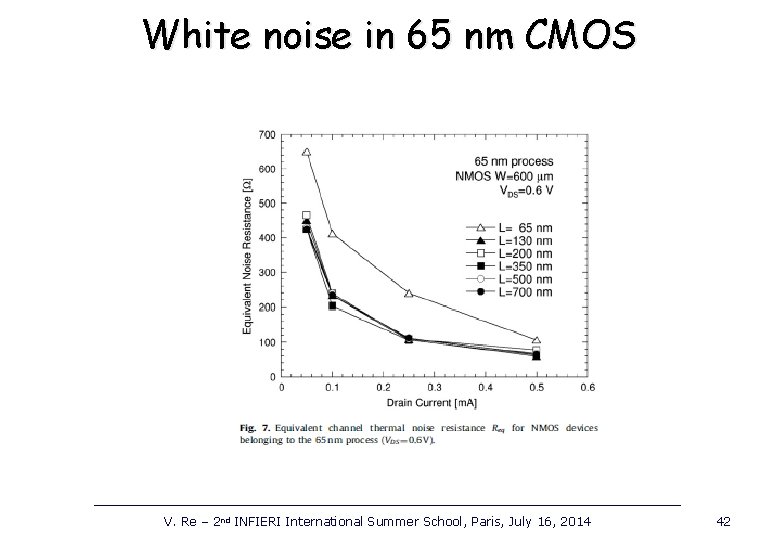

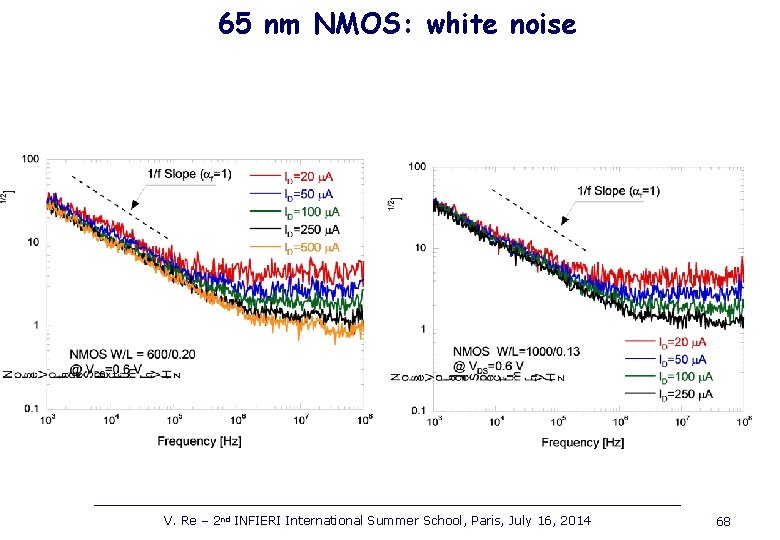

White noise in 65 nm CMOS Evaluated in terms of the equivalent channel thermal noise resistance: • αw excess noise coefficient • n proportional to ID(VGS) subthreshold characteristic • γ channel thermal noise coeff. aw close to unity for NMOS and PMOS with L > 65 nm no sizeable short channel effects in the considered operating regions (except for 65 nm devices with aw ≈1. 3 ) Negligible contributions from parasitic resistances V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

White noise in 65 nm CMOS V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 42

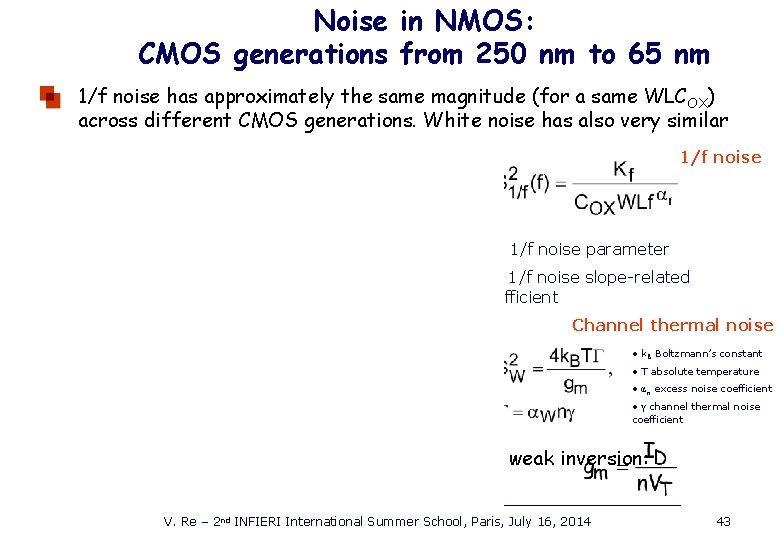

Noise in NMOS: CMOS generations from 250 nm to 65 nm 1/f noise has approximately the same magnitude (for a same WLC OX) across different CMOS generations. White noise has also very similar properties (weak/moderate inversion). 1/f noise • kf 1/f noise parameter • αf 1/f noise slope-related coefficient Channel thermal noise • k. B Boltzmann’s constant • T absolute temperature • αw excess noise coefficient • γ channel thermal noise coefficient In weak inversion: V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 43

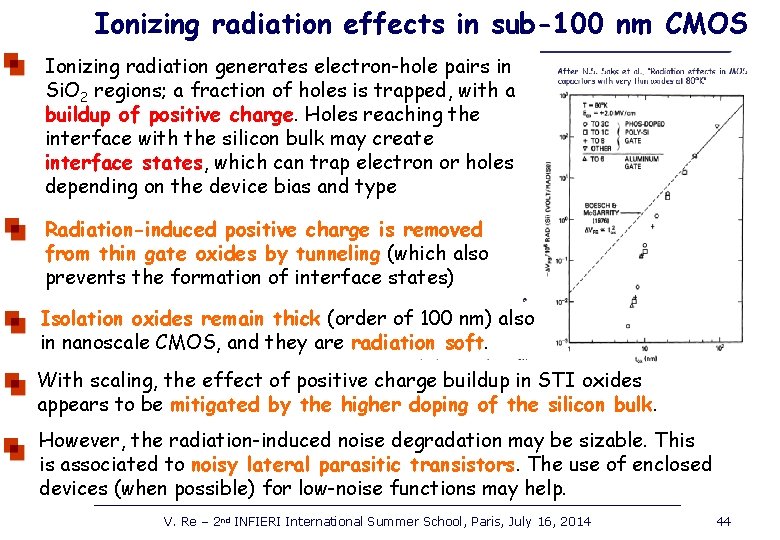

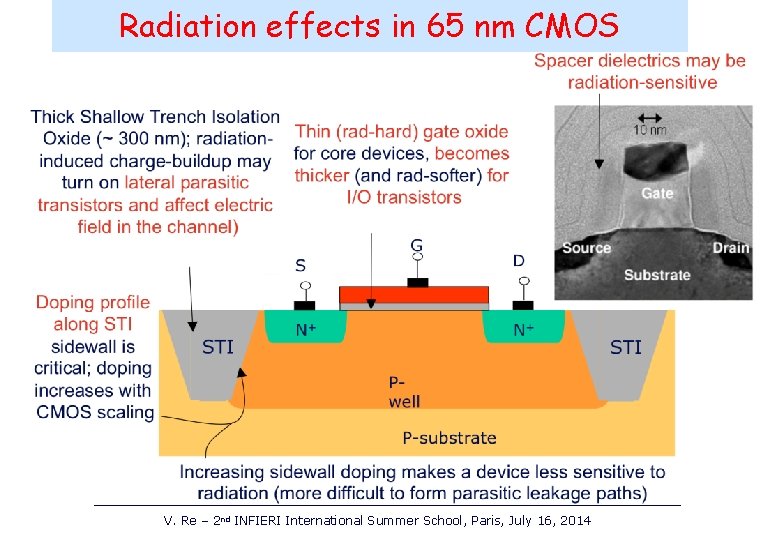

Ionizing radiation effects in sub-100 nm CMOS Ionizing radiation generates electron-hole pairs in Si. O 2 regions; a fraction of holes is trapped, with a buildup of positive charge. Holes reaching the interface with the silicon bulk may create interface states, which can trap electron or holes depending on the device bias and type Radiation-induced positive charge is removed from thin gate oxides by tunneling (which also prevents the formation of interface states) Isolation oxides remain thick (order of 100 nm) also in nanoscale CMOS, and they are radiation soft. With scaling, the effect of positive charge buildup in STI oxides appears to be mitigated by the higher doping of the silicon bulk. However, the radiation-induced noise degradation may be sizable. This is associated to noisy lateral parasitic transistors. The use of enclosed devices (when possible) for low-noise functions may help. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 44

Radiation effects in 65 nm CMOS V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

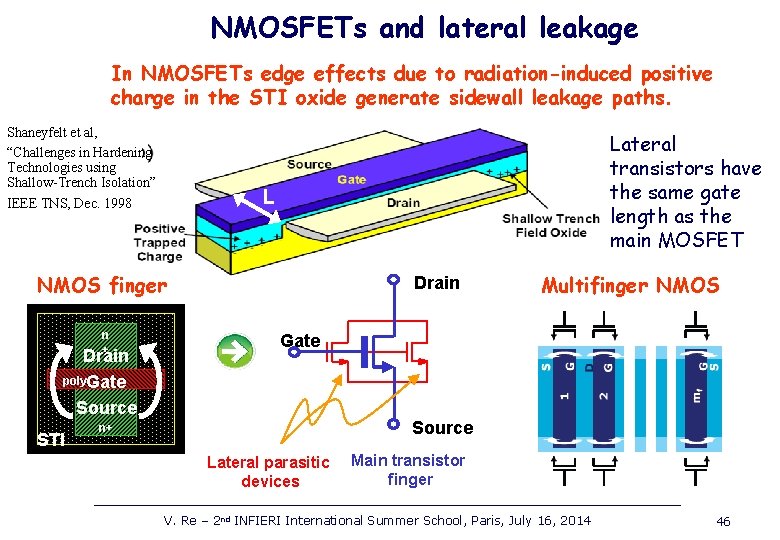

NMOSFETs and lateral leakage In NMOSFETs edge effects due to radiation-induced positive charge in the STI oxide generate sidewall leakage paths. Shaneyfelt et al, “Challenges in Hardening Technologies using Shallow-Trench Isolation” IEEE TNS, Dec. 1998 Lateral transistors have the same gate length as the main MOSFET L NMOS finger n + Drain poly. Gate Source STI Drain Multifinger NMOS Gate Source n+ Lateral parasitic devices Main transistor finger V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 46

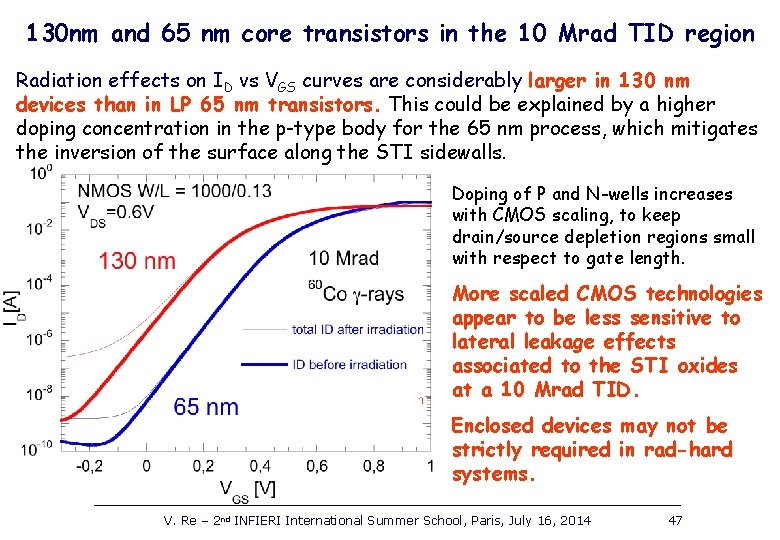

130 nm and 65 nm core transistors in the 10 Mrad TID region Radiation effects on ID vs VGS curves are considerably larger in 130 nm devices than in LP 65 nm transistors. This could be explained by a higher doping concentration in the p-type body for the 65 nm process, which mitigates the inversion of the surface along the STI sidewalls. Doping of P and N-wells increases with CMOS scaling, to keep drain/source depletion regions small with respect to gate length. More scaled CMOS technologies appear to be less sensitive to lateral leakage effects associated to the STI oxides at a 10 Mrad TID. Enclosed devices may not be strictly required in rad-hard systems. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 47

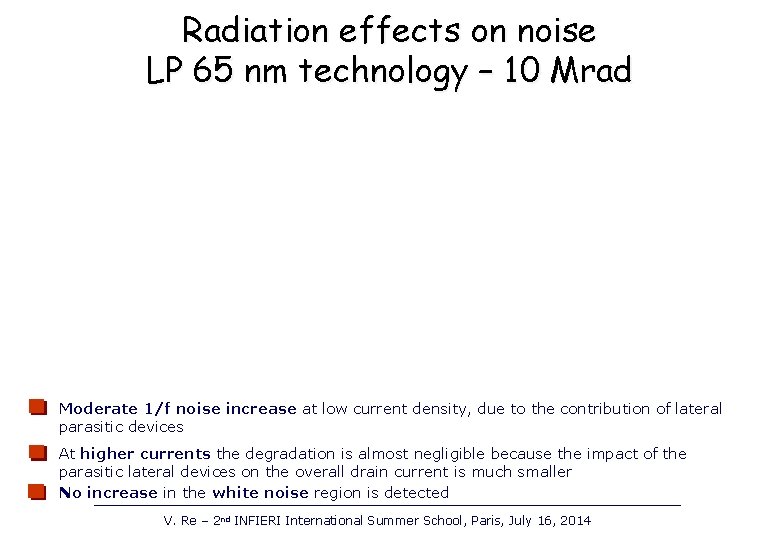

Radiation effects on noise LP 65 nm technology – 10 Mrad Moderate 1/f noise increase at low current density, due to the contribution of lateral parasitic devices At higher currents the degradation is almost negligible because the impact of the parasitic lateral devices on the overall drain current is much smaller No increase in the white noise region is detected V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

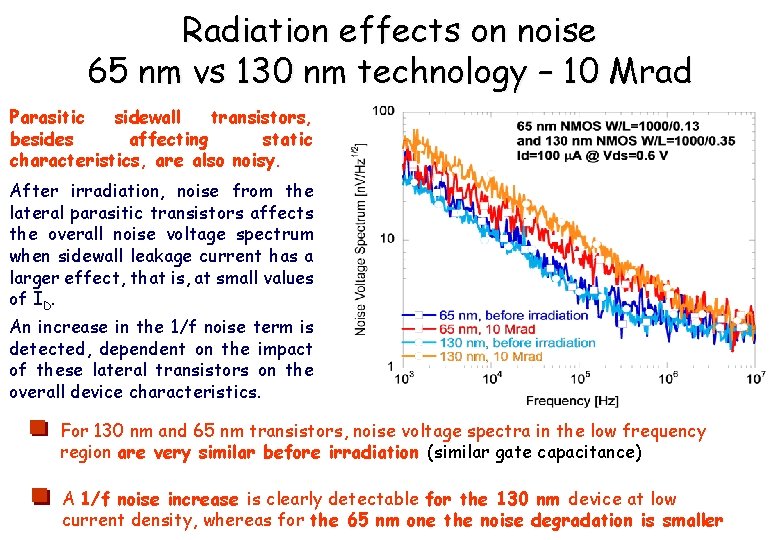

Radiation effects on noise 65 nm vs 130 nm technology – 10 Mrad Parasitic sidewall transistors, besides affecting static characteristics, are also noisy. After irradiation, noise from the lateral parasitic transistors affects the overall noise voltage spectrum when sidewall leakage current has a larger effect, that is, at small values of ID. An increase in the 1/f noise term is detected, dependent on the impact of these lateral transistors on the overall device characteristics. For 130 nm and 65 nm transistors, noise voltage spectra in the low frequency region are very similar before irradiation (similar gate capacitance) A 1/f noise increase is clearly detectable for the 130 nm device at low V. Re –whereas 2 nd INFIERIfor International School, Julydegradation 16, 2014 current density, the 65 Summer nm one the. Paris, noise is smaller

65 nm transistors at extreme total ionizing dose: the PMOS M. Barbero, G. Deptuch, FEE 2014 workshop, Argonne Nat. Lab • Among other effects, PMOSFETs (especially minimum size ones) show a large transconductance degradation, which becomes very steep at TID > 100 Mrad (partial recover after annealing) • Damage mechanisms at 1 Grad (LHC phase II upgrade, innermost pixel layer) have yet to be fully understood (including dependence on geometry and bias conditions under irradiation and annealing, dose rate, temperature, radiation source…) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

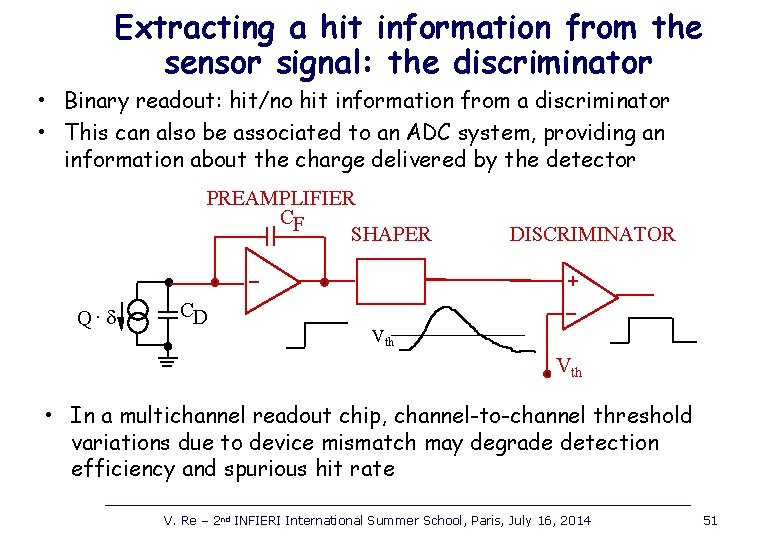

Extracting a hit information from the sensor signal: the discriminator • Binary readout: hit/no hit information from a discriminator • This can also be associated to an ADC system, providing an information about the charge delivered by the detector PREAMPLIFIER CF SHAPER Q. d CD DISCRIMINATOR Vth • In a multichannel readout chip, channel-to-channel threshold variations due to device mismatch may degrade detection efficiency and spurious hit rate V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 51

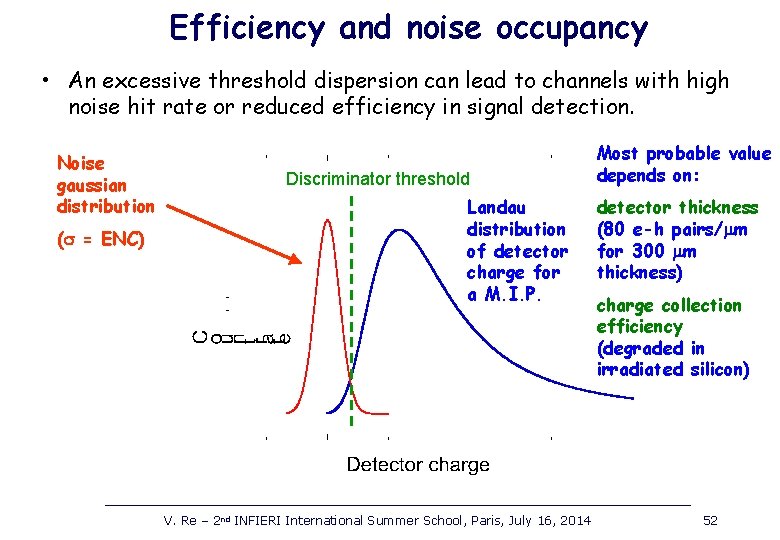

Efficiency and noise occupancy • An excessive threshold dispersion can lead to channels with high noise hit rate or reduced efficiency in signal detection. Noise gaussian distribution (s = ENC) Discriminator threshold Landau distribution of detector charge for a M. I. P. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 Most probable value depends on: detector thickness (80 e-h pairs/mm for 300 mm thickness) charge collection efficiency (degraded in irradiated silicon) 52

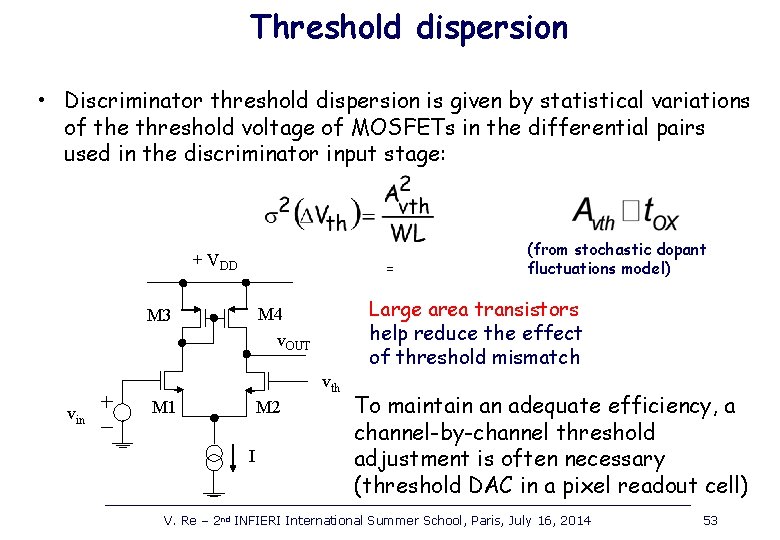

Threshold dispersion • Discriminator threshold dispersion is given by statistical variations of the threshold voltage of MOSFETs in the differential pairs used in the discriminator input stage: (from stochastic dopant fluctuations model) + VDD Large area transistors help reduce the effect of threshold mismatch M 4 v. OUT M 3 vth vin M 2 M 1 I To maintain an adequate efficiency, a channel-by-channel threshold adjustment is often necessary (threshold DAC in a pixel readout cell) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 53

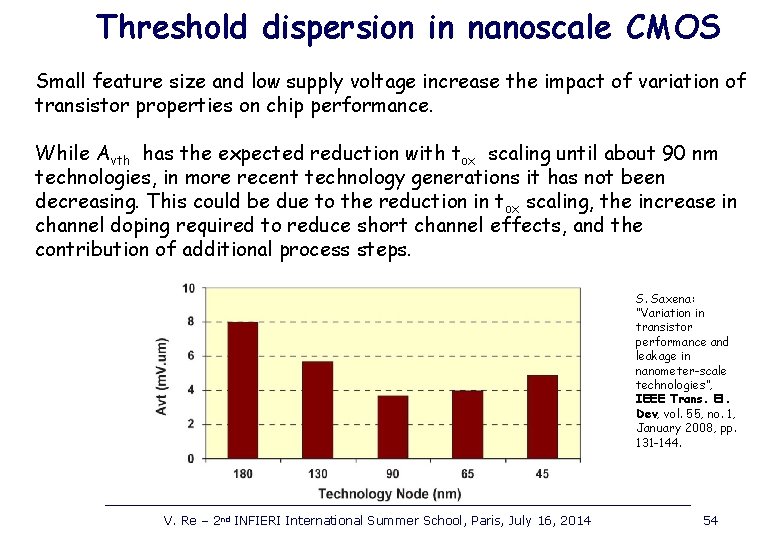

Threshold dispersion in nanoscale CMOS Small feature size and low supply voltage increase the impact of variation of transistor properties on chip performance. While Avth has the expected reduction with tox scaling until about 90 nm technologies, in more recent technology generations it has not been decreasing. This could be due to the reduction in tox scaling, the increase in channel doping required to reduce short channel effects, and the contribution of additional process steps. S. Saxena: “Variation in transistor performance and leakage in nanometer-scale technologies”, IEEE Trans. El. Dev, vol. 55, no. 1, January 2008, pp. 131 -144. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 54

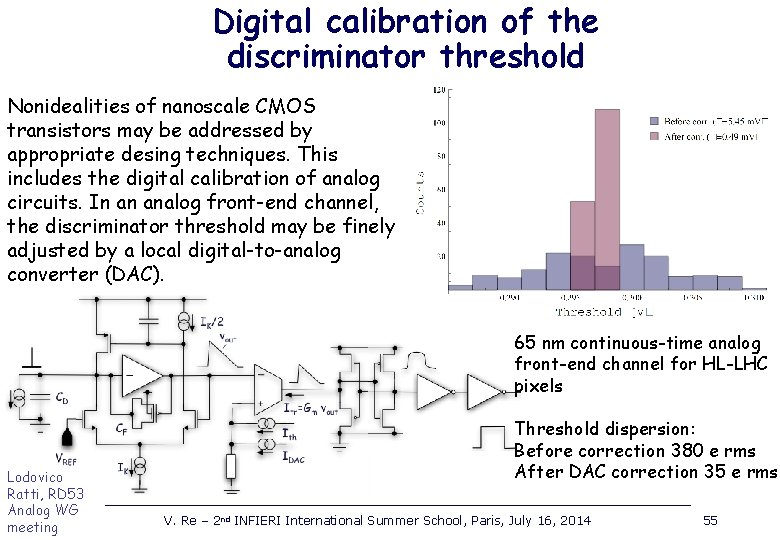

Digital calibration of the discriminator threshold Nonidealities of nanoscale CMOS transistors may be addressed by appropriate desing techniques. This includes the digital calibration of analog circuits. In an analog front-end channel, the discriminator threshold may be finely adjusted by a local digital-to-analog converter (DAC). 65 nm continuous-time analog front-end channel for HL-LHC pixels Lodovico Ratti, RD 53 Analog WG meeting Threshold dispersion: Before correction 380 e rms After DAC correction 35 e rms V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 55

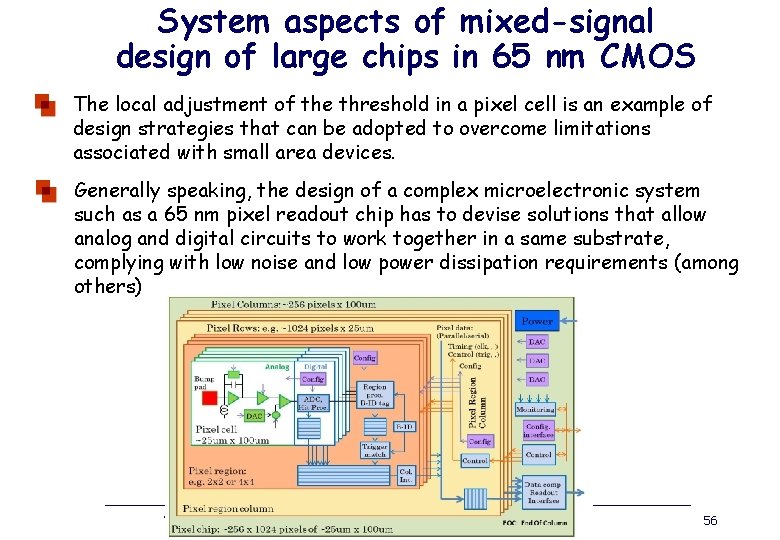

System aspects of mixed-signal design of large chips in 65 nm CMOS The local adjustment of the threshold in a pixel cell is an example of design strategies that can be adopted to overcome limitations associated with small area devices. Generally speaking, the design of a complex microelectronic system such as a 65 nm pixel readout chip has to devise solutions that allow analog and digital circuits to work together in a same substrate, complying with low noise and low power dissipation requirements (among others) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 56

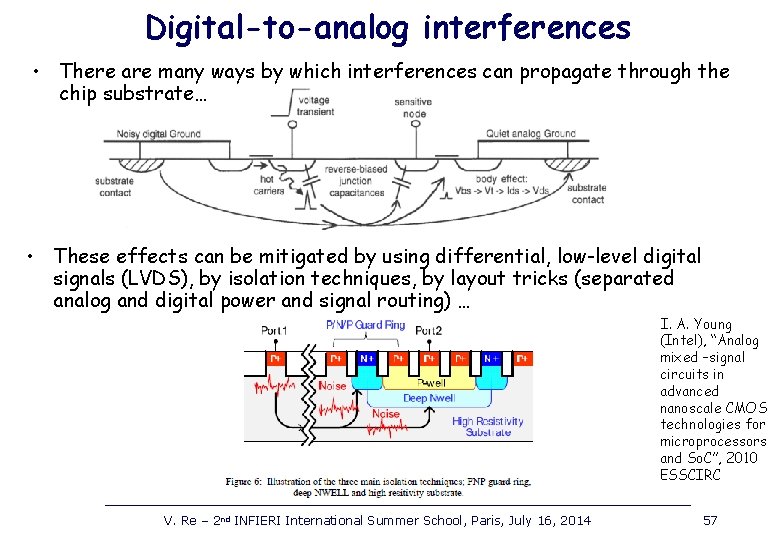

Digital-to-analog interferences • There are many ways by which interferences can propagate through the chip substrate… • These effects can be mitigated by using differential, low-level digital signals (LVDS), by isolation techniques, by layout tricks (separated analog and digital power and signal routing) … I. A. Young (Intel), “Analog mixed –signal circuits in advanced nanoscale CMOS technologies for microprocessors and So. C”, 2010 ESSCIRC V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 57

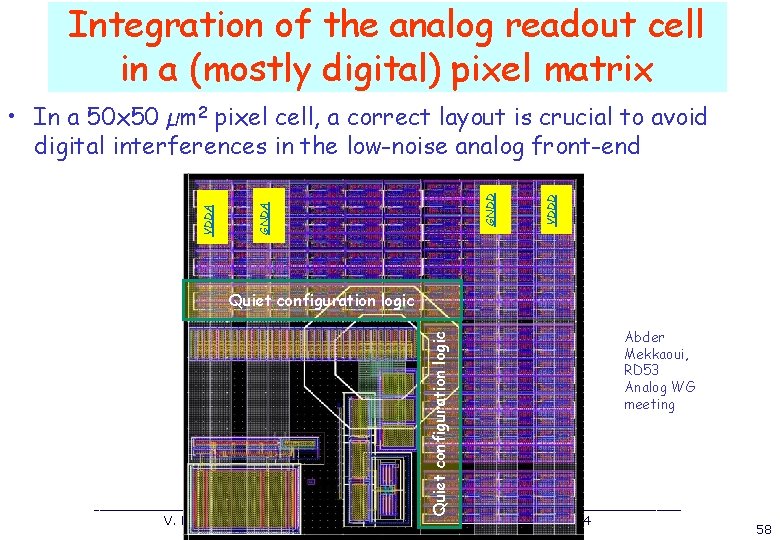

Integration of the analog readout cell in a (mostly digital) pixel matrix VDDD GNDA VDDA • In a 50 x 50 µm 2 pixel cell, a correct layout is crucial to avoid digital interferences in the low-noise analog front-end Quiet configuration logic V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 Abder Mekkaoui, RD 53 Analog WG meeting 58

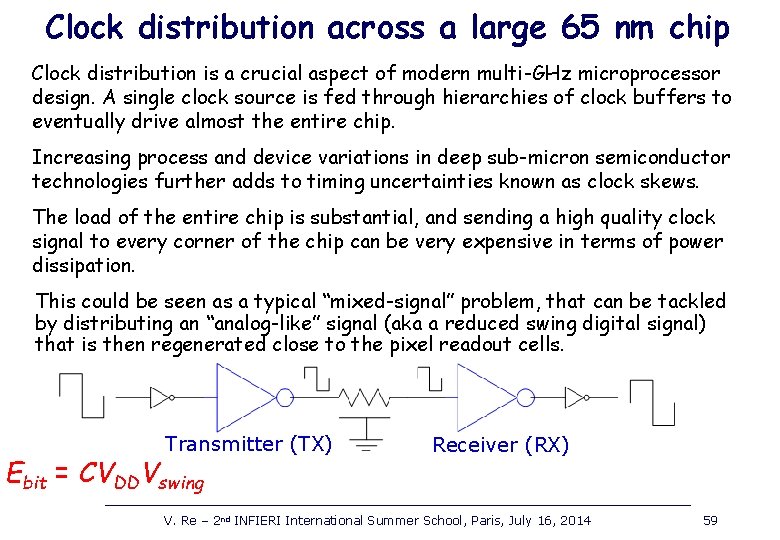

Clock distribution across a large 65 nm chip Clock distribution is a crucial aspect of modern multi-GHz microprocessor design. A single clock source is fed through hierarchies of clock buffers to eventually drive almost the entire chip. Increasing process and device variations in deep sub-micron semiconductor technologies further adds to timing uncertainties known as clock skews. The load of the entire chip is substantial, and sending a high quality clock signal to every corner of the chip can be very expensive in terms of power dissipation. This could be seen as a typical “mixed-signal” problem, that can be tackled by distributing an “analog-like” signal (aka a reduced swing digital signal) that is then regenerated close to the pixel readout cells. Transmitter (TX) Ebit = CVDDVswing Receiver (RX) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 59

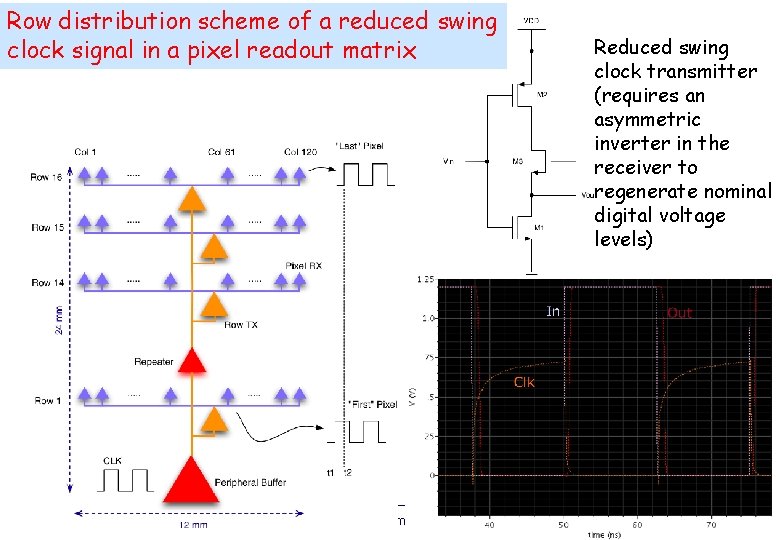

Row distribution scheme of a reduced swing clock signal in a pixel readout matrix V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 Reduced swing clock transmitter (requires an asymmetric inverter in the receiver to regenerate nominal digital voltage levels) 60

Conclusions Nanoscale MOSFETs have very interesting new features in terms of device processing and physics. At the 65 nm node, low-noise design of analog circuits in mixedsignal detector readout chips is challenging but, according to the study of key analog parameters, appears to be still viable in the Low Power technology flavor. Microelectronic technology will drive the evolution of particle detection systems as it has done in the last decades Classical analog problems (signal amplification and filtering, noise optimization, minimization of threshold dispersion) require clever solutions Technology watch for novel devices and processes has to continue, since the evolution of microelectronics is not going to end soon. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 61

Backup slides V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 62

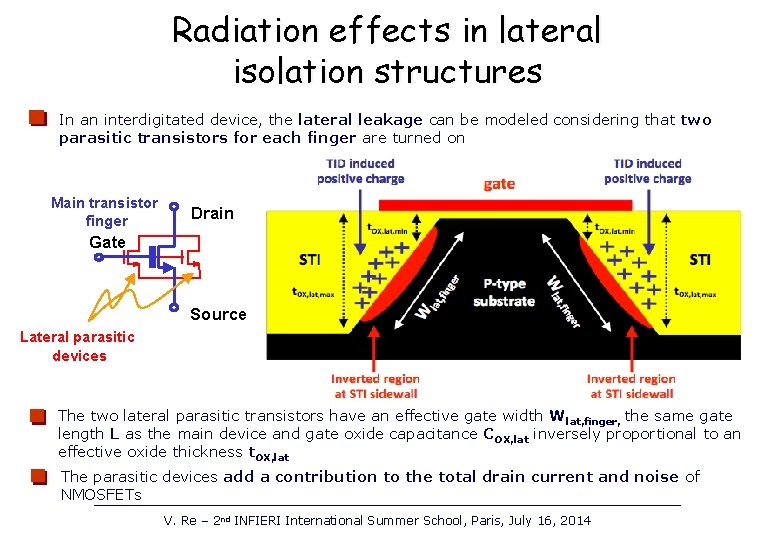

Radiation effects in lateral isolation structures In an interdigitated device, the lateral leakage can be modeled considering that two parasitic transistors for each finger are turned on Main transistor finger Drain Gate Source Lateral parasitic devices The two lateral parasitic transistors have an effective gate width Wlat, finger, the same gate length L as the main device and gate oxide capacitance COX, lat inversely proportional to an effective oxide thickness t. OX, lat The parasitic devices add a contribution to the total drain current and noise of NMOSFETs V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

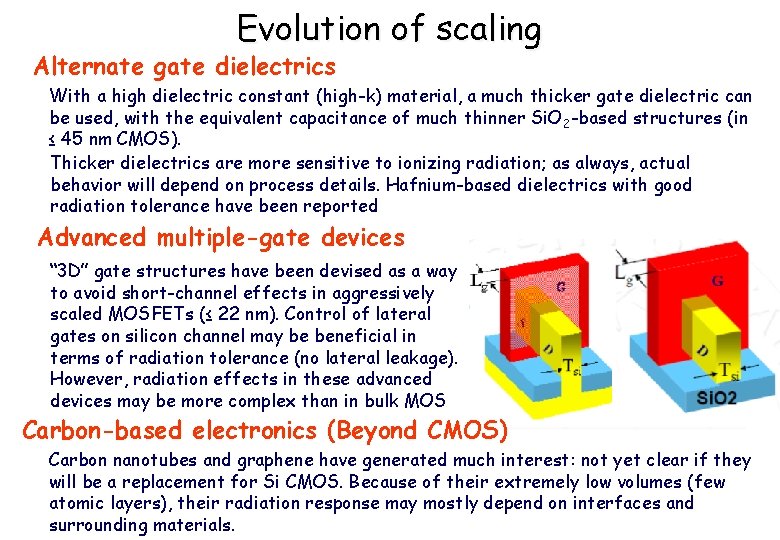

Evolution of scaling Alternate gate dielectrics With a high dielectric constant (high-k) material, a much thicker gate dielectric can be used, with the equivalent capacitance of much thinner Si. O 2 -based structures (in ≤ 45 nm CMOS). Thicker dielectrics are more sensitive to ionizing radiation; as always, actual behavior will depend on process details. Hafnium-based dielectrics with good radiation tolerance have been reported Advanced multiple-gate devices “ 3 D” gate structures have been devised as a way to avoid short-channel effects in aggressively scaled MOSFETs (≤ 22 nm). Control of lateral gates on silicon channel may be beneficial in terms of radiation tolerance (no lateral leakage). However, radiation effects in these advanced devices may be more complex than in bulk MOS Carbon-based electronics (Beyond CMOS) Carbon nanotubes and graphene have generated much interest: not yet clear if they will be a replacement for Si CMOS. Because of their extremely low volumes (few atomic layers), their radiation response may mostly depend on interfaces and V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 surrounding materials.

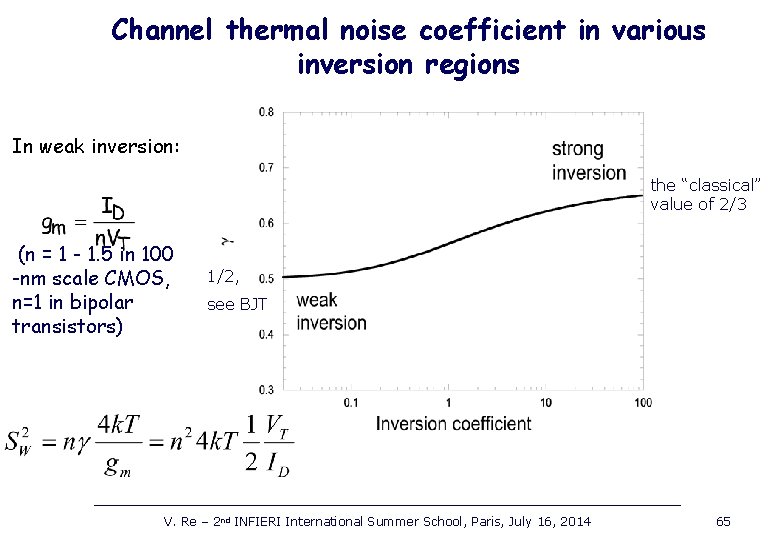

Channel thermal noise coefficient in various inversion regions In weak inversion: the “classical” value of 2/3 (n = 1 - 1. 5 in 100 -nm scale CMOS, n=1 in bipolar transistors) 1/2, see BJT V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 65

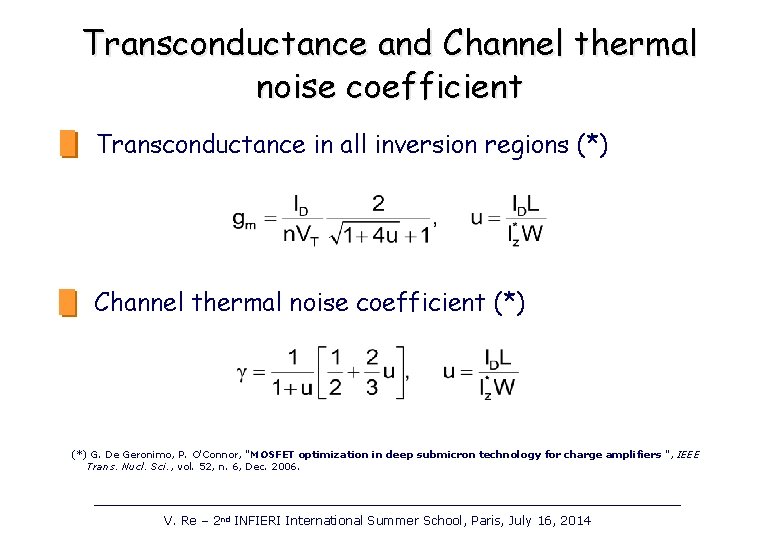

Transconductance and Channel thermal noise coefficient Transconductance in all inversion regions (*) Channel thermal noise coefficient (*) G. De Geronimo, P. O'Connor, "MOSFET optimization in deep submicron technology for charge amplifiers ", IEEE Trans. Nucl. Sci. , vol. 52, n. 6, Dec. 2006. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

![NMOSFETs and lateral leakage D I [A] Ionizing radiation leads to a large negative NMOSFETs and lateral leakage D I [A] Ionizing radiation leads to a large negative](http://slidetodoc.com/presentation_image_h2/d8e35199c2a1e0f7050dd7cb9c34da05/image-67.jpg)

NMOSFETs and lateral leakage D I [A] Ionizing radiation leads to a large negative threshold shift of the equivalent parasitic transistor associated to the thick STI oxide 10 -2 10 -4 10 -6 10 -8 10 -10 Total ID after irradiation Lateral parasitic transistor after irradiation NMOS 130 nm process W=1000 m L=0. 2 m VDS=0. 6 V ID before irradiation 0 0. 5 VGS [V] 1 V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 67

65 nm NMOS: white noise V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 68

CMOS 65 nm variants V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 69

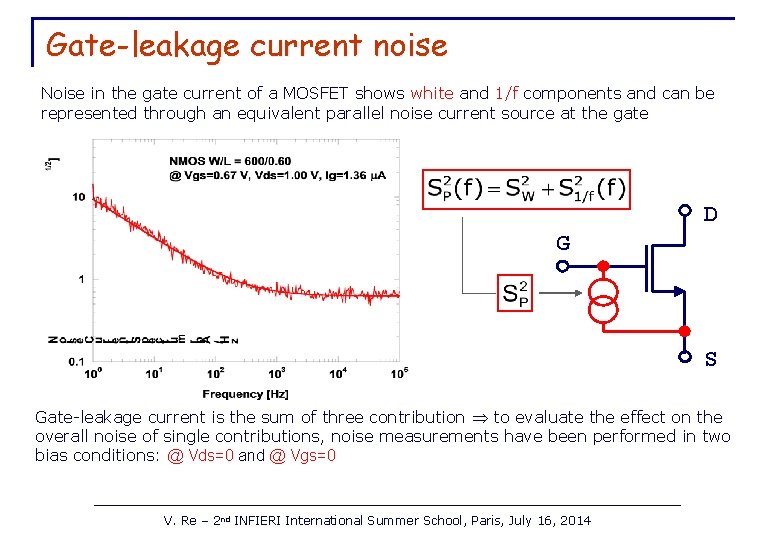

Gate-leakage current noise Noise in the gate current of a MOSFET shows white and 1/f components and can be represented through an equivalent parallel noise current source at the gate D G S Gate-leakage current is the sum of three contribution to evaluate the effect on the overall noise of single contributions, noise measurements have been performed in two bias conditions: @ Vds=0 and @ Vgs=0 V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

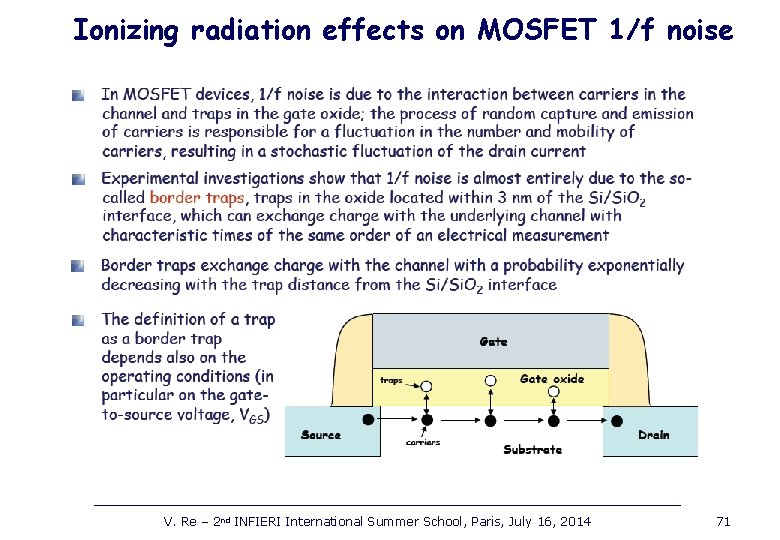

Ionizing radiation effects on MOSFET 1/f noise V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 71

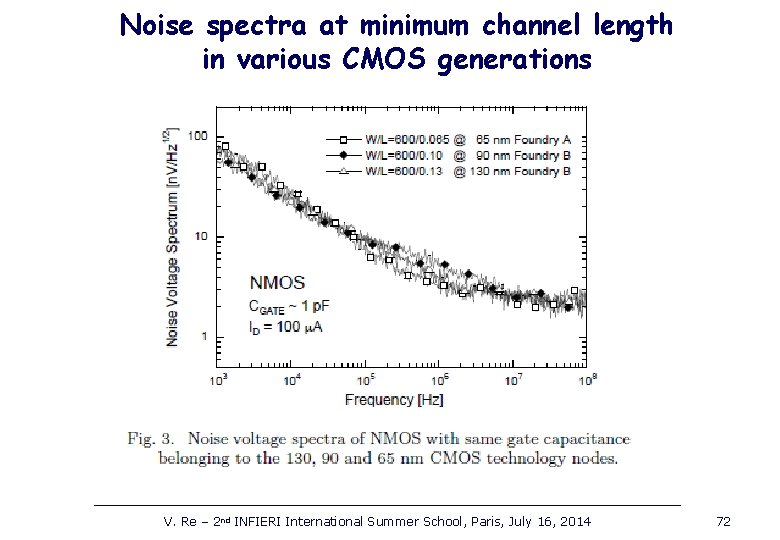

Noise spectra at minimum channel length in various CMOS generations V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 72

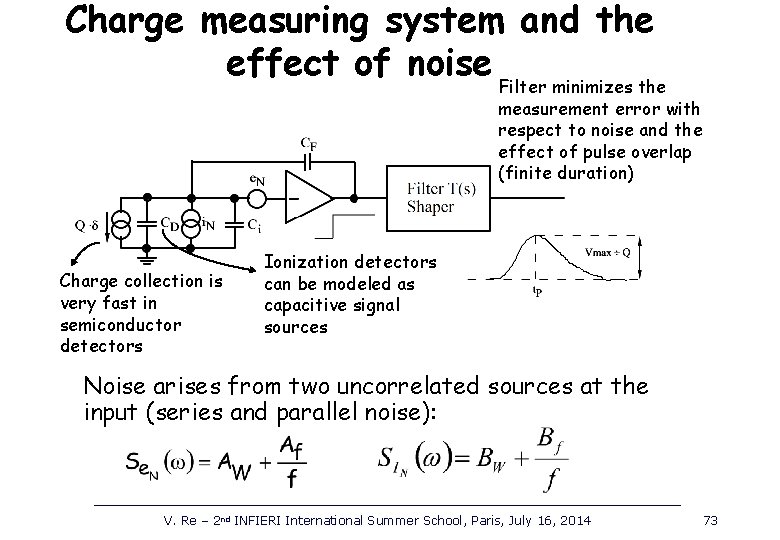

Charge measuring system and the effect of noise Filter minimizes the measurement error with respect to noise and the effect of pulse overlap (finite duration) Charge collection is very fast in semiconductor detectors Ionization detectors can be modeled as capacitive signal sources Noise arises from two uncorrelated sources at the input (series and parallel noise): V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 73

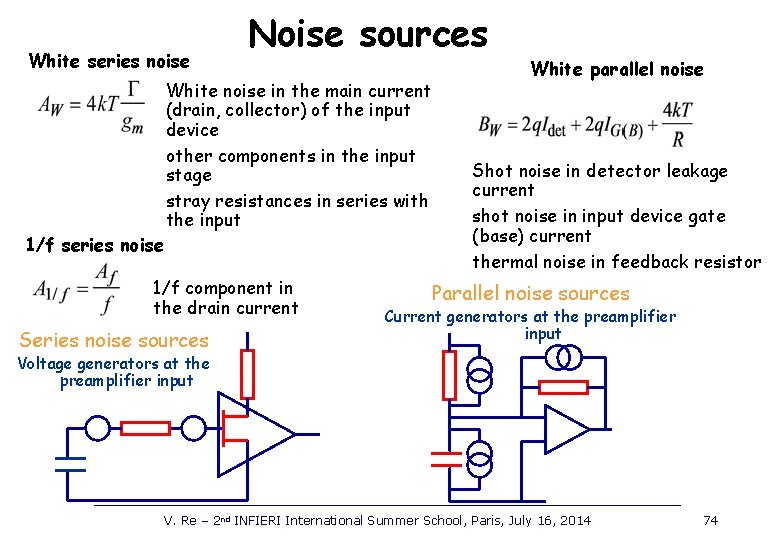

White series noise 1/f series noise Noise sources White noise in the main current (drain, collector) of the input device other components in the input stage stray resistances in series with the input 1/f component in the drain current Series noise sources White parallel noise Shot noise in detector leakage current shot noise in input device gate (base) current thermal noise in feedback resistor Parallel noise sources Current generators at the preamplifier input Voltage generators at the preamplifier input V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 74

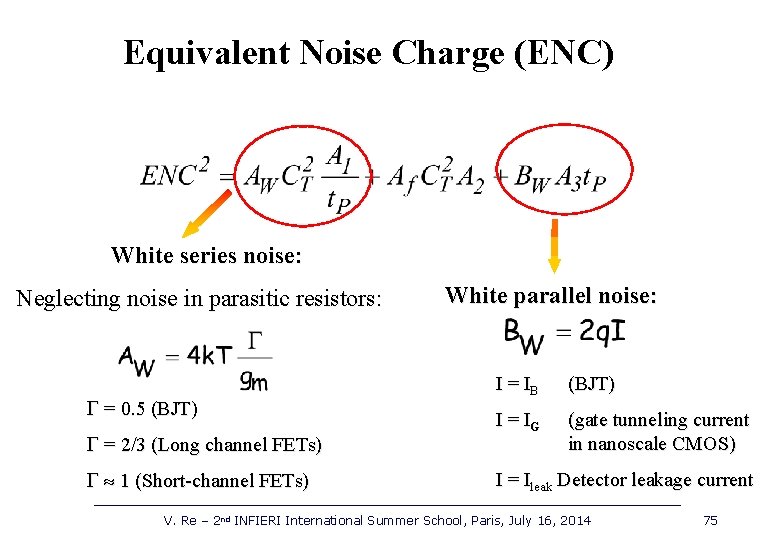

Equivalent Noise Charge (ENC) White series noise: Neglecting noise in parasitic resistors: G = 0. 5 (BJT) G = 2/3 (Long channel FETs) G 1 (Short-channel FETs) White parallel noise: I = IB (BJT) I = IG (gate tunneling current in nanoscale CMOS) I = Ileak Detector leakage current V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 75

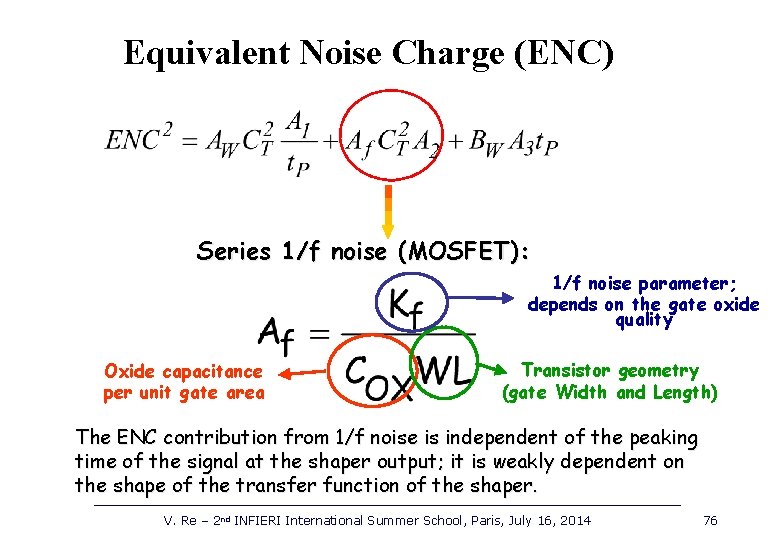

Equivalent Noise Charge (ENC) Series 1/f noise (MOSFET): 1/f noise parameter; depends on the gate oxide quality Oxide capacitance per unit gate area Transistor geometry (gate Width and Length) The ENC contribution from 1/f noise is independent of the peaking time of the signal at the shaper output; it is weakly dependent on the shape of the transfer function of the shaper. V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 76

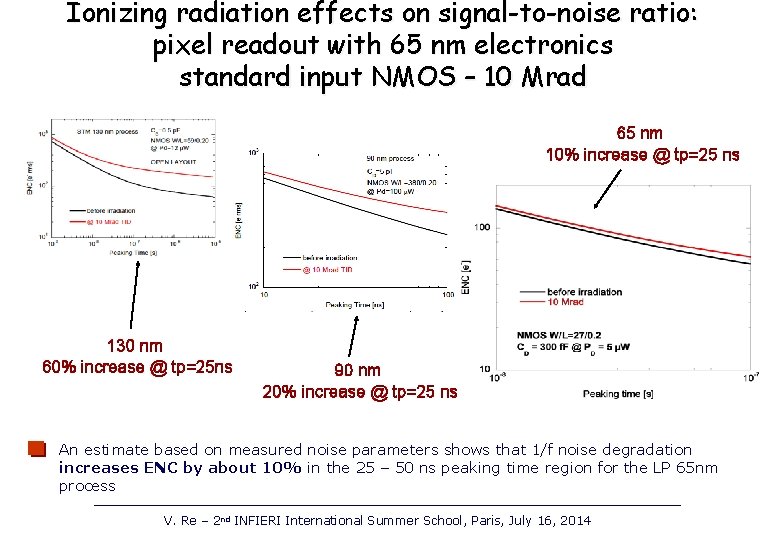

Ionizing radiation effects on signal-to-noise ratio: pixel readout with 65 nm electronics standard input NMOS – 10 Mrad 65 nm 10% increase @ tp=25 ns 130 nm 60% increase @ tp=25 ns 90 nm 20% increase @ tp=25 ns An estimate based on measured noise parameters shows that 1/f noise degradation increases ENC by about 10% in the 25 – 50 ns peaking time region for the LP 65 nm process V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014

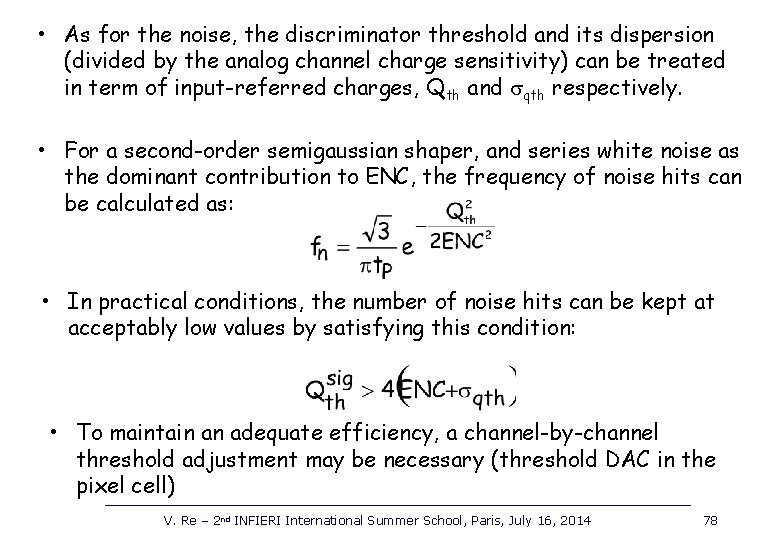

• As for the noise, the discriminator threshold and its dispersion (divided by the analog channel charge sensitivity) can be treated in term of input-referred charges, Qth and sqth respectively. • For a second-order semigaussian shaper, and series white noise as the dominant contribution to ENC, the frequency of noise hits can be calculated as: • In practical conditions, the number of noise hits can be kept at acceptably low values by satisfying this condition: • To maintain an adequate efficiency, a channel-by-channel threshold adjustment may be necessary (threshold DAC in the pixel cell) V. Re – 2 nd INFIERI International Summer School, Paris, July 16, 2014 78

- Slides: 78