Introduction to Verilog ELEE 4303 Digital II Learning

- Slides: 15

Introduction to Verilog ELEE 4303 Digital II

Learning Objectives • Get familiar with background of HDLs • Basic concepts of Verilog languages – Gate level primitives – Module – Ports – Structural and behavioral descriptions – Continuous assignment and procedural statements – Verilog syntax ELEE 4303 Digital II

Hardware Description Languages • A hardware description language is a computer language that is used to describe hardware. • Two HDLs are widely used – Verilog HDL – VHDL (Very High Speed Integrated Circuit Hardware Description Language) • Schematic design entry can be replaced by writing HDL code that CAD tools understand. • CAD tools can verify the HDL codes, and create the circuits automatically from HDL codes. ELEE 4303 Digital II

Facts about Verilog • We use Verilog, not VHDL, in ELEE 4303. – Verilog is more popular in industry than VHDL – They offer similar features • History of Verilog – In 1980 s, originally developed by Gateway Design Automation. – In 1990, was put in public domain. – In 1995, adopted as an IEEE standard 1364 -1995 – In 2001, an enhanced version, Verilog 2001 ELEE 4303 Digital II

Use of Verilog • Functions of Verilog – Design entry, like schematic – Simulation and verification of your design – Synthesis • Verilog is a complex, sophisticated language – We focus on a subset of its features that is synthesizable. – For complete Verilog, refer to reference books. – Verilog will be taught in several stages through this course when the language elements are relevant to the design topics. – Appendix A provides a concise summary of Verilog. ELEE 4303 Digital II

Representation of Digital Circuits in Verilog • Design entry in several different ways – Truth tables – Schematic captures – Hardware description languages (efficient !) • Two types of representations in Verilog – Structural – Behavioral ELEE 4303 Digital II

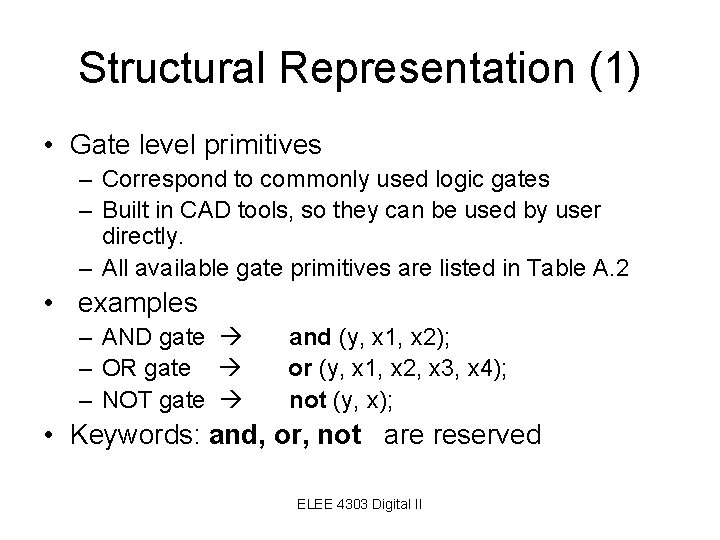

Structural Representation (1) • Gate level primitives – Correspond to commonly used logic gates – Built in CAD tools, so they can be used by user directly. – All available gate primitives are listed in Table A. 2 • examples – AND gate – OR gate – NOT gate and (y, x 1, x 2); or (y, x 1, x 2, x 3, x 4); not (y, x); • Keywords: and, or, not are reserved ELEE 4303 Digital II

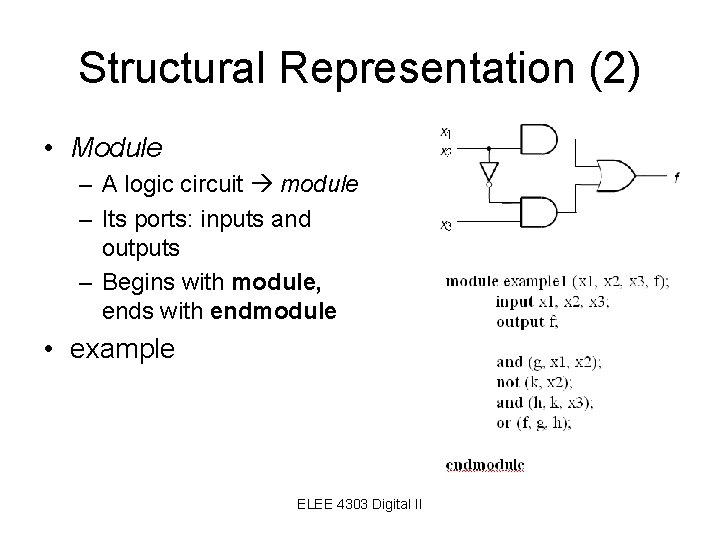

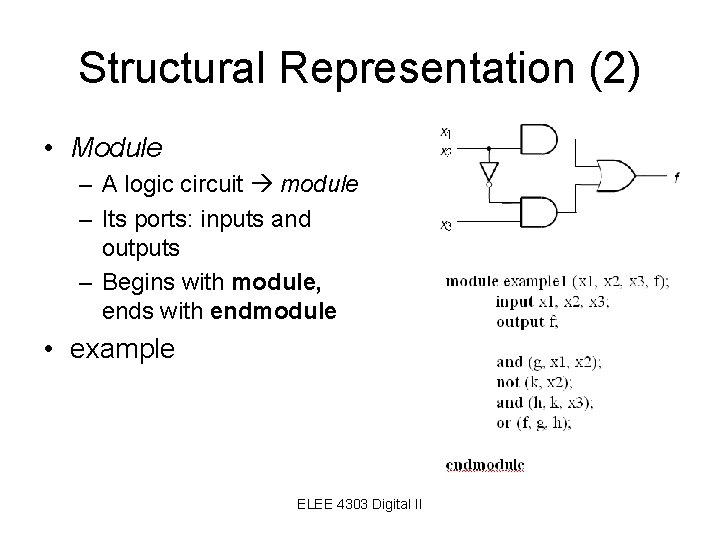

Structural Representation (2) • Module – A logic circuit module – Its ports: inputs and outputs – Begins with module, ends with endmodule • example ELEE 4303 Digital II

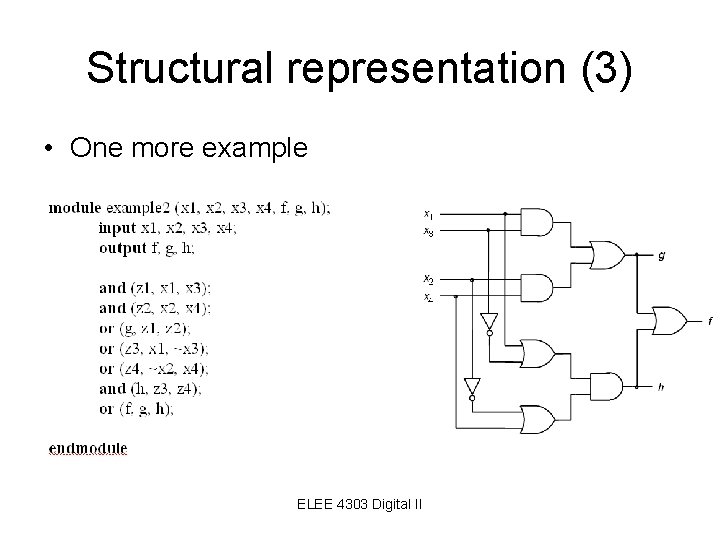

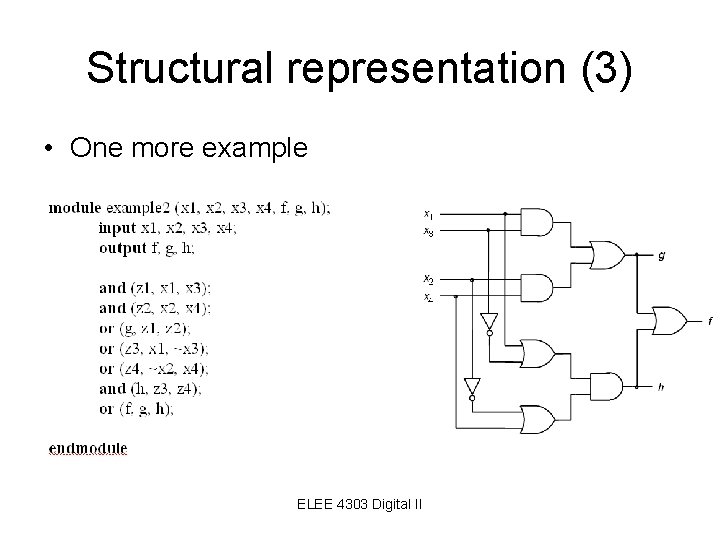

Structural representation (3) • One more example ELEE 4303 Digital II

Behavioral Representation (1) • Why behavioral representation? – Using primitives can be tedious when circuits are large – It is desired to describe the circuit in more abstract level – behavior • Two fundamental types of behavior model – Logic expression – Procedural statements • CAD synthesis tools use this representation to construct the actual circuit ELEE 4303 Digital II

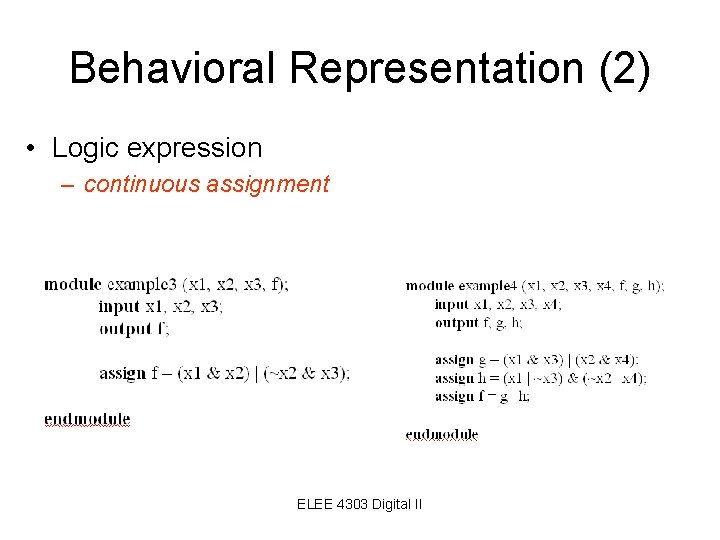

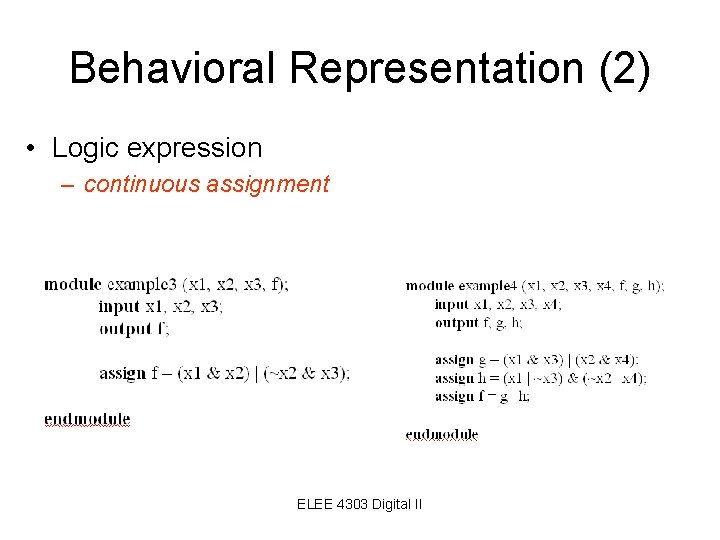

Behavioral Representation (2) • Logic expression – continuous assignment ELEE 4303 Digital II

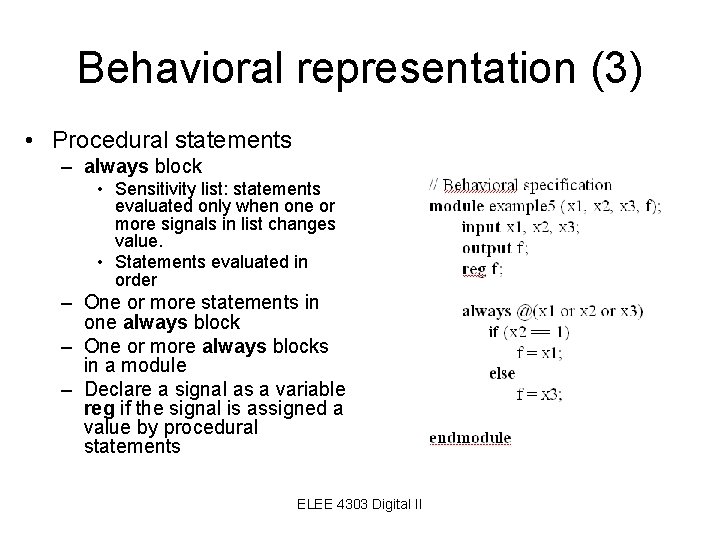

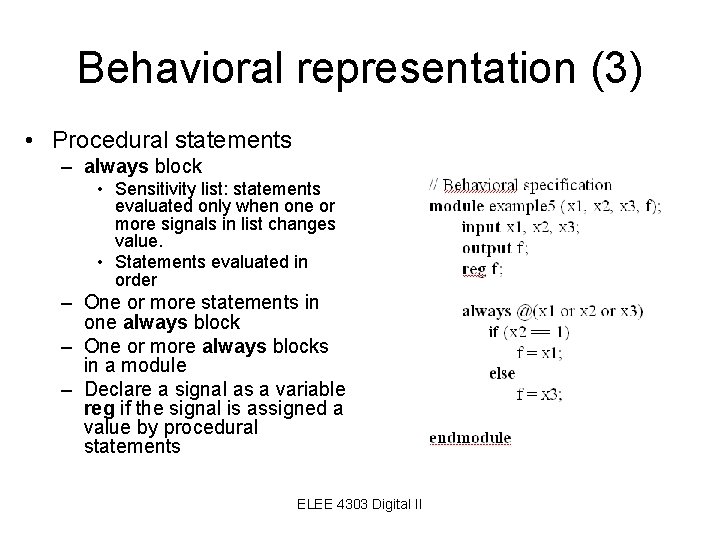

Behavioral representation (3) • Procedural statements – always block • Sensitivity list: statements evaluated only when one or more signals in list changes value. • Statements evaluated in order – One or more statements in one always block – One or more always blocks in a module – Declare a signal as a variable reg if the signal is assigned a value by procedural statements ELEE 4303 Digital II

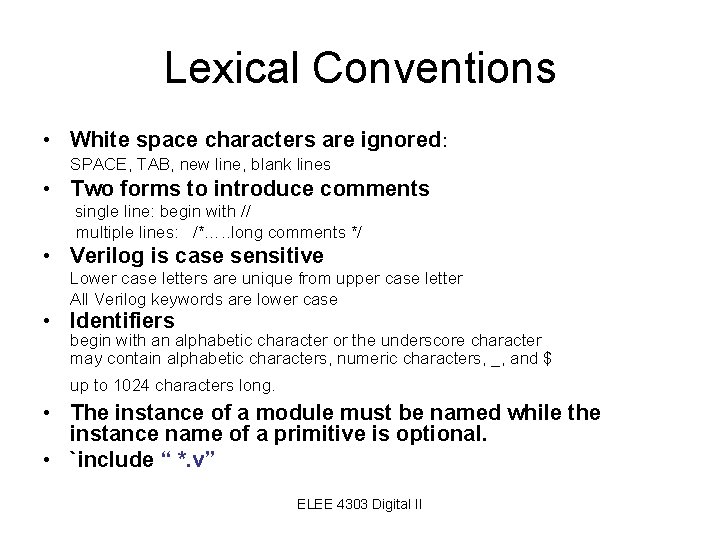

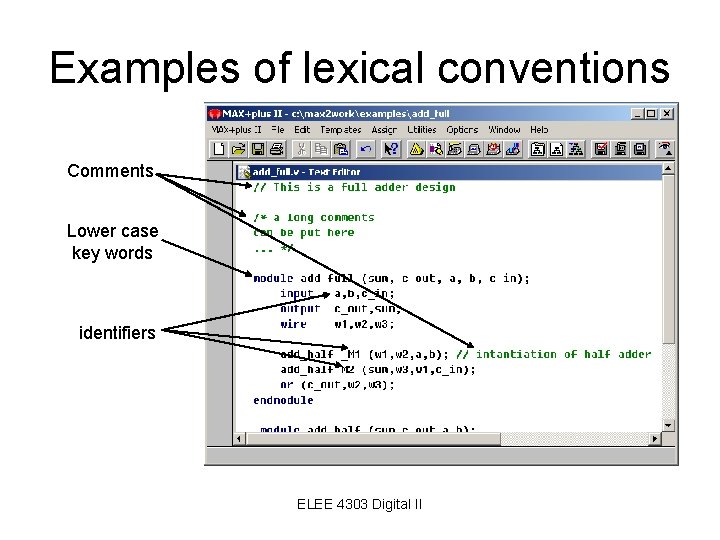

Lexical Conventions • White space characters are ignored: SPACE, TAB, new line, blank lines • Two forms to introduce comments single line: begin with // multiple lines: /*…. . long comments */ • Verilog is case sensitive Lower case letters are unique from upper case letter All Verilog keywords are lower case • Identifiers begin with an alphabetic character or the underscore character may contain alphabetic characters, numeric characters, _, and $ up to 1024 characters long. • The instance of a module must be named while the instance name of a primitive is optional. • `include “ *. v” ELEE 4303 Digital II

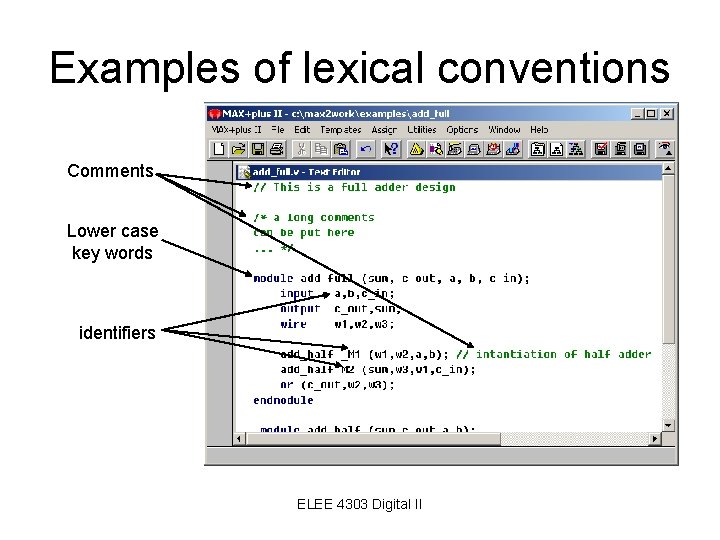

Examples of lexical conventions Comments Lower case key words identifiers ELEE 4303 Digital II

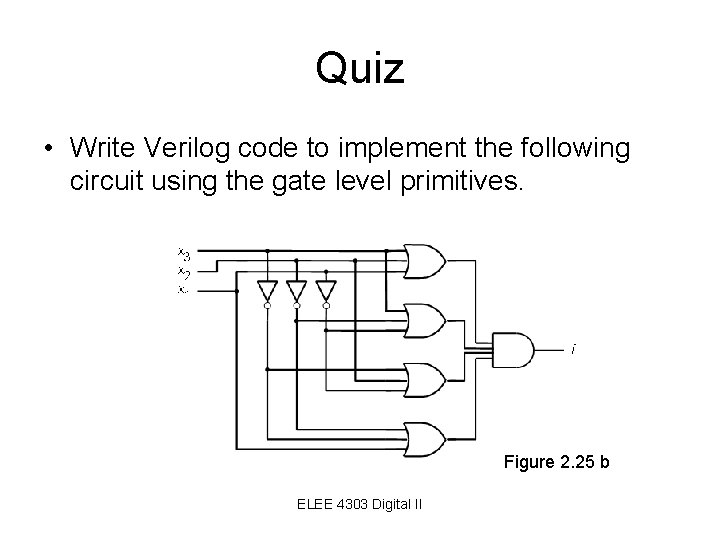

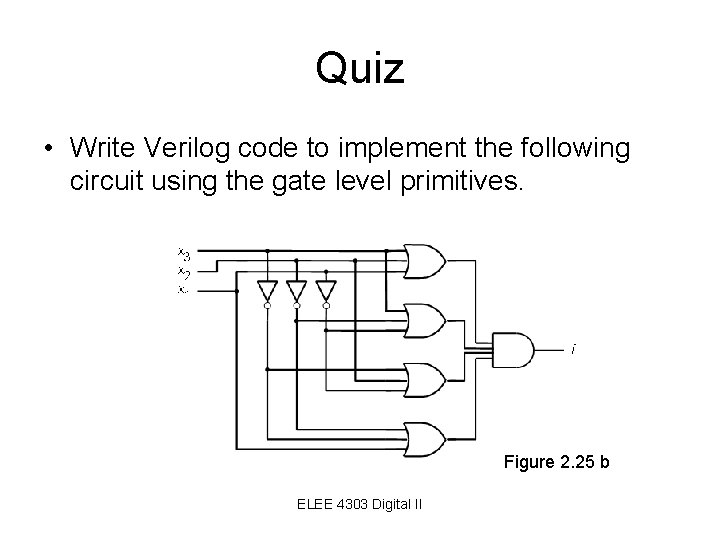

Quiz • Write Verilog code to implement the following circuit using the gate level primitives. Figure 2. 25 b ELEE 4303 Digital II