Introduction to The Semiconductor Industry 2009 Oct 1

- Slides: 31

Introduction to The Semiconductor Industry 2009 Oct. 1 中山電機 黃義佑 1

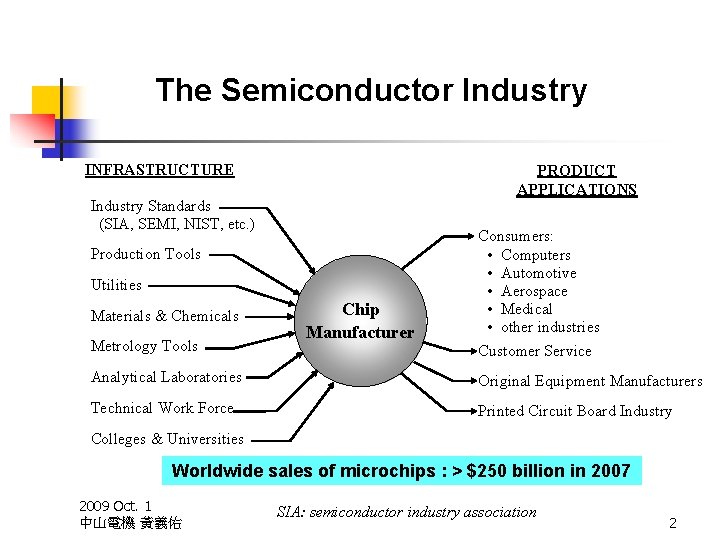

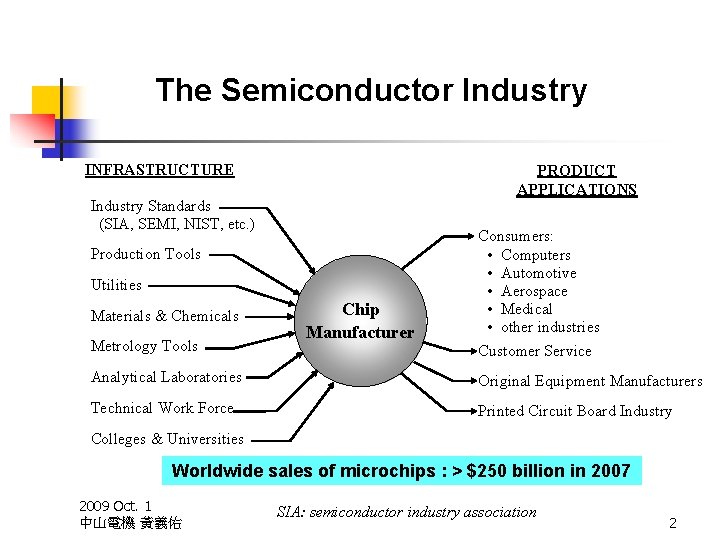

The Semiconductor Industry INFRASTRUCTURE PRODUCT APPLICATIONS Industry Standards (SIA, SEMI, NIST, etc. ) Production Tools Utilities Materials & Chemicals Metrology Tools Chip Manufacturer Consumers: • Computers • Automotive • Aerospace • Medical • other industries Customer Service Analytical Laboratories Original Equipment Manufacturers Technical Work Force Printed Circuit Board Industry Colleges & Universities Worldwide sales of microchips : > $250 billion in 2007 2009 Oct. 1 中山電機 黃義佑 SIA: semiconductor industry association 2

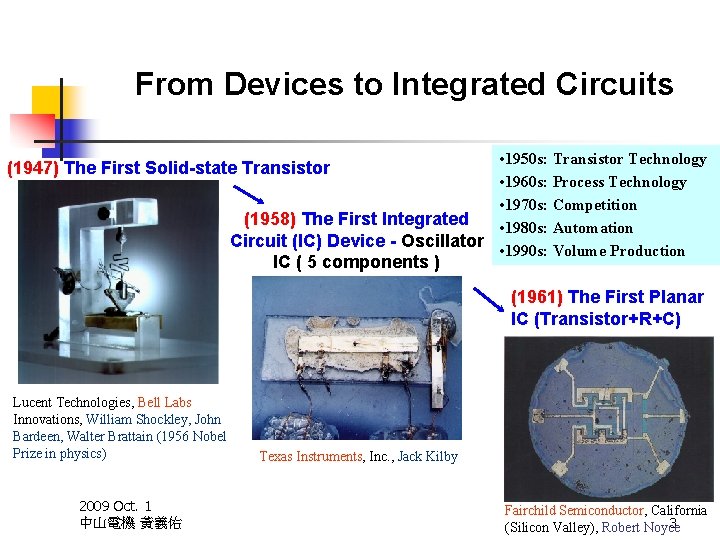

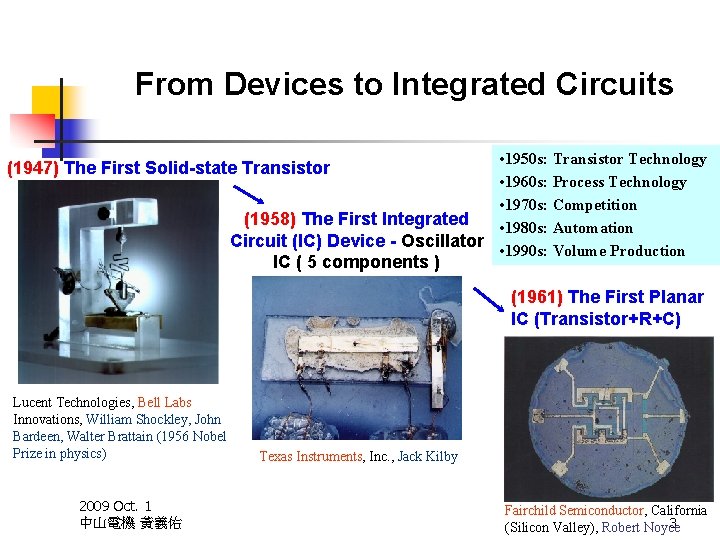

From Devices to Integrated Circuits • 1950 s: Transistor Technology • 1960 s: Process Technology • 1970 s: Competition (1958) The First Integrated • 1980 s: Automation Circuit (IC) Device - Oscillator • 1990 s: Volume Production (1947) The First Solid-state Transistor IC ( 5 components ) (1961) The First Planar IC (Transistor+R+C) Lucent Technologies, Bell Labs Innovations, William Shockley, John Bardeen, Walter Brattain (1956 Nobel Prize in physics) 2009 Oct. 1 中山電機 黃義佑 Texas Instruments, Inc. , Jack Kilby Fairchild Semiconductor, California 3 (Silicon Valley), Robert Noyce

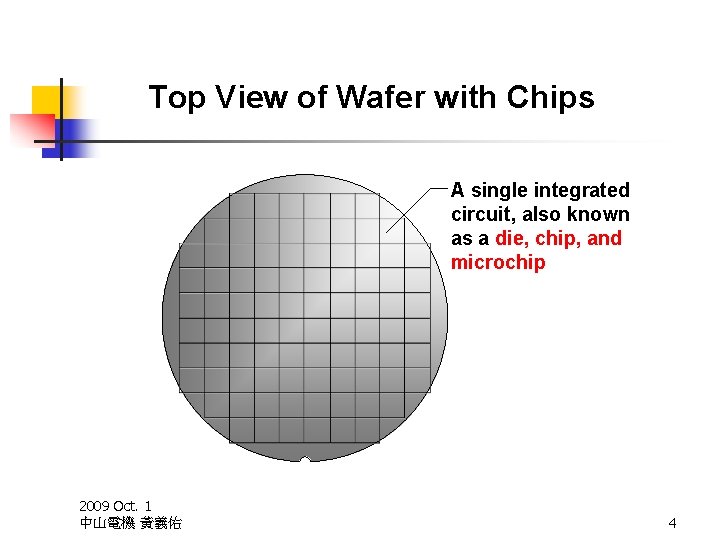

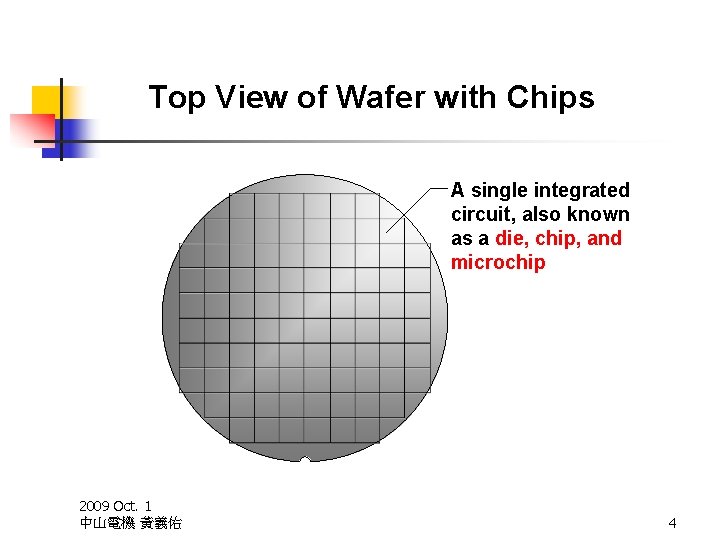

Top View of Wafer with Chips A single integrated circuit, also known as a die, chip, and microchip 2009 Oct. 1 中山電機 黃義佑 4

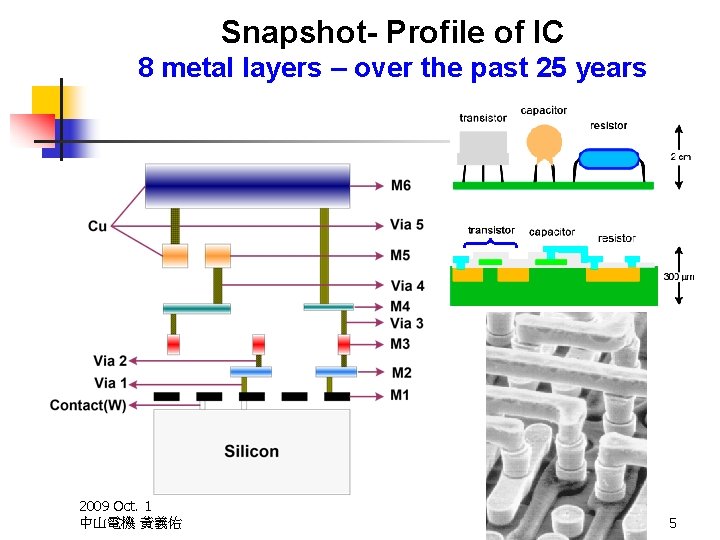

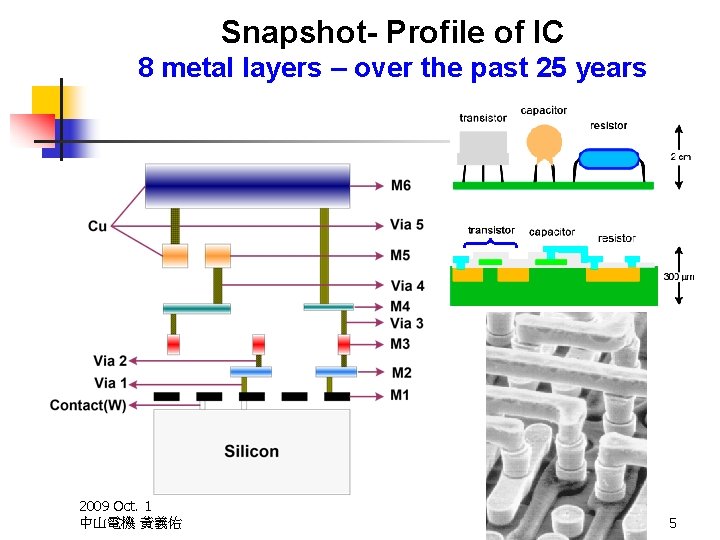

Snapshot- Profile of IC 8 metal layers – over the past 25 years 2009 Oct. 1 中山電機 黃義佑 5

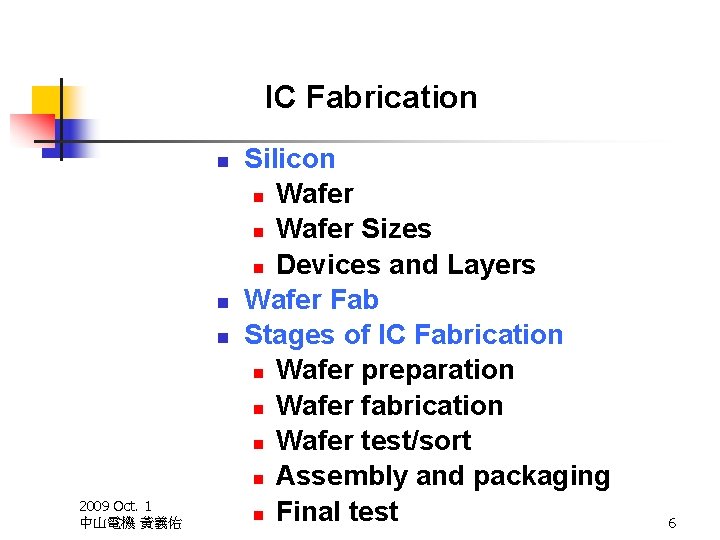

IC Fabrication n 2009 Oct. 1 中山電機 黃義佑 Silicon n Wafer Sizes n Devices and Layers Wafer Fab Stages of IC Fabrication n Wafer preparation n Wafer fabrication n Wafer test/sort n Assembly and packaging n Final test 6

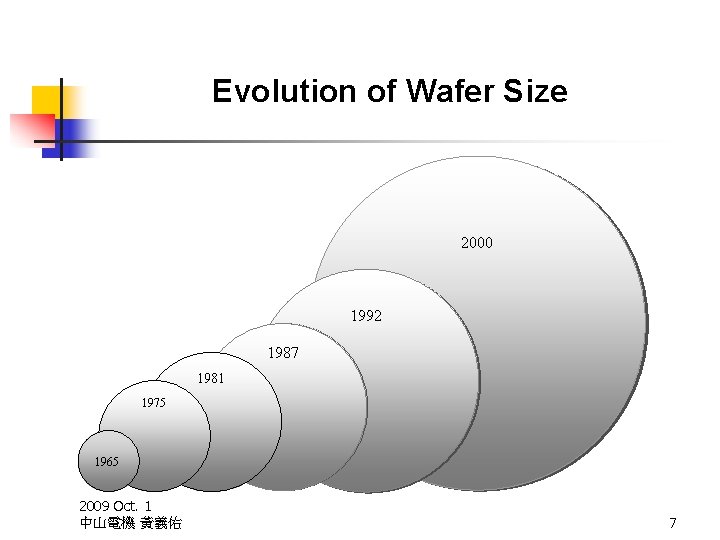

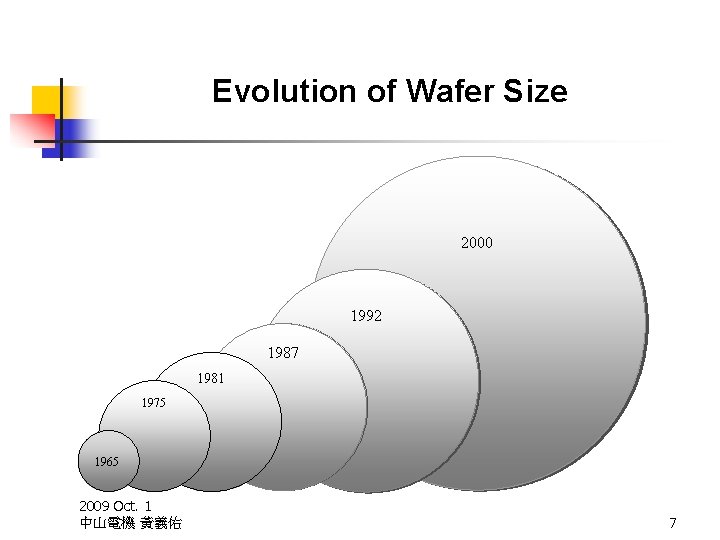

Evolution of Wafer Size 2000 1992 1987 1981 1975 1965 2009 Oct. 1 中山電機 黃義佑 7

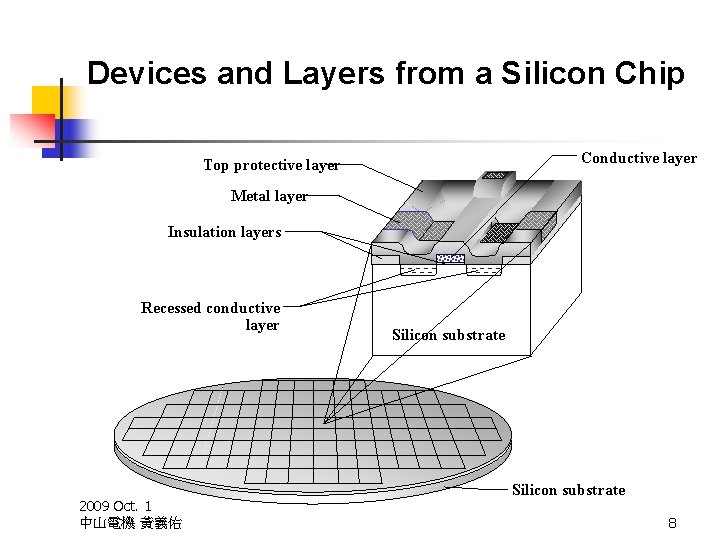

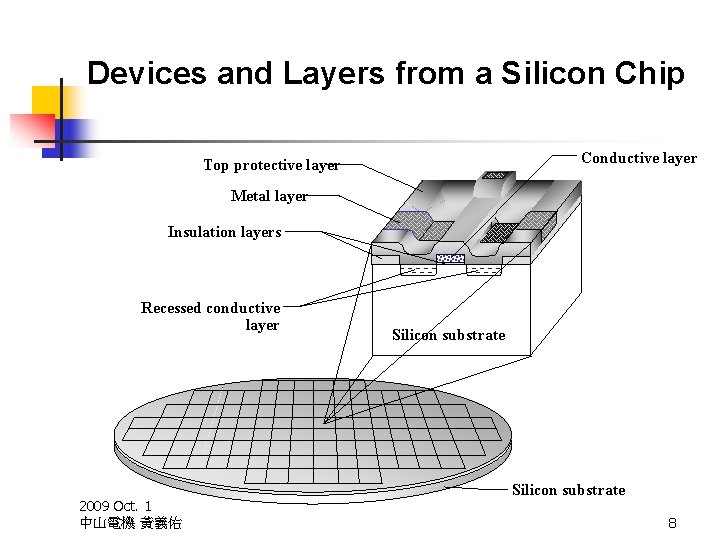

Devices and Layers from a Silicon Chip Conductive layer Top protective layer Metal layer Insulation layers Recessed conductive layer 2009 Oct. 1 中山電機 黃義佑 drain Silicon substrate 8

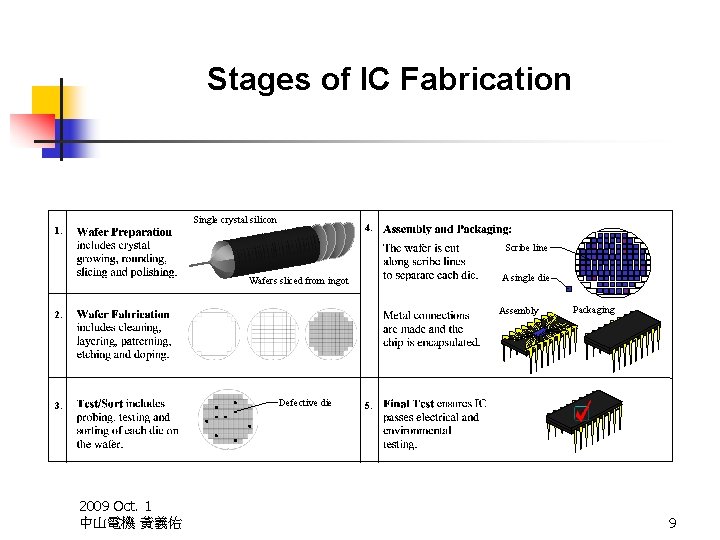

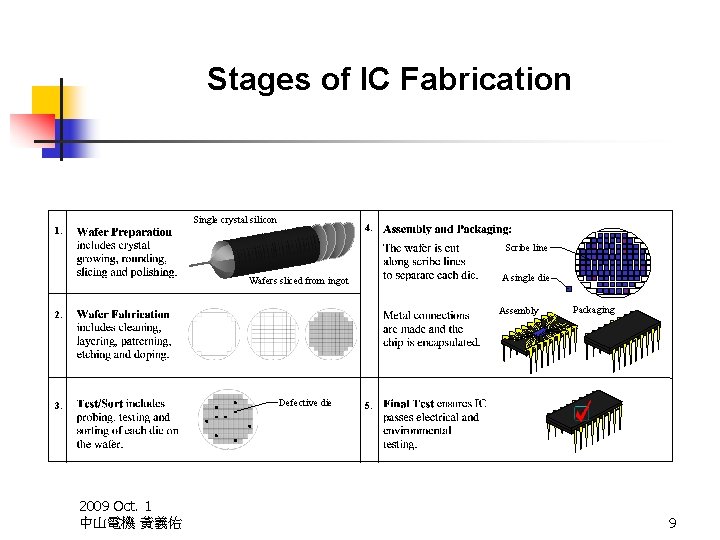

Stages of IC Fabrication Single crystal silicon 1. 4. Scribe line A single die Wafers sliced from ingot Assembly 2. Defective die 3. 2009 Oct. 1 中山電機 黃義佑 Packaging 5. 9

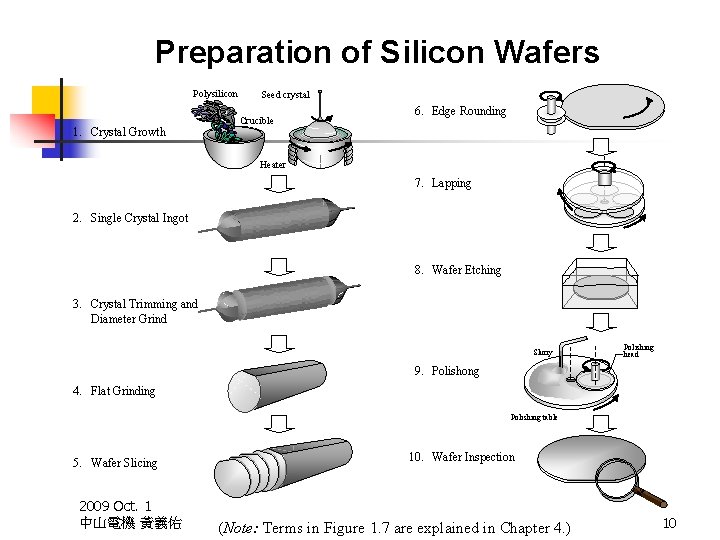

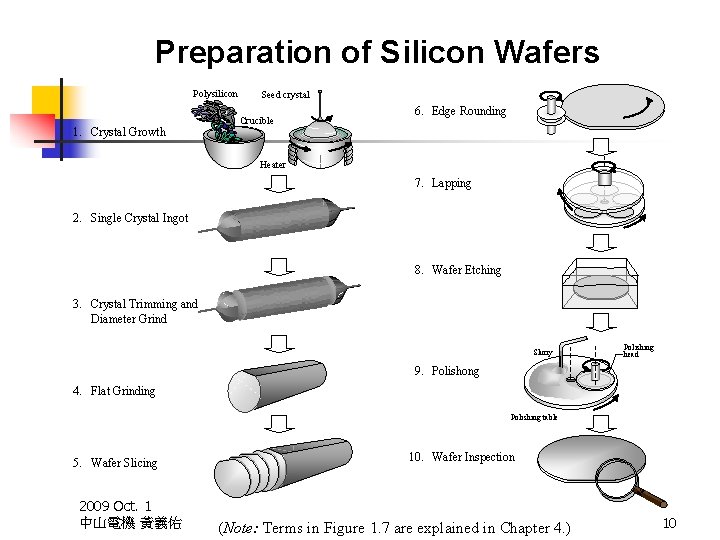

Preparation of Silicon Wafers Polysilicon 1. Crystal Growth Seed crystal Crucible 6. Edge Rounding Heater 7. Lapping 2. Single Crystal Ingot 8. Wafer Etching 3. Crystal Trimming and Diameter Grind Slurry Polishing head 9. Polishong 4. Flat Grinding Polishing table 5. Wafer Slicing 2009 Oct. 1 中山電機 黃義佑 10. Wafer Inspection (Note: Terms in Figure 1. 7 are explained in Chapter 4. ) 10

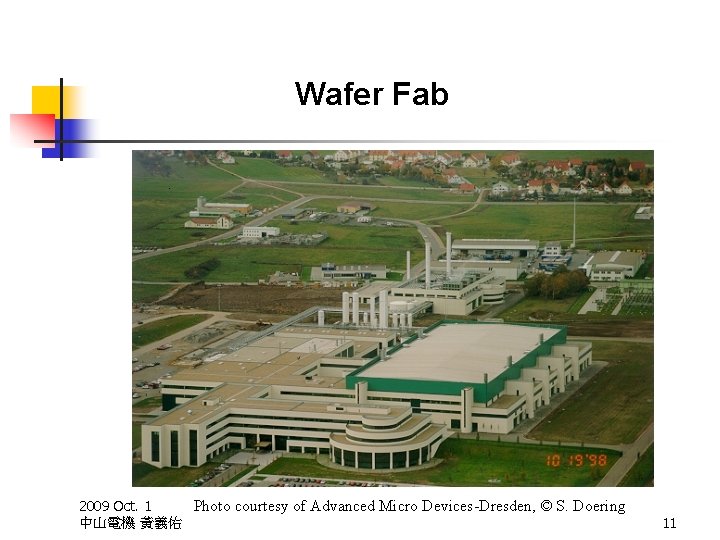

Wafer Fab 2009 Oct. 1 Photo courtesy of Advanced Micro Devices-Dresden, © S. Doering 中山電機 黃義佑 11

TSMC (台積電) Fab 2 (Hsinchu) Fab 3 (Hsinchu) Fab 5(Hsinchu) Fab 6(Tainan) Fab 7 (Hsinchu) Fab 8 (Hsinchu) Fab 12 (Hsinchu) Fab 14(Tainan) TSMC (Shanghai) Wafer Tech (USA) SSMC (Singapore) 2009 Oct. 1 中山電機 黃義佑 12

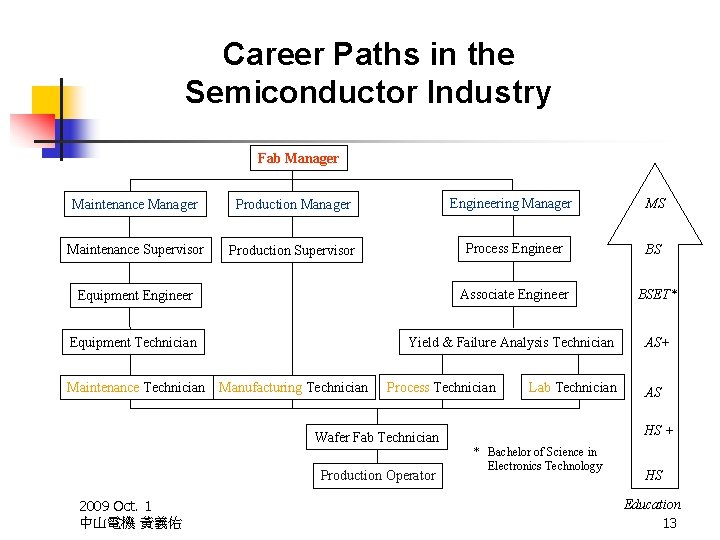

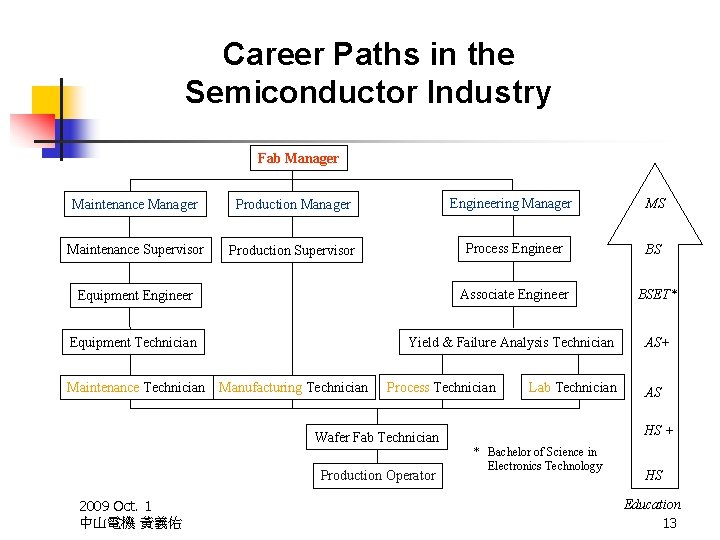

Career Paths in the Semiconductor Industry Fab Manager Maintenance Manager Production Manager Engineering Manager MS Maintenance Supervisor Production Supervisor Process Engineer BS Equipment Engineer Associate Engineer BSET* Equipment Technician Yield & Failure Analysis Technician AS+ Maintenance Technician Manufacturing Technician Process Technician Wafer Fab Technician Production Operator 2009 Oct. 1 中山電機 黃義佑 Lab Technician AS HS + * Bachelor of Science in Electronics Technology HS Education 13

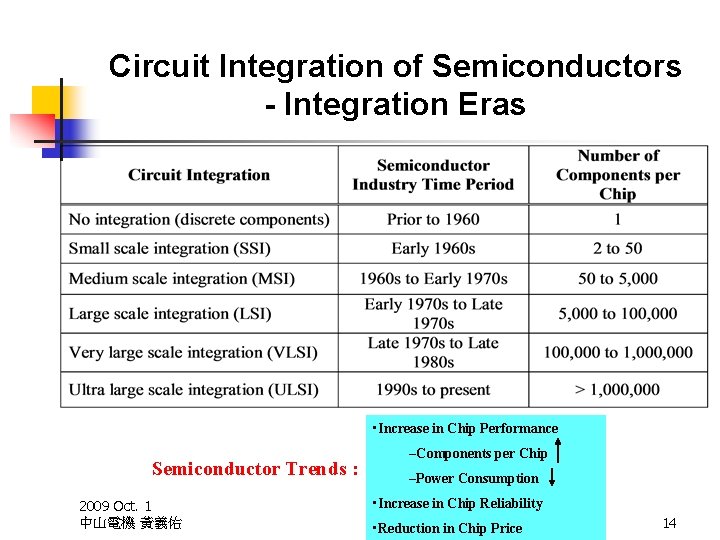

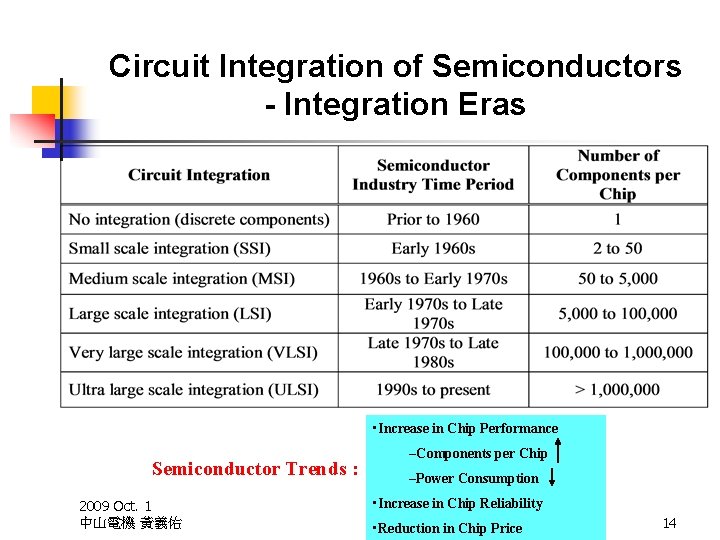

Circuit Integration of Semiconductors - Integration Eras • Increase in Chip Performance Semiconductor Trends : 2009 Oct. 1 中山電機 黃義佑 –Components per Chip –Power Consumption • Increase in Chip Reliability • Reduction in Chip Price 14

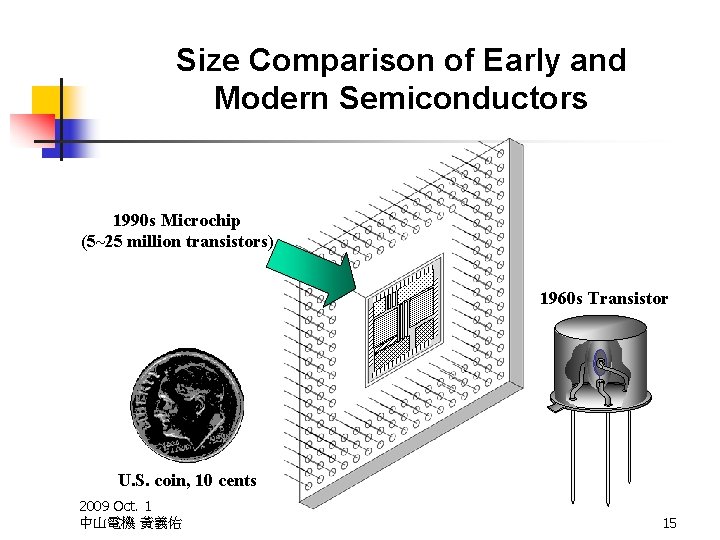

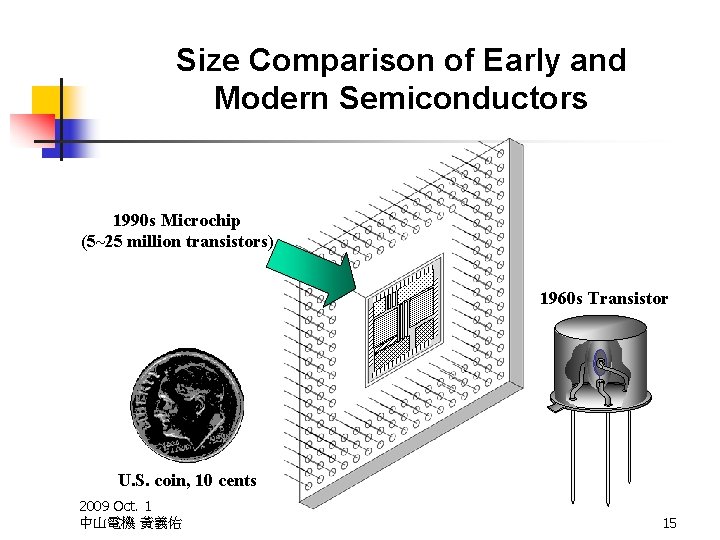

Size Comparison of Early and Modern Semiconductors 1990 s Microchip (5~25 million transistors) 1960 s Transistor U. S. coin, 10 cents 2009 Oct. 1 中山電機 黃義佑 15

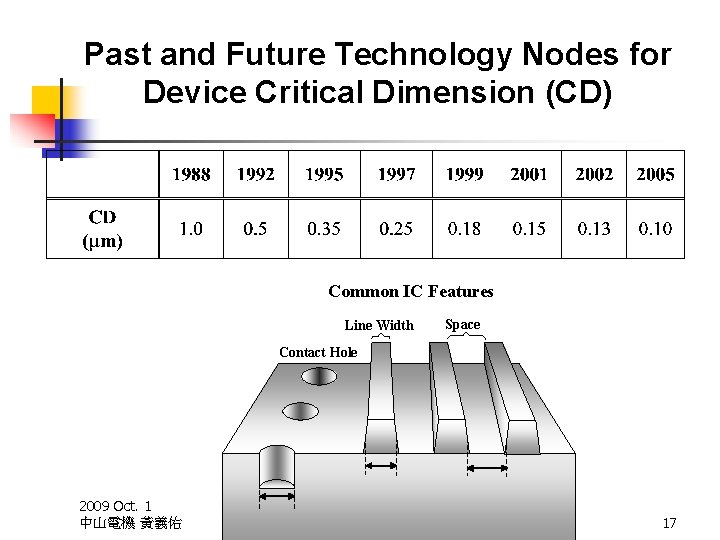

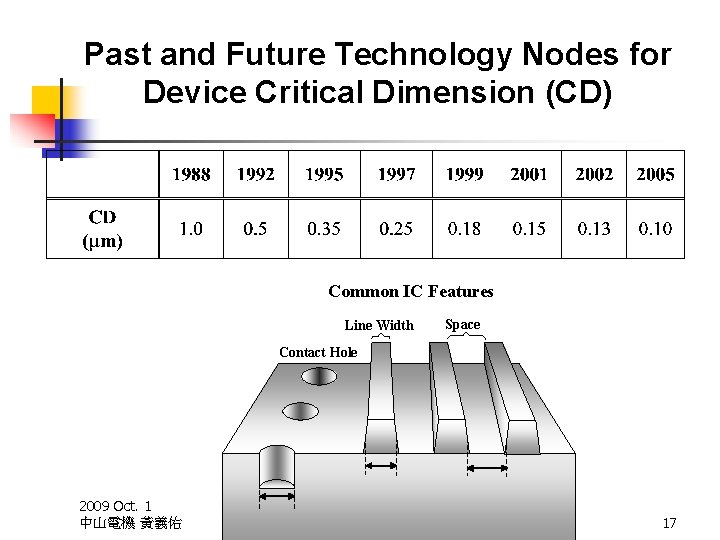

Past and Future Technology Nodes for Device Critical Dimension (CD) Common IC Features Line Width Space Contact Hole 2009 Oct. 1 中山電機 黃義佑 17

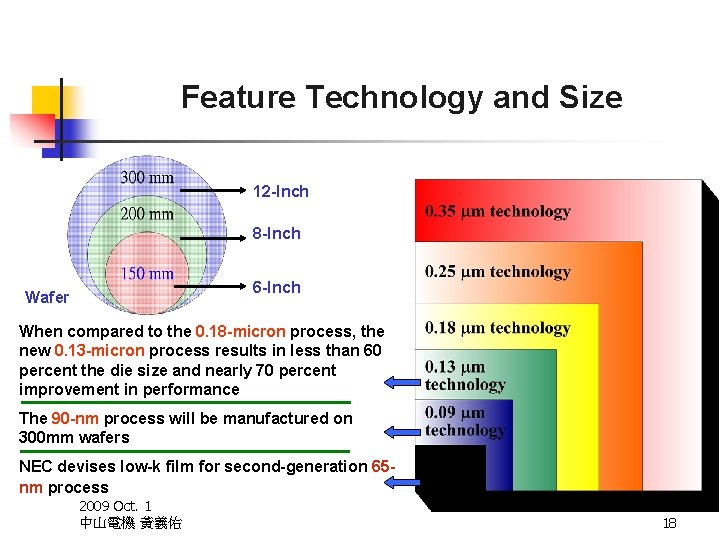

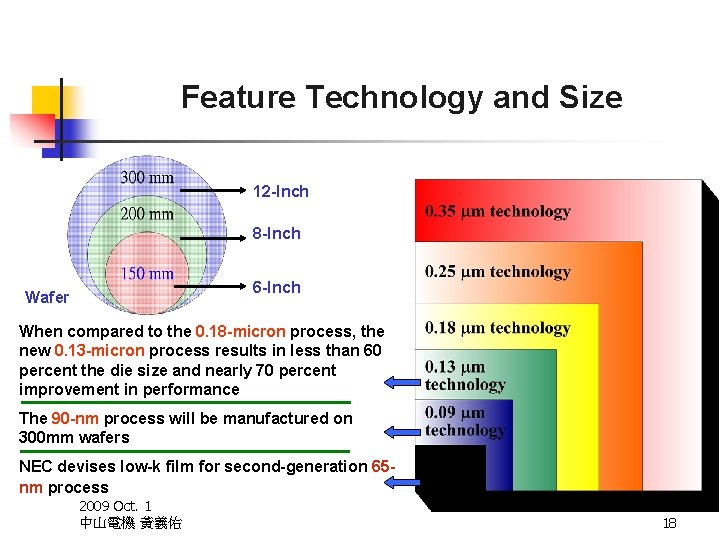

Feature Technology and Size 12 -Inch 8 -Inch 6 -Inch Wafer When compared to the 0. 18 -micron process, the new 0. 13 -micron process results in less than 60 percent the die size and nearly 70 percent improvement in performance The 90 -nm process will be manufactured on 300 mm wafers NEC devises low-k film for second-generation 65 nm process 2009 Oct. 1 中山電機 黃義佑 18

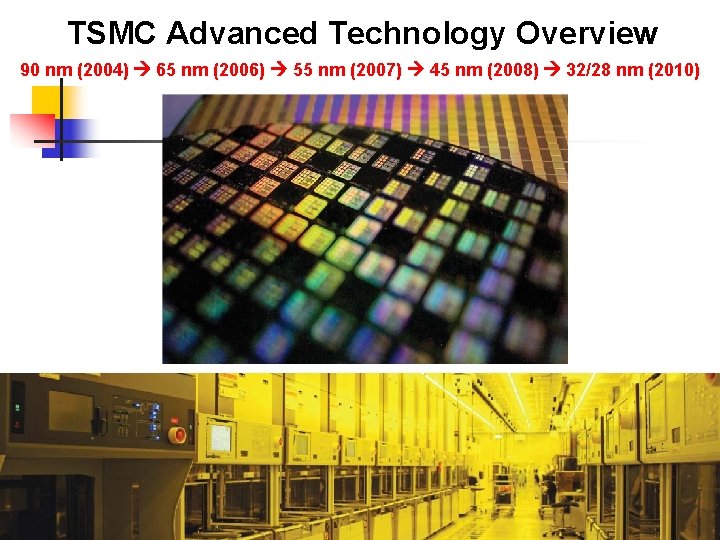

TSMC Advanced Technology Overview 90 nm (2004) 65 nm (2006) 55 nm (2007) 45 nm (2008) 32/28 nm (2010) 2009 Oct. 1 中山電機 黃義佑 19

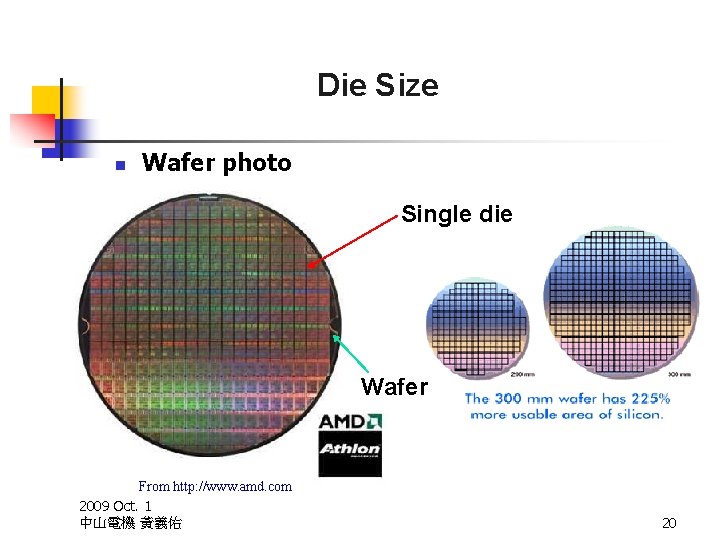

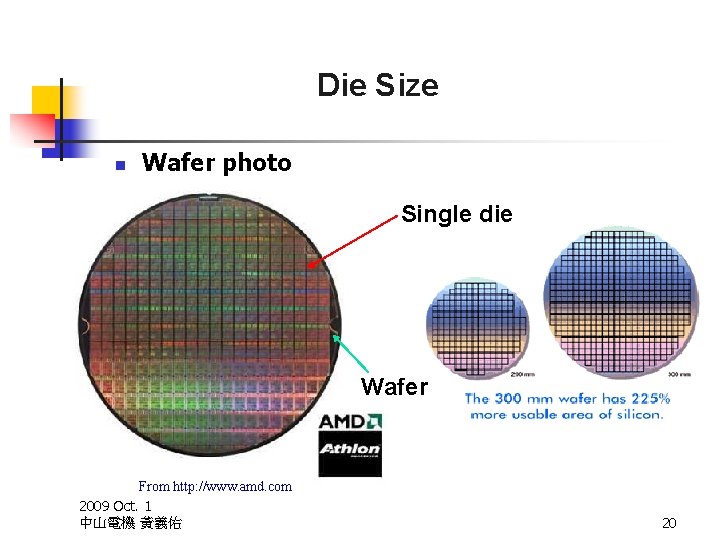

Die Size n Wafer photo Single die Wafer From http: //www. amd. com 2009 Oct. 1 中山電機 黃義佑 20

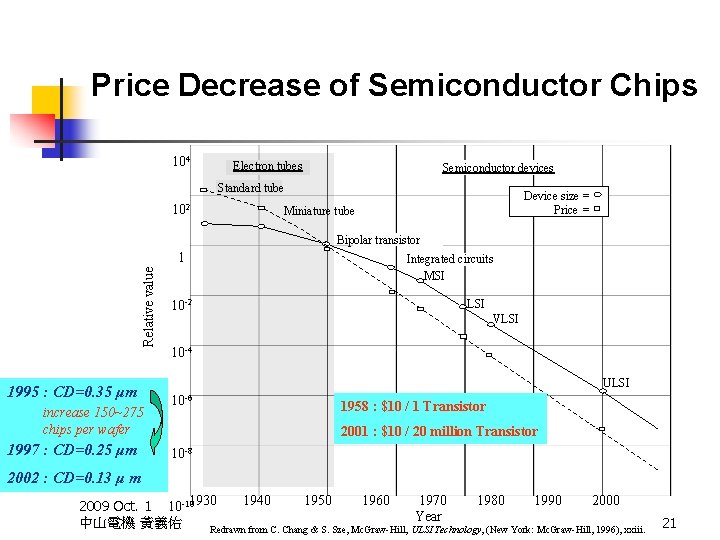

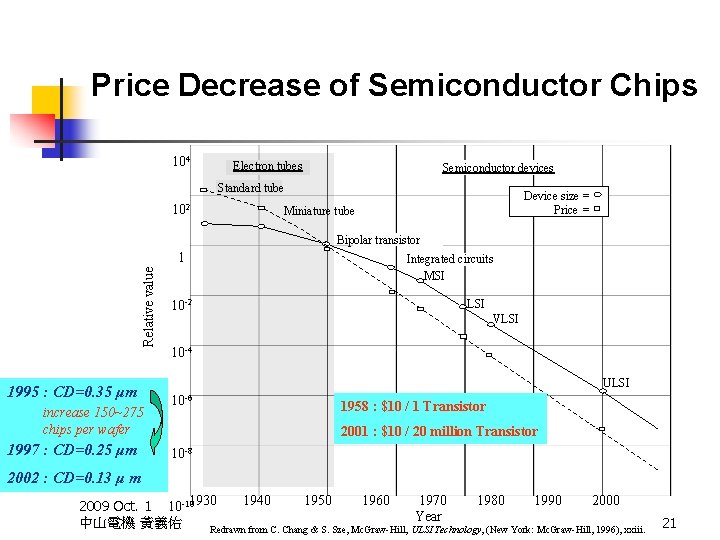

Price Decrease of Semiconductor Chips 104 Electron tubes Semiconductor devices Standard tube 102 Device size = Price = Miniature tube Bipolar transistor Relative value 1 1995 : CD=0. 35 μm increase 150~275 chips per wafer 1997 : CD=0. 25 μm 10 -2 Integrated circuits MSI LSI VLSI 10 -4 ULSI 10 -6 1958 : $10 / 1 Transistor 2001 : $10 / 20 million Transistor 10 -8 2002 : CD=0. 13 μ m 1940 1950 1960 1970 1980 1990 2009 Oct. 1 10 -101930 Year 中山電機 黃義佑 Redrawn from C. Chang & S. Sze, Mc. Graw-Hill, ULSI Technology, (New York: Mc. Graw-Hill, 1996), xxiii. 21

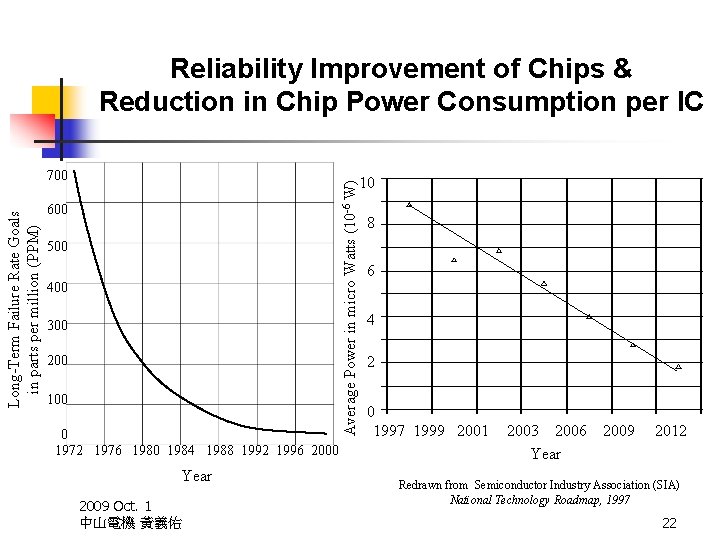

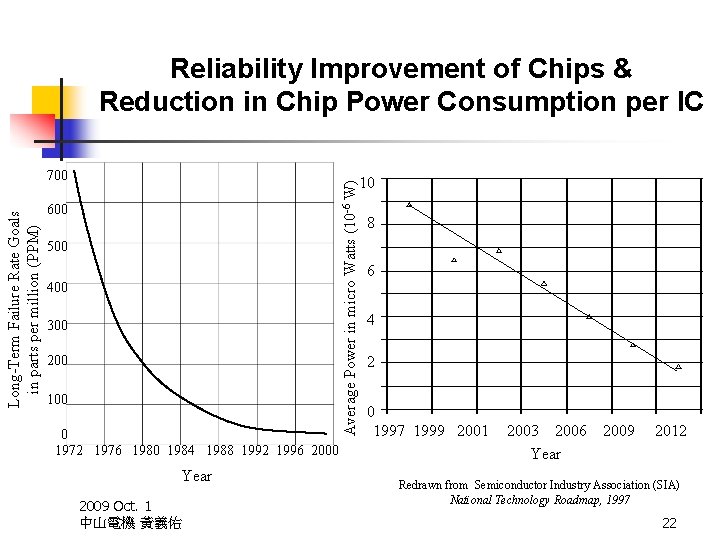

Long-Term Failure Rate Goals in parts per million (PPM) 700 600 500 400 300 200 100 0 1972 1976 1980 1984 1988 1992 1996 2000 Year 2009 Oct. 1 中山電機 黃義佑 Average Power in micro Watts (10 -6 W) Reliability Improvement of Chips & Reduction in Chip Power Consumption per IC 10 8 6 4 2 0 1997 1999 2001 2003 2006 Year 2009 2012 Redrawn from Semiconductor Industry Association (SIA) National Technology Roadmap, 1997 22

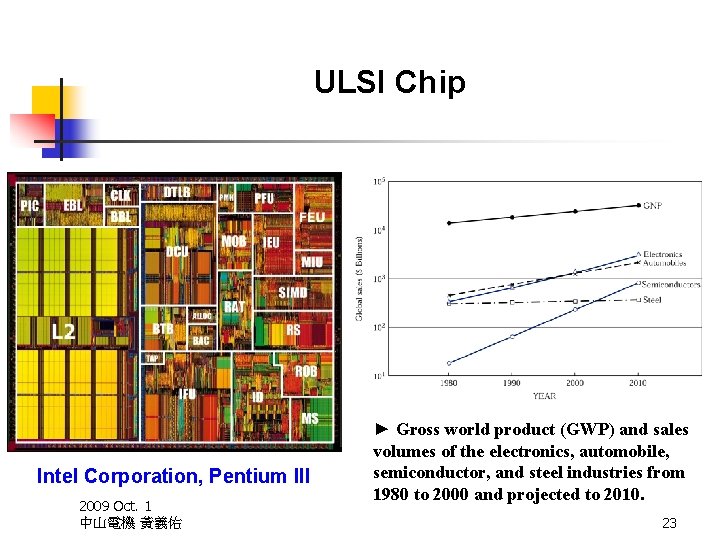

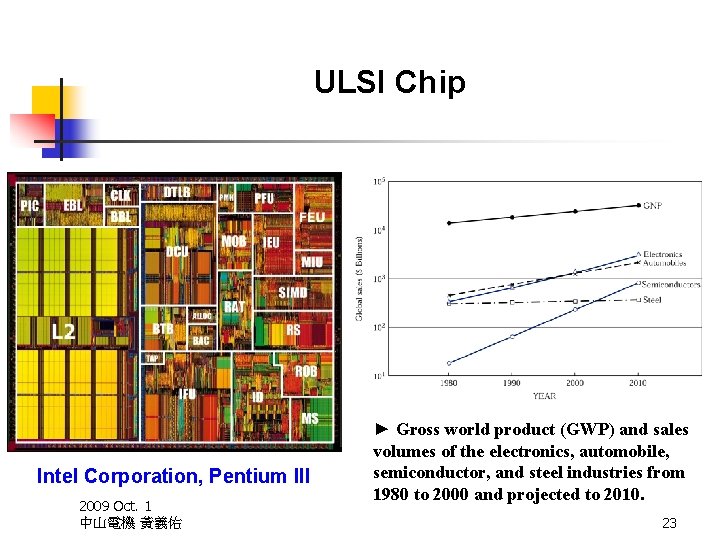

ULSI Chip Intel Corporation, Pentium III 2009 Oct. 1 中山電機 黃義佑 ► Gross world product (GWP) and sales volumes of the electronics, automobile, semiconductor, and steel industries from 1980 to 2000 and projected to 2010. 23

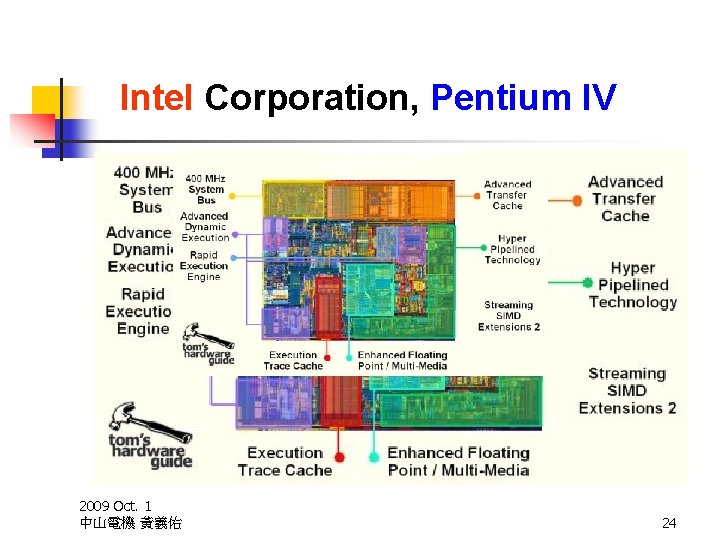

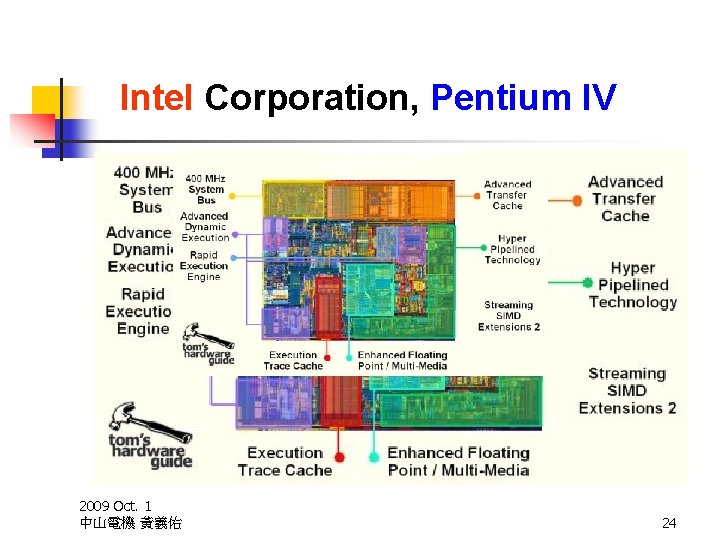

Intel Corporation, Pentium IV 2009 Oct. 1 中山電機 黃義佑 24

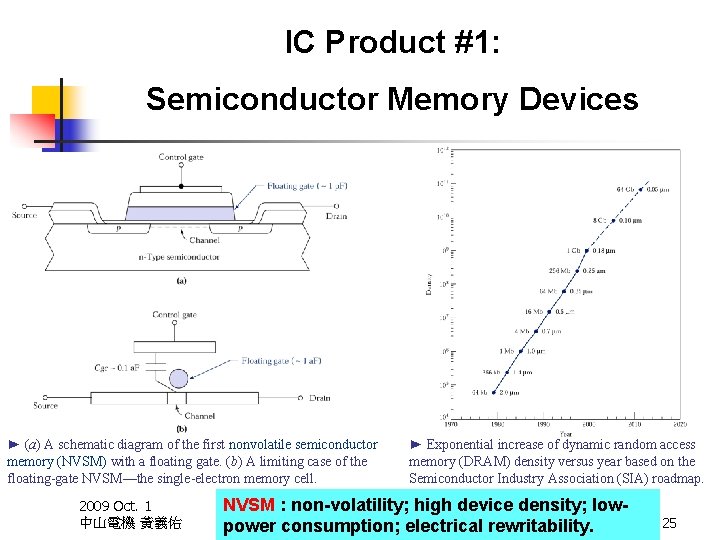

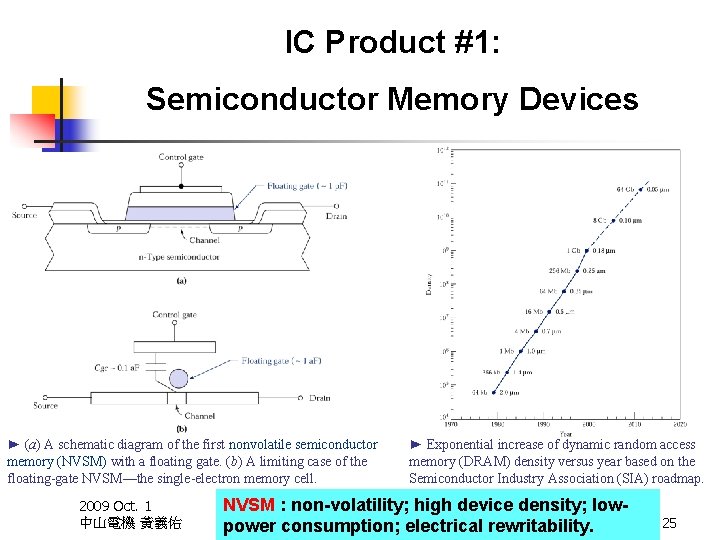

IC Product #1: Semiconductor Memory Devices ► (a) A schematic diagram of the first nonvolatile semiconductor memory (NVSM) with a floating gate. (b) A limiting case of the floating-gate NVSM—the single-electron memory cell. 2009 Oct. 1 中山電機 黃義佑 ► Exponential increase of dynamic random access memory (DRAM) density versus year based on the Semiconductor Industry Association (SIA) roadmap. NVSM : non-volatility; high device density; lowpower consumption; electrical rewritability. 25

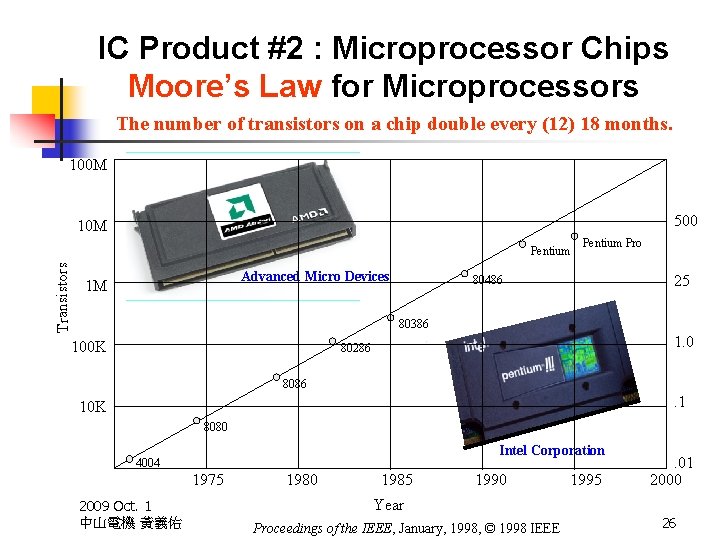

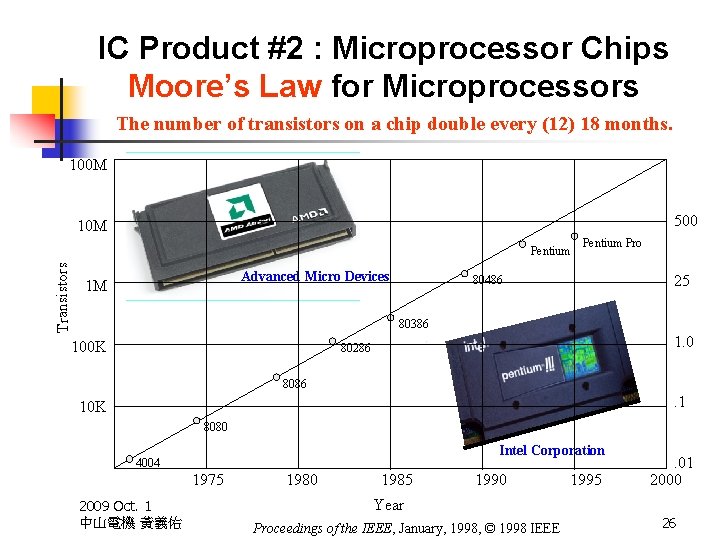

IC Product #2 : Microprocessor Chips Moore’s Law for Microprocessors The number of transistors on a chip double every (12) 18 months. 100 M 500 10 M Transistors Pentium Advanced Micro Devices 1 M Pentium Pro 25 80486 80386 100 K 1. 0 80286 8086 . 1 10 K 8080 Intel Corporation 4004 1975 2009 Oct. 1 中山電機 黃義佑 1980 1985 1990 1995 . 01 2000 Year Proceedings of the IEEE, January, 1998, © 1998 IEEE 26

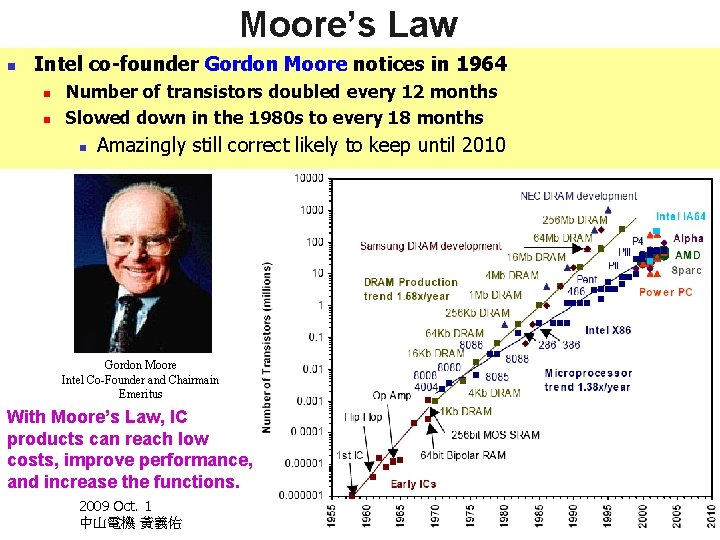

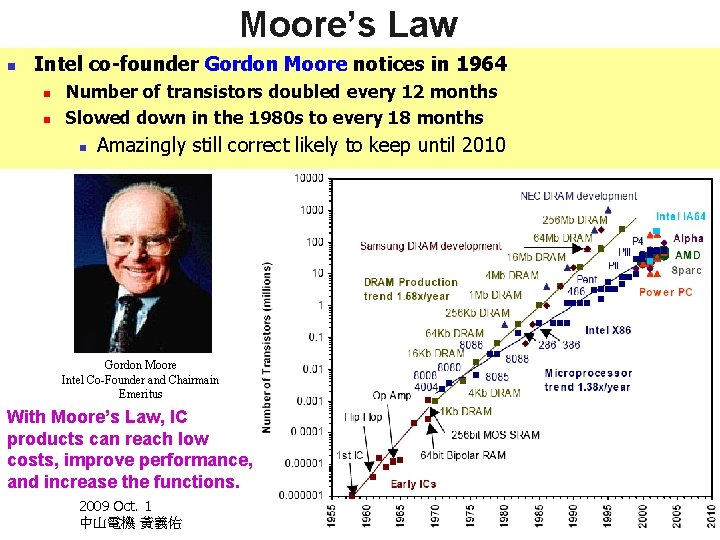

Moore’s Law n Intel co-founder Gordon Moore notices in 1964 n n Number of transistors doubled every 12 months Slowed down in the 1980 s to every 18 months n Amazingly still correct likely to keep until 2010 Gordon Moore Intel Co-Founder and Chairmain Emeritus With Moore’s Law, IC products can reach low costs, improve performance, and increase the functions. 2009 Oct. 1 中山電機 黃義佑 27

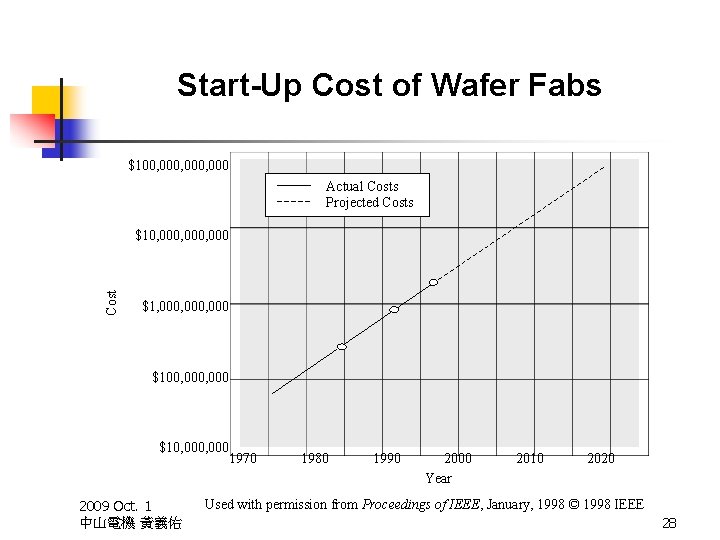

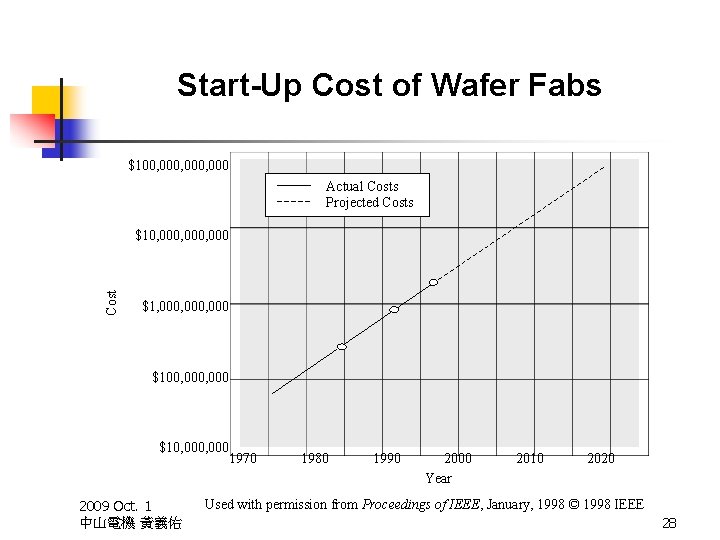

Start-Up Cost of Wafer Fabs $100, 000, 000 Actual Costs Projected Costs Cost $10, 000, 000 $1, 000, 000 $100, 000 $10, 000 2009 Oct. 1 中山電機 黃義佑 1970 1980 1990 2000 Year 2010 2020 Used with permission from Proceedings of IEEE, January, 1998 © 1998 IEEE 28

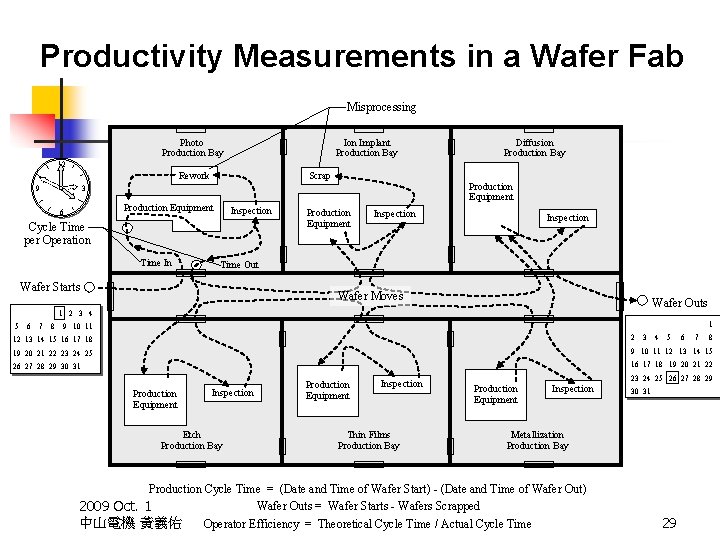

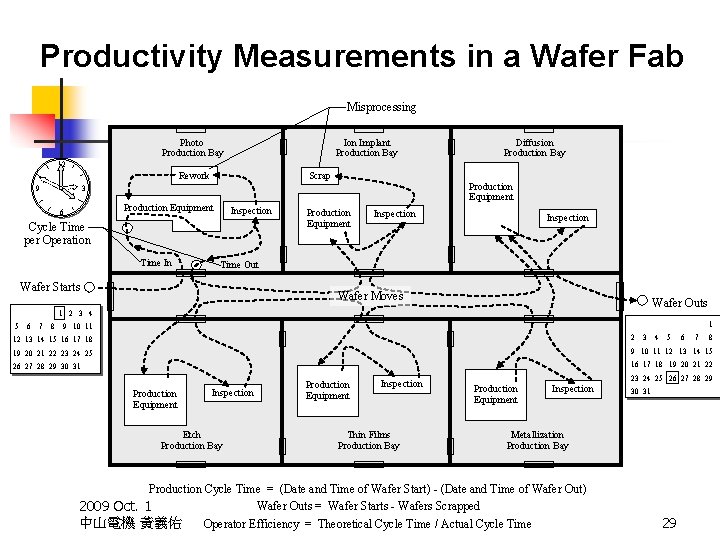

Productivity Measurements in a Wafer Fab Misprocessing Photo Production Bay Ion Implant Production Bay Diffusion Production Bay 12 Rework 9 Scrap Production Equipment 3 Production Equipment 6 Inspection Cycle Time per Operation Time In Production Equipment Inspection Time Out Wafer Starts Wafer Moves Wafer Outs 1 2 3 4 5 6 7 8 1 9 10 11 12 13 14 15 16 17 18 2 19 20 21 22 23 24 25 9 10 11 12 13 14 15 26 27 28 29 30 31 16 17 18 19 20 21 22 Production Equipment Inspection Etch Production Bay Production Equipment Inspection Thin Films Production Bay 3 4 5 6 7 8 23 24 25 26 27 28 29 Production Equipment Inspection 30 31 Metallization Production Bay Production Cycle Time = (Date and Time of Wafer Start) - (Date and Time of Wafer Out) Wafer Outs = Wafer Starts - Wafers Scrapped 2009 Oct. 1 中山電機 黃義佑 Operator Efficiency = Theoretical Cycle Time / Actual Cycle Time 29

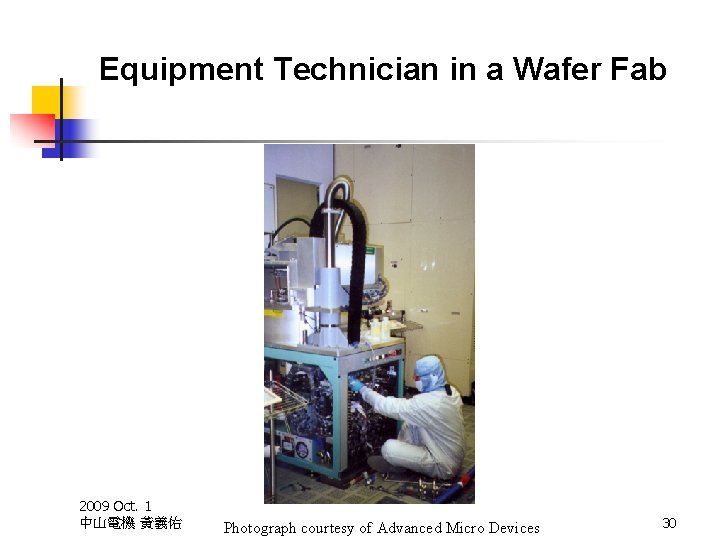

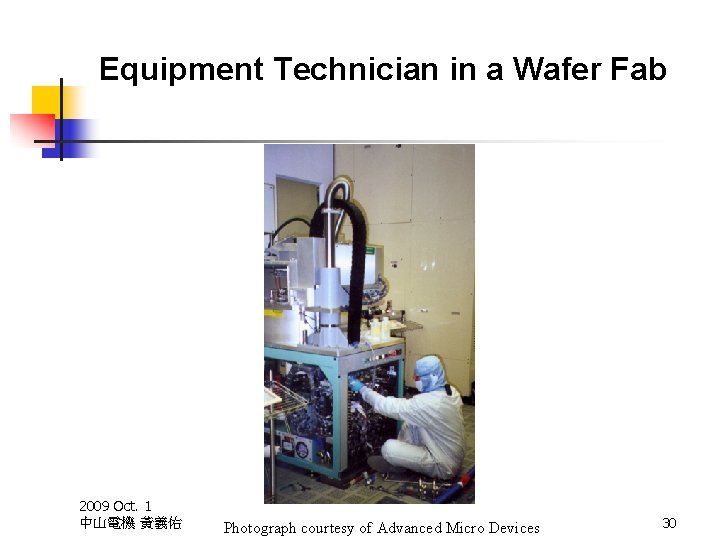

Equipment Technician in a Wafer Fab 2009 Oct. 1 中山電機 黃義佑 Photograph courtesy of Advanced Micro Devices 30

Technician in Wafer Fab 2009 Oct. 1 中山電機 黃義佑 Photo courtesy of Advanced Micro Devices 31