Introduction to Static Timing Analysis What is timing

- Slides: 36

Introduction to Static Timing Analysis:

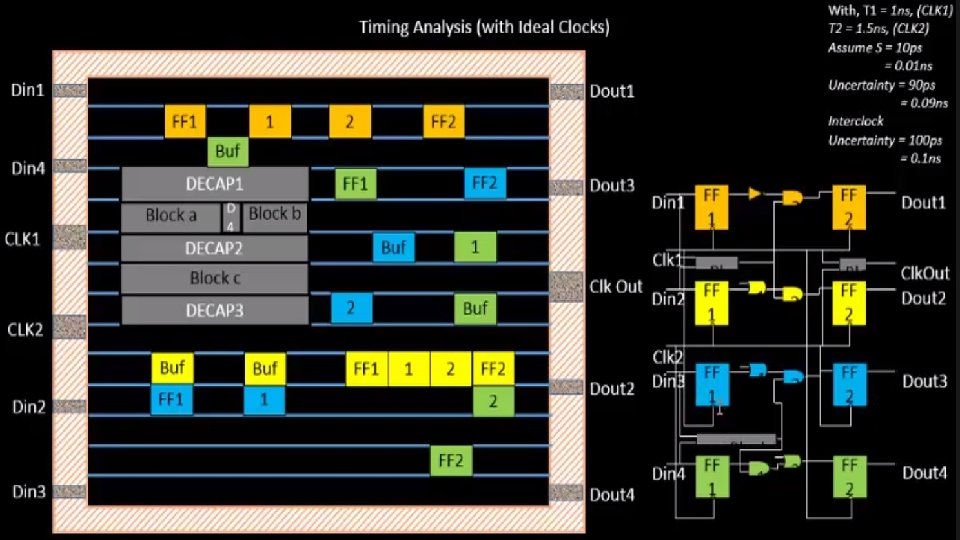

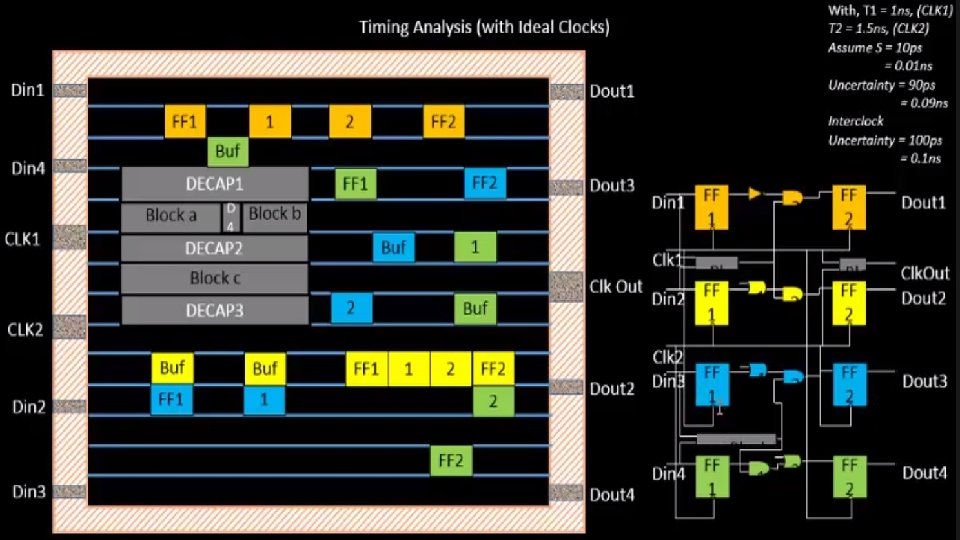

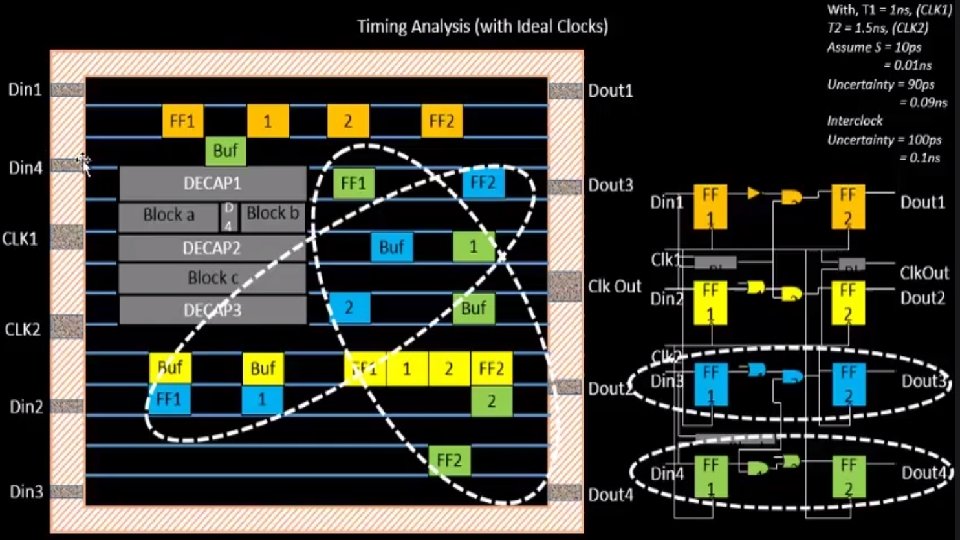

What is timing analysis? • It checks the design for proper timing not correct functionality. • It is a simulation method of computing expected timing of a digital circuit, without requiring the complete simulation of the circuit. • Method of validating timing performance of a design by checking all possible paths for timing violation, under worst case conditions.

How STA is performed on the circuit? • Design is broken down into sets of timing paths • Calculate signal propogation delay along each path • Checks for violations

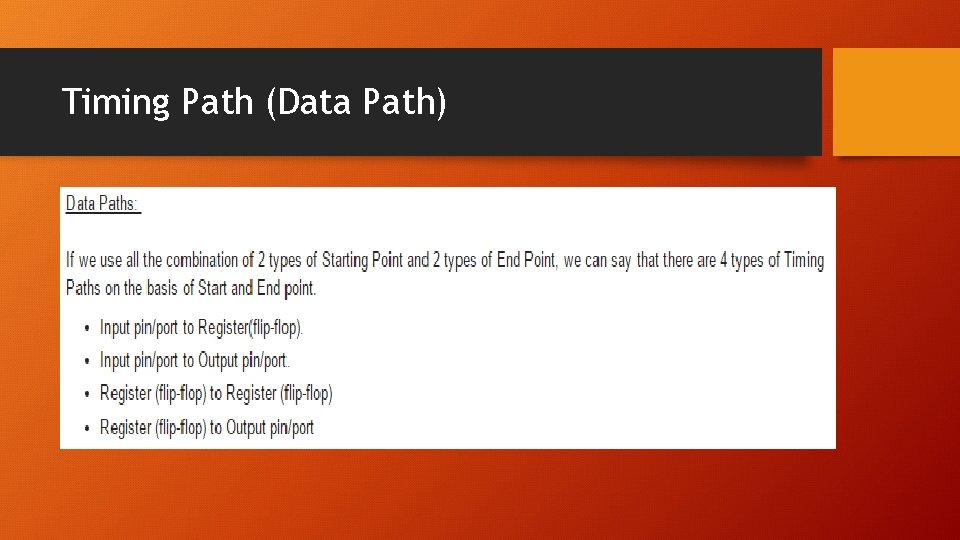

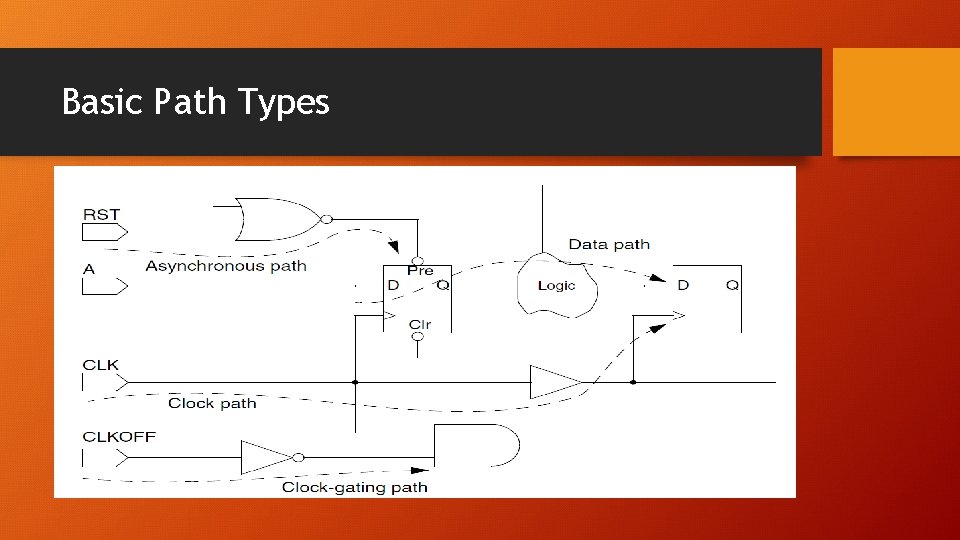

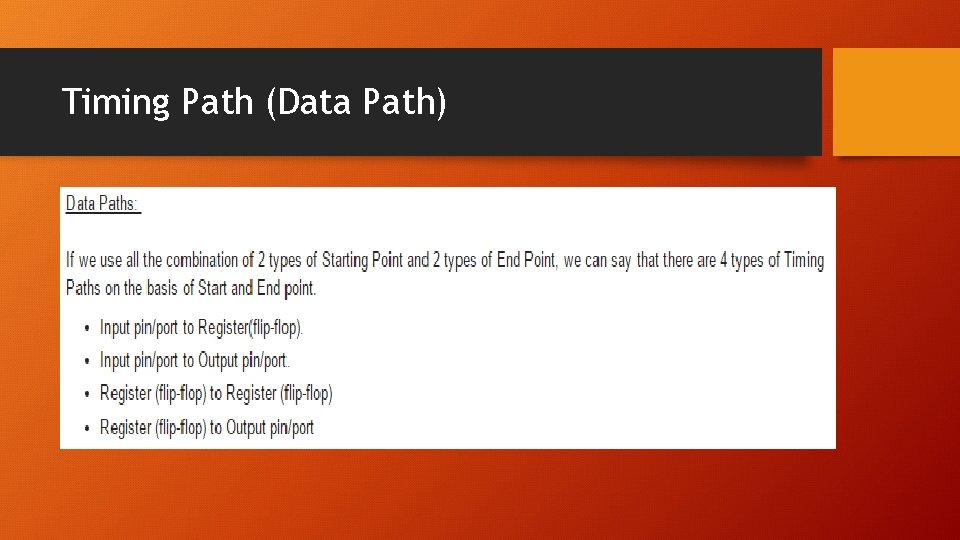

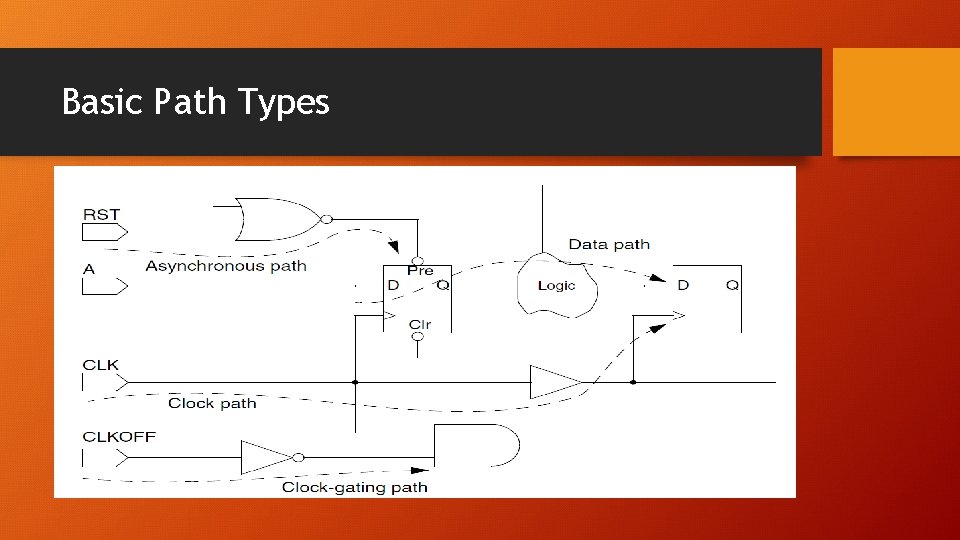

Timing Path (Data Path)

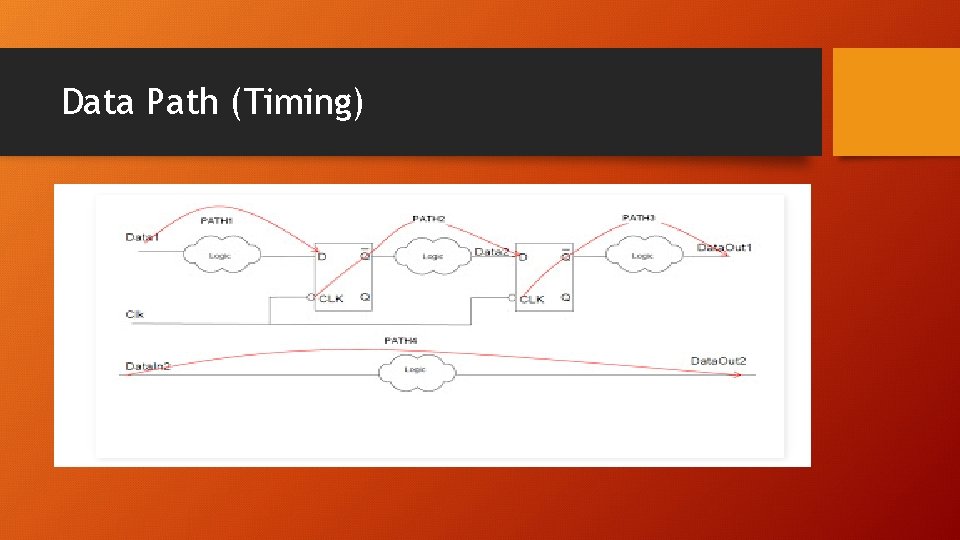

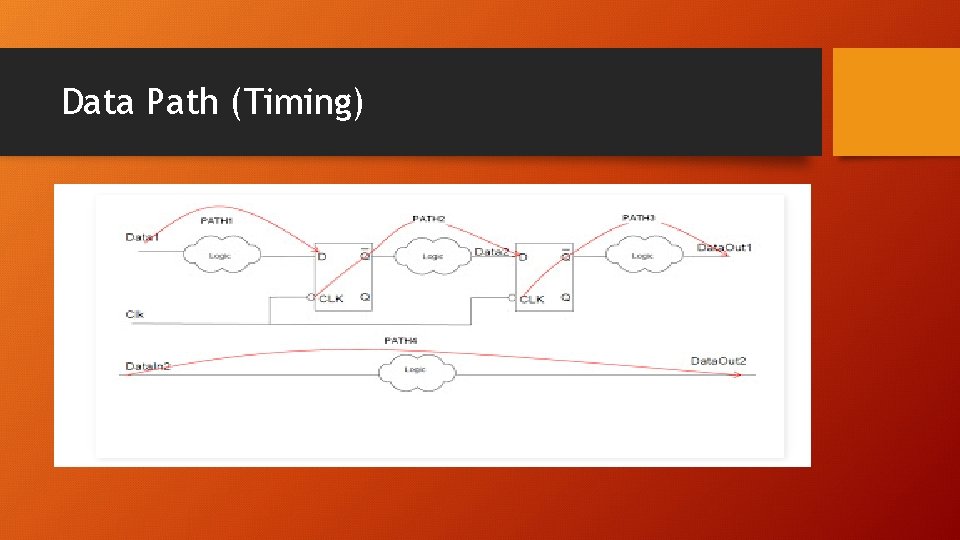

Data Path (Timing)

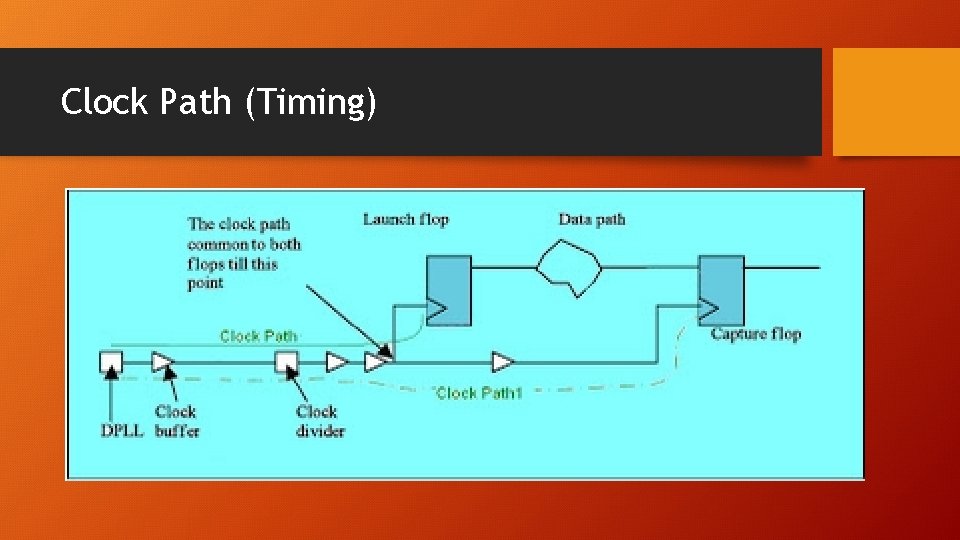

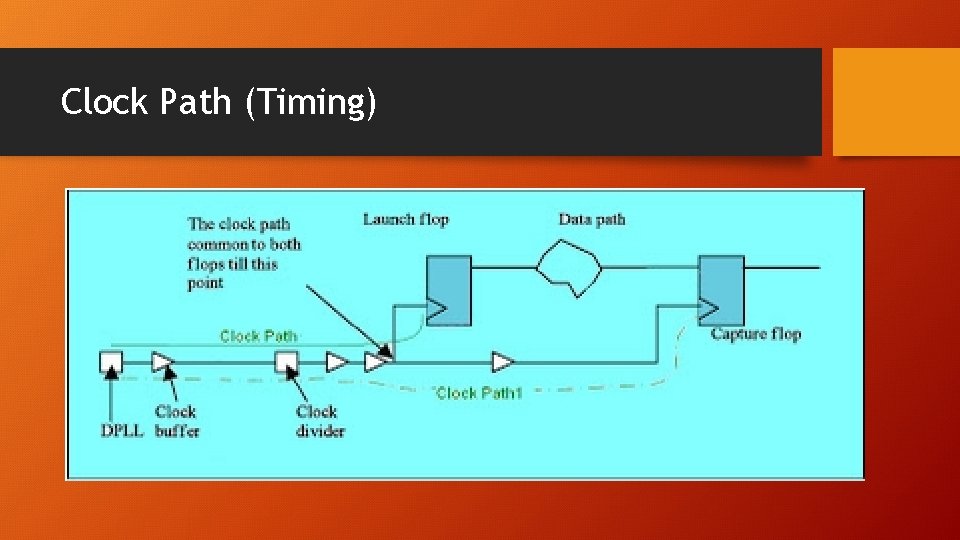

Clock Path (Timing)

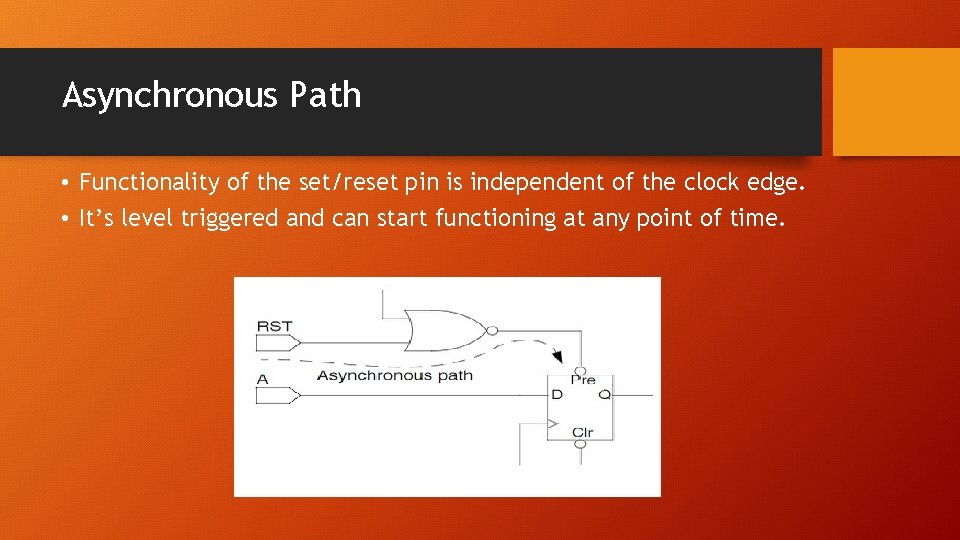

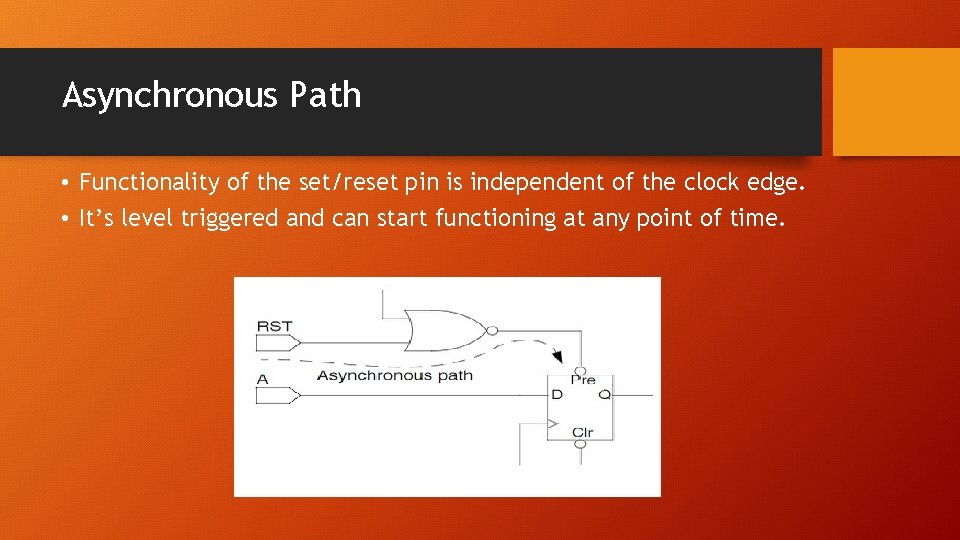

Asynchronous Path • Functionality of the set/reset pin is independent of the clock edge. • It’s level triggered and can start functioning at any point of time.

Basic Path Types

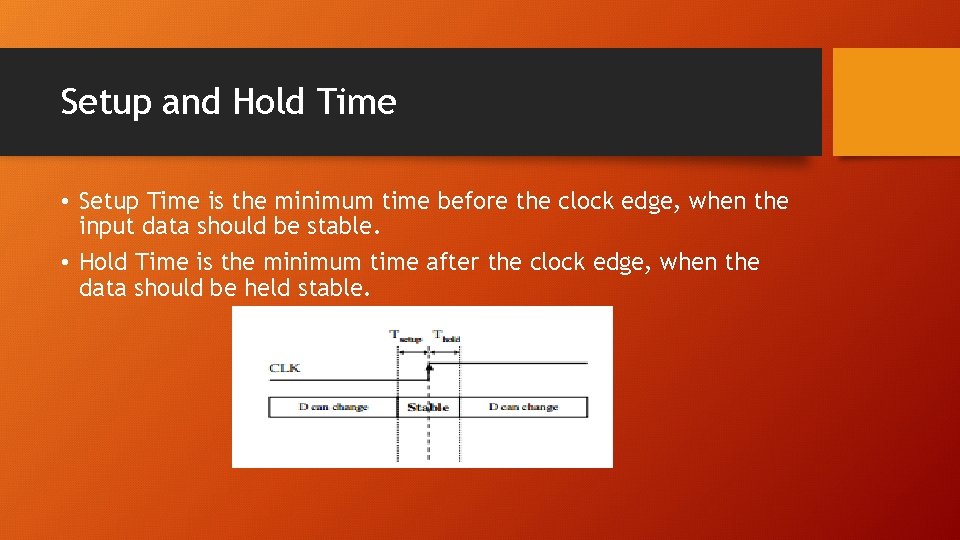

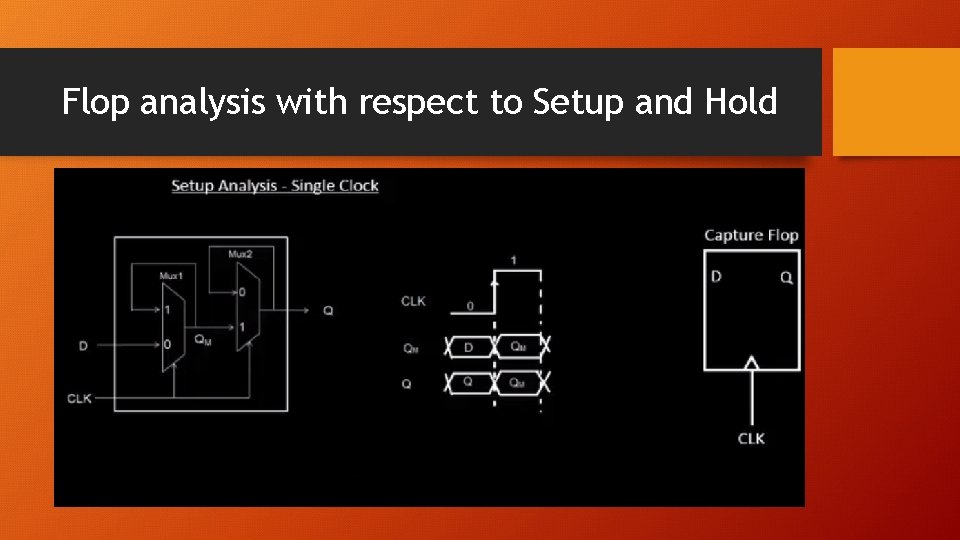

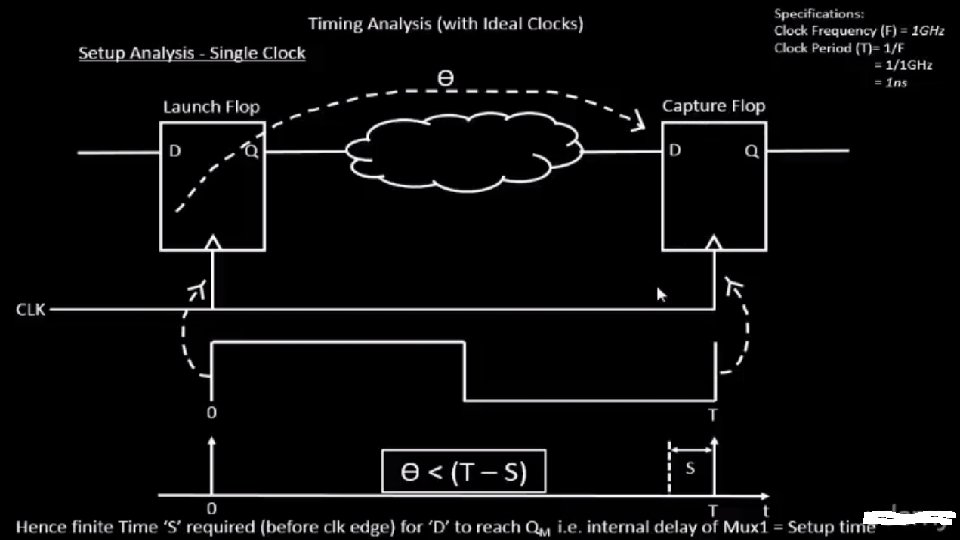

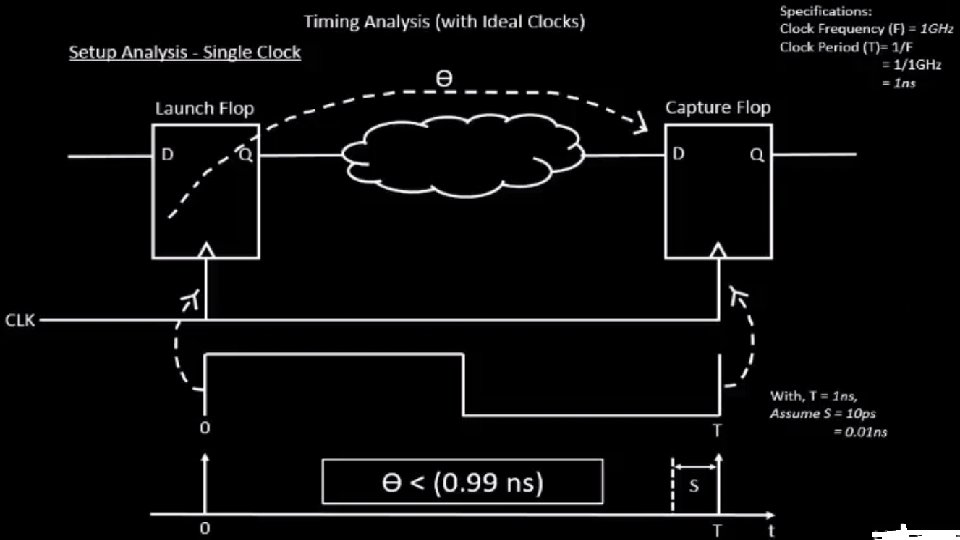

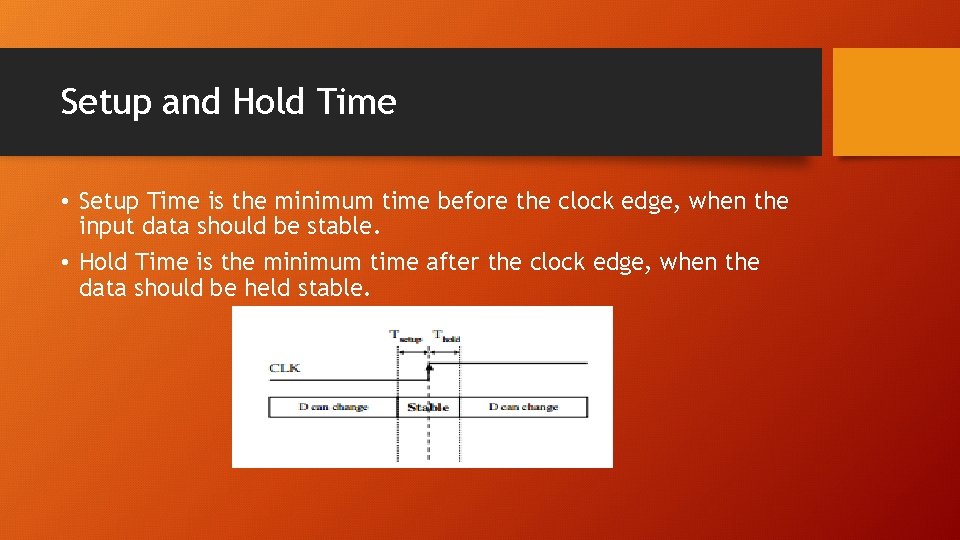

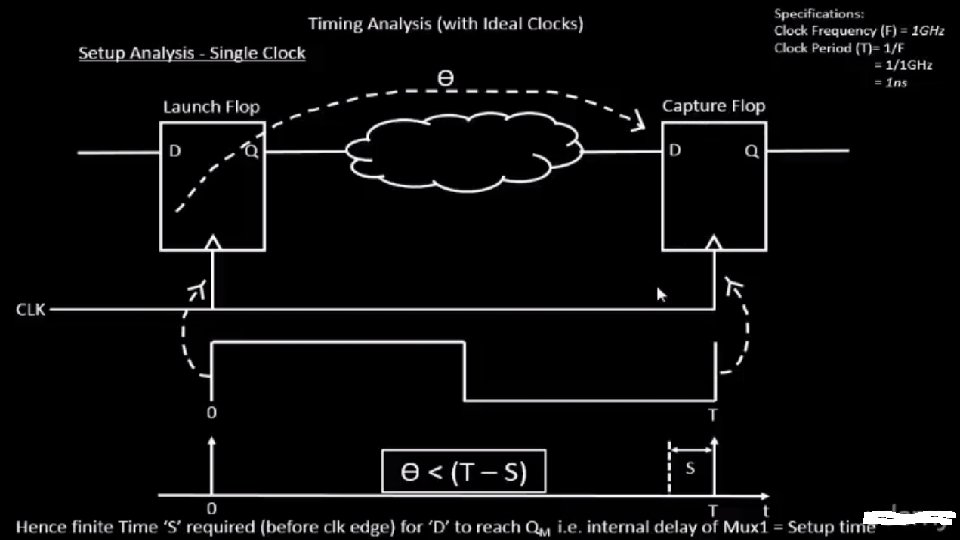

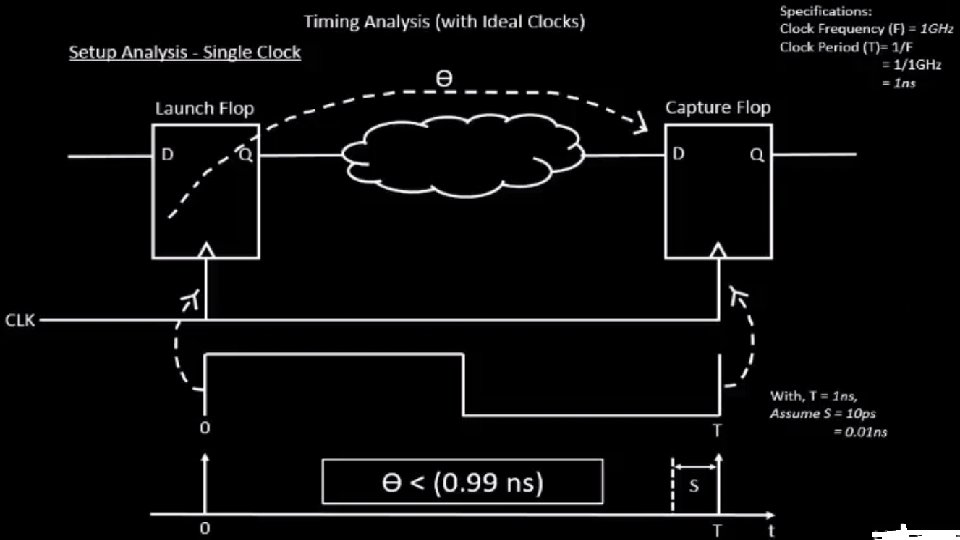

Setup and Hold Time • Setup Time is the minimum time before the clock edge, when the input data should be stable. • Hold Time is the minimum time after the clock edge, when the data should be held stable.

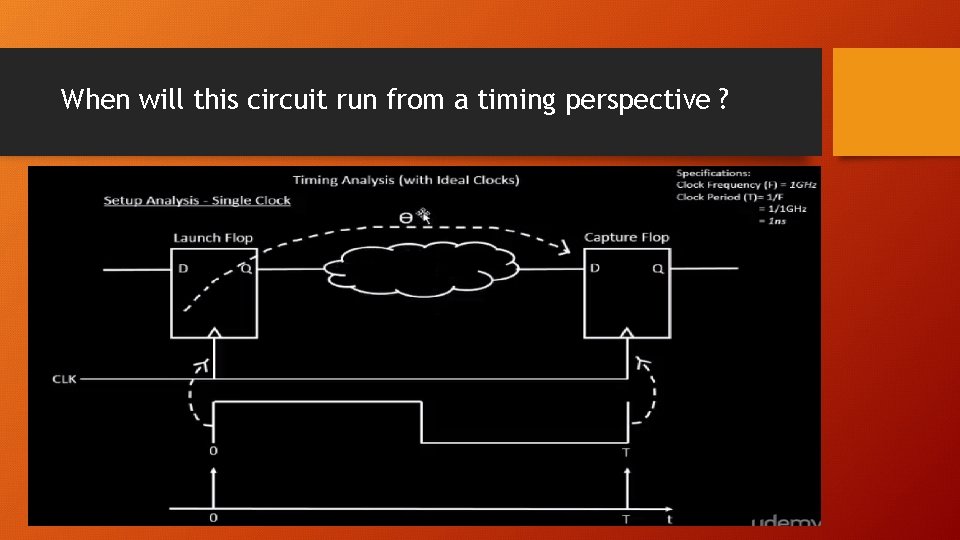

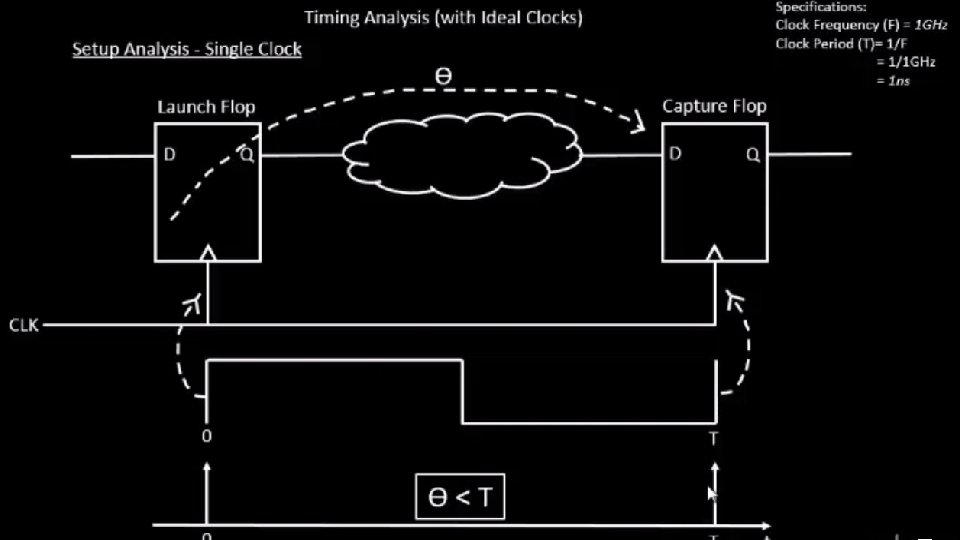

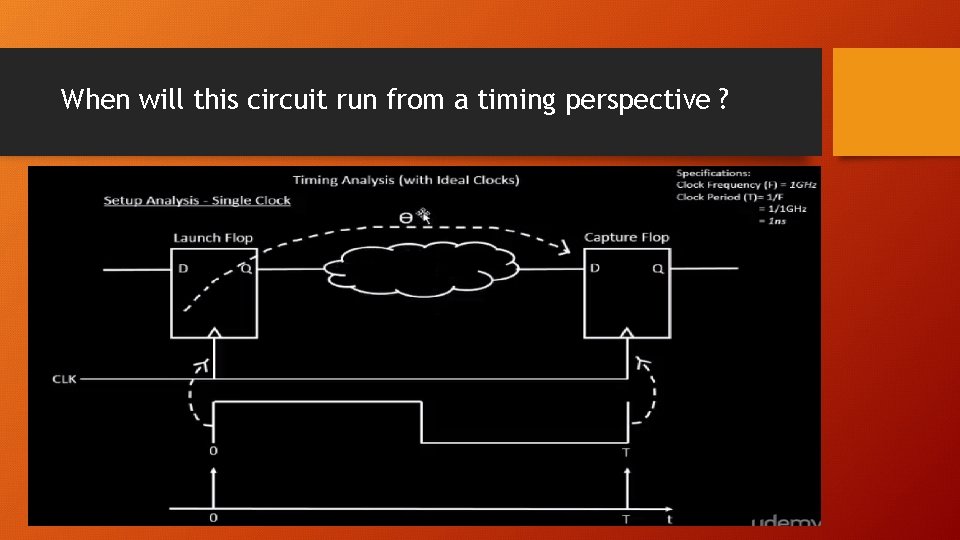

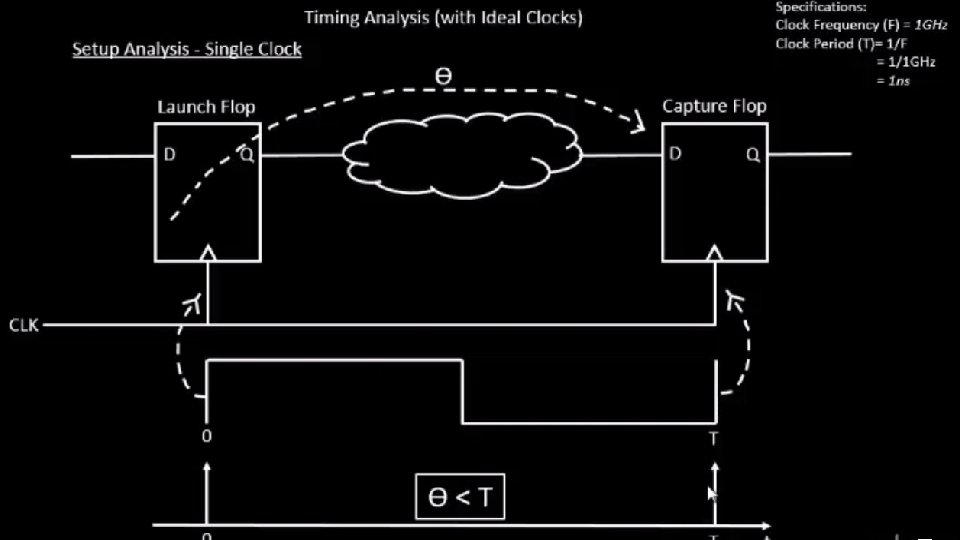

When will this circuit run from a timing perspective ?

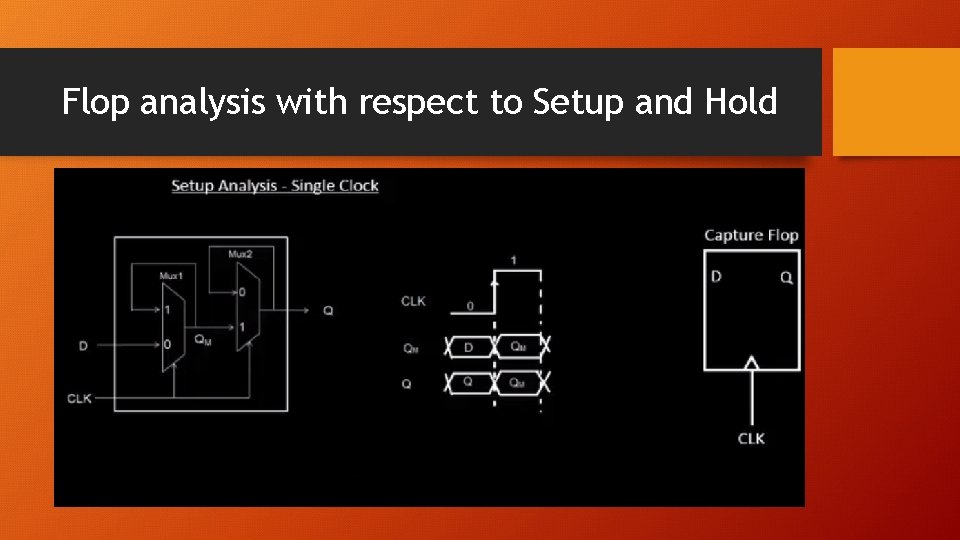

Flop analysis with respect to Setup and Hold

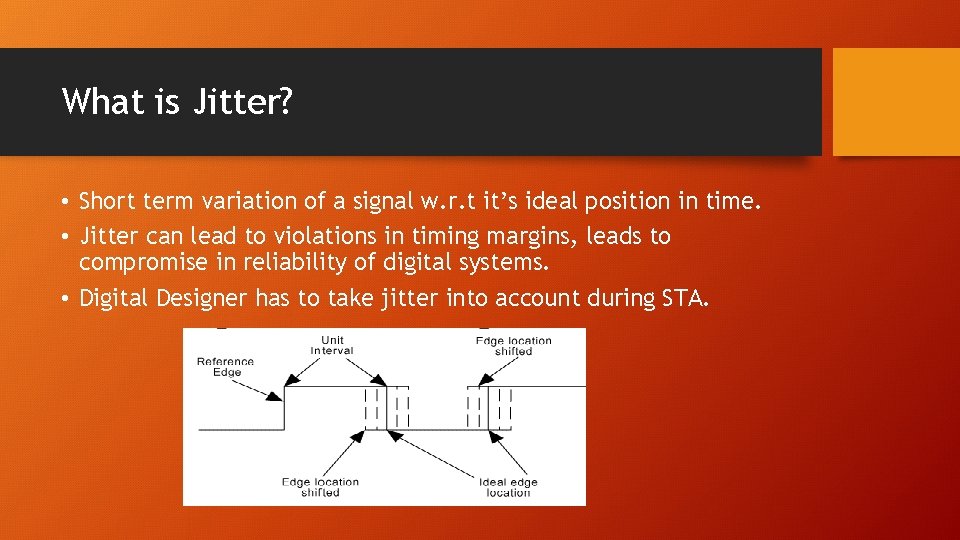

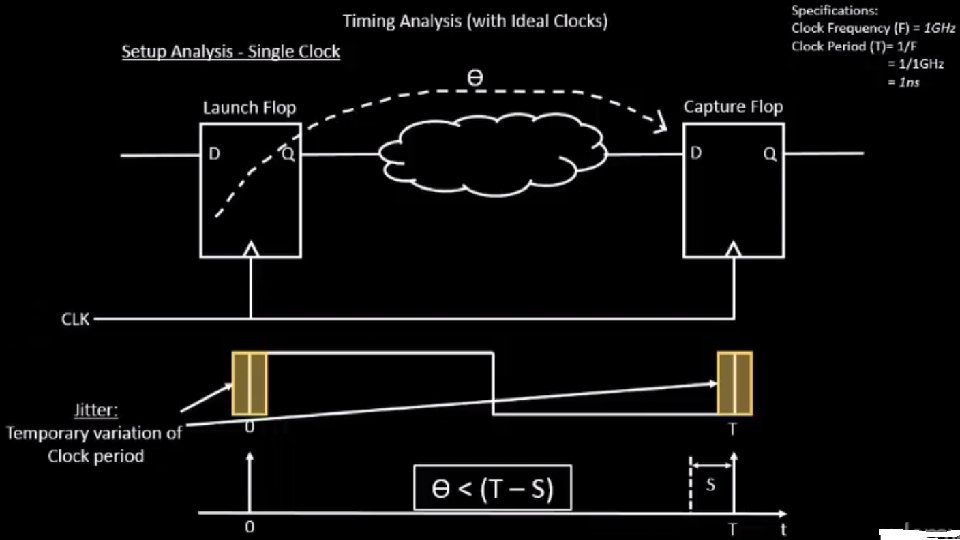

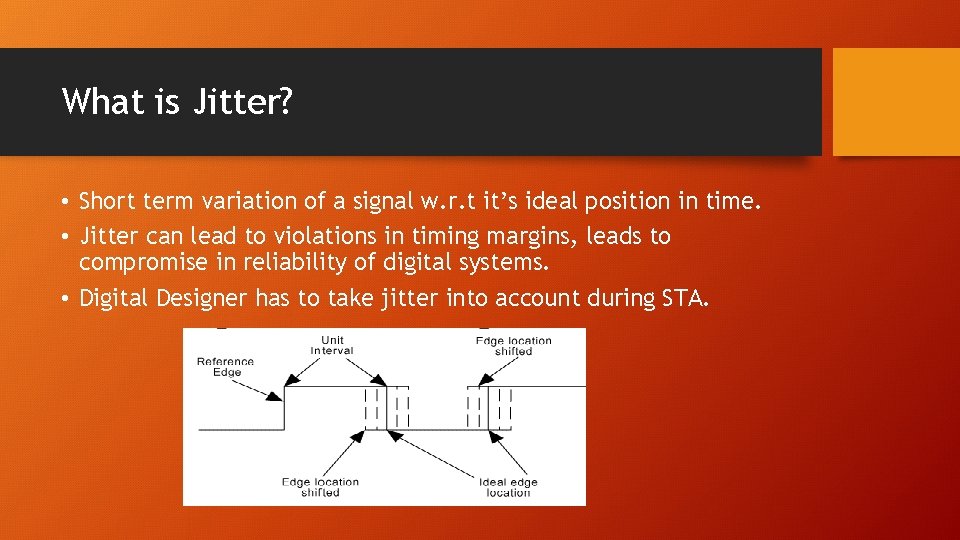

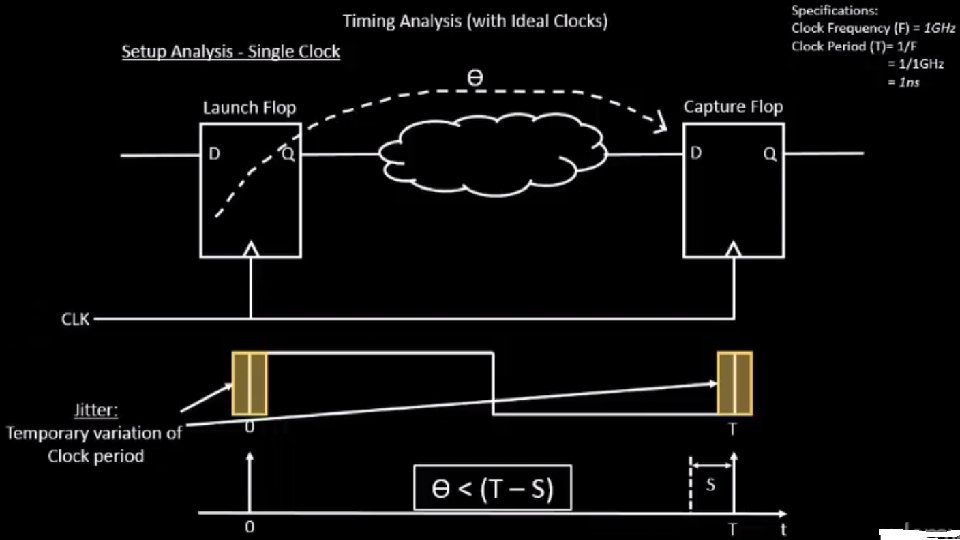

What is Jitter? • Short term variation of a signal w. r. t it’s ideal position in time. • Jitter can lead to violations in timing margins, leads to compromise in reliability of digital systems. • Digital Designer has to take jitter into account during STA.

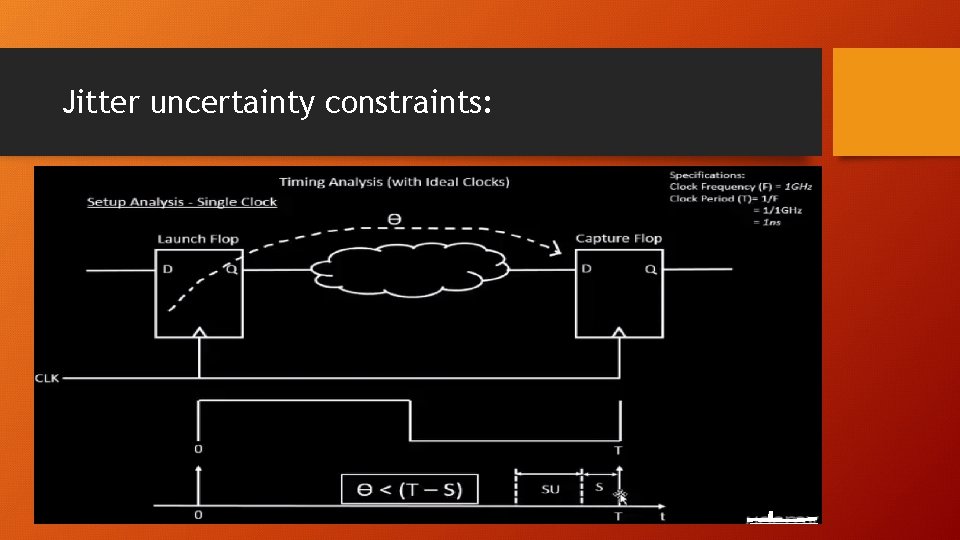

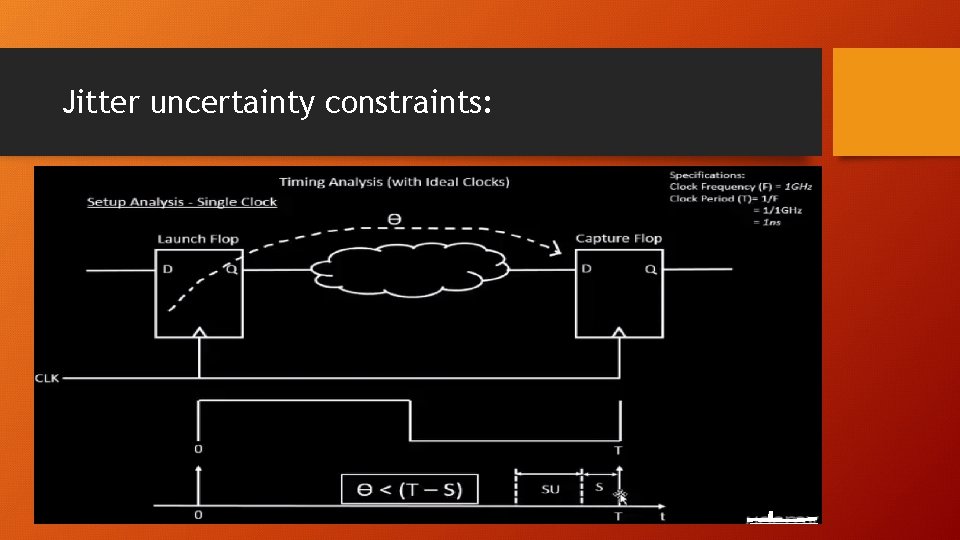

Jitter uncertainty constraints:

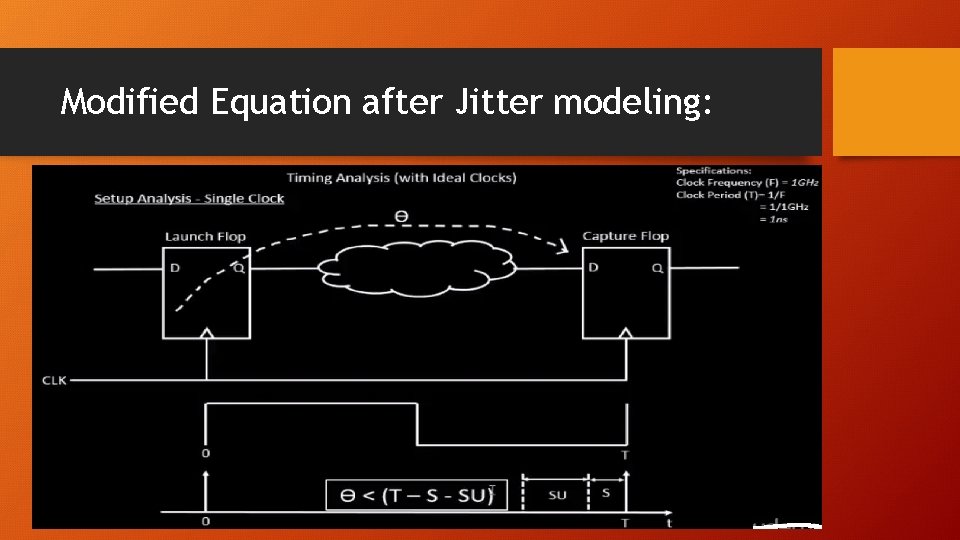

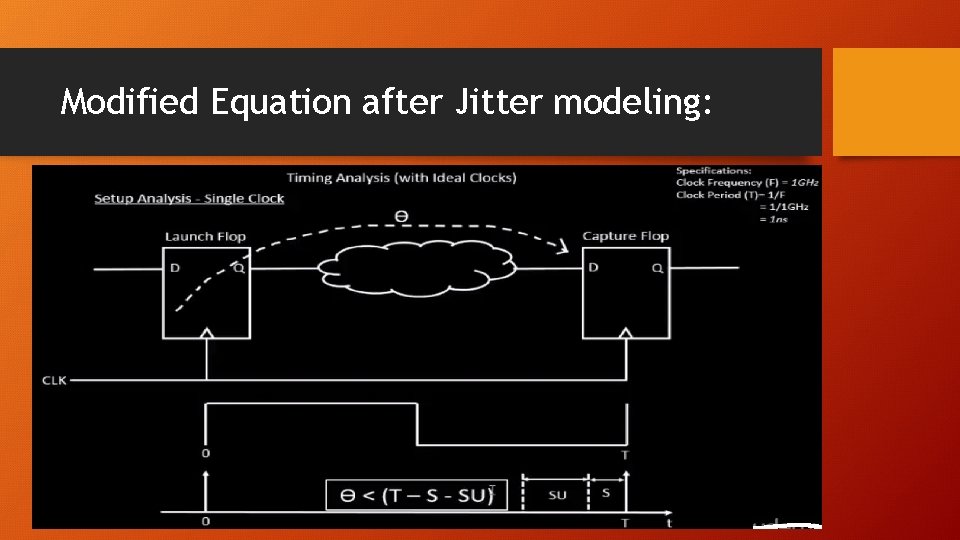

Modified Equation after Jitter modeling:

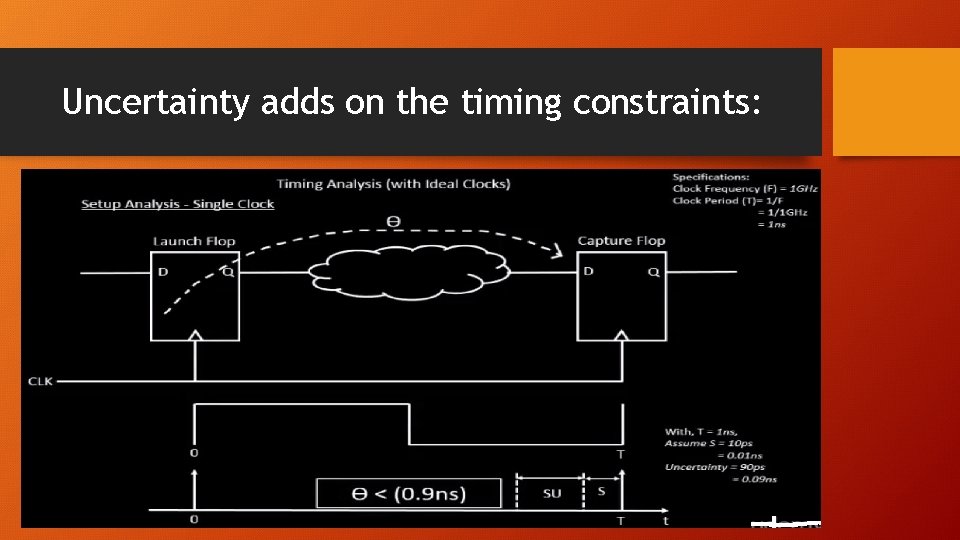

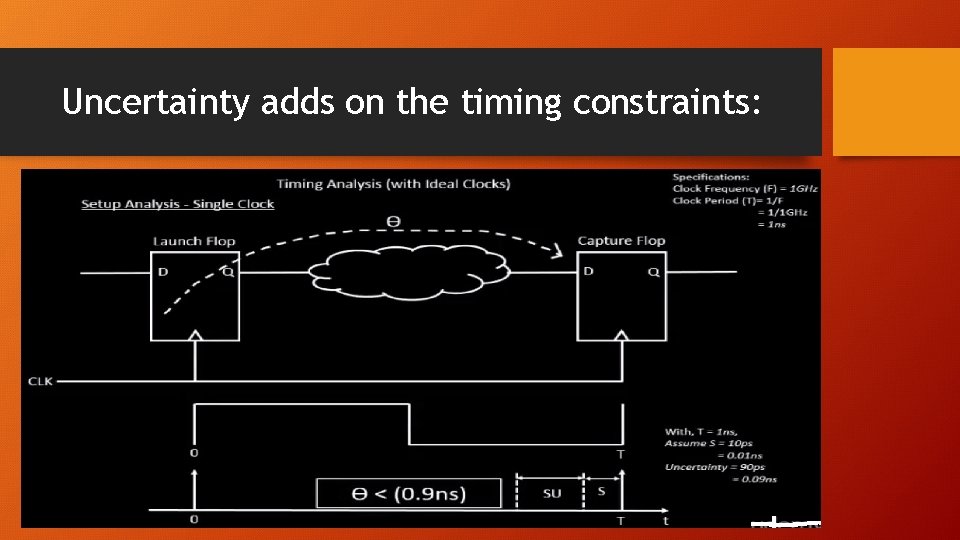

Uncertainty adds on the timing constraints:

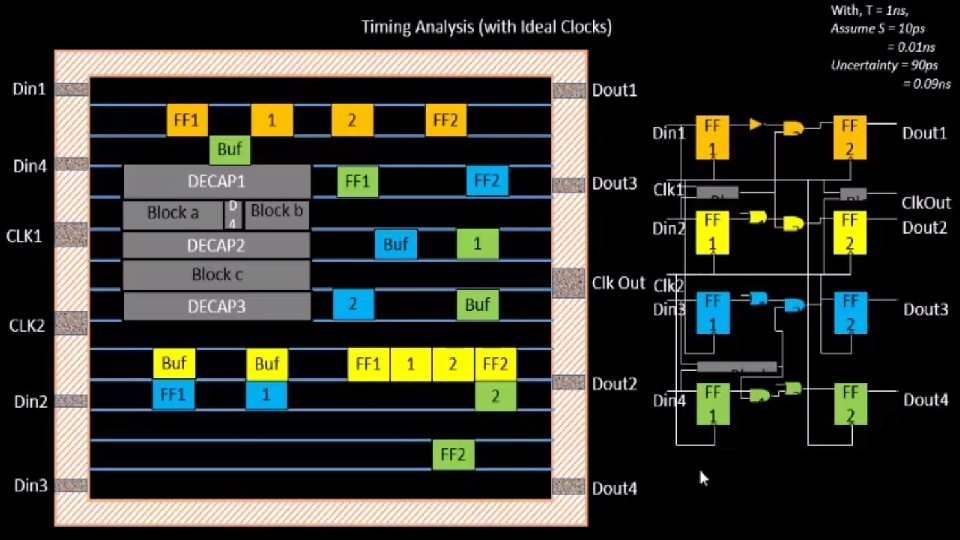

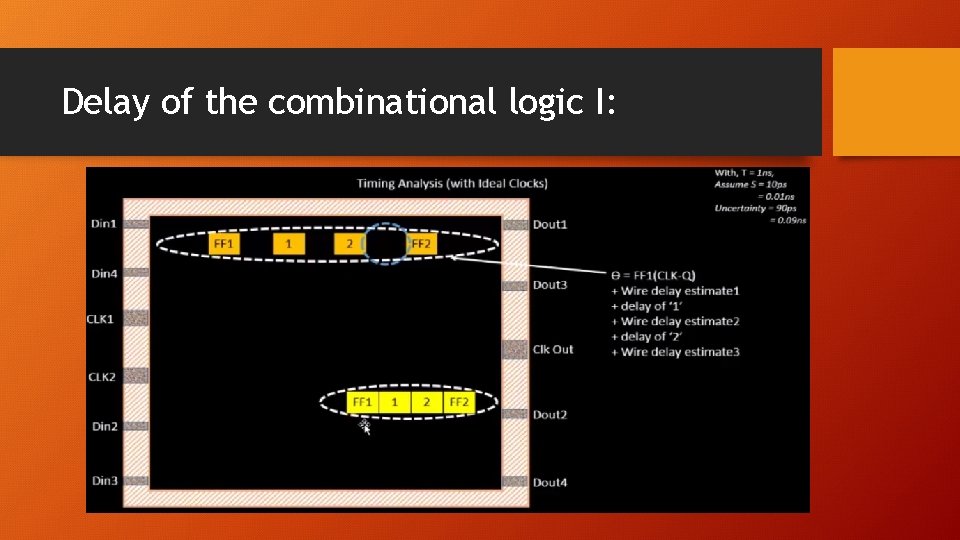

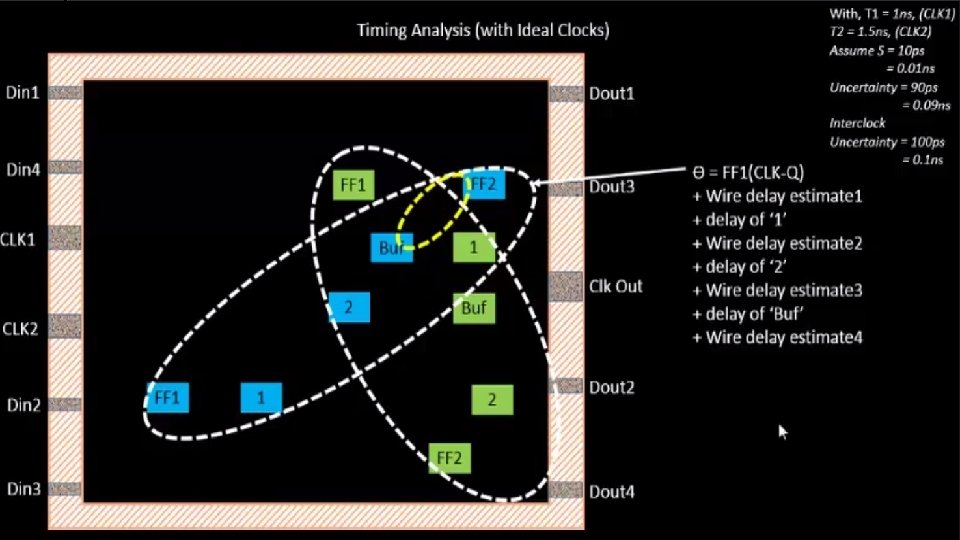

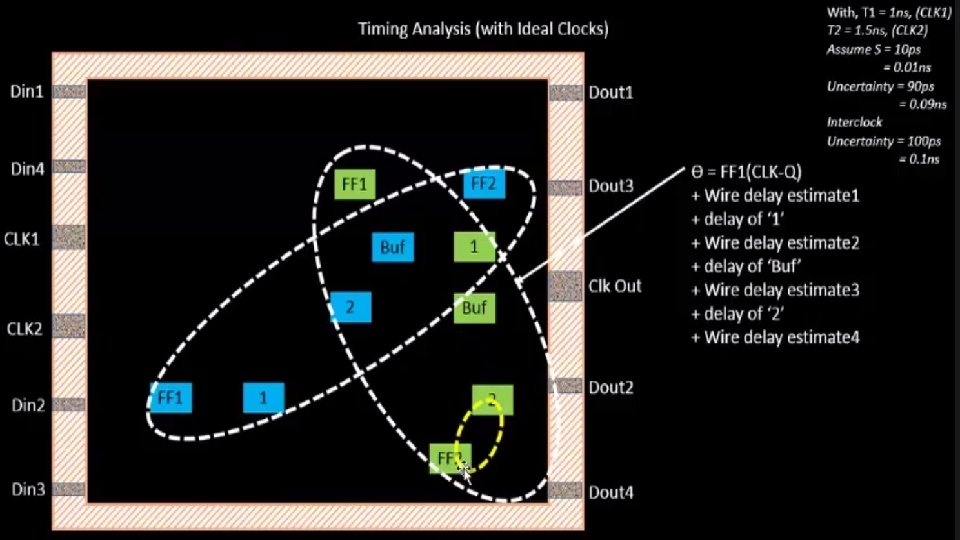

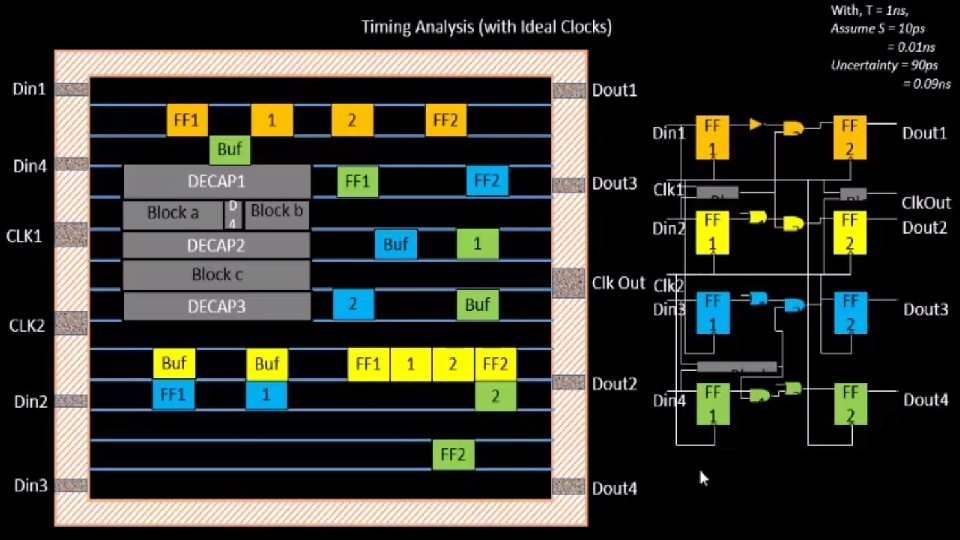

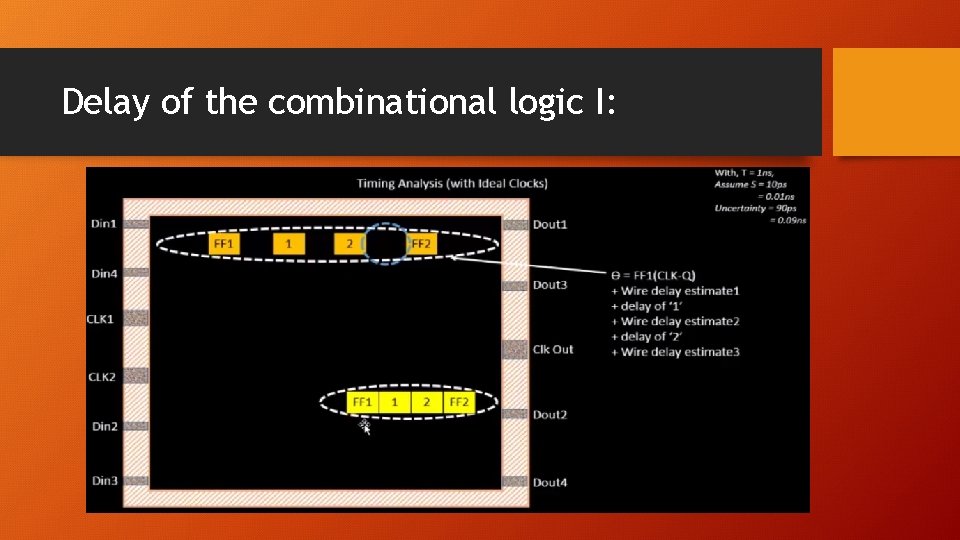

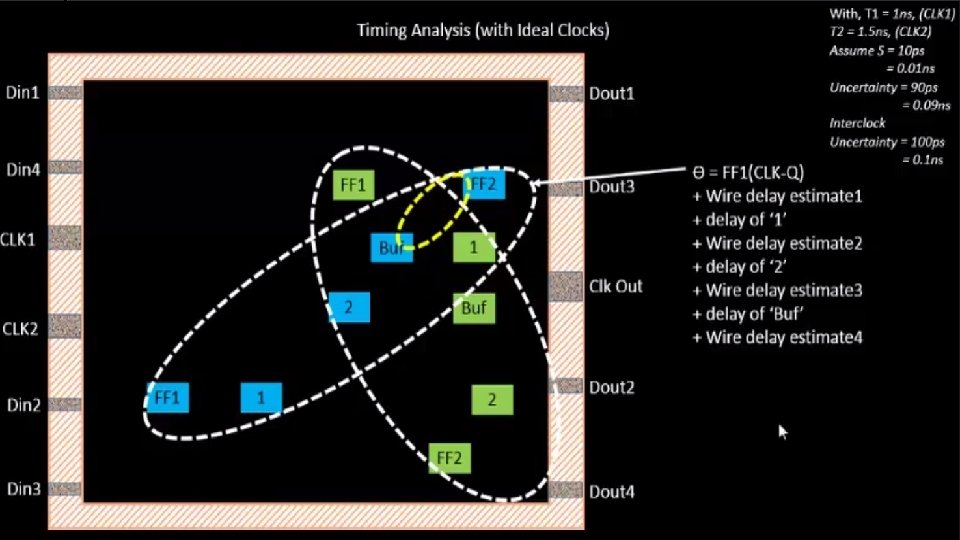

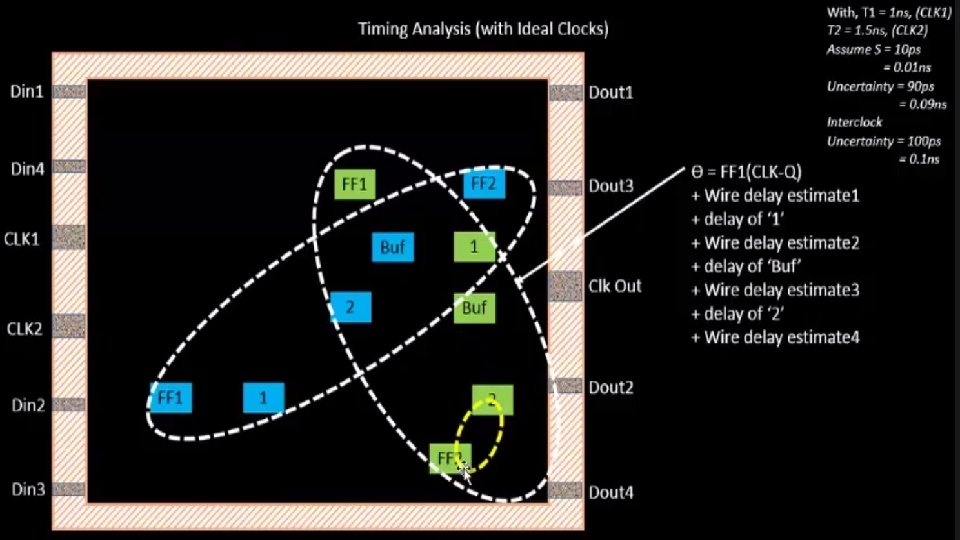

Delay of the combinational logic I:

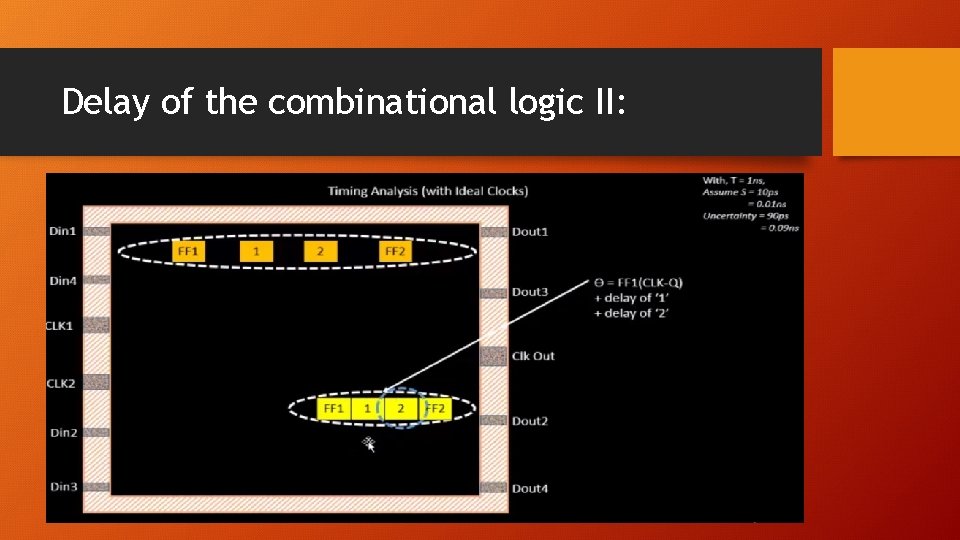

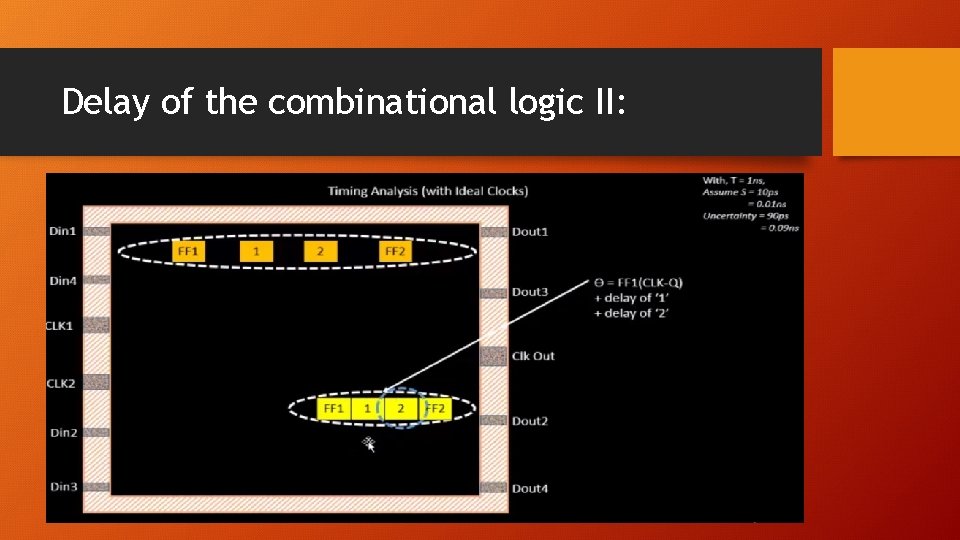

Delay of the combinational logic II:

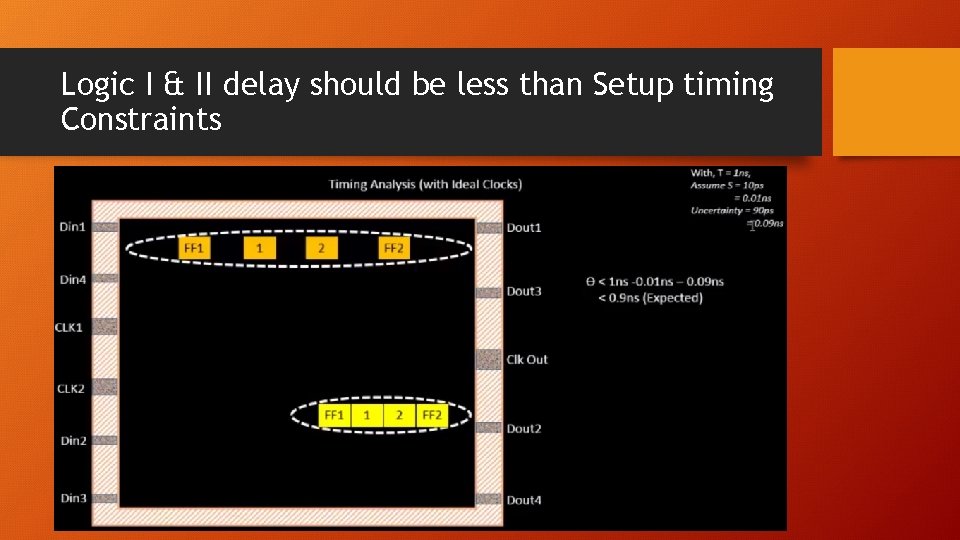

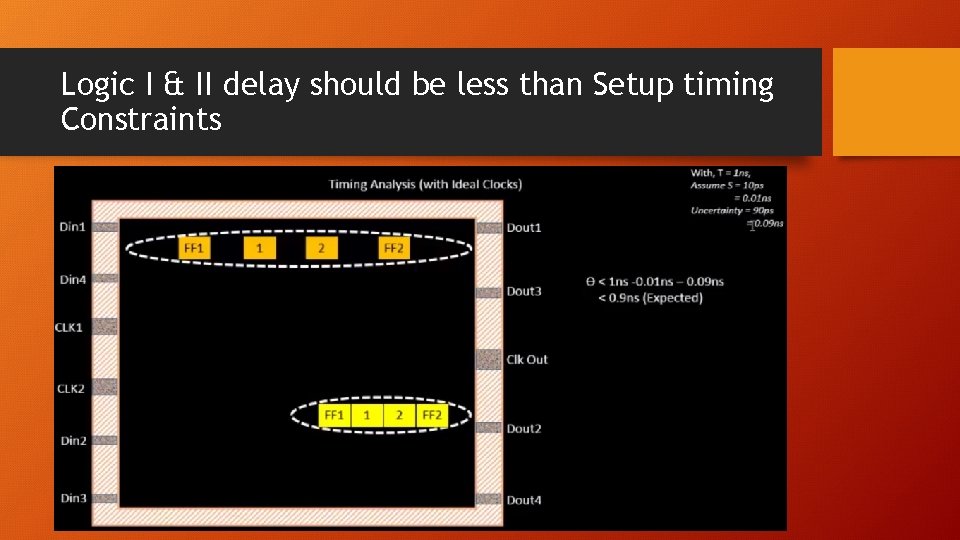

Logic I & II delay should be less than Setup timing Constraints

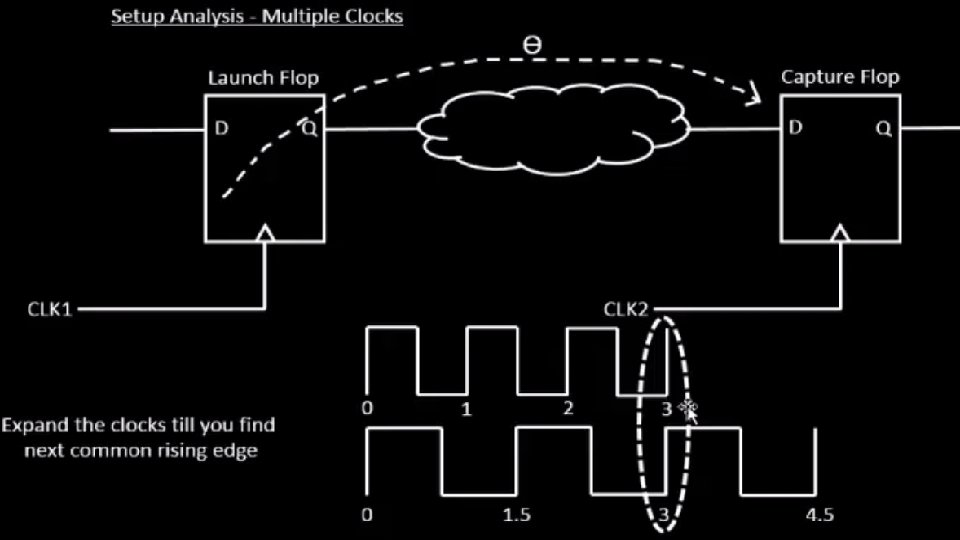

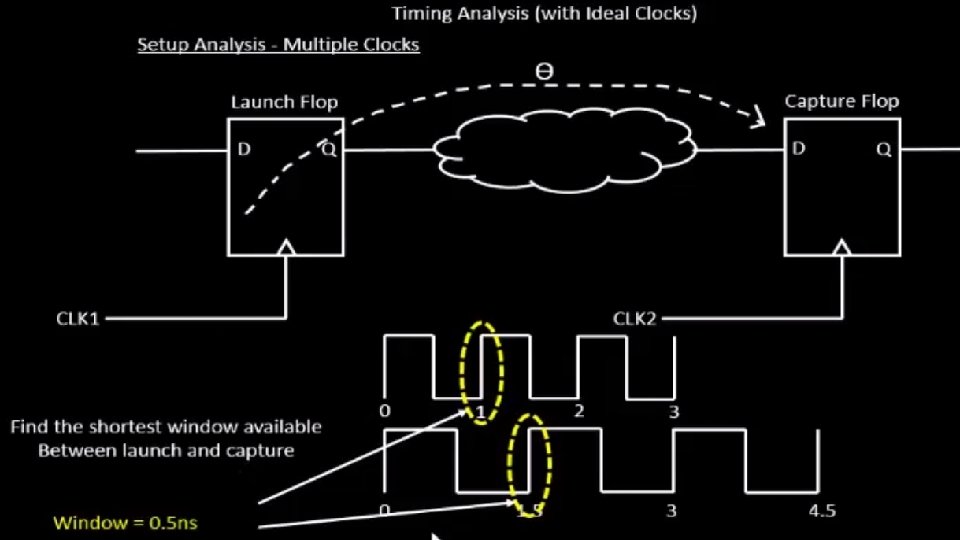

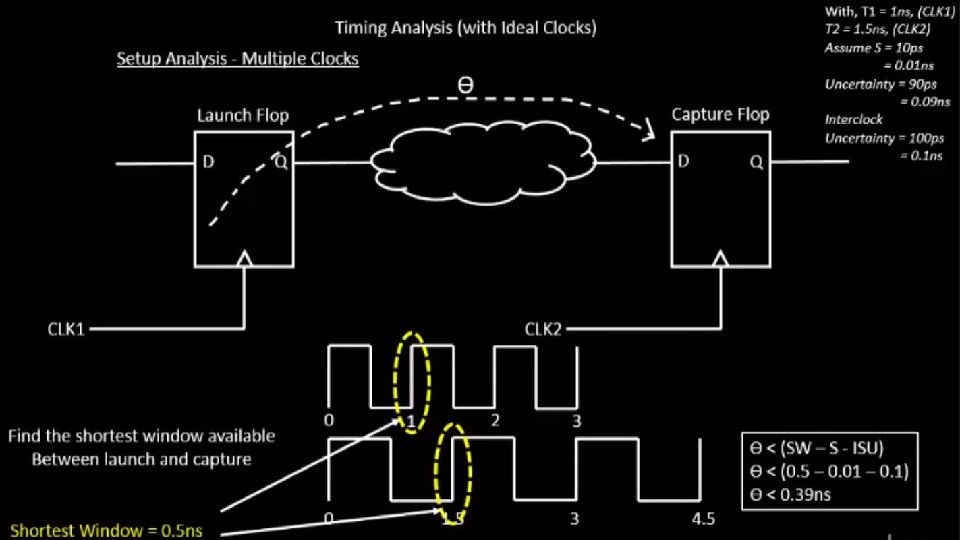

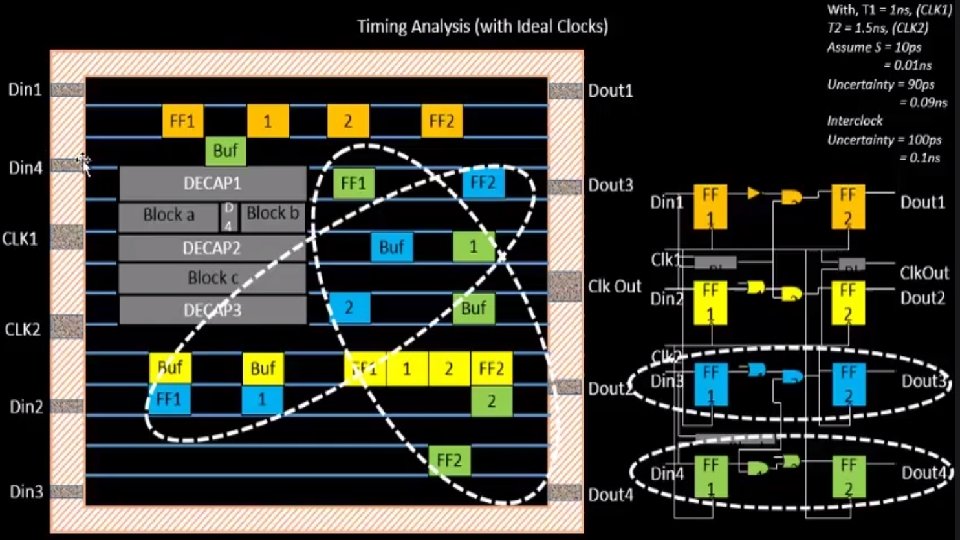

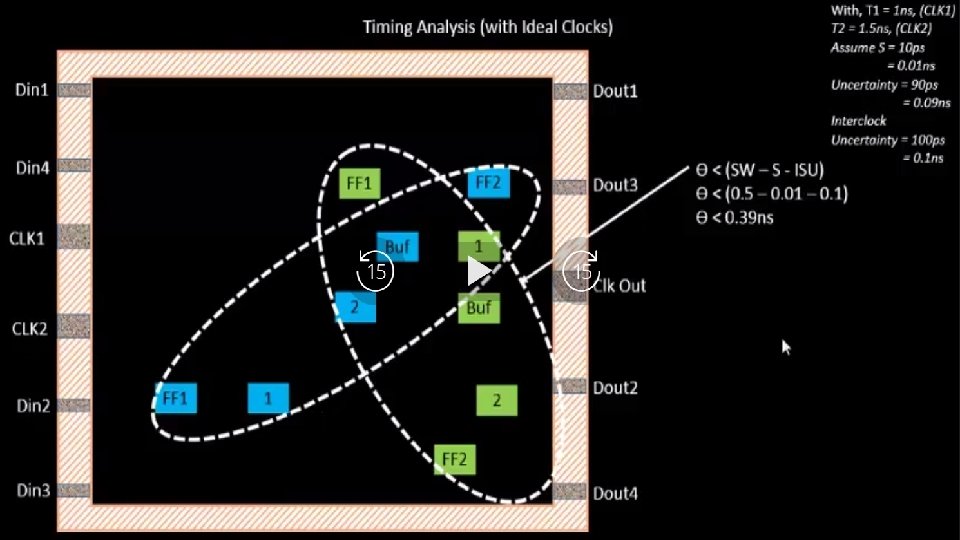

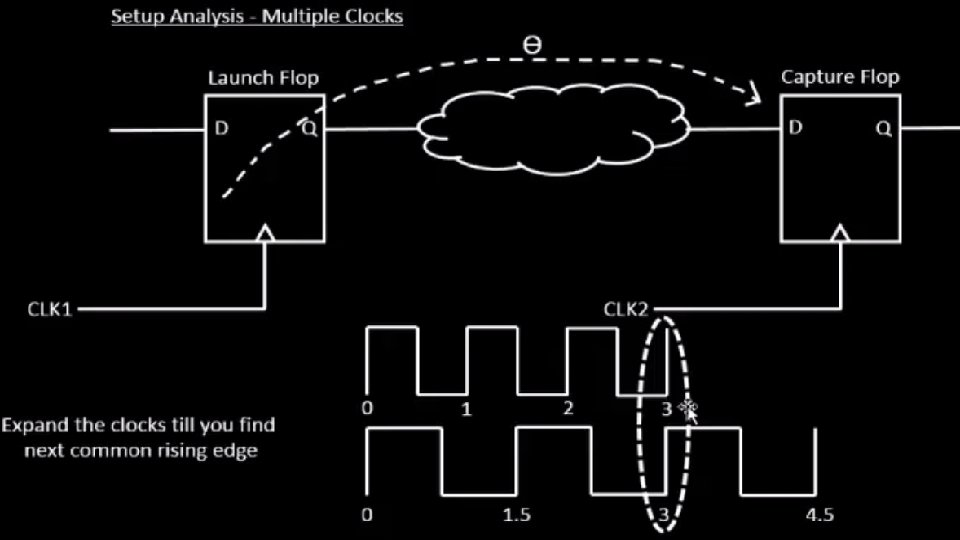

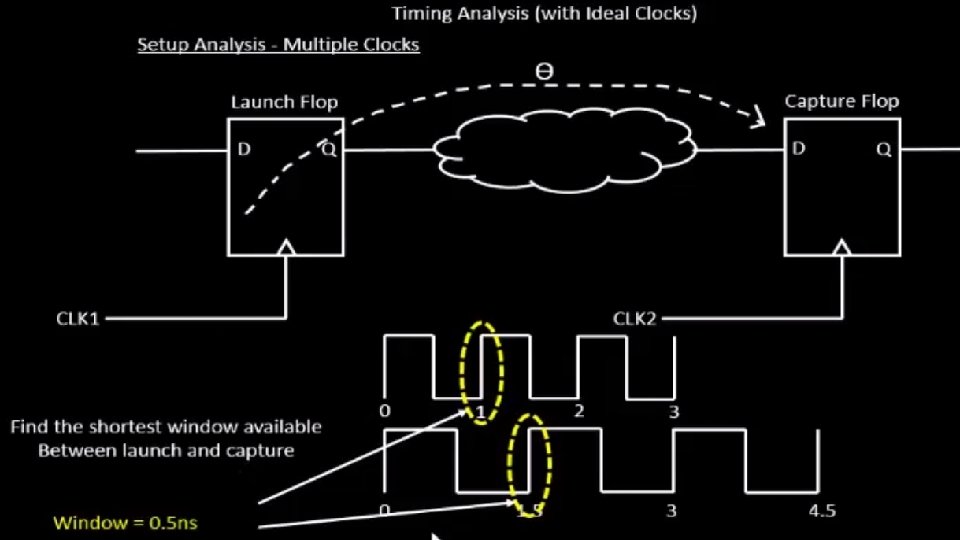

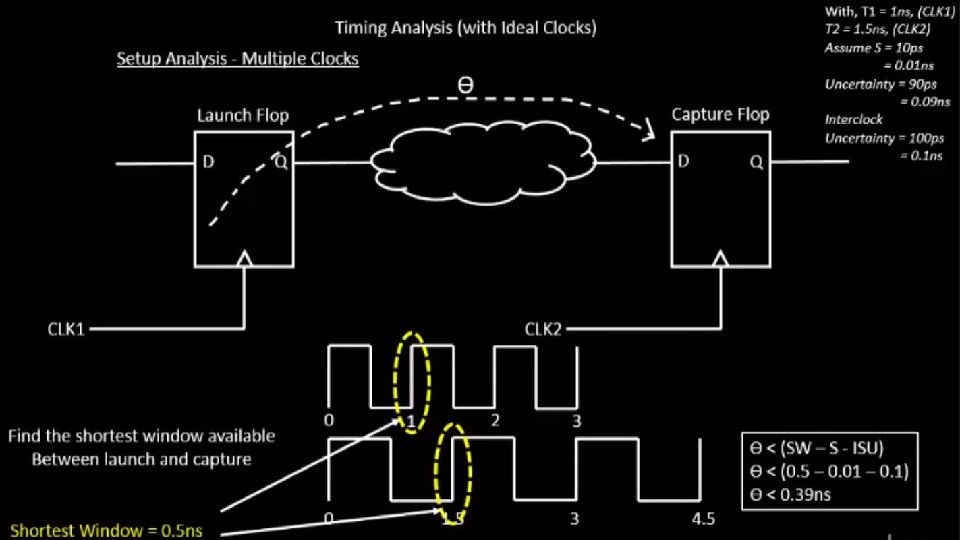

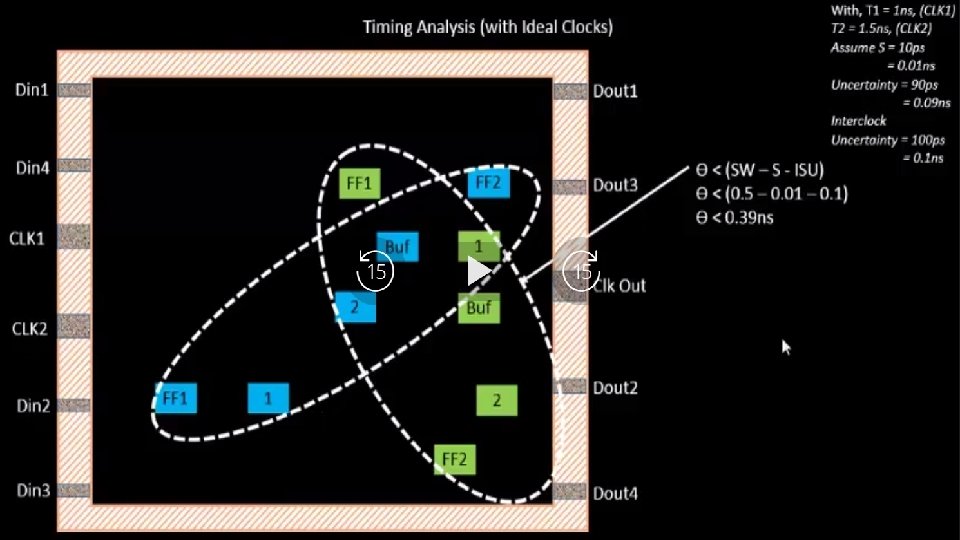

Setup Analysis with Multiple Clocks • There will be two different clock sources for the two flops. • The two clocks will be related to one other : a valid timing path between the two clocks. • The two flops will be synchronous in nature but asynchronous to one another. • Challenge is to design with uncommon rising edges.

Hold Time Analysis = Think reverse of Setup • Hold Time Check is done on the same clock edge unlike Setup Time • Delay of the Combinational logic should be greater than the Hold Time as the data needs to be held stable for a finite amount of time after clock edge, before new data replaces it. • Hold Time analysis helps us retain functional credibility of the design and does not determine the frequency of the design.

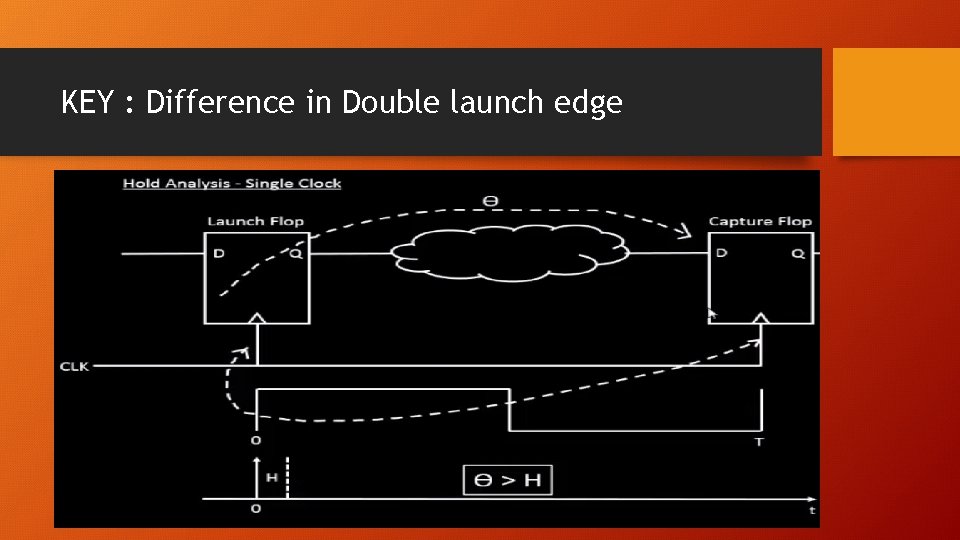

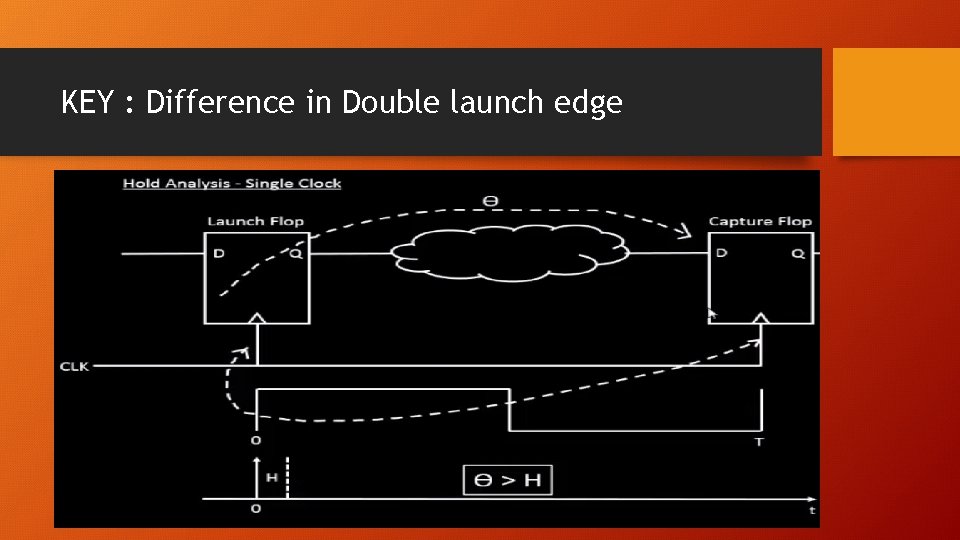

KEY : Difference in Double launch edge

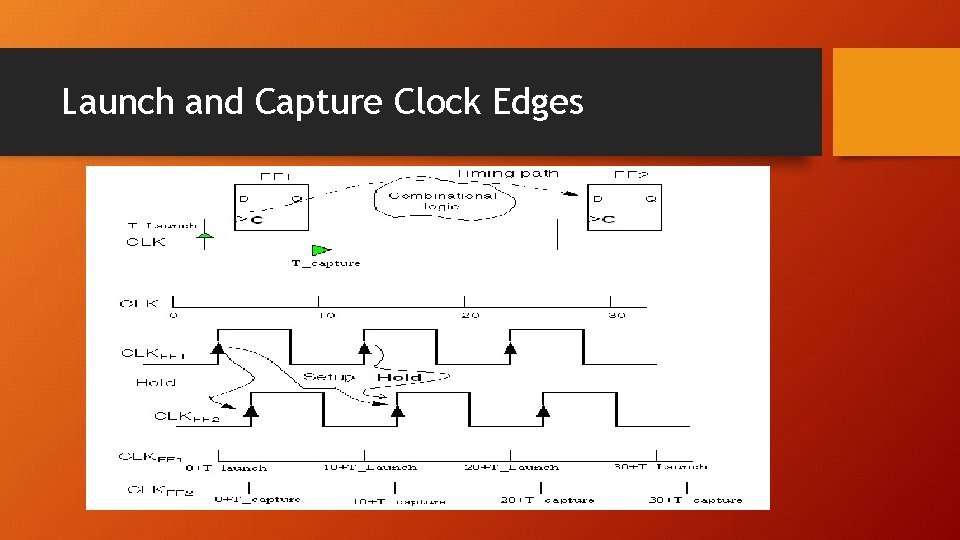

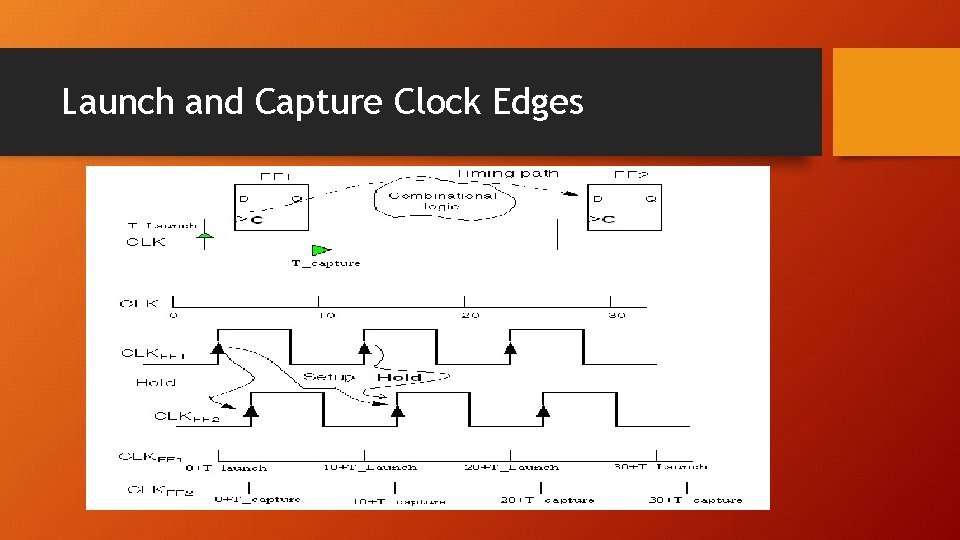

Launch and Capture Clock Edges