Introduction to Programmable Logic Devices Edward Freeman STFC

Introduction to Programmable Logic Devices Edward Freeman STFC Technology Department Detector & Electronics Division

PPD Lectures Programmable Logic is a Key Underlying Technology for PP Experiments. n First-Level and High-Level Triggering n Data Transport (Networks) n Computers interacting with Hardware (Networks) n Silicon Trackers (Millions of Data Channels) Commercial Devices. Developments driven by Industry. Telecomms, Gaming, Aerospace, Automotive, Set-top boxes…. edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

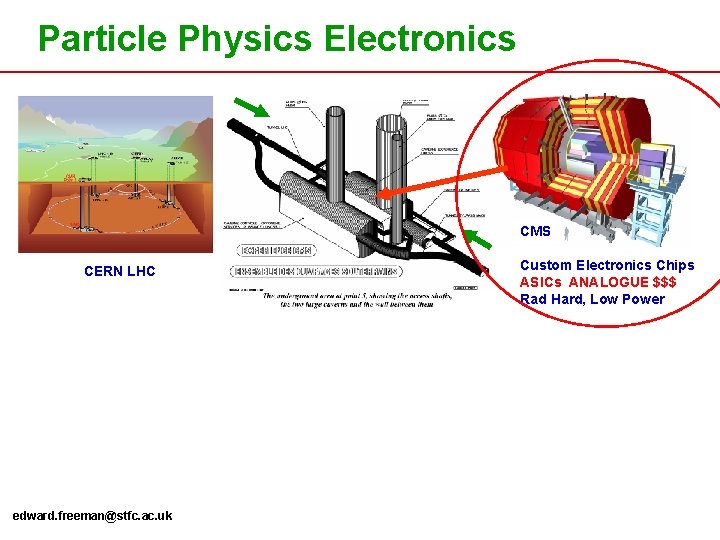

Particle Physics Electronics CMS CERN LHC edward. freeman@stfc. ac. uk Custom Electronics Chips ASICs ANALOGUE $$$ Rad Hard, Low Power The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

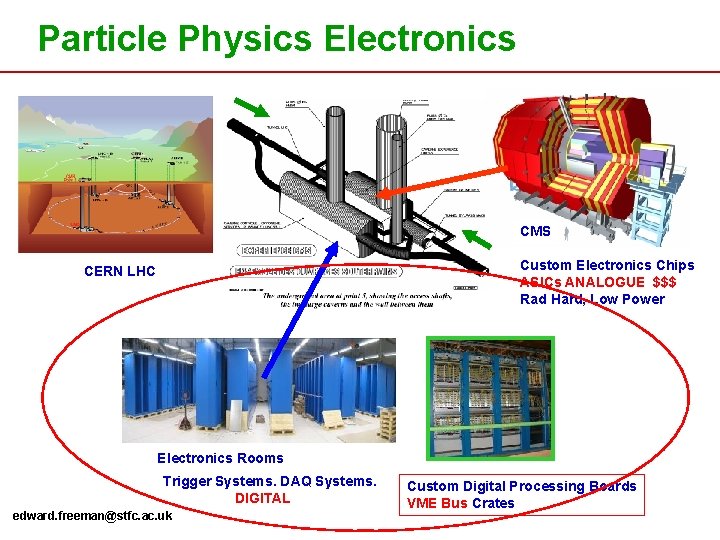

Particle Physics Electronics CMS Custom Electronics Chips ASICs ANALOGUE $$$ Rad Hard, Low Power CERN LHC Electronics Rooms Trigger Systems. DAQ Systems. DIGITAL edward. freeman@stfc. ac. uk Custom Digital Processing Boards VME Bus Crates The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

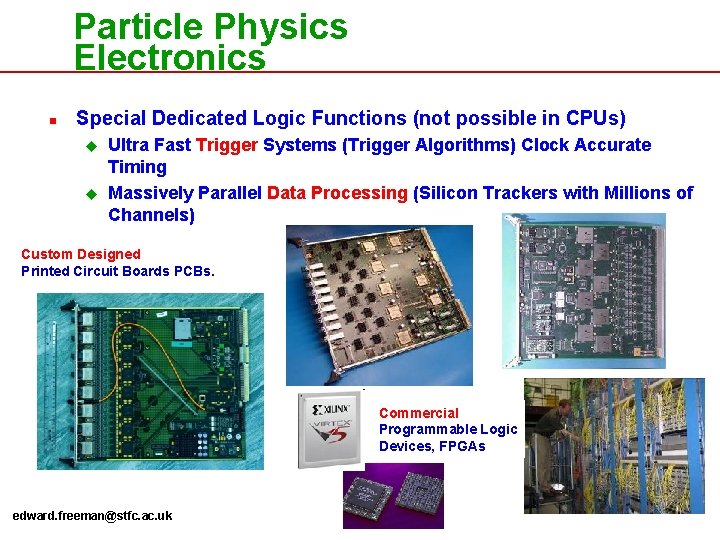

Particle Physics Electronics n Special Dedicated Logic Functions (not possible in CPUs) u u Ultra Fast Trigger Systems (Trigger Algorithms) Clock Accurate Timing Massively Parallel Data Processing (Silicon Trackers with Millions of Channels) Custom Designed Printed Circuit Boards PCBs. Commercial Programmable Logic Devices, FPGAs edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

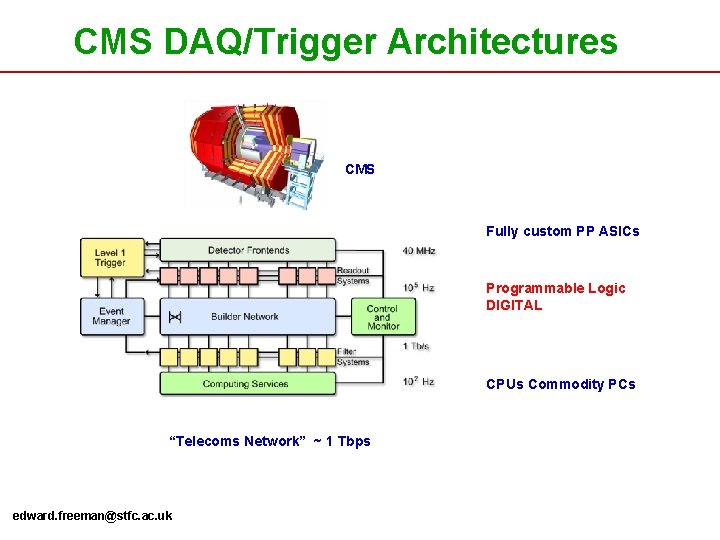

CMS DAQ/Trigger Architectures CMS Fully custom PP ASICs Programmable Logic DIGITAL CPUs Commodity PCs “Telecoms Network” ~ 1 Tbps edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Lecture Outline n Programmable Logic Devices u u n FPGA Field Programmable Gate Array u n Basics Evolution Architecture Design Flow u u Hardware Description Languages Design Tools edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

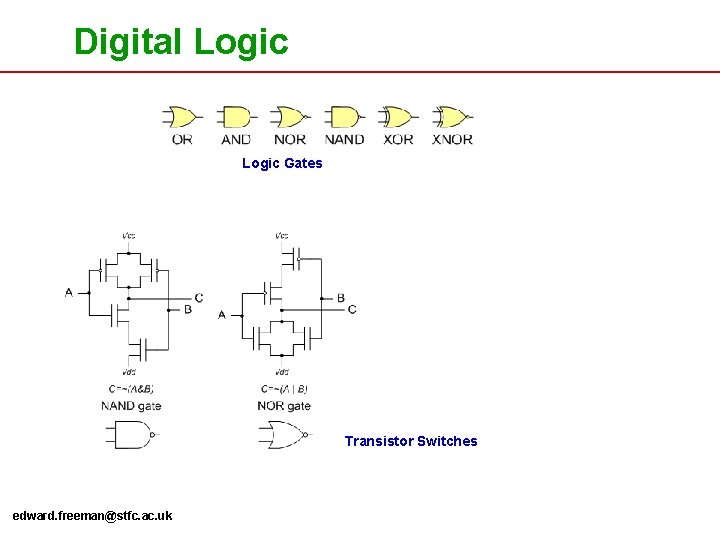

Digital Logic Gates edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Digital Logic Gates Transistor Switches edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

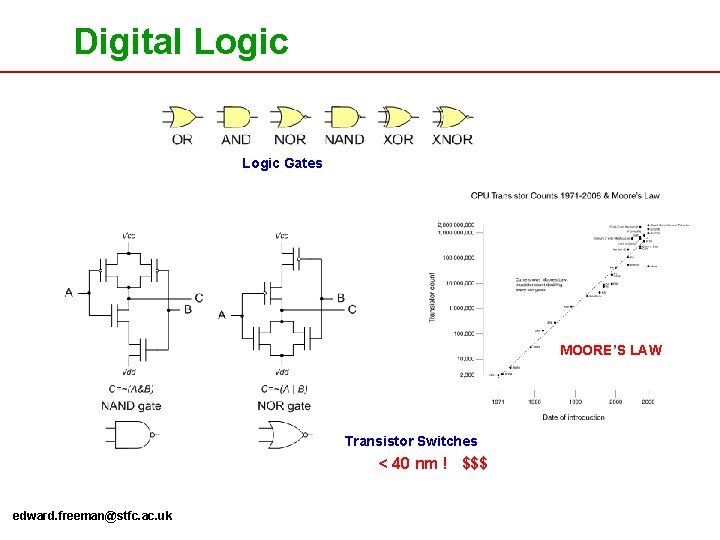

Digital Logic Gates MOORE’S LAW Transistor Switches < 40 nm ! $$$ edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

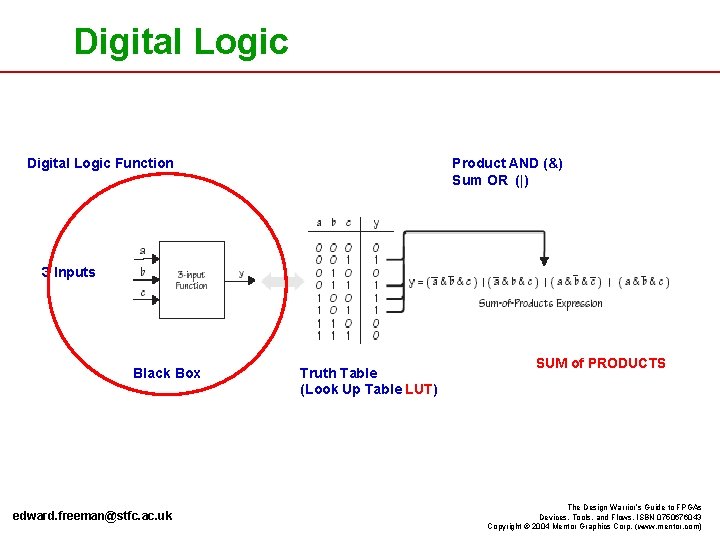

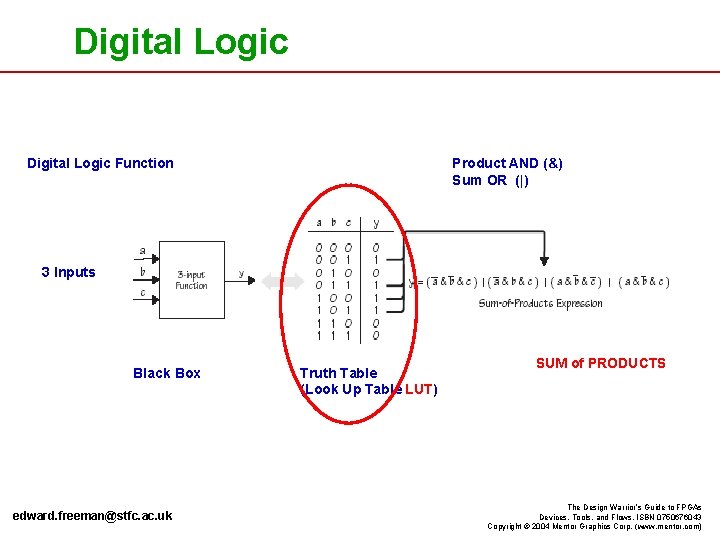

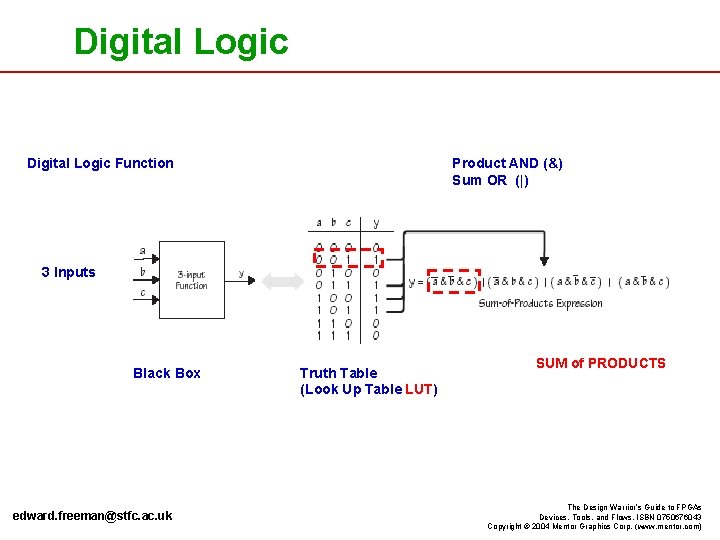

Digital Logic Function Product AND (&) Sum OR (|) 3 Inputs Black Box edward. freeman@stfc. ac. uk Truth Table (Look Up Table LUT) SUM of PRODUCTS The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Digital Logic Function Product AND (&) Sum OR (|) 3 Inputs Black Box edward. freeman@stfc. ac. uk Truth Table (Look Up Table LUT) SUM of PRODUCTS The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Digital Logic Function Product AND (&) Sum OR (|) 3 Inputs Black Box edward. freeman@stfc. ac. uk Truth Table (Look Up Table LUT) SUM of PRODUCTS The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

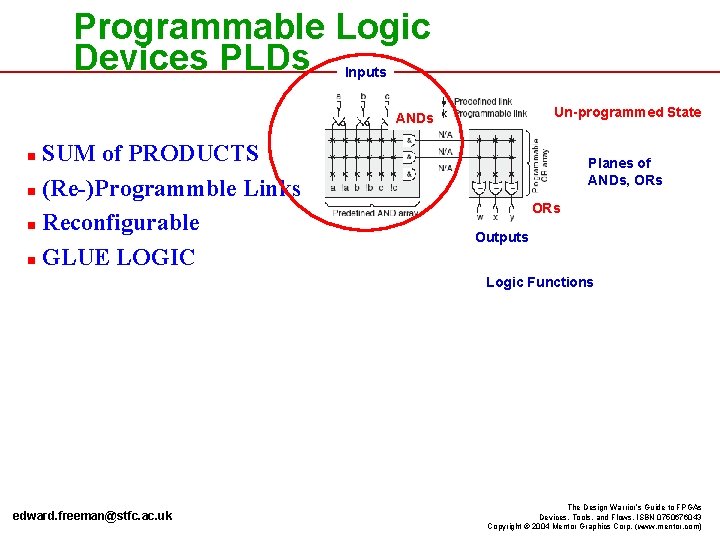

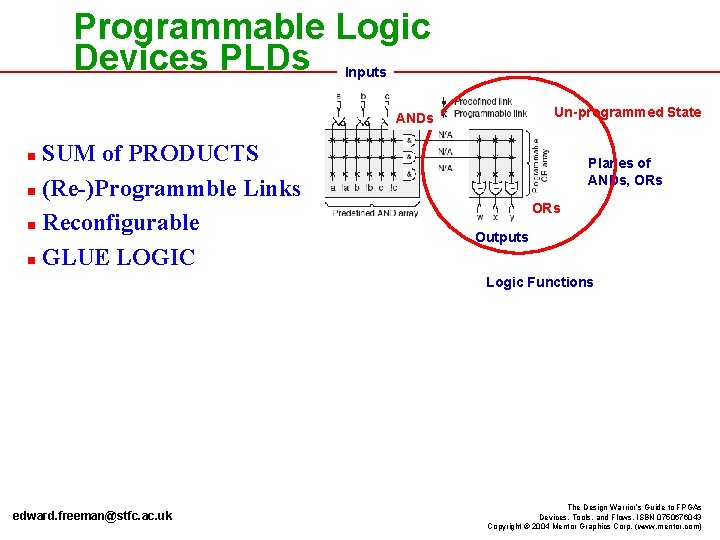

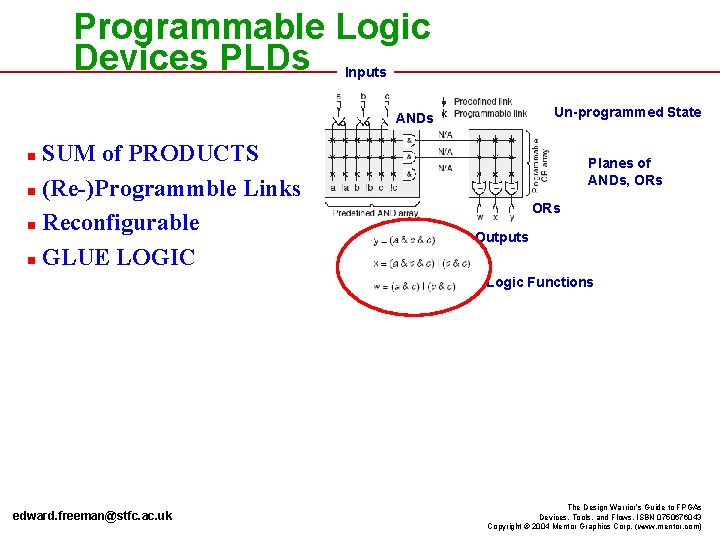

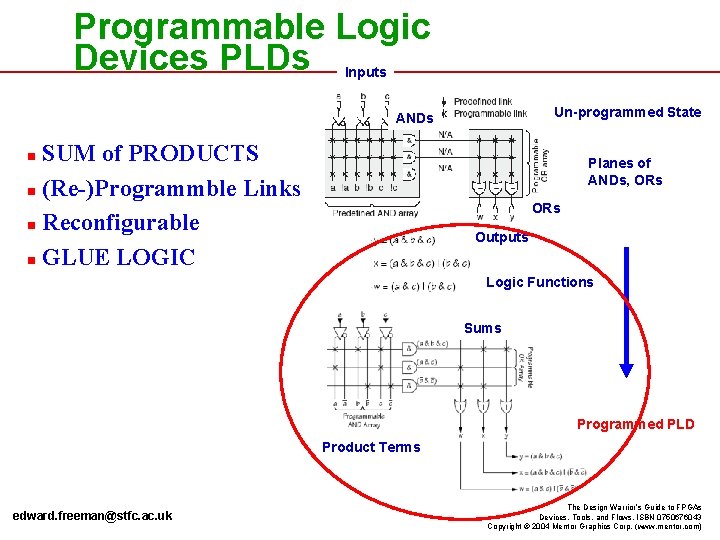

Programmable Logic Devices PLDs Inputs Un-programmed State ANDs SUM of PRODUCTS n (Re-)Programmble Links n Reconfigurable n GLUE LOGIC n Planes of ANDs, ORs Outputs Logic Functions edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Programmable Logic Devices PLDs Inputs Un-programmed State ANDs SUM of PRODUCTS n (Re-)Programmble Links n Reconfigurable n GLUE LOGIC n Planes of ANDs, ORs Outputs Logic Functions edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Programmable Logic Devices PLDs Inputs Un-programmed State ANDs SUM of PRODUCTS n (Re-)Programmble Links n Reconfigurable n GLUE LOGIC n Planes of ANDs, ORs Outputs Logic Functions edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Programmable Logic Devices PLDs Inputs Un-programmed State ANDs SUM of PRODUCTS n (Re-)Programmble Links n Reconfigurable n GLUE LOGIC n Planes of ANDs, ORs Outputs Logic Functions Sums Programmed PLD Product Terms edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

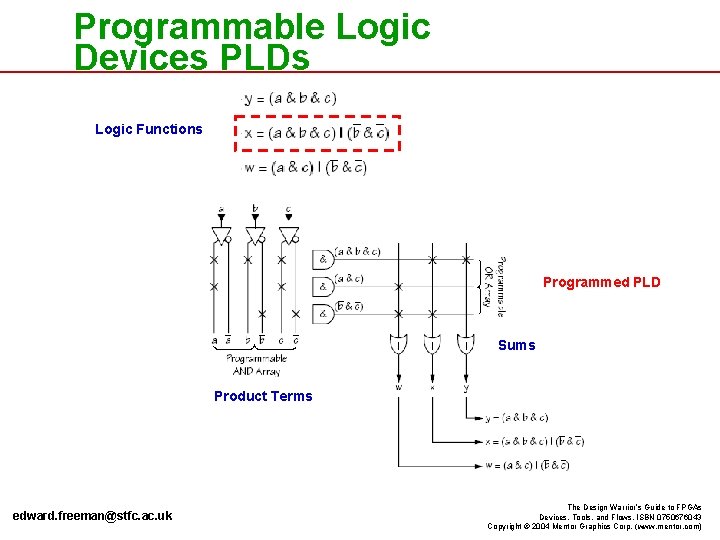

Programmable Logic Devices PLDs Logic Functions Programmed PLD Sums Product Terms edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

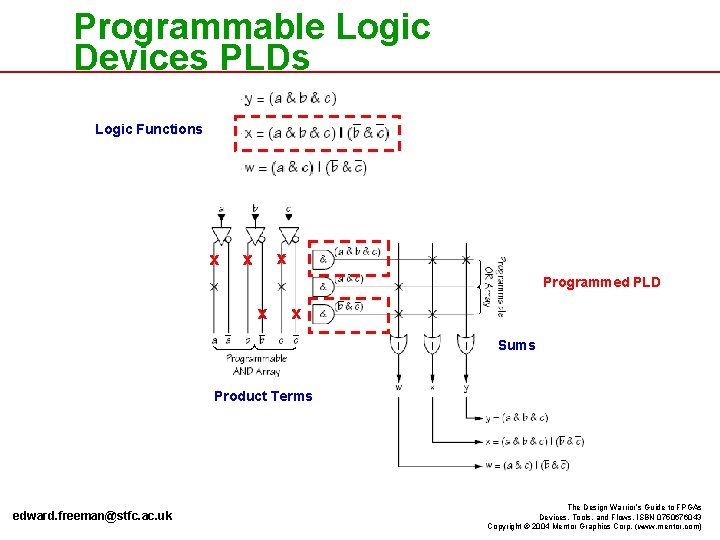

Programmable Logic Devices PLDs Logic Functions x x x Programmed PLD x x Sums Product Terms edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

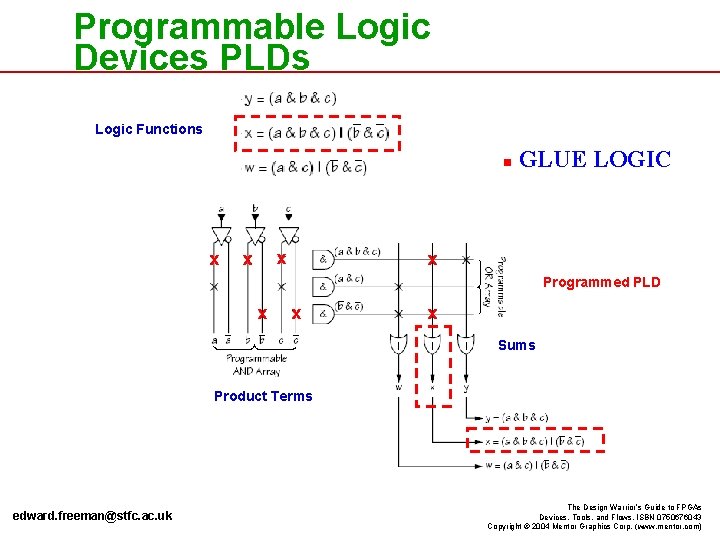

Programmable Logic Devices PLDs Logic Functions n x x x GLUE LOGIC x Programmed PLD x x x Sums Product Terms edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

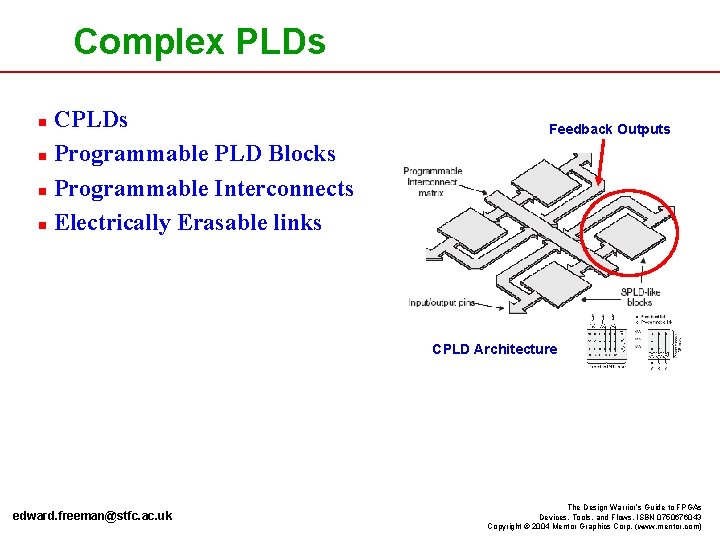

Complex PLDs CPLDs n Programmable PLD Blocks n Programmable Interconnects n Electrically Erasable links n Feedback Outputs CPLD Architecture edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

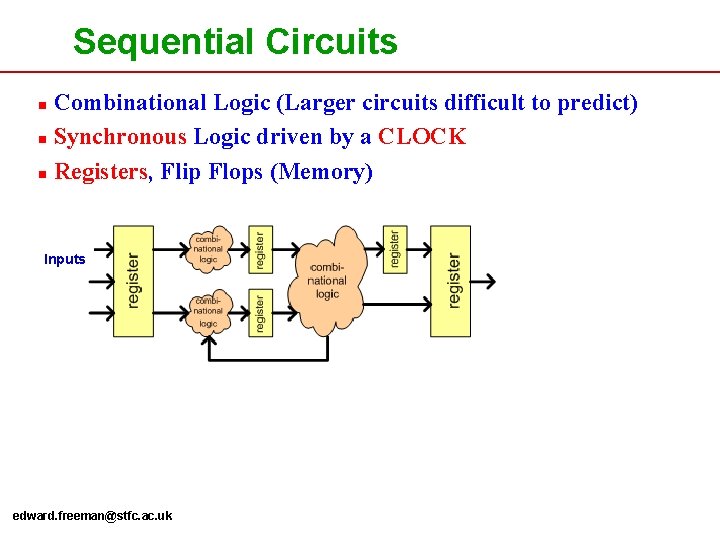

Sequential Circuits Combinational Logic (Larger circuits difficult to predict) n Synchronous Logic driven by a CLOCK n Registers, Flip Flops (Memory) n Inputs edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

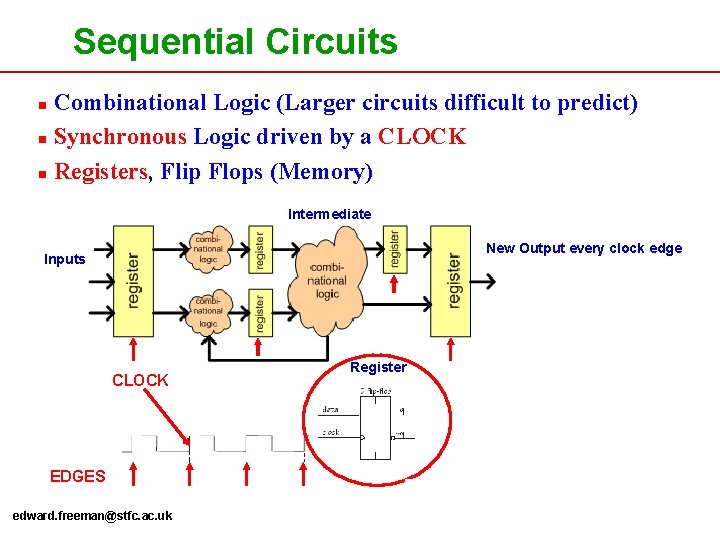

Sequential Circuits Combinational Logic (Larger circuits difficult to predict) n Synchronous Logic driven by a CLOCK n Registers, Flip Flops (Memory) n Intermediate New Output every clock edge Inputs CLOCK Register EDGES edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

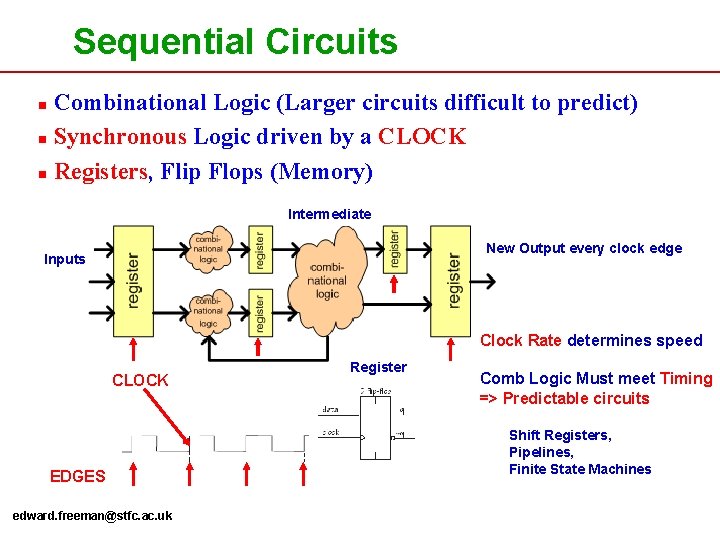

Sequential Circuits Combinational Logic (Larger circuits difficult to predict) n Synchronous Logic driven by a CLOCK n Registers, Flip Flops (Memory) n Intermediate New Output every clock edge Inputs Clock Rate determines speed CLOCK EDGES edward. freeman@stfc. ac. uk Register Comb Logic Must meet Timing => Predictable circuits Shift Registers, Pipelines, Finite State Machines … The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

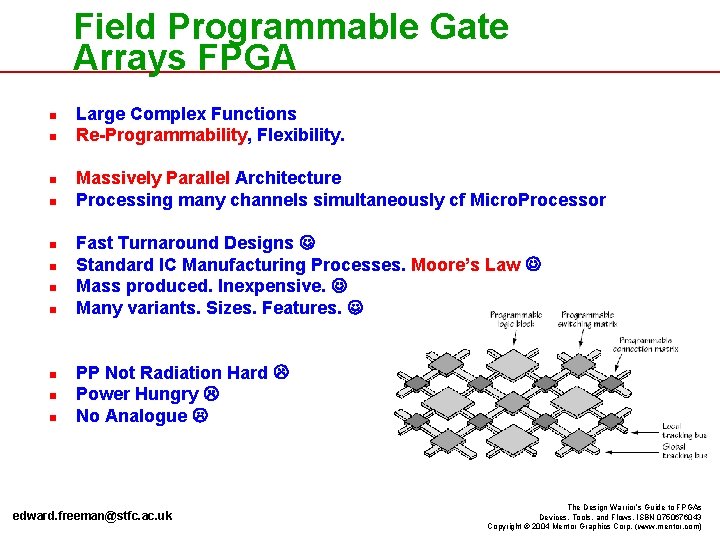

Field Programmable Gate Arrays FPGA n Field Programmable Gate Array u u u ‘Simple’ Programmable Logic Blocks Massive Fabric of Programmable Interconnects Standard CMOS Integrated Circuit fabrication process as for memory chips (Moore’s Law) edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

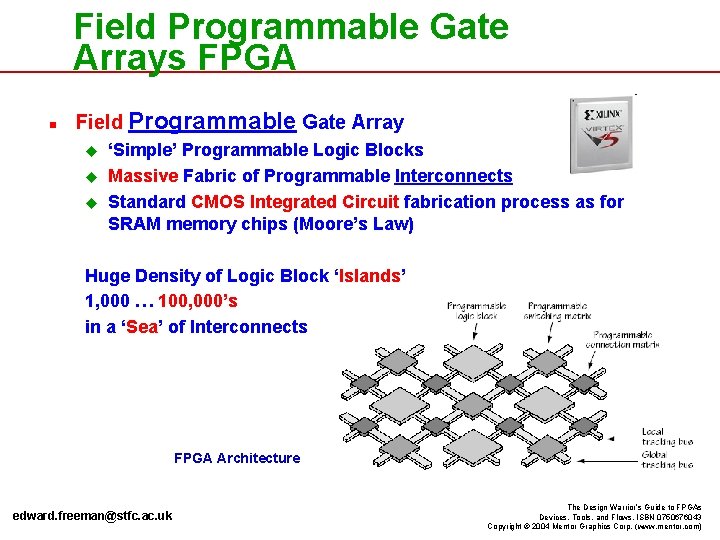

Field Programmable Gate Arrays FPGA n Field Programmable Gate Array u u u ‘Simple’ Programmable Logic Blocks Massive Fabric of Programmable Interconnects Standard CMOS Integrated Circuit fabrication process as for SRAM memory chips (Moore’s Law) Huge Density of Logic Block ‘Islands’ 1, 000 … 100, 000’s in a ‘Sea’ of Interconnects FPGA Architecture edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

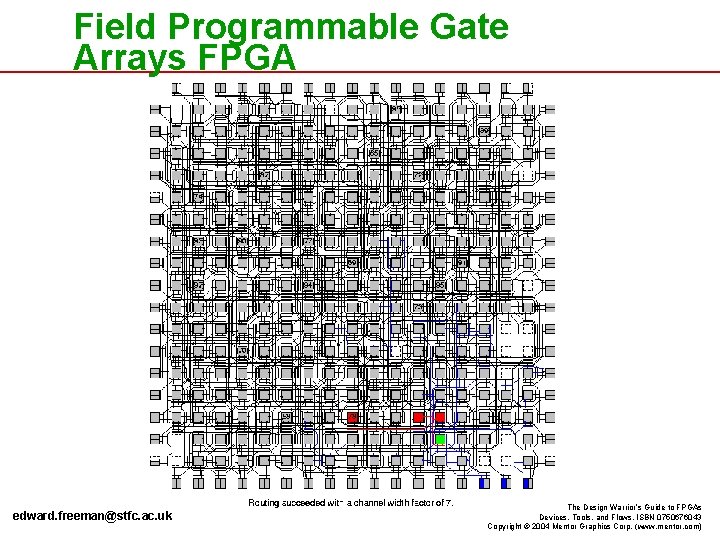

Field Programmable Gate Arrays FPGA edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

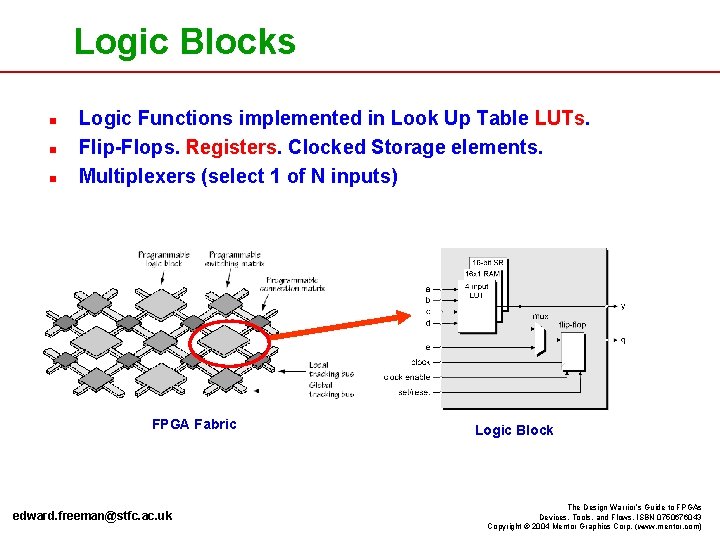

Logic Blocks n n n Logic Functions implemented in Look Up Table LUTs. Flip-Flops. Registers. Clocked Storage elements. Multiplexers (select 1 of N inputs) FPGA Fabric edward. freeman@stfc. ac. uk Logic Block The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

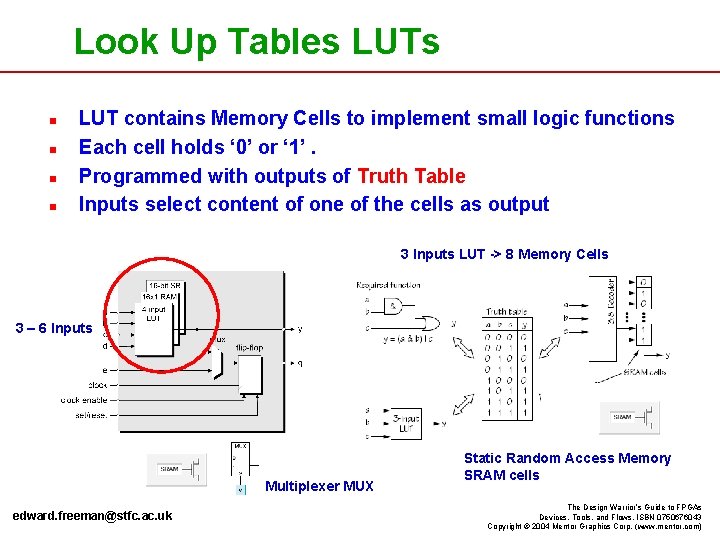

Look Up Tables LUTs n n LUT contains Memory Cells to implement small logic functions Each cell holds ‘ 0’ or ‘ 1’. Programmed with outputs of Truth Table Inputs select content of one of the cells as output 3 Inputs LUT -> 8 Memory Cells 3 – 6 Inputs Multiplexer MUX edward. freeman@stfc. ac. uk Static Random Access Memory SRAM cells The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

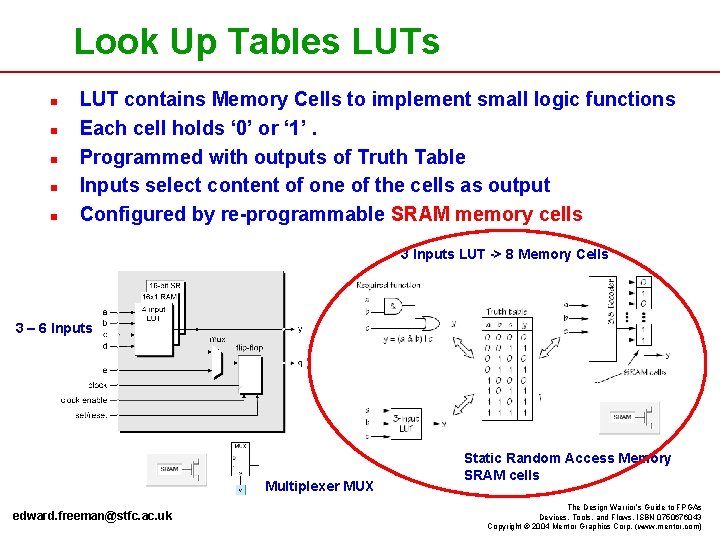

Look Up Tables LUTs n n n LUT contains Memory Cells to implement small logic functions Each cell holds ‘ 0’ or ‘ 1’. Programmed with outputs of Truth Table Inputs select content of one of the cells as output Configured by re-programmable SRAM memory cells 3 Inputs LUT -> 8 Memory Cells 3 – 6 Inputs Multiplexer MUX edward. freeman@stfc. ac. uk Static Random Access Memory SRAM cells The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

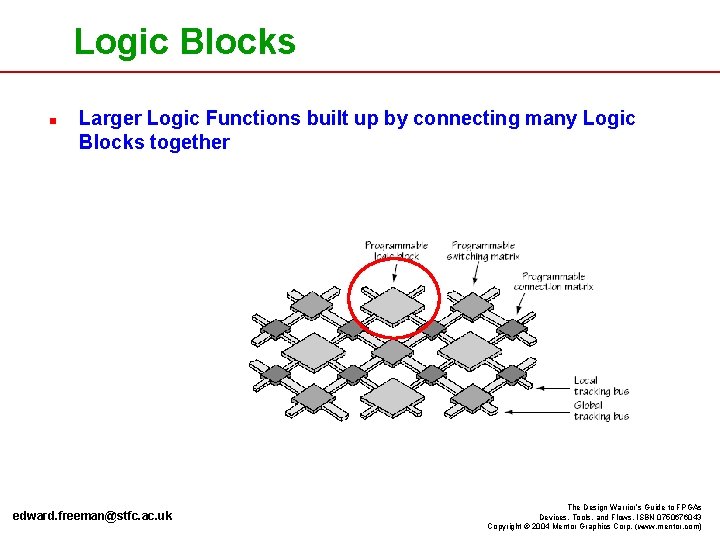

Logic Blocks n Larger Logic Functions built up by connecting many Logic Blocks together edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

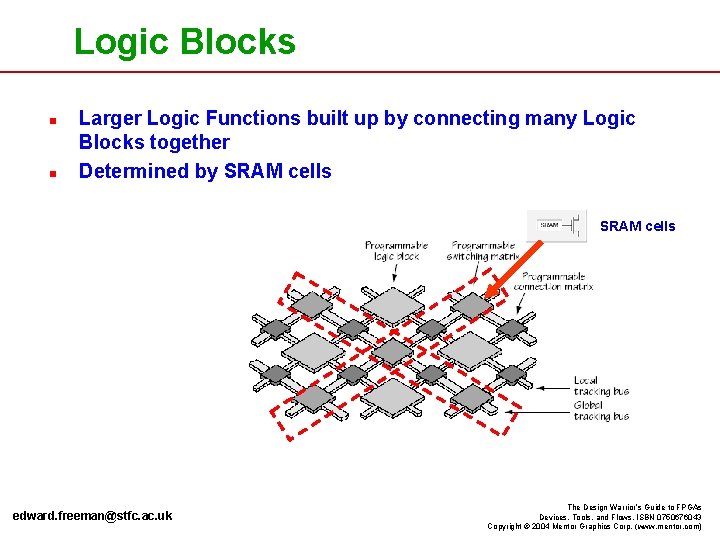

Logic Blocks n n Larger Logic Functions built up by connecting many Logic Blocks together Determined by SRAM cells edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

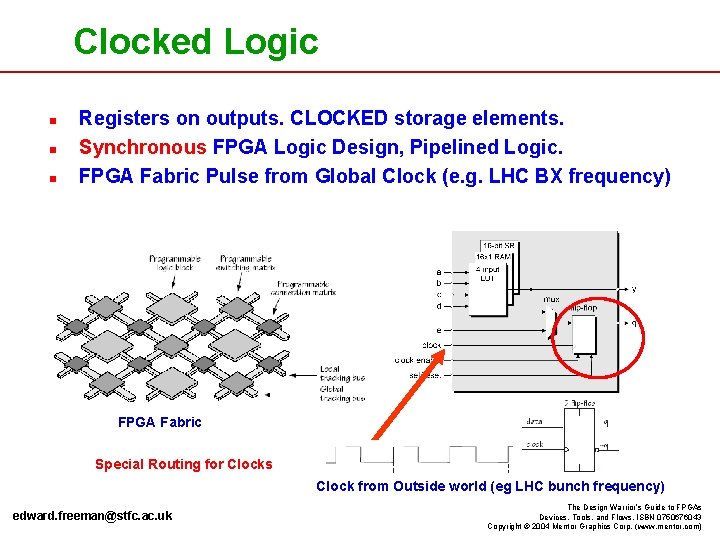

Clocked Logic n n n Registers on outputs. CLOCKED storage elements. Synchronous FPGA Logic Design, Pipelined Logic. FPGA Fabric Pulse from Global Clock (e. g. LHC BX frequency) FPGA Fabric Special Routing for Clocks Clock from Outside world (eg LHC bunch frequency) edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

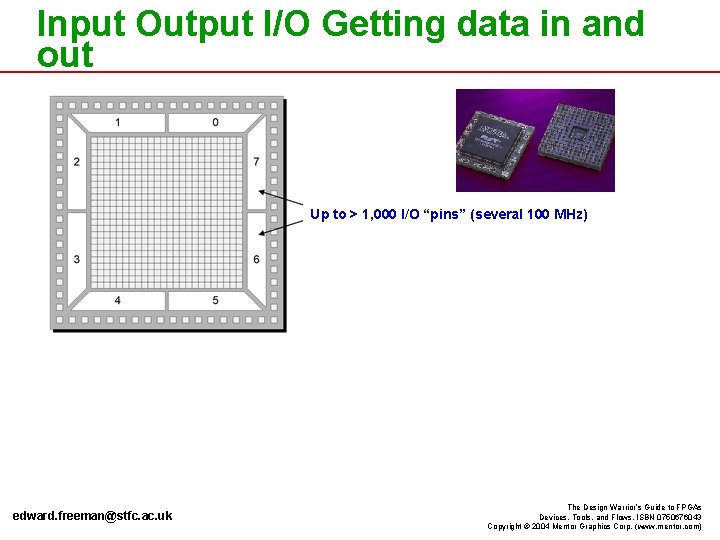

Input Output I/O Getting data in and out Up to > 1, 000 I/O “pins” (several 100 MHz) edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

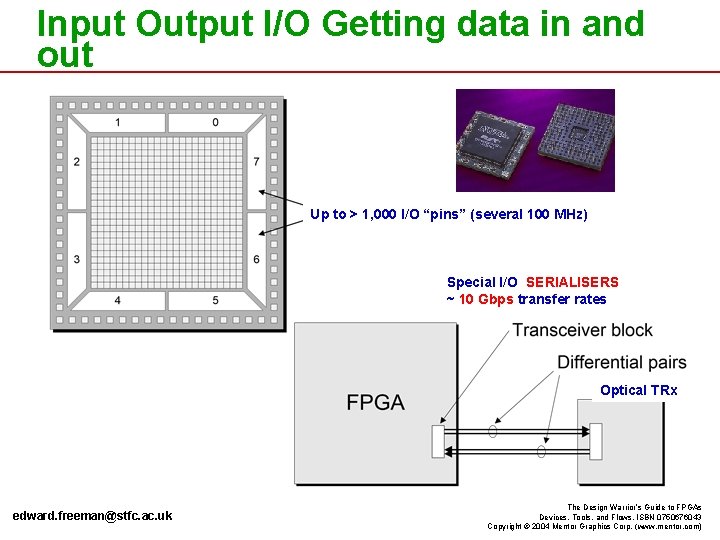

Input Output I/O Getting data in and out Up to > 1, 000 I/O “pins” (several 100 MHz) Special I/O SERIALISERS ~ 10 Gbps transfer rates Optical TRx edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

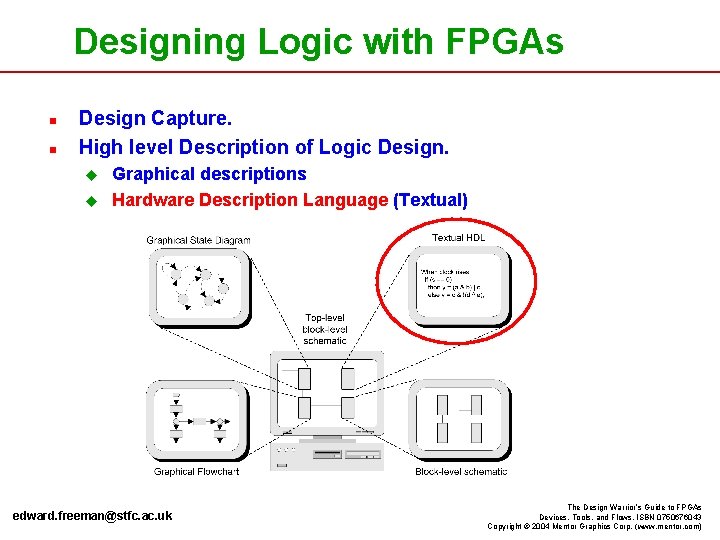

Designing Logic with FPGAs n n Design Capture. High level Description of Logic Design. u u Graphical descriptions Hardware Description Language (Textual) edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

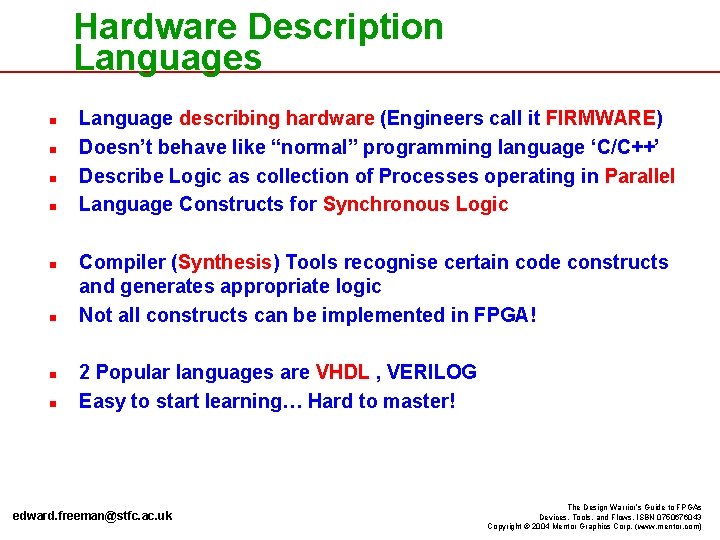

Hardware Description Languages n n n n Language describing hardware (Engineers call it FIRMWARE) Doesn’t behave like “normal” programming language ‘C/C++’ Describe Logic as collection of Processes operating in Parallel Language Constructs for Synchronous Logic Compiler (Synthesis) Tools recognise certain code constructs and generates appropriate logic Not all constructs can be implemented in FPGA! 2 Popular languages are VHDL , VERILOG Easy to start learning… Hard to master! edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

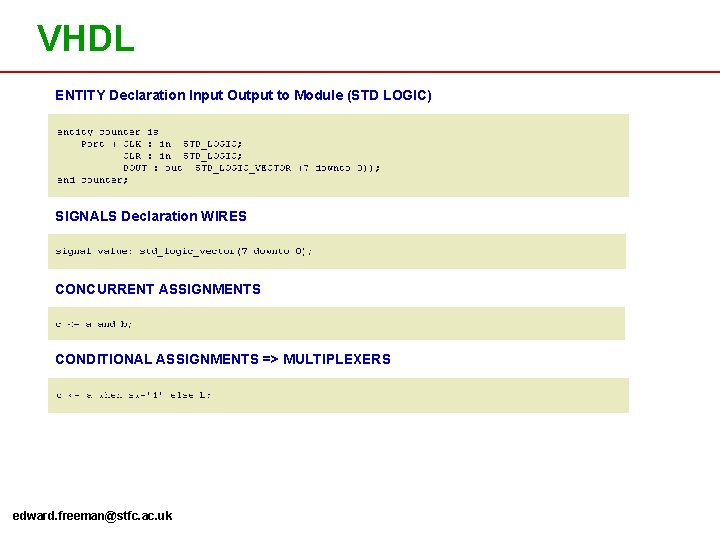

VHDL ENTITY Declaration Input Output to Module (STD LOGIC) SIGNALS Declaration WIRES CONCURRENT ASSIGNMENTS CONDITIONAL ASSIGNMENTS => MULTIPLEXERS edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

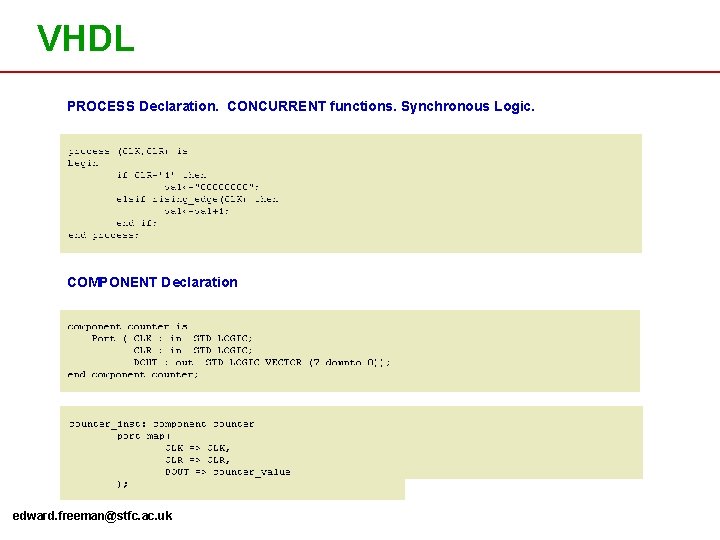

VHDL PROCESS Declaration. CONCURRENT functions. Synchronous Logic. COMPONENT Declaration edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

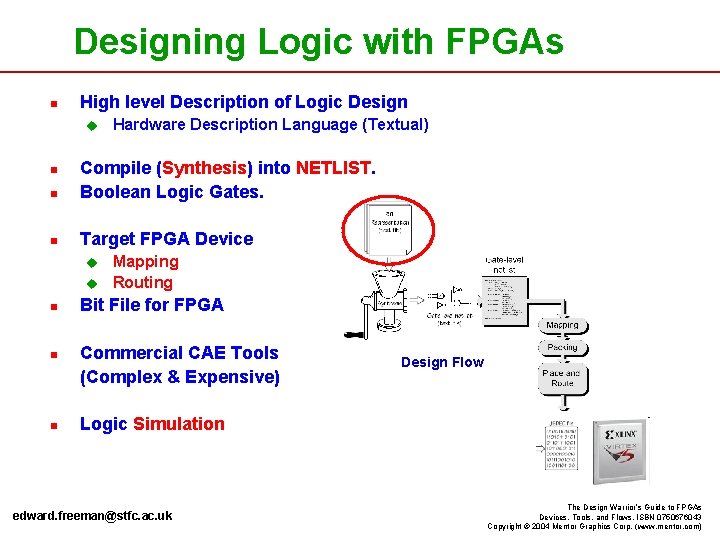

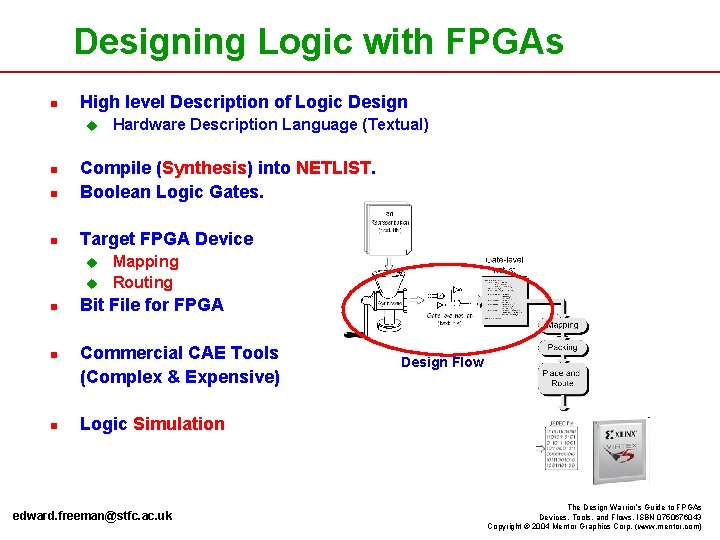

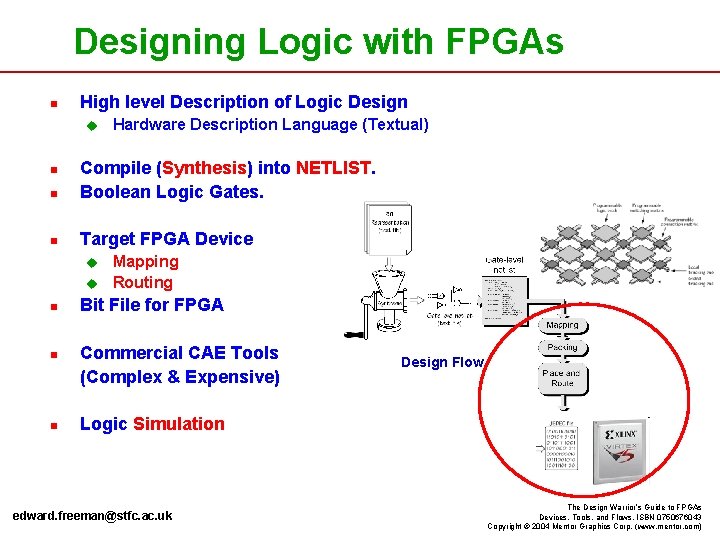

Designing Logic with FPGAs n High level Description of Logic Design u Hardware Description Language (Textual) n Compile (Synthesis) into NETLIST. Boolean Logic Gates. n Target FPGA Device n u u n n n Mapping Routing Bit File for FPGA Commercial CAE Tools (Complex & Expensive) Design Flow Logic Simulation edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Designing Logic with FPGAs n High level Description of Logic Design u Hardware Description Language (Textual) n Compile (Synthesis) into NETLIST. Boolean Logic Gates. n Target FPGA Device n u u n n n Mapping Routing Bit File for FPGA Commercial CAE Tools (Complex & Expensive) Design Flow Logic Simulation edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Designing Logic with FPGAs n High level Description of Logic Design u Hardware Description Language (Textual) n Compile (Synthesis) into NETLIST. Boolean Logic Gates. n Target FPGA Device n u u n n n Mapping Routing Bit File for FPGA Commercial CAE Tools (Complex & Expensive) Design Flow Logic Simulation edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

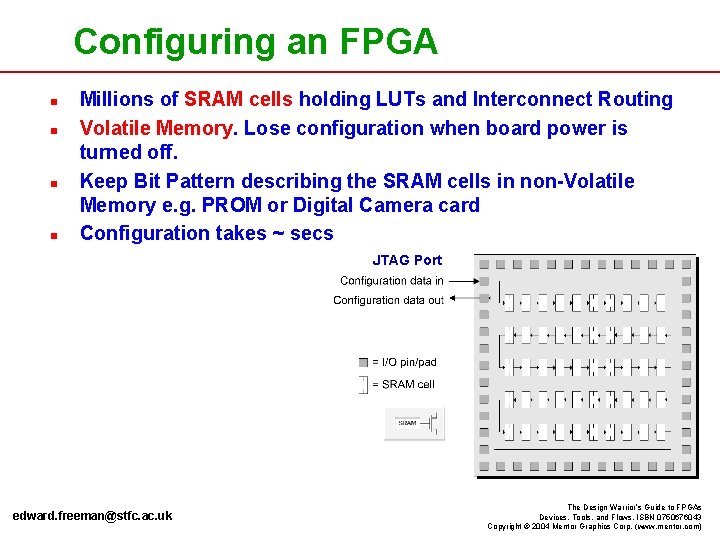

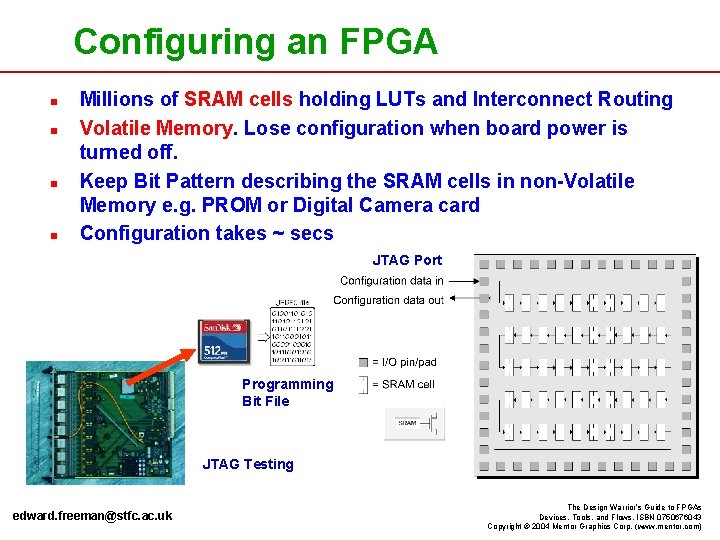

Configuring an FPGA n n Millions of SRAM cells holding LUTs and Interconnect Routing Volatile Memory. Lose configuration when board power is turned off. Keep Bit Pattern describing the SRAM cells in non-Volatile Memory e. g. PROM or Digital Camera card Configuration takes ~ secs JTAG Port edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Configuring an FPGA n n Millions of SRAM cells holding LUTs and Interconnect Routing Volatile Memory. Lose configuration when board power is turned off. Keep Bit Pattern describing the SRAM cells in non-Volatile Memory e. g. PROM or Digital Camera card Configuration takes ~ secs JTAG Port Programming Bit File JTAG Testing edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Field Programmable Gate Arrays FPGA n n n Large Complex Functions Re-Programmability, Flexibility. Massively Parallel Architecture Processing many channels simultaneously cf Micro. Processor Fast Turnaround Designs Standard IC Manufacturing Processes. Moore’s Law Mass produced. Inexpensive. Many variants. Sizes. Features. PP Not Radiation Hard Power Hungry No Analogue edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

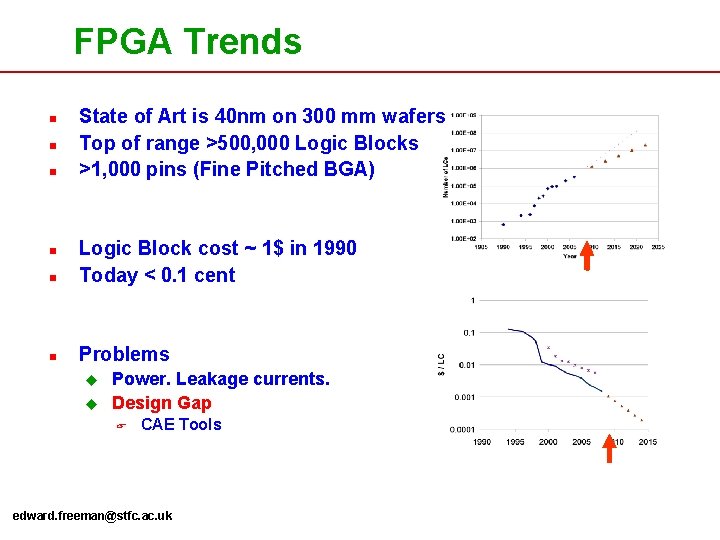

FPGA Trends n n n State of Art is 40 nm on 300 mm wafers Top of range >500, 000 Logic Blocks >1, 000 pins (Fine Pitched BGA) n Logic Block cost ~ 1$ in 1990 Today < 0. 1 cent n Problems n u u Power. Leakage currents. Design Gap F CAE Tools edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Summary n Programmable Logic Devices u u n FPGA Field Programmable Gate Arrays u n Basics Evolution Architecture Design Flow u u Hardware Description Languages Design Tools Importance for Particle Physics Experiments edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

References n The Design Warrior’s Guide to FPGAs u n VHDL for Logic Synthesis u n Andrew Rushden, Wiley FPGA manufacturer web sites u u n Clive Maxfield, Newnes Elsevier www. xilinx. com www. altera. com FPGA Online u u u www. pldesignline. com www. fpgajournal. com www. doulos. com edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

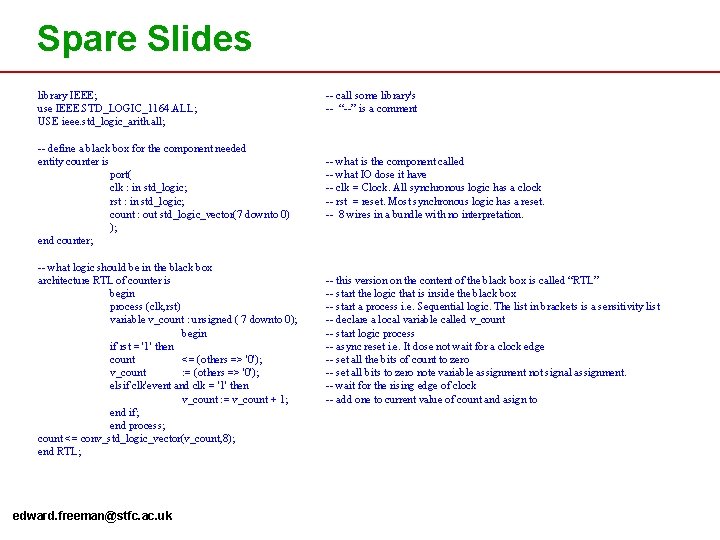

Spare Slides library IEEE; use IEEE. STD_LOGIC_1164. ALL; USE ieee. std_logic_arith. all; -- define a black box for the component needed entity counter is port( clk : in std_logic; rst : in std_logic; count : out std_logic_vector(7 downto 0) ); end counter; -- what logic should be in the black box architecture RTL of counter is begin process (clk, rst) variable v_count : unsigned ( 7 downto 0); begin if rst = '1' then count <= (others => '0'); v_count : = (others => '0'); elsif clk'event and clk = '1' then v_count : = v_count + 1; end if; end process; count <= conv_std_logic_vector(v_count, 8); end RTL; edward. freeman@stfc. ac. uk -- call some library's -- “--” is a comment -- what is the component called -- what IO dose it have -- clk = Clock. All synchronous logic has a clock -- rst = reset. Most synchronous logic has a reset. -- 8 wires in a bundle with no interpretation. -- this version on the content of the black box is called “RTL” -- start the logic that is inside the black box -- start a process i. e. Sequential logic. The list in brackets is a sensitivity list -- declare a local variable called v_count -- start logic process -- async reset i. e. It dose not wait for a clock edge -- set all the bits of count to zero -- set all bits to zero note variable assignment not signal assignment. -- wait for the rising edge of clock -- add one to current value of count and asign to The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

- Slides: 49