Introduction to Programmable Logic Devices Aleksandra Kovacevic ksandrasezampro

Introduction to Programmable Logic Devices Aleksandra Kovacevic ksandra@sezampro. yu Veljko Milutinovic vm@etf. bg. ac. yu 0/13

Introduction § Comparison of Standard Logic Circuits and Programmable Logic Circuits § Evolution and Overview of PLC: § PROM, PLA, PAL § CPLD § FPGA 1/13

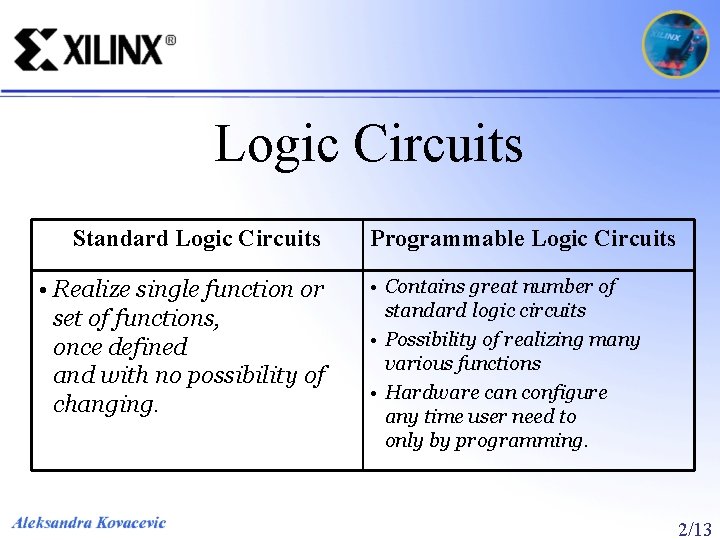

Logic Circuits Standard Logic Circuits • Realize single function or set of functions, once defined and with no possibility of changing. Programmable Logic Circuits • Contains great number of standard logic circuits • Possibility of realizing many various functions • Hardware can configure any time user need to only by programming. 2/13

Standard Logic Circuits • Appropriate for many applications because of possibility of realization in mass production for relative low cost. • Standard logic circuits are sometimes the best choice in high-performance devices. • Disadvantage: Not permitting design updates (function changes) with no hardware replacement necessary. 3/13

Field- Programmable Logic Devices • Component function is defined by users program. • Logic Cells Fields are interconnected by programming. • Advantages: - Flexible design that changes by reprogramming, ease of design changes - Reduce prototype-product time - Large scale integration (over 100 000 gates) - Reliability increased, low financial risk - Smaller device, low start-up cost 4/13

FPLDs Representatives • PLA - Programmable Logic Arrays • PAL - Programmable Array Logic Programmable logic device PLD • CPLD - Complex Programmable Logic Devices • FPGA - Field Programmable Gate Arrays 5/13

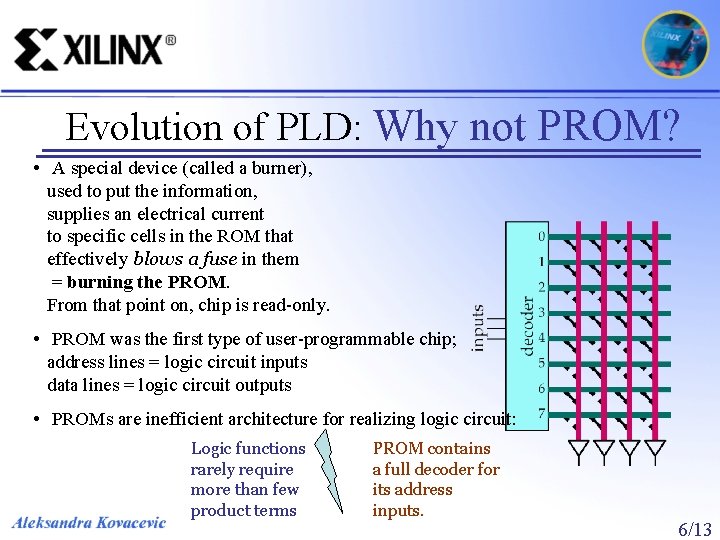

Evolution of PLD: Why not PROM? • A special device (called a burner), used to put the information, supplies an electrical current to specific cells in the ROM that effectively blows a fuse in them = burning the PROM. From that point on, chip is read-only. • PROM was the first type of user-programmable chip; address lines = logic circuit inputs data lines = logic circuit outputs • PROMs are inefficient architecture for realizing logic circuit: Logic functions rarely require more than few product terms PROM contains a full decoder for its address inputs. 6/13

Evolution of PLD: PLA • PLA was the first device developed for implementing • Consist of two levels of logic gates programmable “wired” AND -plane & OR-plane • Drawbacks: • Expensive to manufacture • Offered somewhat poor speed-performance Note: 7/13

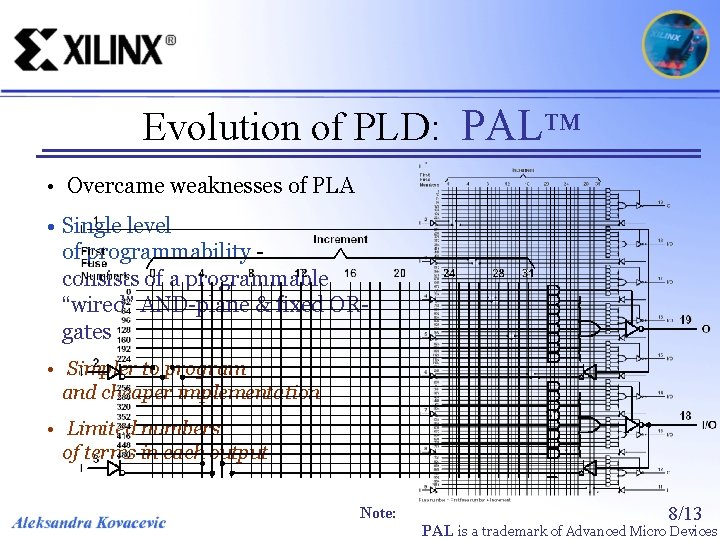

Evolution of PLD: PAL™ • Overcame weaknesses of PLA • Single level of programmability consists of a programmable “wired” AND-plane & fixed ORgates • Simpler to program and cheaper implementation • Limited numbers of terms in each output Note: 8/13 PAL is a trademark of Advanced Micro Devices

Evolution of PLD: Register PLA • Contain flip flops connected to the OR gate outputs sequential circuits can be realized • Importance: • Profound effect on digital hardware design • Basis for more sophisticated architectures 9/13

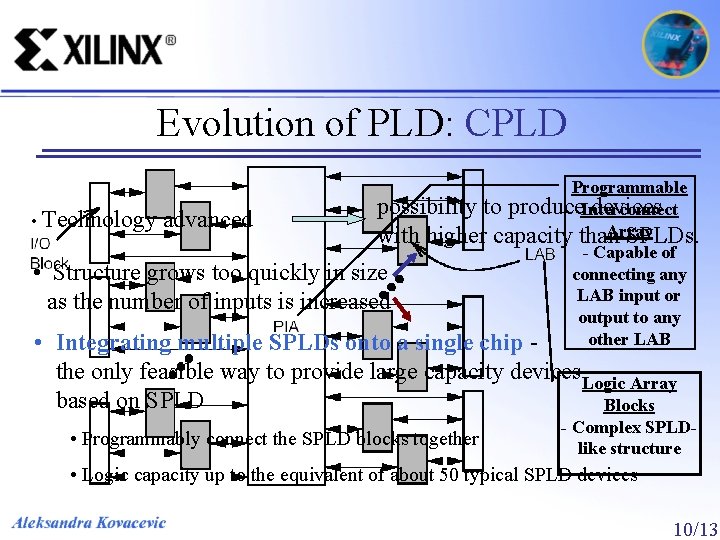

Evolution of PLD: CPLD Programmable possibility to produce. Interconnect devices • Technology advanced Array with higher capacity than SPLDs. - Capable of • Structure grows too quickly in size connecting any LAB input or as the number of inputs is increased output to any other LAB • Integrating multiple SPLDs onto a single chip - the only feasible way to provide large capacity devices. Logic Array based on SPLD Blocks • Programmably connect the SPLD blocks together - Complex SPLDlike structure • Logic capacity up to the equivalent of about 50 typical SPLD devices 10/13

. . . and finally. . . 11/13

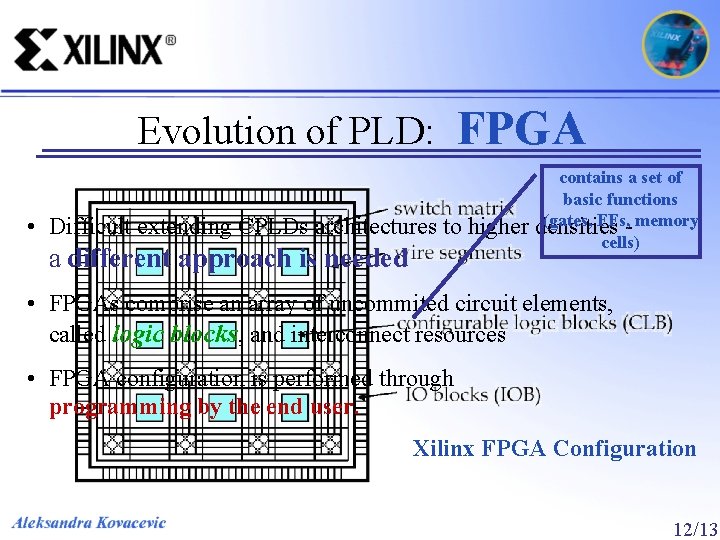

Evolution of PLD: FPGA • Difficult extending CPLDs architectures to higher a different approach is needed contains a set of basic functions (gates, FFs, - memory densities cells) • FPGAs comprise an array of uncommited circuit elements, called logic blocks, and interconnect resources • FPGA configuration is performed through programming by the end user. Xilinx FPGA Configuration 12/13

Introduction to Programmable Logic Devices Aleksandra Kovacevic ksandra@sezampro. yu Veljko Milutinovic vm@etf. bg. ac. yu 13/13

- Slides: 14