Introduction to Personal Computer Architecture Crystal Oscillator Core

- Slides: 12

Introduction to Personal Computer Architecture

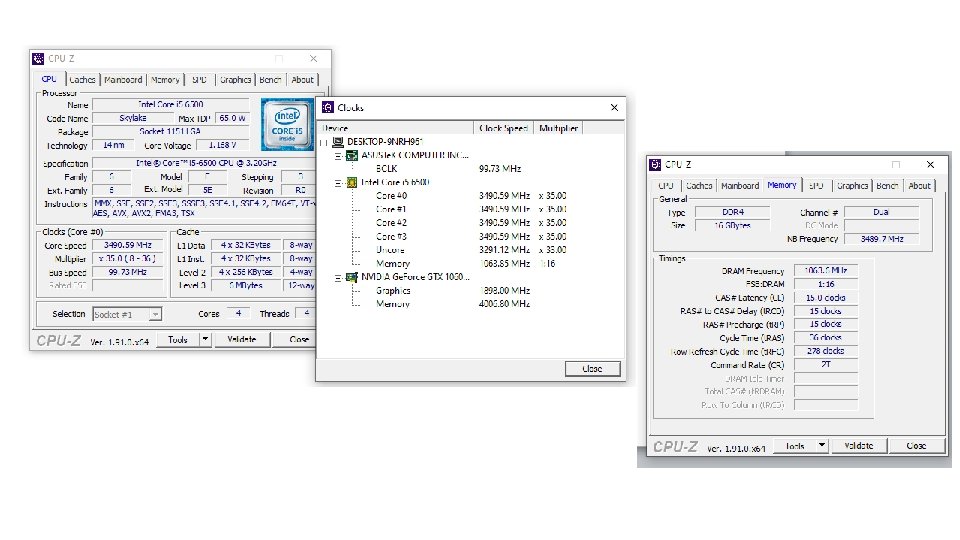

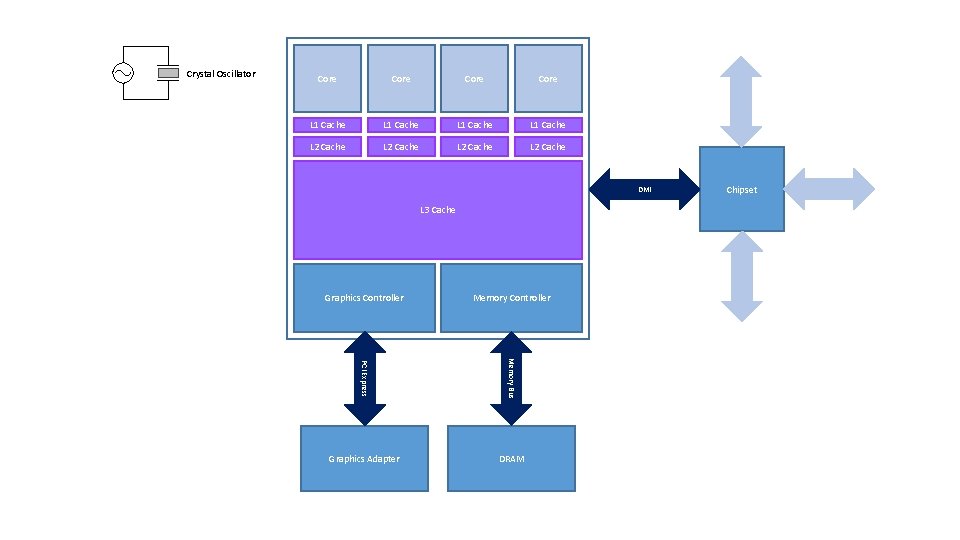

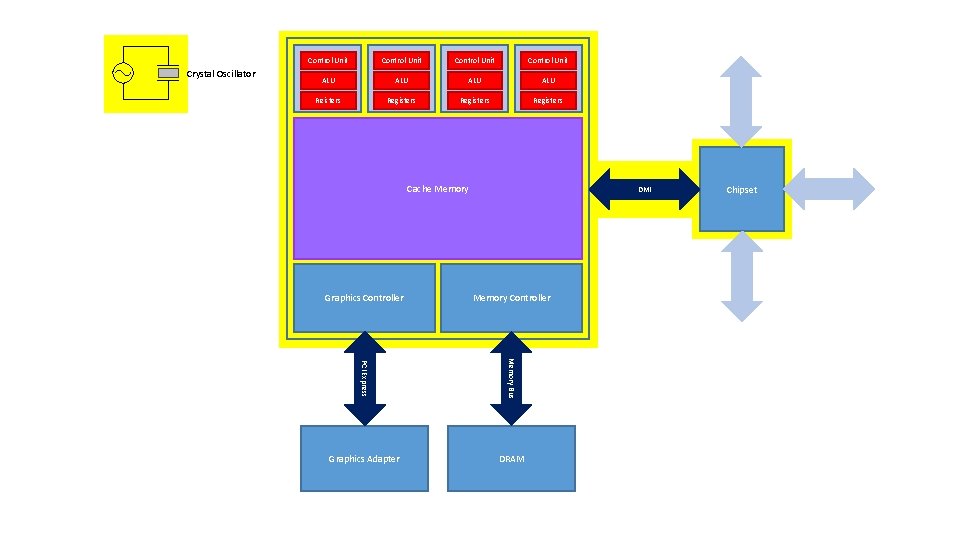

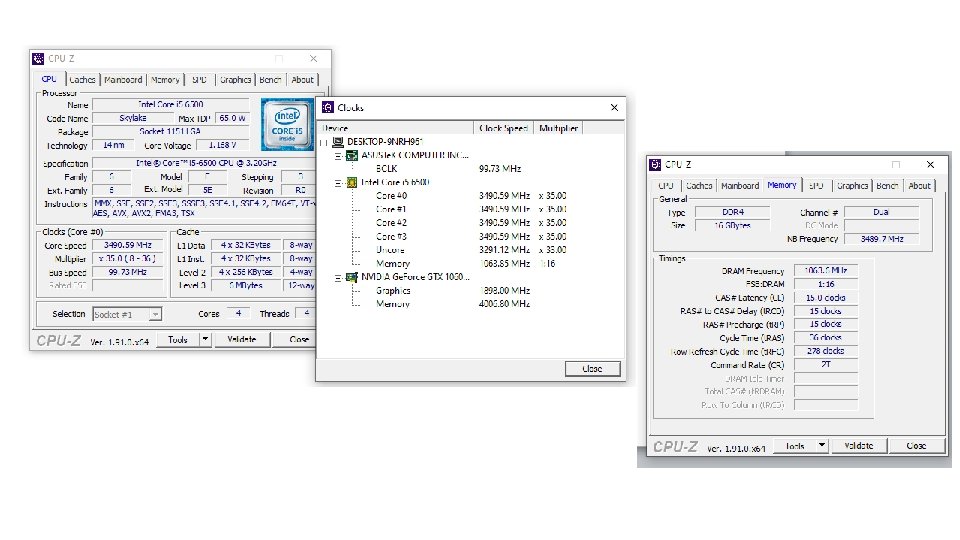

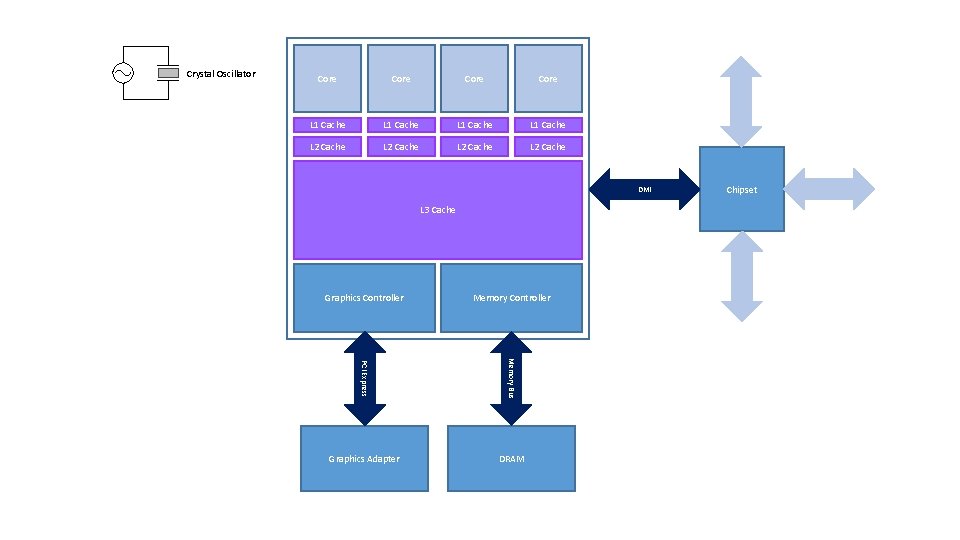

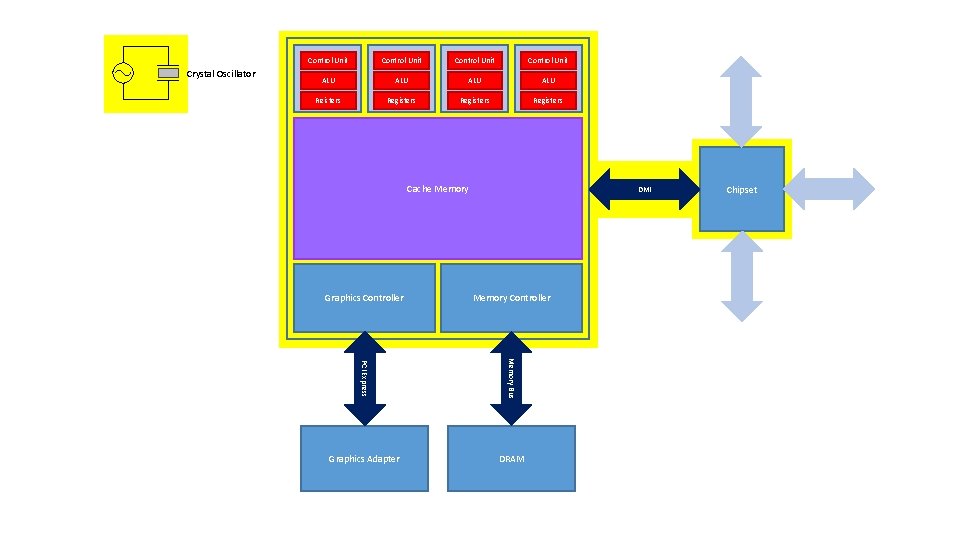

Crystal Oscillator Core L 1 Cache L 2 Cache DMI L 3 Cache Graphics Controller Memory Controller PCI Express Memory Bus Graphics Adapter DRAM Chipset

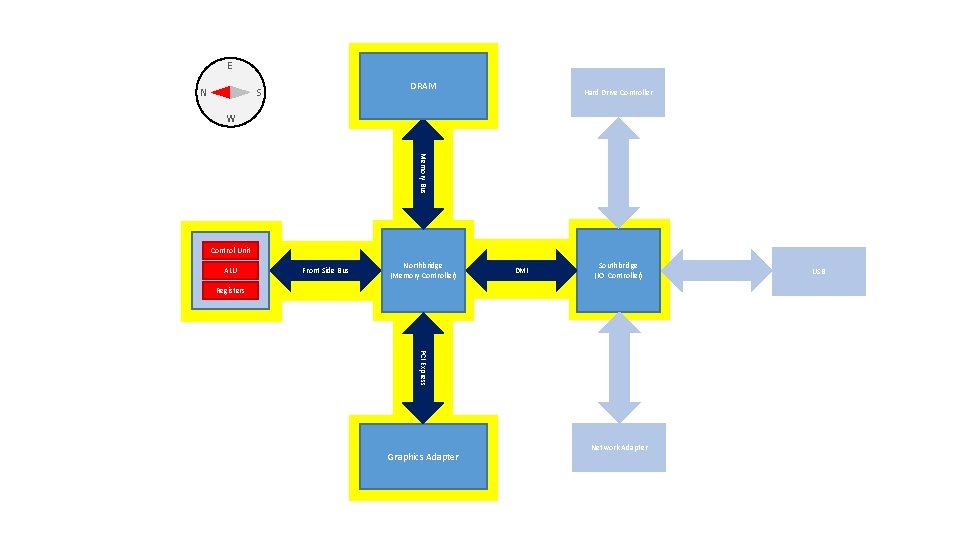

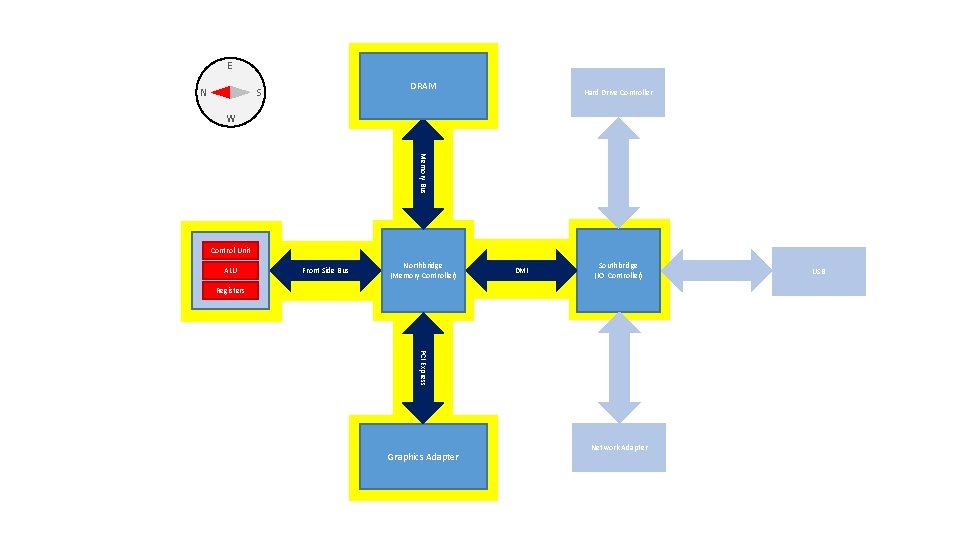

E N DRAM S Hard Drive Controller W Memory Bus Control Unit ALU CPU Front Side Bus Northbridge (Memory Controller) DMI Southbridge (IO Controller) Registers PCI Express Graphics Adapter Network Adapter USB

Crystal Oscillator Control Unit Core ALU Reisters Registers L 1 I Cache L 1 D Cache L 1 I Cache L 2 Cache Memory DMI L 3 Cache Graphics Controller L 1 D Cache Memory Controller PCI Express Memory Bus Graphics Adapter DRAM Chipset

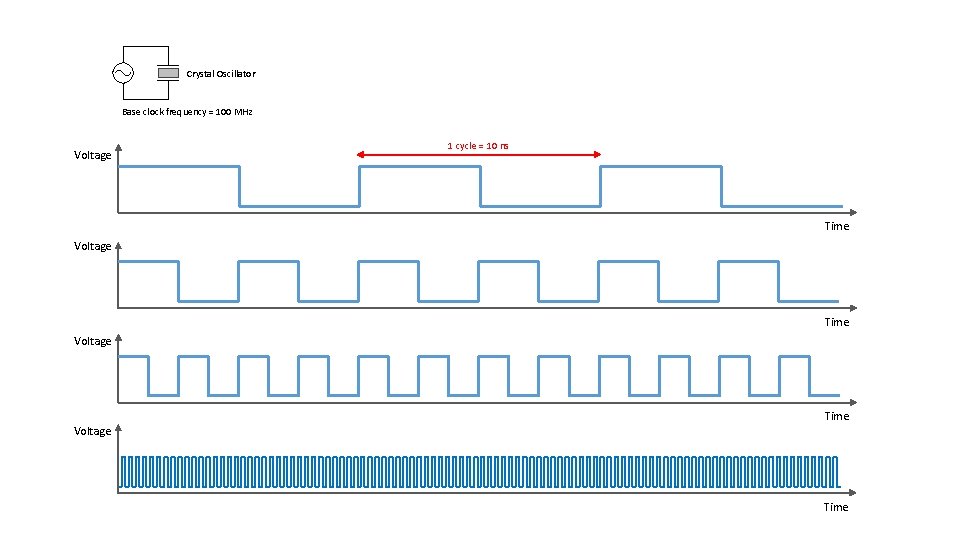

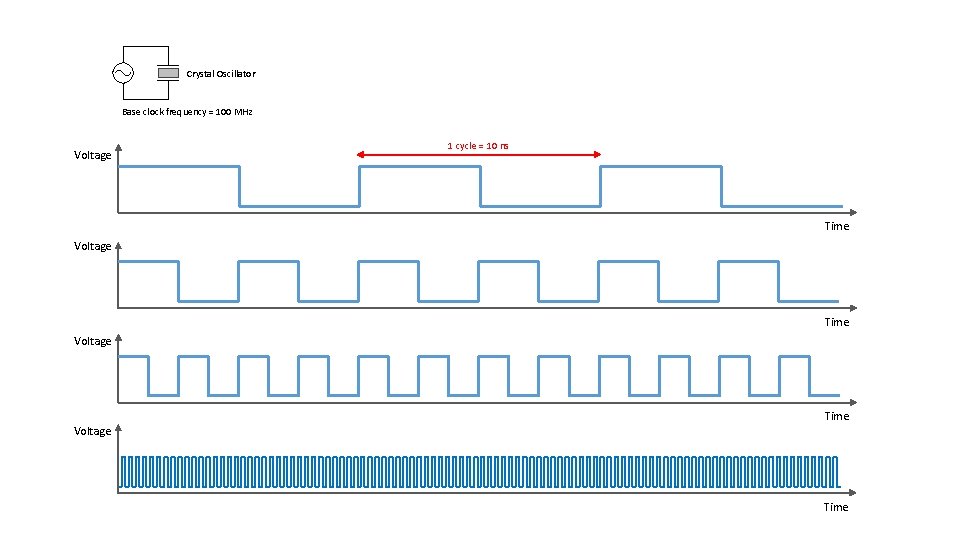

Crystal Oscillator Base clock frequency = 100 MHz Voltage 1 cycle = 10 ns Time Voltage Time

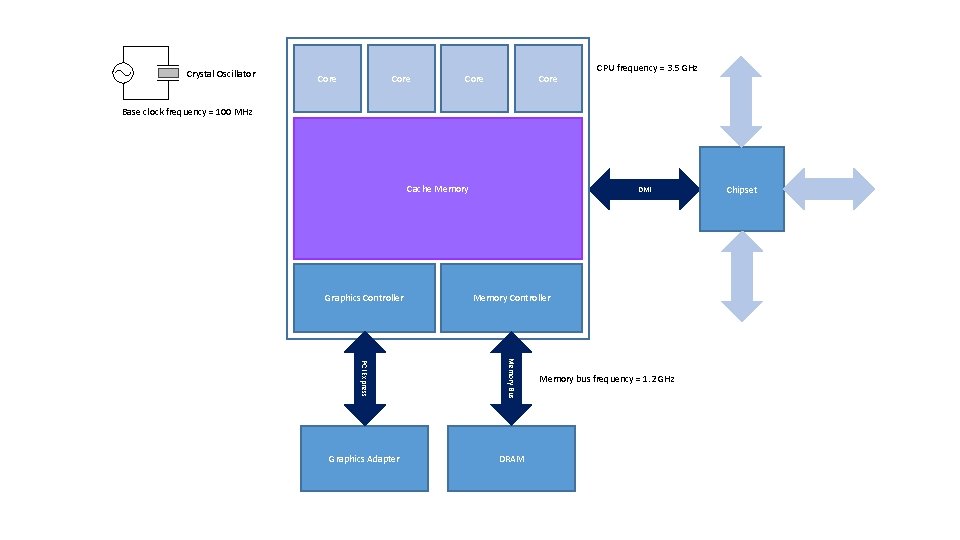

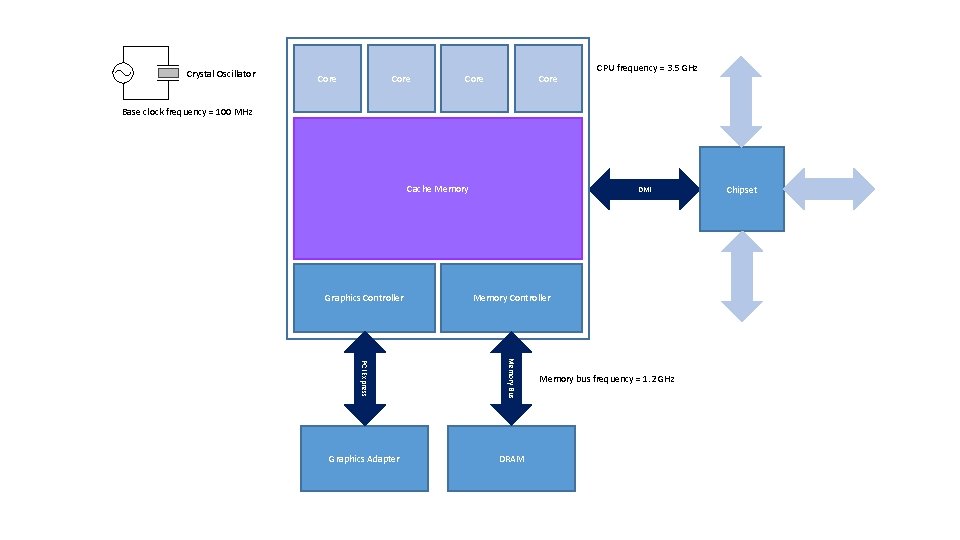

Crystal Oscillator Core Base clock frequency = 100 MHz L 1 I Cache L 1 D Cache Core L 1 I Cache L 2 Cache Core L 1 D Cache L 1 I Cache L 2 Cache CPU frequency = 3. 5 GHz L 1 D Cache L 2 Cache Memory DMI L 3 Cache Graphics Controller Memory Controller PCI Express Memory Bus Graphics Adapter DRAM Memory bus frequency = 1. 2 GHz Chipset

L 1 I Cache L 1 D Cache L 2 Cache L 1 I Cache L 1 D Cache L 1 I Cache L 2 Cache L 1 D Cache L 2 Cache L 1 I Cache L 1 D Cache L 2 Cache L 3 Cache Dynamic Random Access Memory

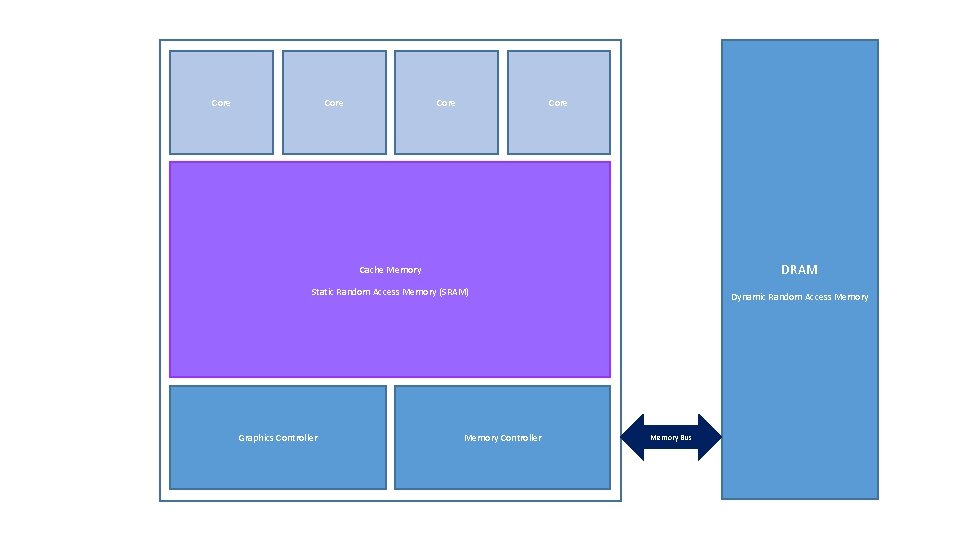

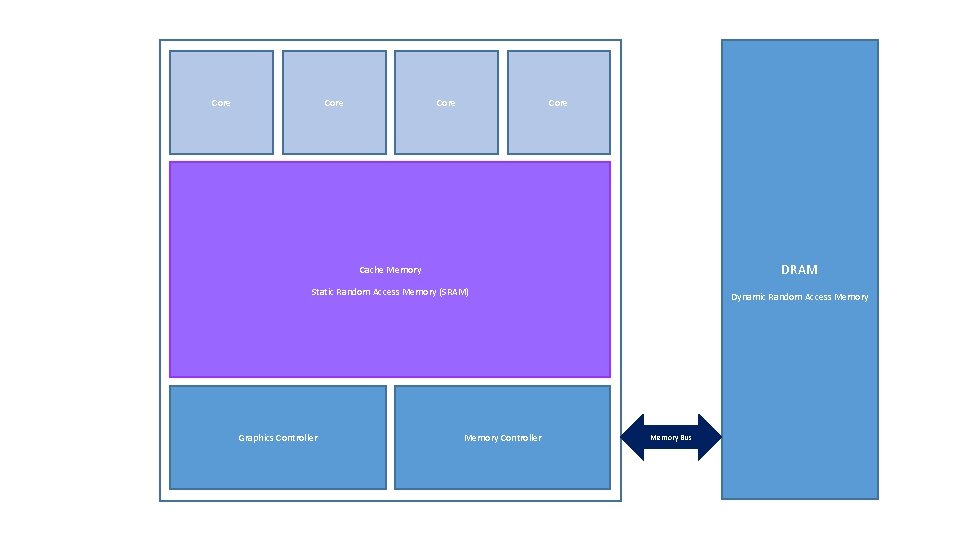

Core L 1 I Cache Core L 1 D Cache L 1 I Cache L 2 Cache L 1 D Cache L 2 Cache Memory DRAM Static Random Access Memory (SRAM) Dynamic Random Access Memory L 3 Cache Graphics Controller Memory Bus

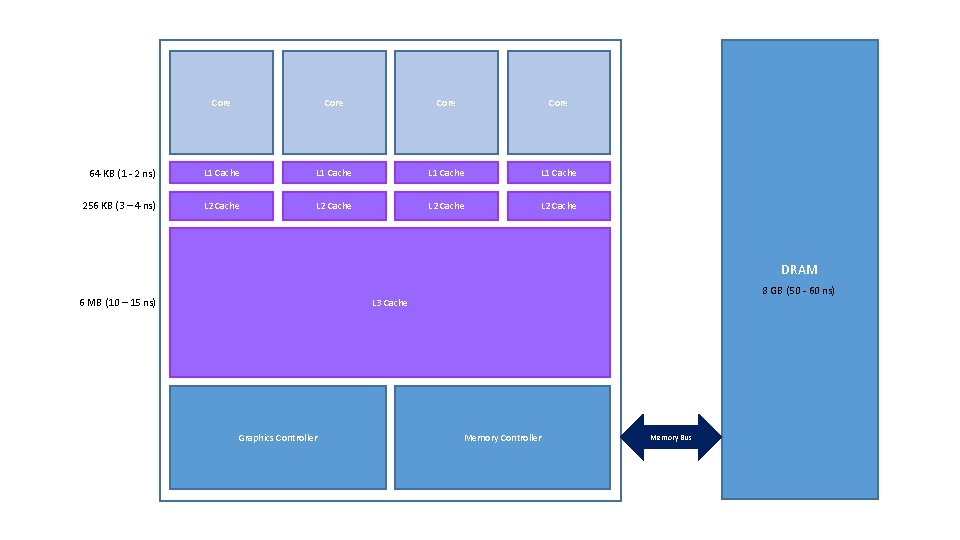

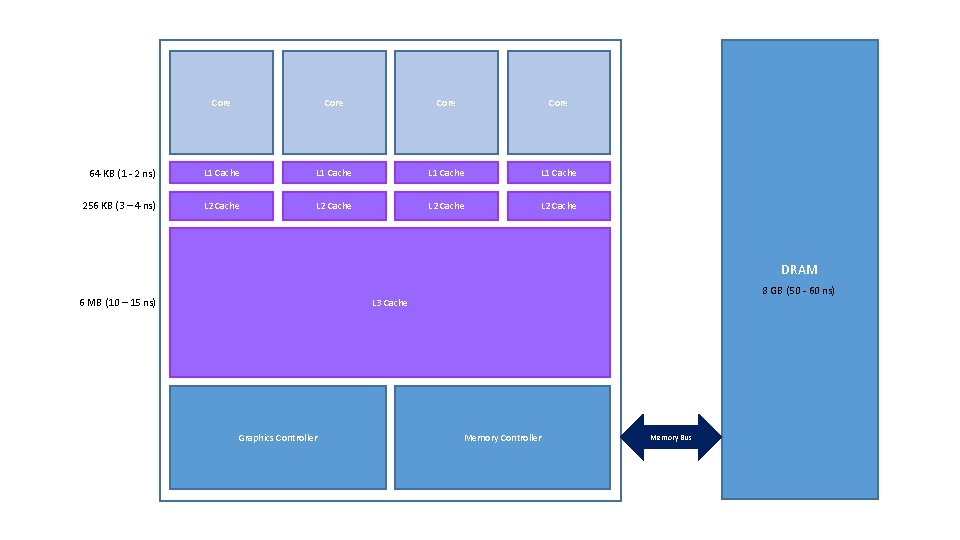

64 KB (1 - 2 ns) 256 KB (3 – 4 ns) Core L 1 ICache L 1 DCache L 1 ICache L 1 DCache L 1 ICache L 1 DCache L 2 Cache DRAM 6 MB (10 – 15 ns) 8 GB (50 - 60 ns) L 3 Cache Graphics Controller Memory Bus

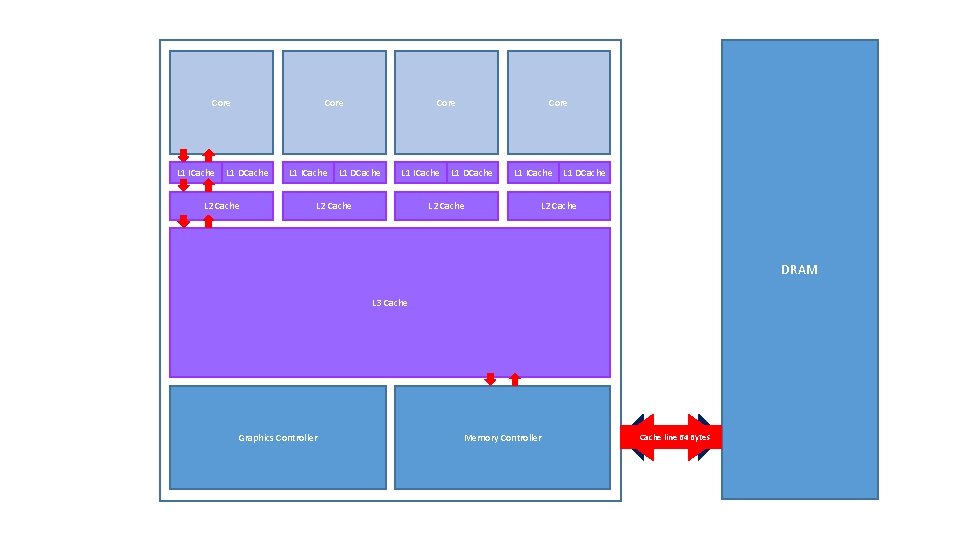

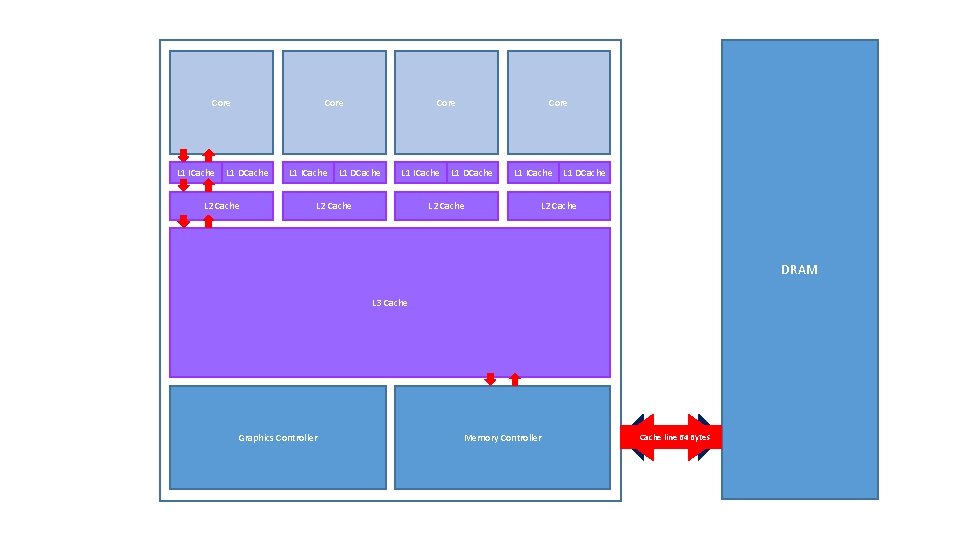

Core L 1 ICache Core L 1 DCache L 2 Cache L 1 ICache Core L 1 DCache L 1 ICache L 2 Cache Core L 1 DCache L 2 Cache L 1 ICache L 1 DCache L 2 Cache DRAM L 3 Cache Graphics Controller Memory Bus. Bytes Cache line 64

Summary • Central Processing Unit can have multiple cores • Each core has a control unit, an Arithmetic and Logic Unit, and various registers • Memory and graphics controllers are built into the CPU • Base clock frequency is provided by a crystal oscillator • Different components divide and multiply the base clock frequency as needed • CPU can adjust its clock speed dynamically • CPU cache is organised into three levels • Data move between cache levels and DRAM in cache lines of 64 bytes