Introduction to Interconnection Networks Introduction to Interconnection network

- Slides: 22

Introduction to Interconnection Networks

Introduction to Interconnection network • Digital systems(DS) are pervasive in modern society. • Digital computers - simulating physical systems, managing large databases , preparing documents and etc • Audio and video entertainment is increasingly being delivered and processed in digital form. Finally, almost all products from automobiles to home appliances are digitally controlled.

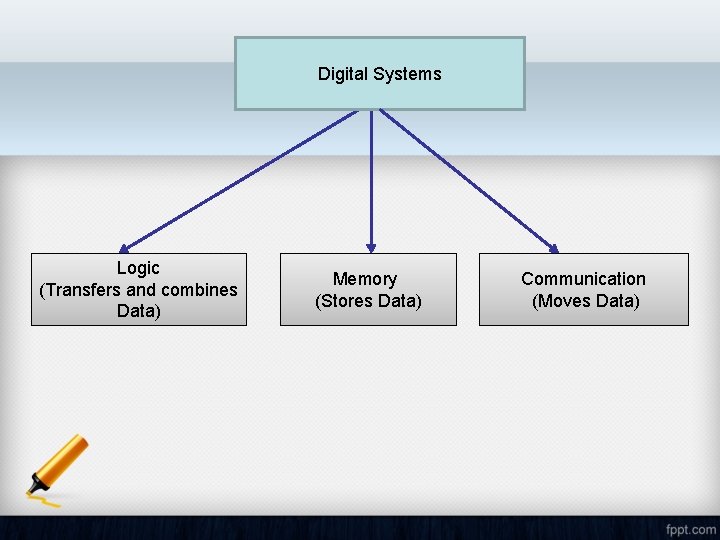

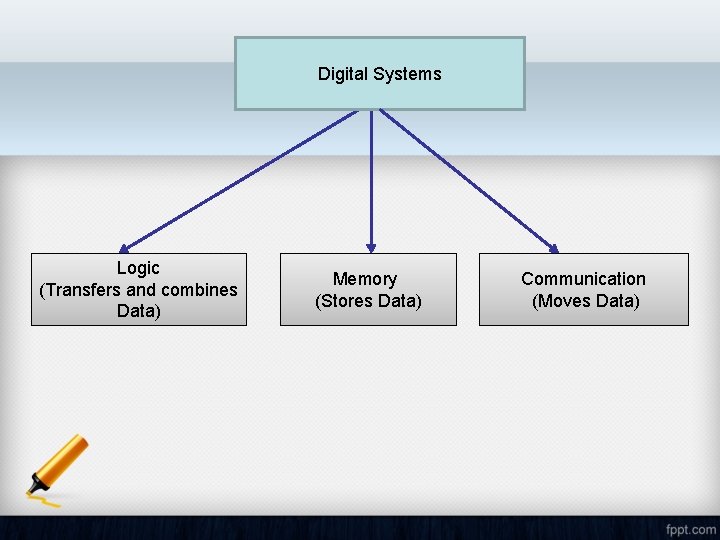

Digital Systems Logic (Transfers and combines Data) Memory (Stores Data) Communication (Moves Data)

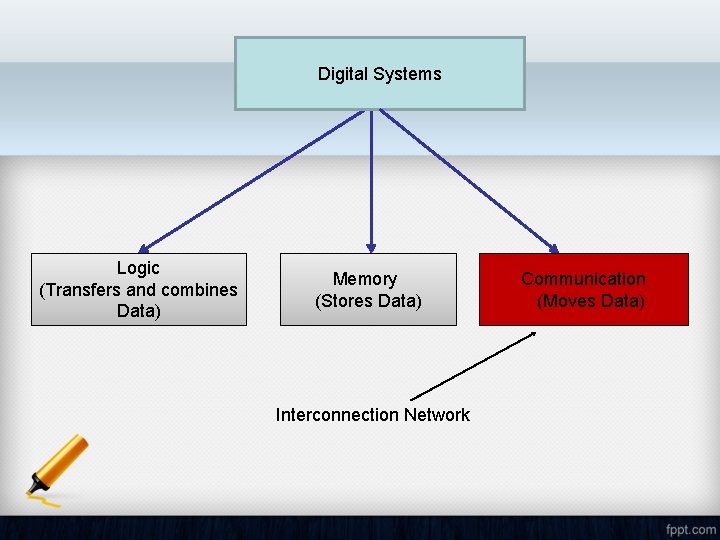

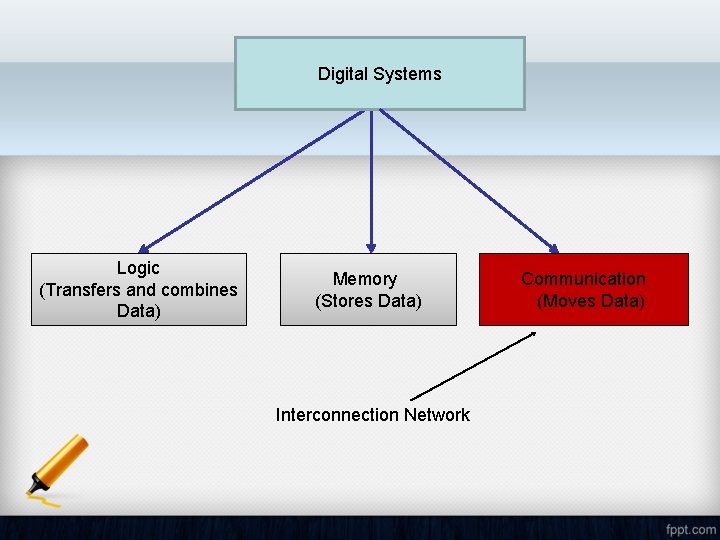

Digital Systems Logic (Transfers and combines Data) Memory (Stores Data) Interconnection Network Communication (Moves Data)

• Performance – limited by communication/interconnection not logic/memory • Power - most of the clock cycle spent on wire delays not gate delay. • Technology improves, memories and processors become small, fast, and inexpensive. • Also, the frequency of communication between components is lagging far beyond the clock rates of modern processors. • These factors combine to make interconnection the key factor in the success of future digital systems.

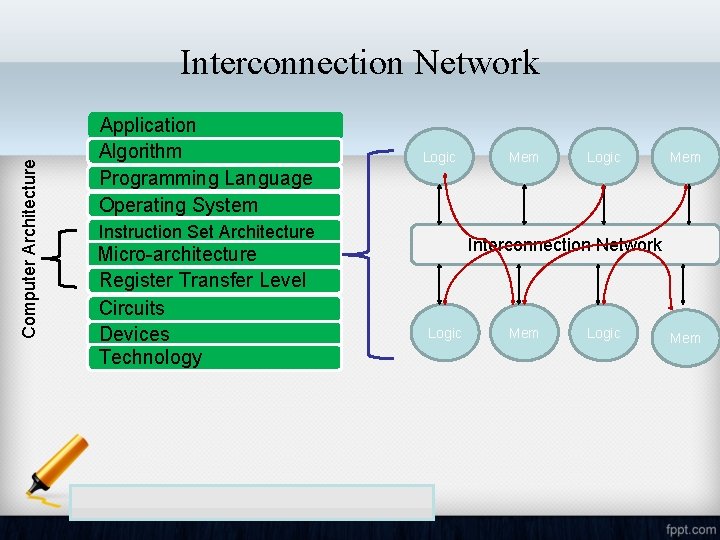

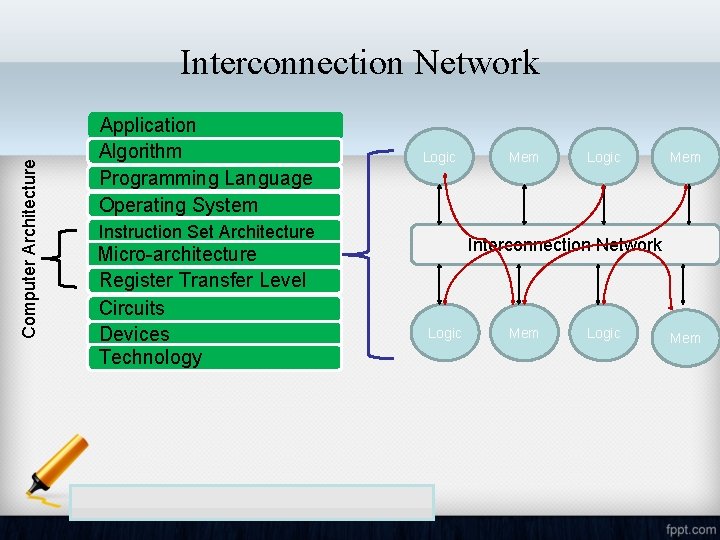

Computer Architecture Interconnection Network Application Algorithm Programming Language Operating System Logic Instruction Set Architecture Micro-architecture Register Transfer Level Circuits Devices Technology Mem Logic Mem Interconnection Network Logic Mem

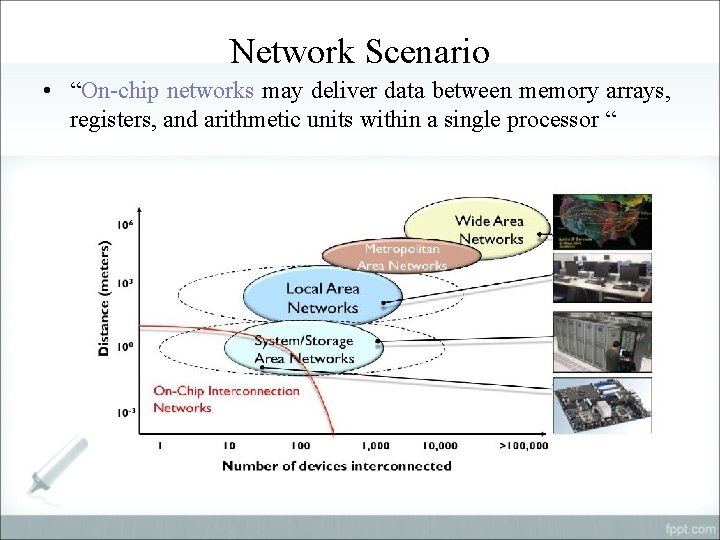

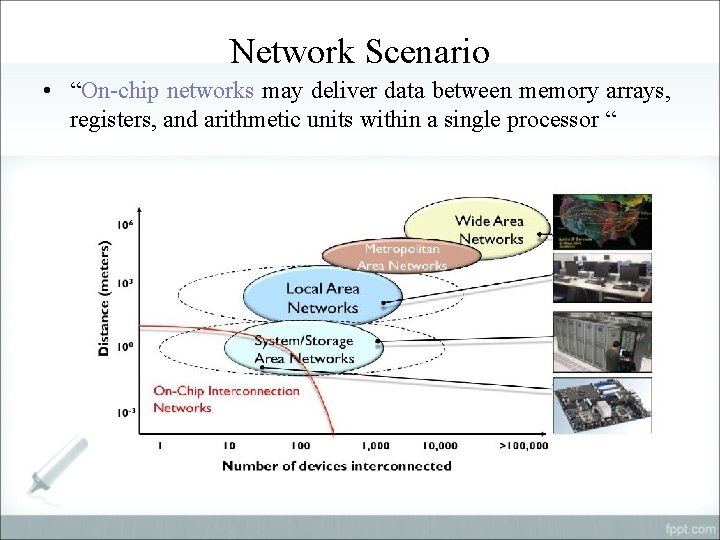

Network Scenario • “On-chip networks may deliver data between memory arrays, registers, and arithmetic units within a single processor “

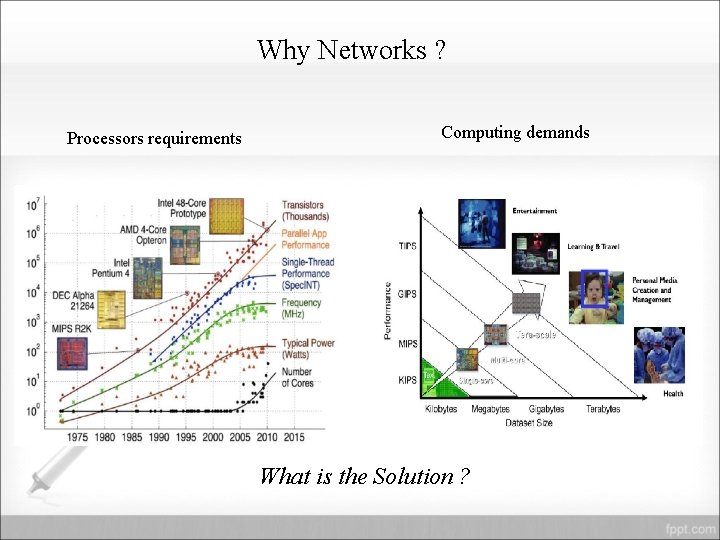

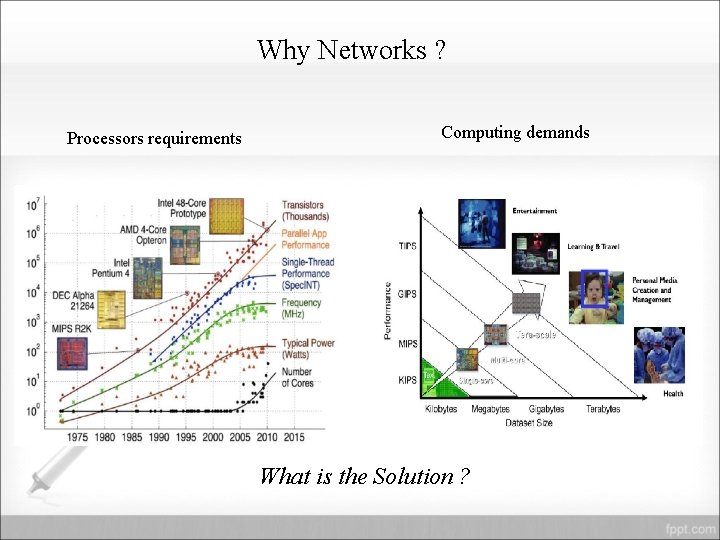

Why Networks ? Processors requirements Computing demands What is the Solution ?

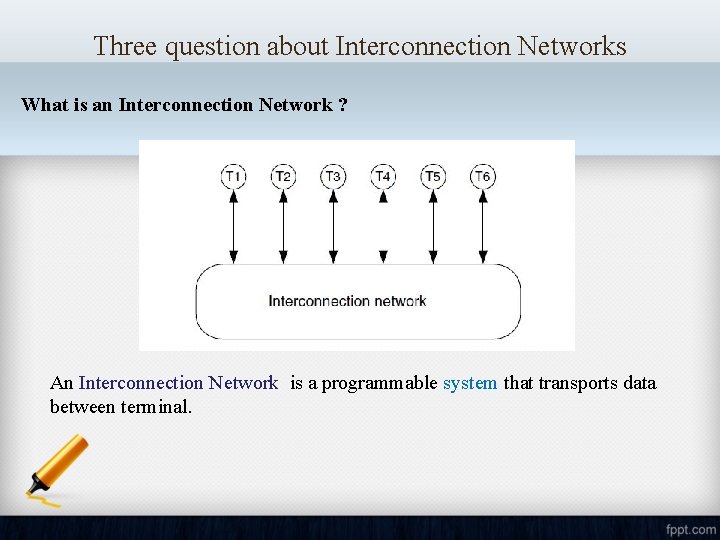

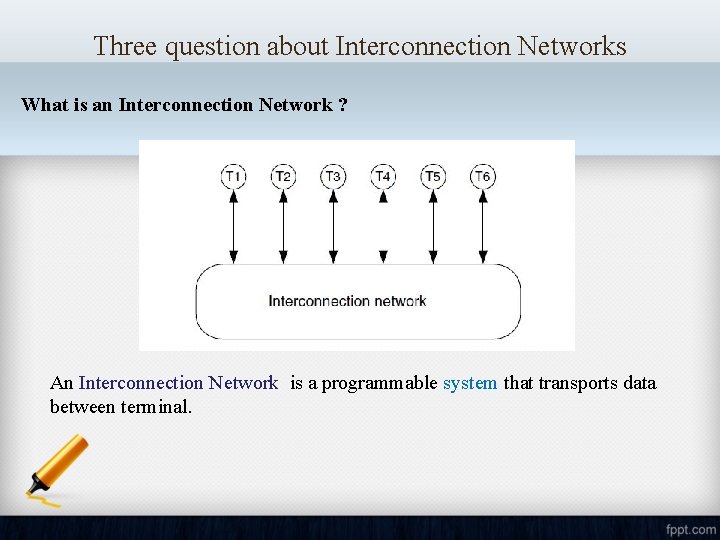

Three question about Interconnection Networks What is an Interconnection Network ? An Interconnection Network is a programmable system that transports data between terminal.

Where do you find Interconnection Network ? • They are used in almost all digital systems that are large enough to have two components to connect. • The most common applications computer systems and communication switches • Computer System - they connect processors to memories and input/output (I/O) devices to I/O controllers • Communication Switches - They connect input ports to output ports

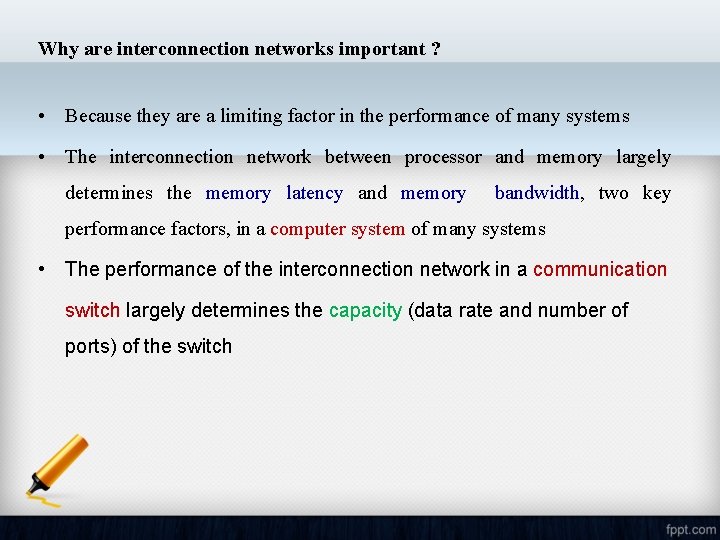

Why are interconnection networks important ? • Because they are a limiting factor in the performance of many systems • The interconnection network between processor and memory largely determines the memory latency and memory bandwidth, two key performance factors, in a computer system of many systems • The performance of the interconnection network in a communication switch largely determines the capacity (data rate and number of ports) of the switch

Why on-chip networks ? • They provide external connectivity from system to outside world �Also, connectivity within a single computer system at many levels �I/O units , chips, modules and blocks inside chips • Trends: high demand on communication bandwidth �Increased computing power and storage capacity �Switched networks are replacing buses • Integral part of many-core architectures �Energy consumed by communication will exceed that of computation in future systems

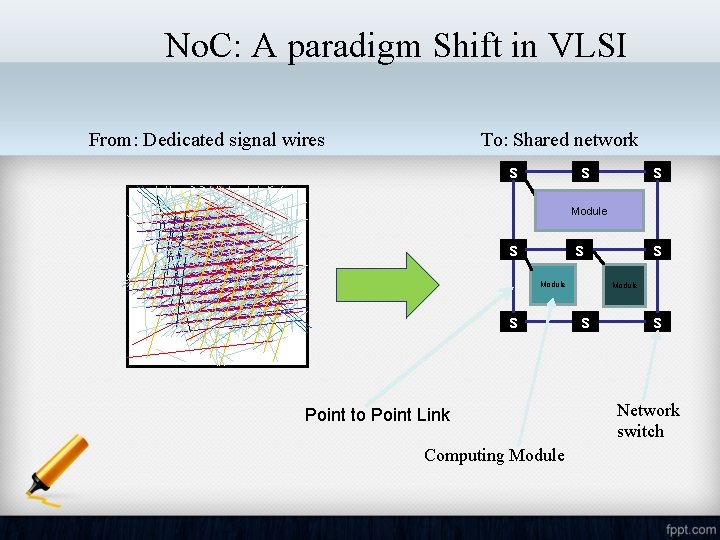

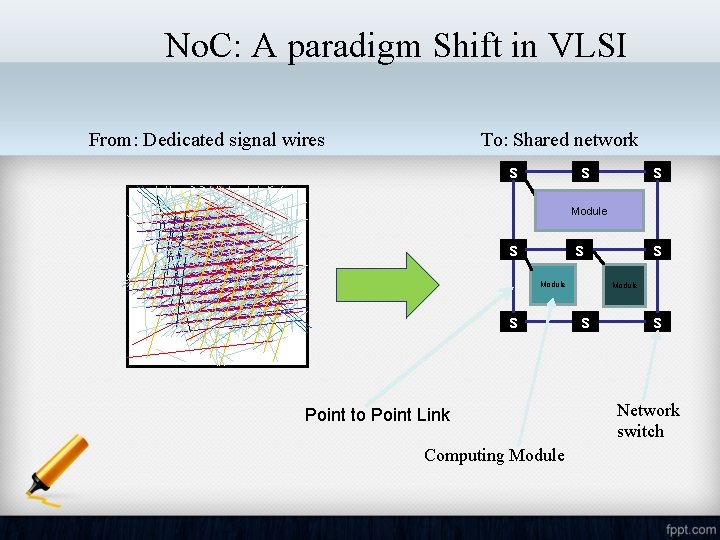

No. C: A paradigm Shift in VLSI From: Dedicated signal wires To: Shared network s s s Module s Point to Point Link Computing Module s s Network switch

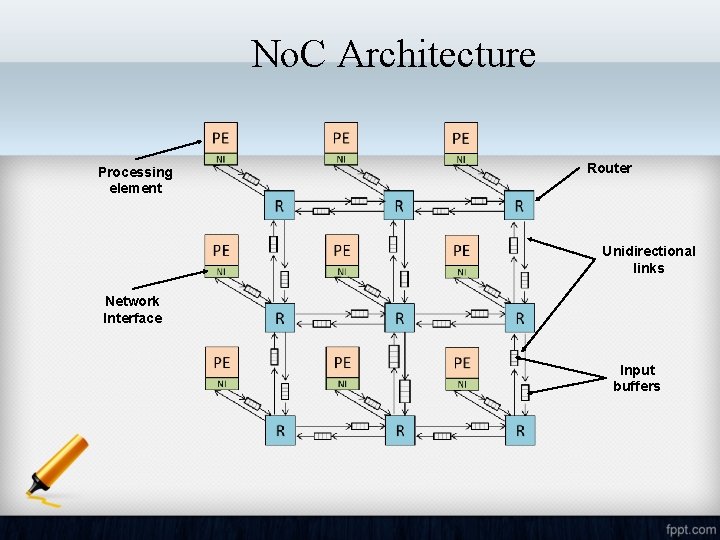

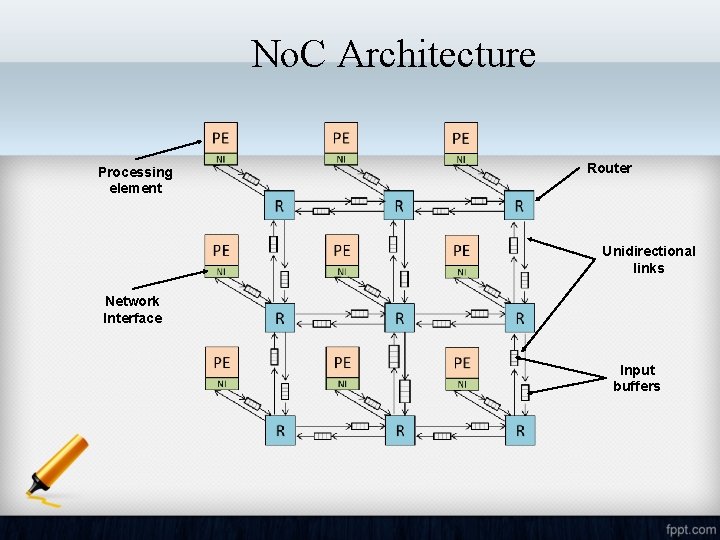

No. C Architecture Processing element Router Unidirectional links Network Interface Input buffers

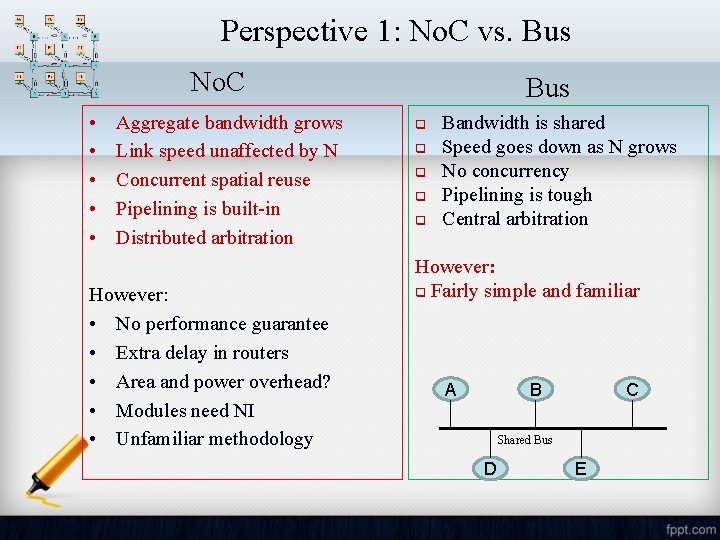

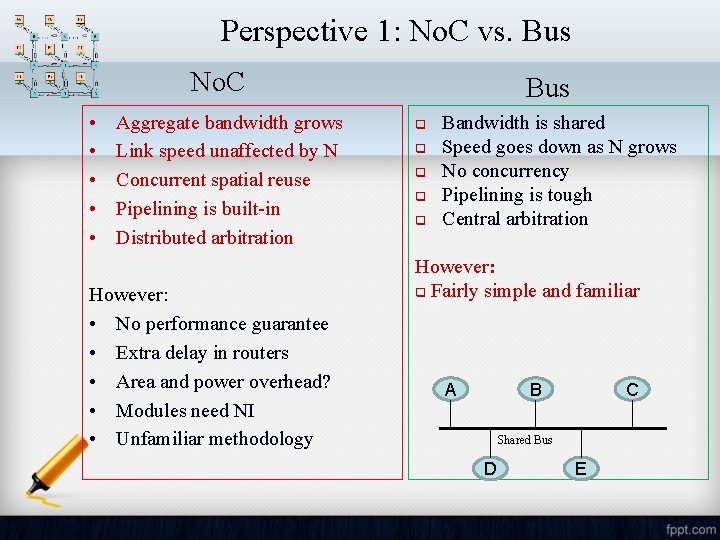

Perspective 1: No. C vs. Bus No. C • • • Aggregate bandwidth grows Link speed unaffected by N Concurrent spatial reuse Pipelining is built-in Distributed arbitration However: • No performance guarantee • Extra delay in routers • Area and power overhead? • Modules need NI • Unfamiliar methodology Bus q q q Bandwidth is shared Speed goes down as N grows No concurrency Pipelining is tough Central arbitration However: q Fairly simple and familiar A B C Shared Bus D E

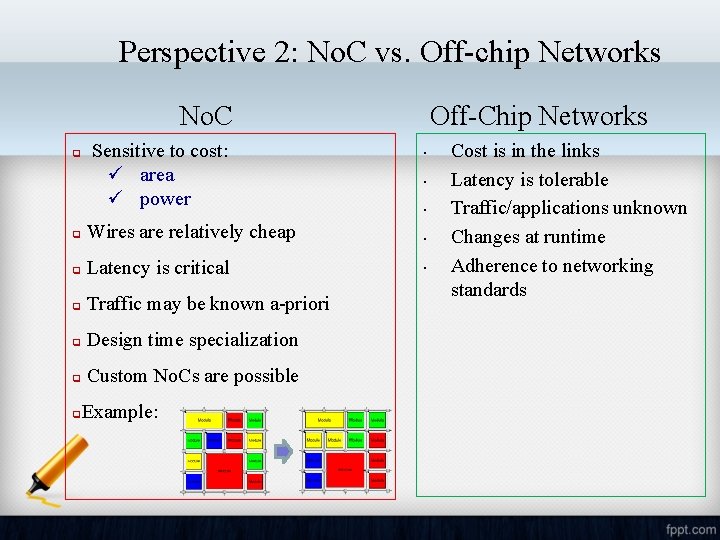

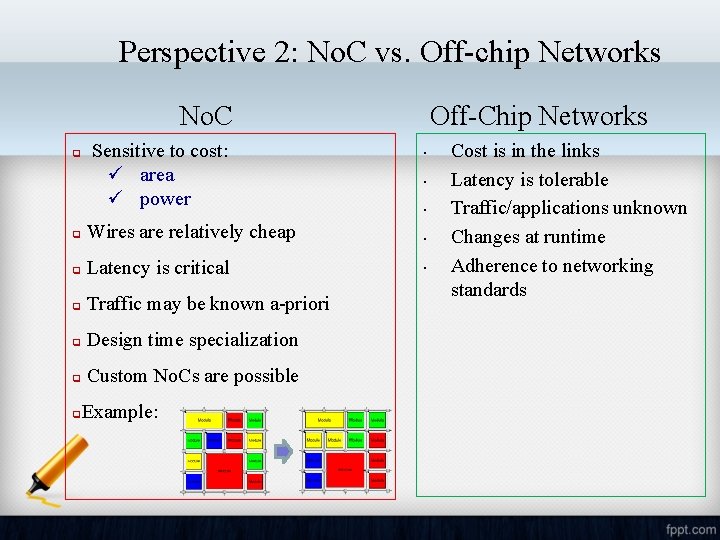

Perspective 2: No. C vs. Off-chip Networks No. C q Sensitive to cost: ü area ü power Off-Chip Networks • • • q Wires are relatively cheap • q Latency is critical • q Traffic may be known a-priori q Design time specialization q Custom No. Cs are possible q Example: Cost is in the links Latency is tolerable Traffic/applications unknown Changes at runtime Adherence to networking standards

Performance Metrics: • Packet Latency • Effective Bandwidth

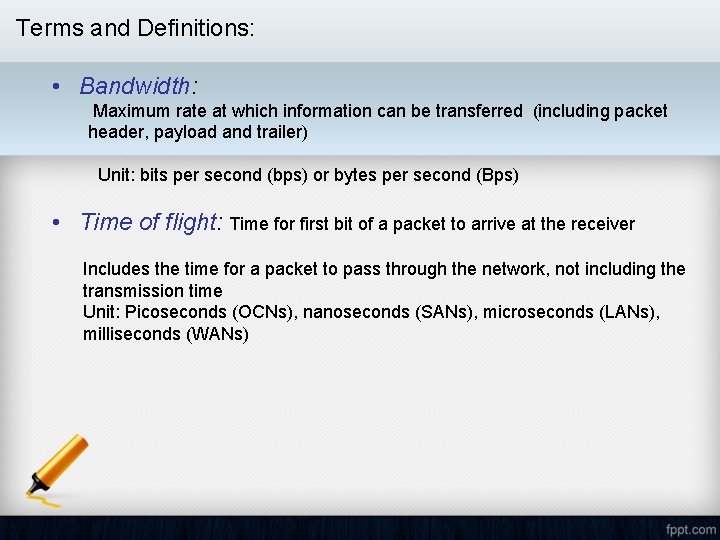

Terms and Definitions: • Bandwidth: Maximum rate at which information can be transferred (including packet header, payload and trailer) Unit: bits per second (bps) or bytes per second (Bps) • Time of flight: Time for first bit of a packet to arrive at the receiver Includes the time for a packet to pass through the network, not including the transmission time Unit: Picoseconds (OCNs), nanoseconds (SANs), microseconds (LANs), milliseconds (WANs)

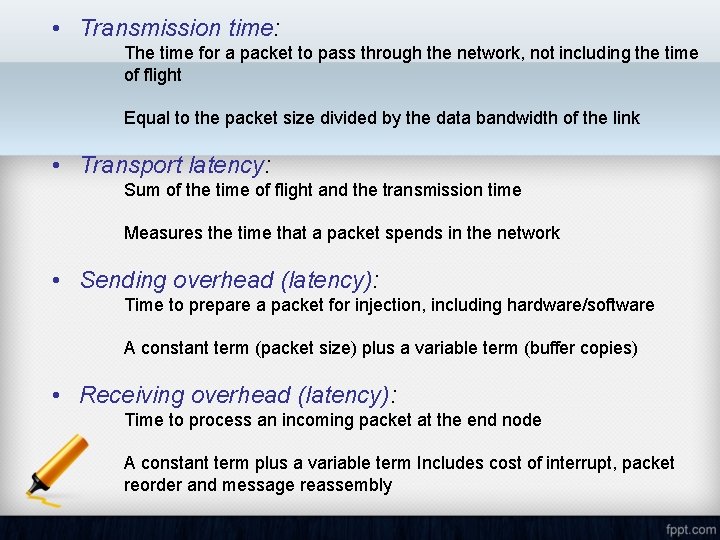

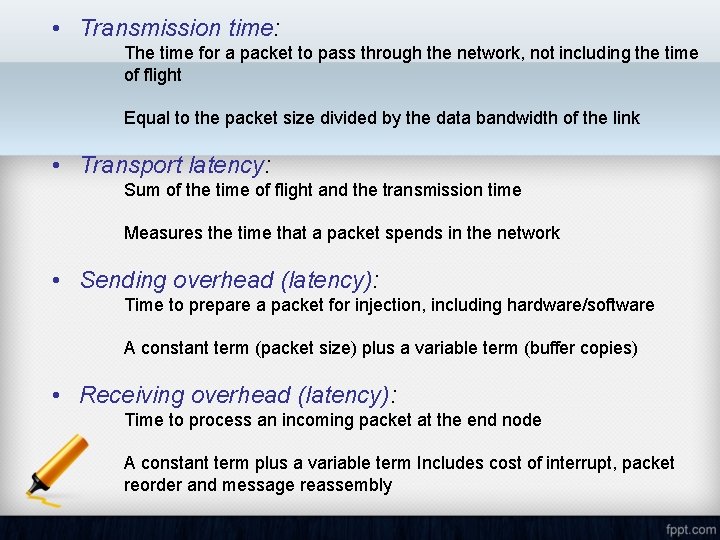

• Transmission time: The time for a packet to pass through the network, not including the time of flight Equal to the packet size divided by the data bandwidth of the link • Transport latency: Sum of the time of flight and the transmission time Measures the time that a packet spends in the network • Sending overhead (latency): Time to prepare a packet for injection, including hardware/software A constant term (packet size) plus a variable term (buffer copies) • Receiving overhead (latency): Time to process an incoming packet at the end node A constant term plus a variable term Includes cost of interrupt, packet reorder and message reassembly

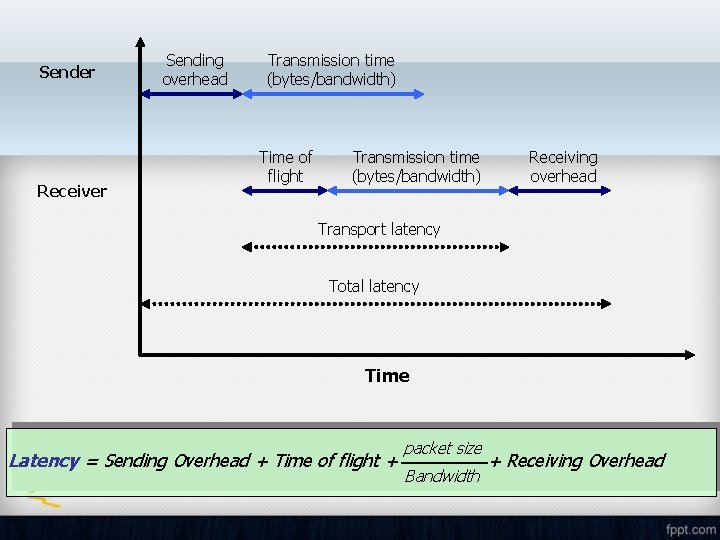

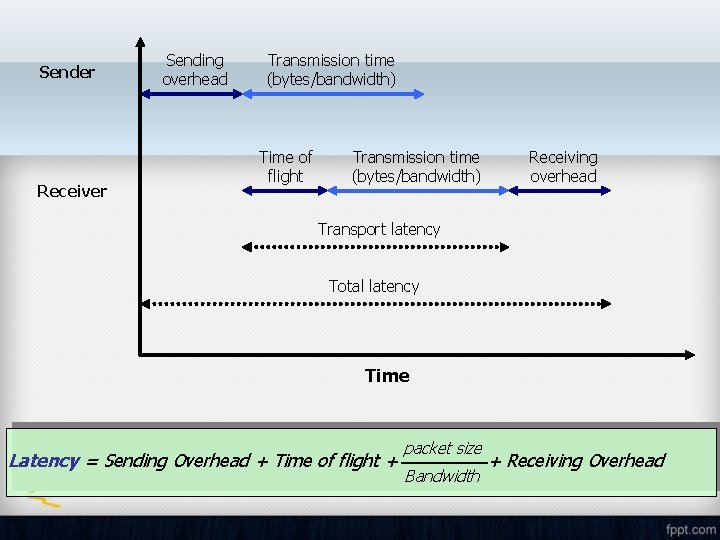

Sender Receiver Sending overhead Transmission time (bytes/bandwidth) Time of flight Transmission time (bytes/bandwidth) Receiving overhead Transport latency Total latency Time Latency = Sending Overhead + Time of flight + packet size Bandwidth + Receiving Overhead

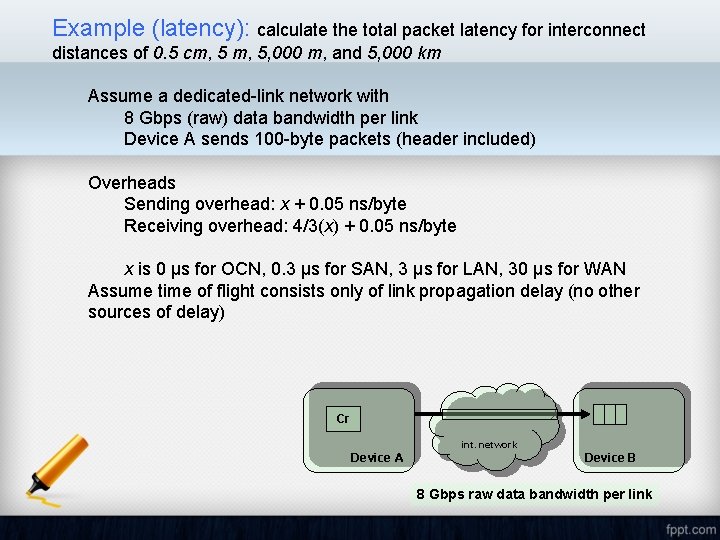

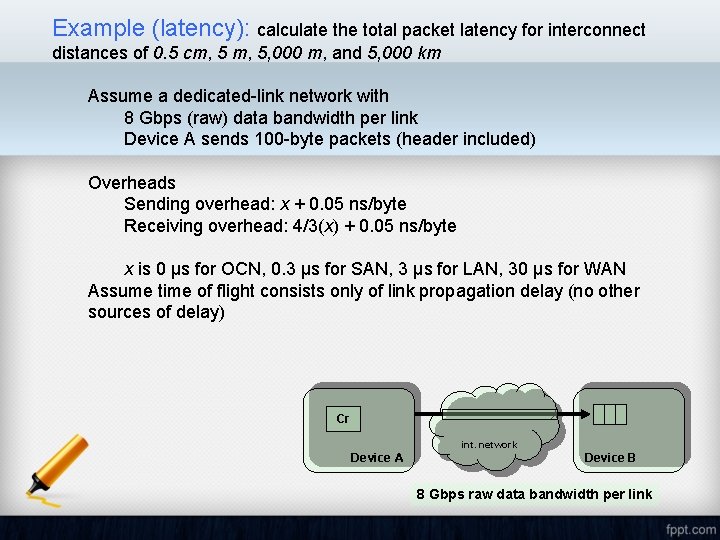

Example (latency): calculate the total packet latency for interconnect distances of 0. 5 cm, 5, 000 m, and 5, 000 km Assume a dedicated-link network with 8 Gbps (raw) data bandwidth per link Device A sends 100 -byte packets (header included) Overheads Sending overhead: x + 0. 05 ns/byte Receiving overhead: 4/3(x) + 0. 05 ns/byte x is 0 μs for OCN, 0. 3 μs for SAN, 3 μs for LAN, 30 μs for WAN Assume time of flight consists only of link propagation delay (no other sources of delay) Cr int. network Device A Device B 8 Gbps raw data bandwidth per link

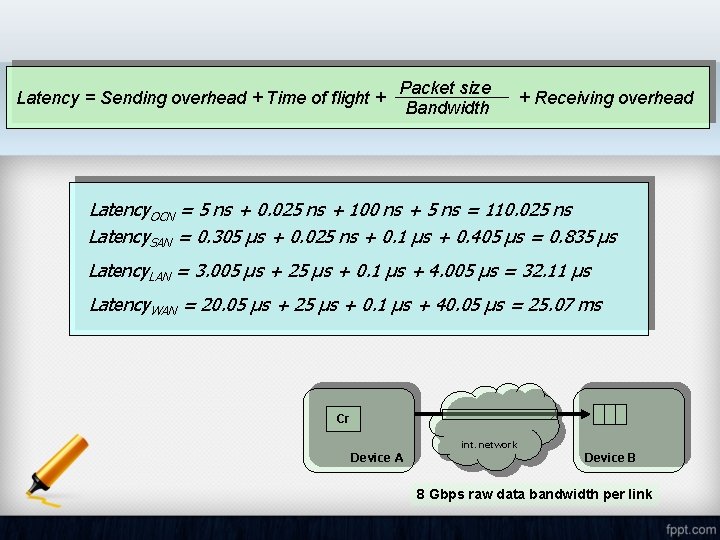

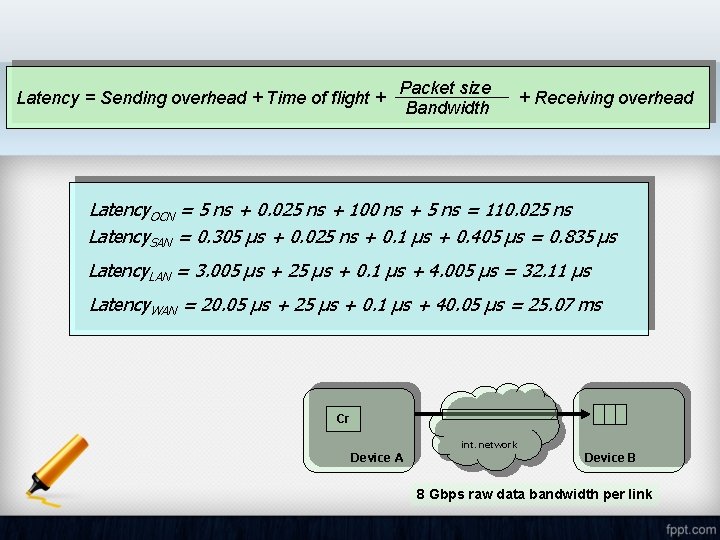

Latency = Sending overhead + Time of flight + Packet size Bandwidth + Receiving overhead Latency. OCN = 5 ns + 0. 025 ns + 100 ns + 5 ns = 110. 025 ns Latency. SAN = 0. 305 μs + 0. 025 ns + 0. 1 μs + 0. 405 μs = 0. 835 μs Latency. LAN = 3. 005 μs + 25 μs + 0. 1 μs + 4. 005 μs = 32. 11 μs Latency. WAN = 20. 05 μs + 25 μs + 0. 1 μs + 40. 05 μs = 25. 07 ms Cr int. network Device A Device B 8 Gbps raw data bandwidth per link