Introduction to IC Design TsungChu Huang Department of

- Slides: 38

Introduction to IC Design Tsung-Chu Huang (黃宗柱) Department of Electronic Eng. Chong Chou Institute of Tech. Email: tch@dragon. ccut. edu. tw TCH 2003/10/4 EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 1

2003/10/4 MOS Transistor Theory Ÿ MOS V-I Characteristics/Modeling Ÿ Pass Transistor Operation Ÿ Some Special Primitives in Last Lecture - Tri-State, MUX, XOR, Latch/FF Ÿ CMOS Inverter Operation Ÿ Various Inverters Ÿ Transistor Sizing TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 2

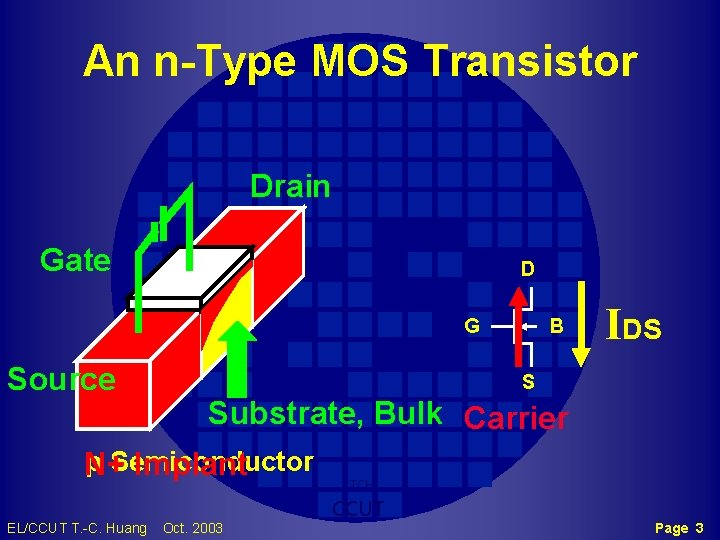

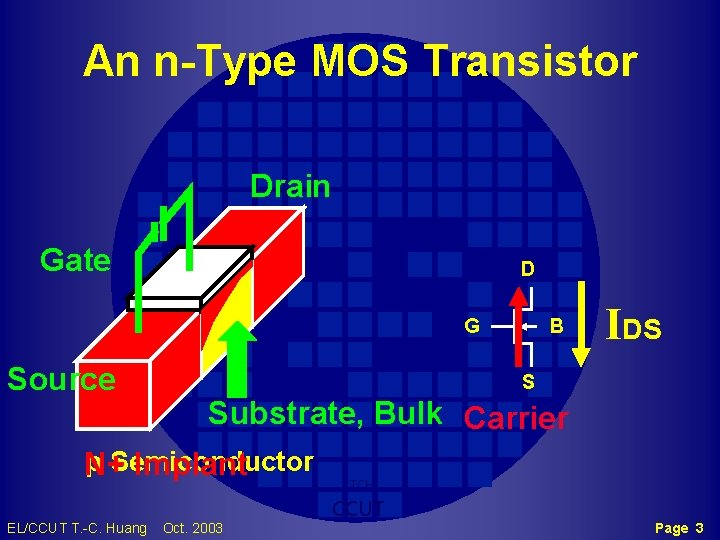

An n-Type MOS Transistor Drain Gate D G Source B IDS S Substrate, Bulk Carrier p Semiconductor N+ Implant TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 3

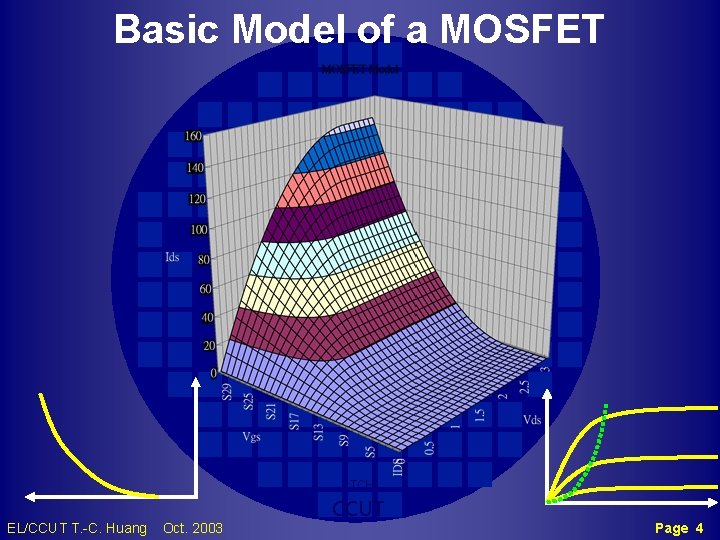

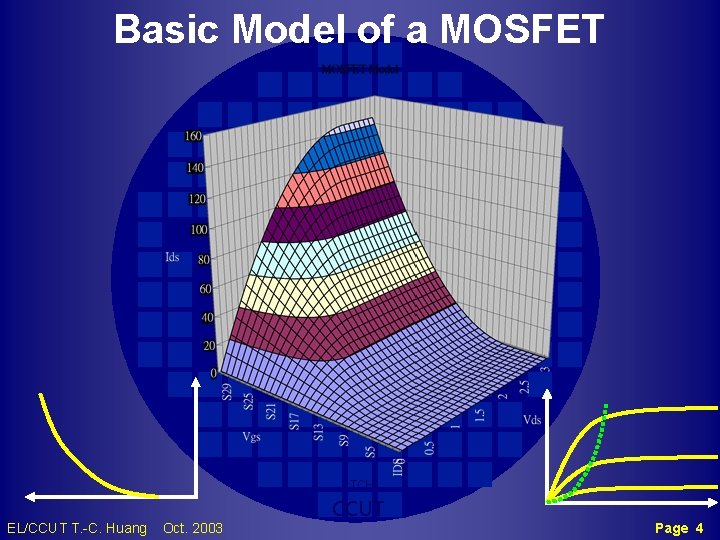

Basic Model of a MOSFET TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 4

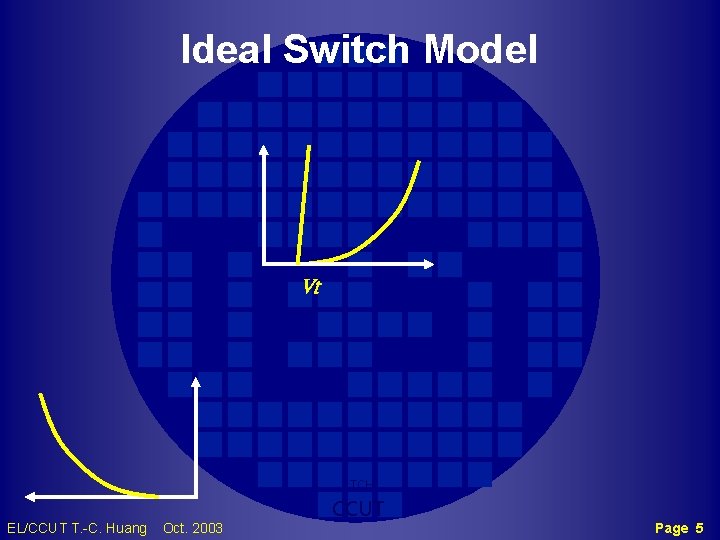

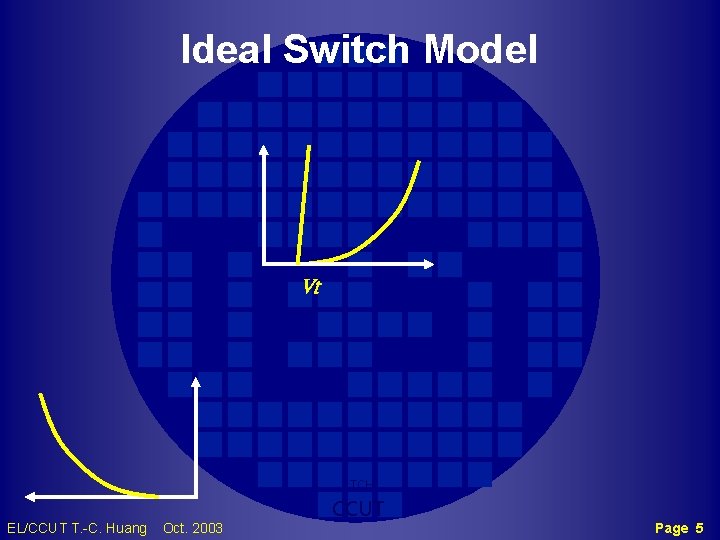

Ideal Switch Model Vt TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 5

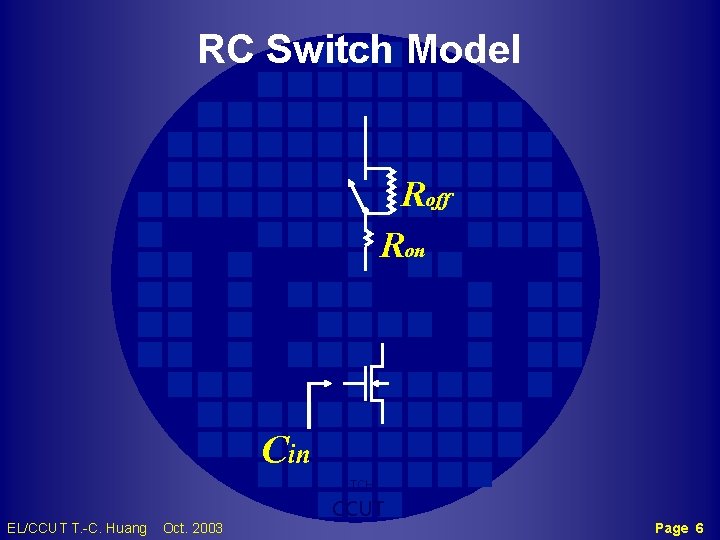

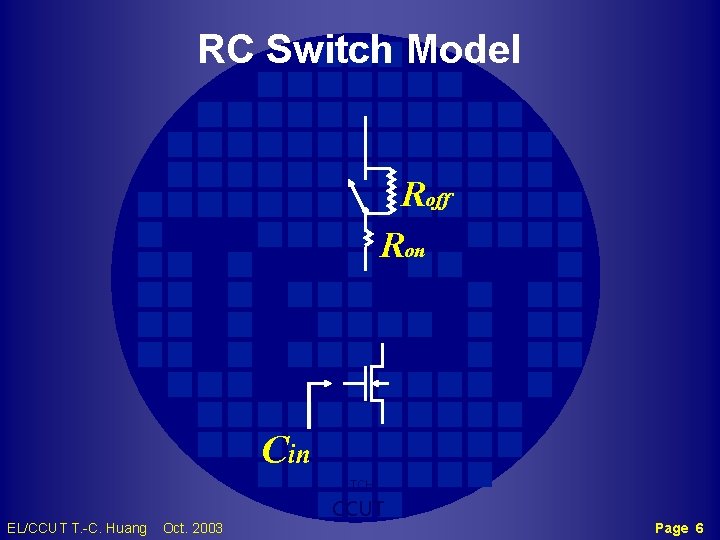

RC Switch Model Roff Ron Cin TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 6

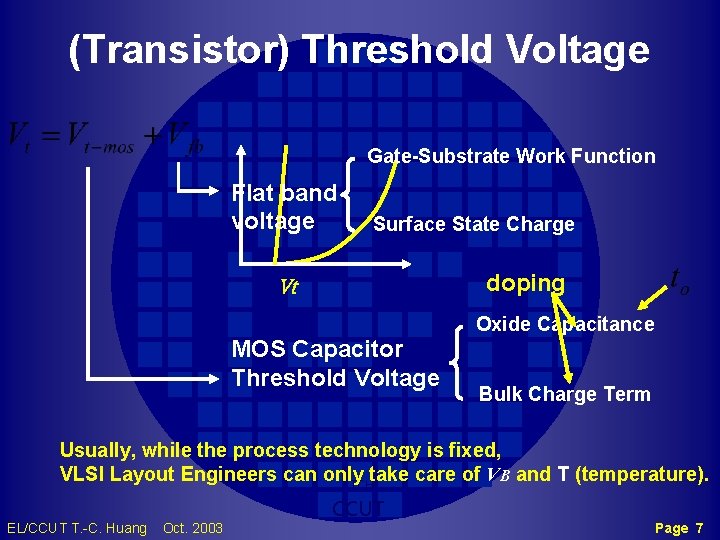

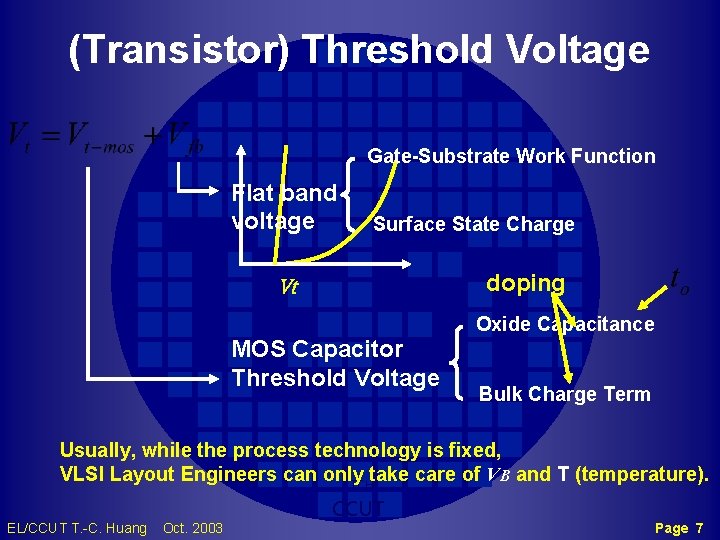

(Transistor) Threshold Voltage Gate-Substrate Work Function Flat band voltage Surface State Charge doping Vt Oxide Capacitance MOS Capacitor Threshold Voltage Bulk Charge Term Usually, while the process technology is fixed, VLSI Layout Engineers can only take care of VB and T (temperature). TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 7

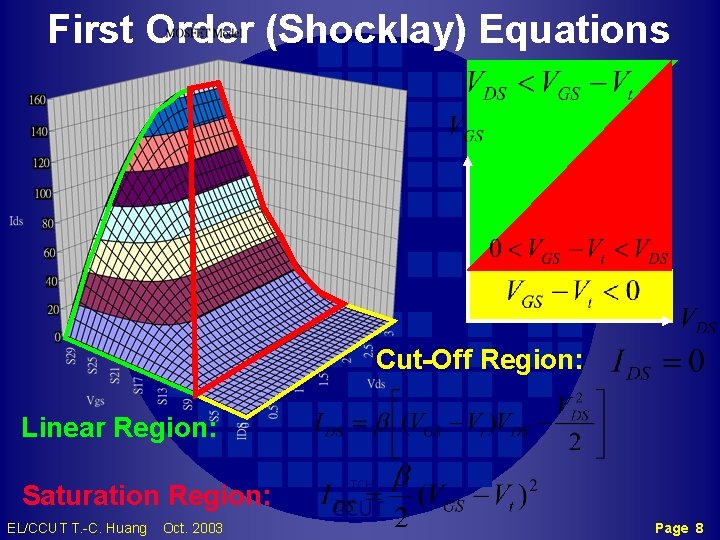

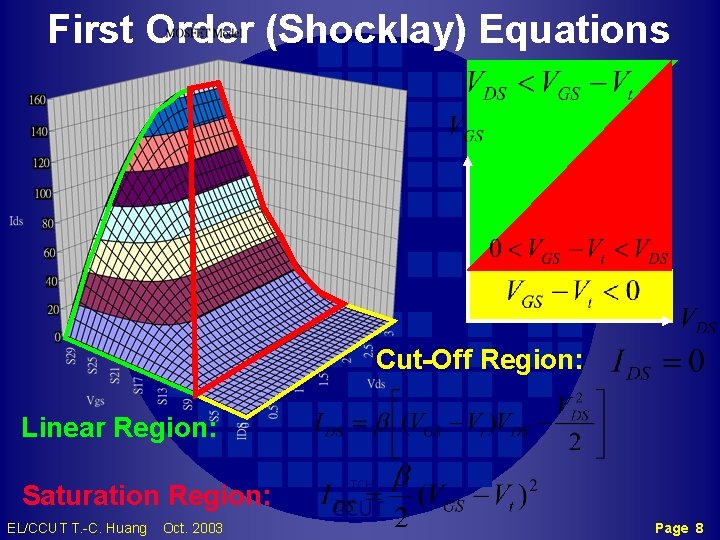

First Order (Shocklay) Equations Cut-Off Region: Linear Region: Saturation Region: EL/CCUT T. -C. Huang Oct. 2003 TCH CCUT Page 8

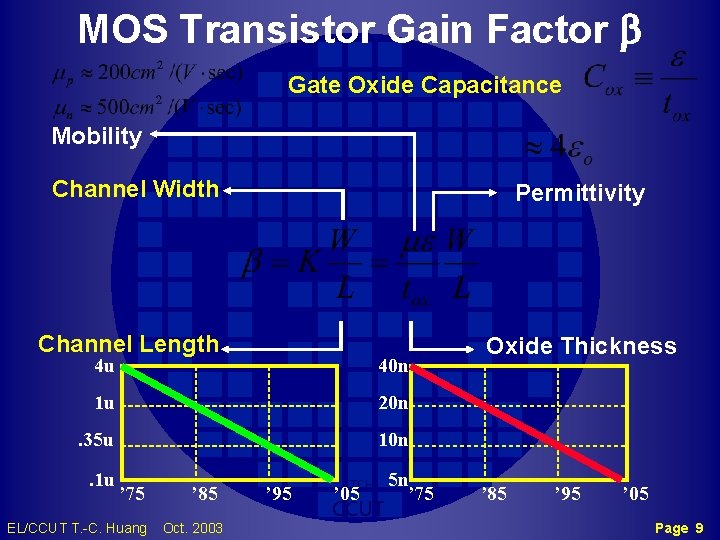

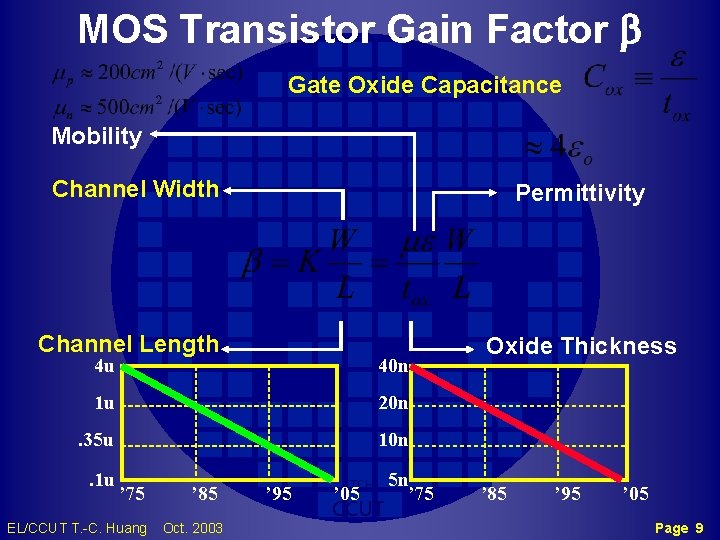

MOS Transistor Gain Factor b Gate Oxide Capacitance Mobility Channel Width Permittivity Channel Length Oxide Thickness 4 u 40 n 1 u 20 n . 35 u 10 n . 1 u ’ 75 EL/CCUT T. -C. Huang ’ 85 Oct. 2003 ’ 95 TCH ’ 05 CCUT 5 n ’ 75 ’ 85 ’ 95 ’ 05 Page 9

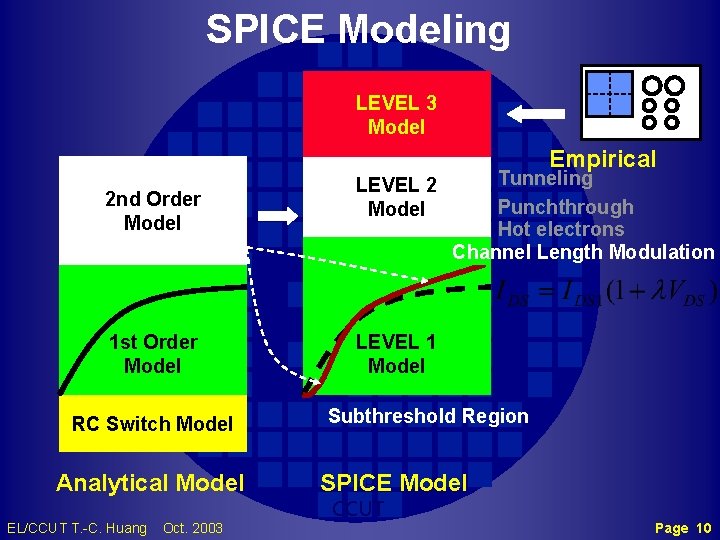

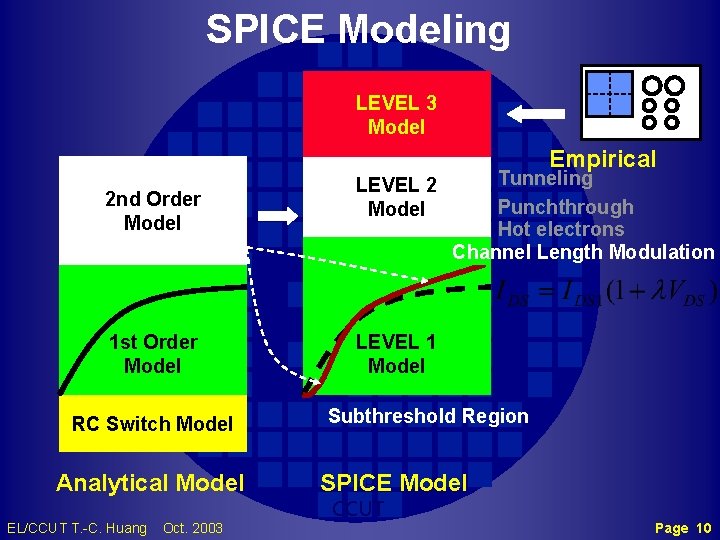

SPICE Modeling LEVEL 3 Model Empirical 2 nd Order Model 1 st Order Model RC Switch Model Analytical Model EL/CCUT T. -C. Huang Oct. 2003 LEVEL 2 Model Tunneling Punchthrough Hot electrons Channel Length Modulation LEVEL 1 Model Subthreshold Region TCH SPICE Model CCUT Page 10

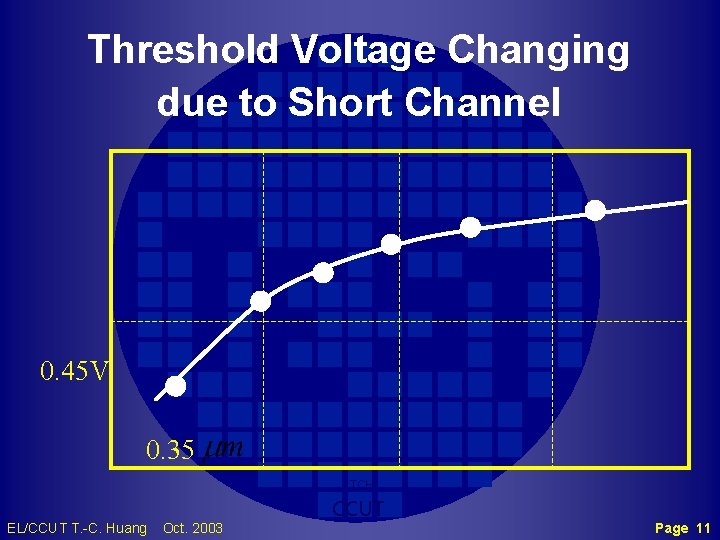

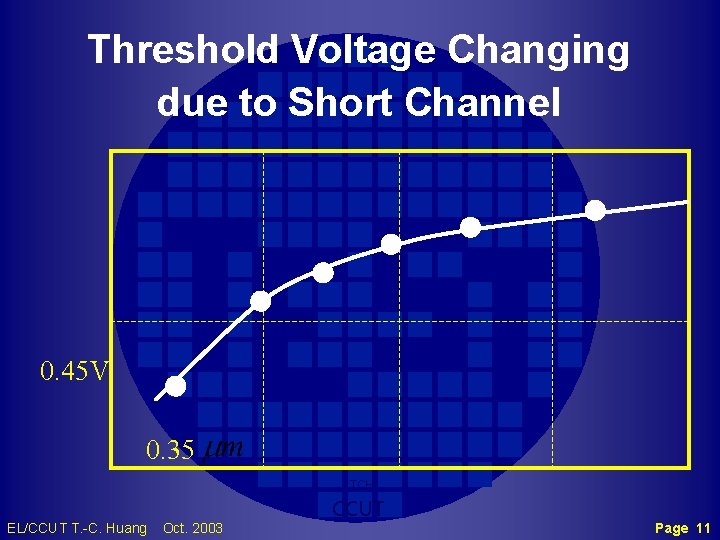

Threshold Voltage Changing due to Short Channel 0. 45 V 0. 35 TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 11

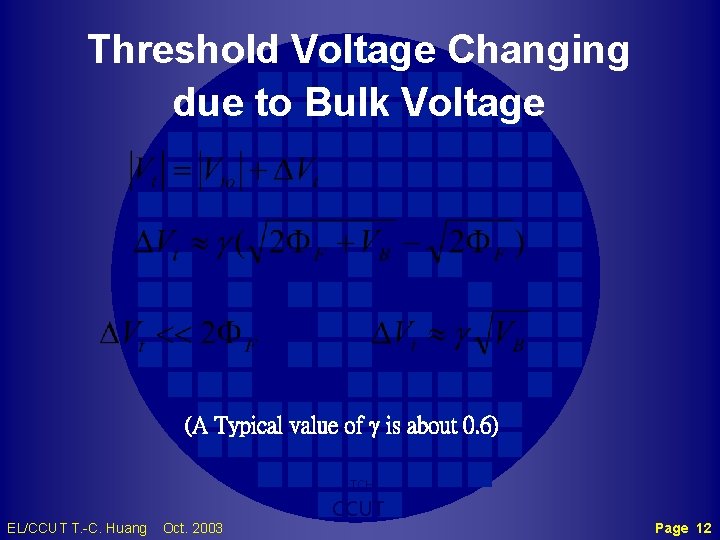

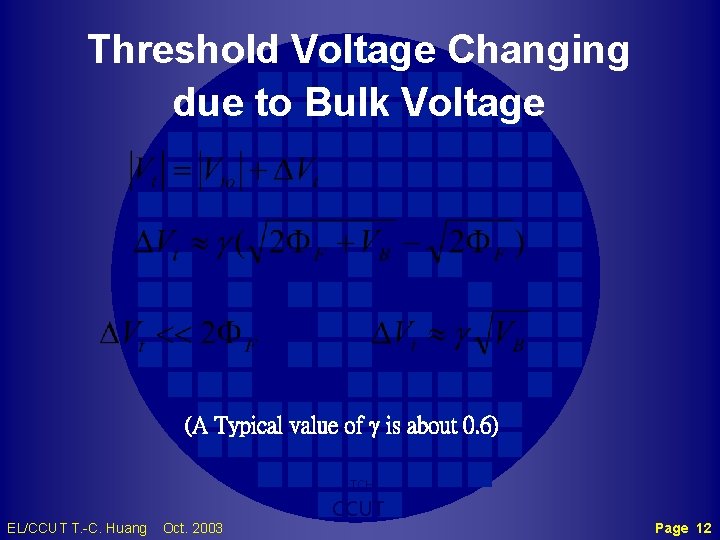

Threshold Voltage Changing due to Bulk Voltage (A Typical value of g is about 0. 6) TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 12

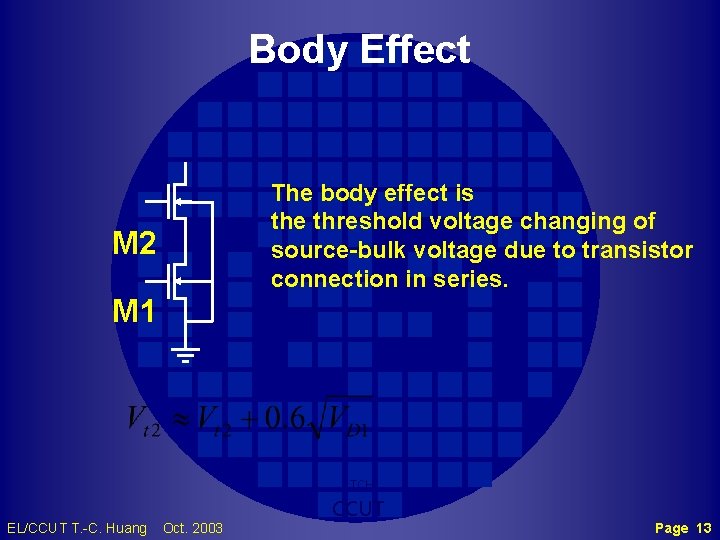

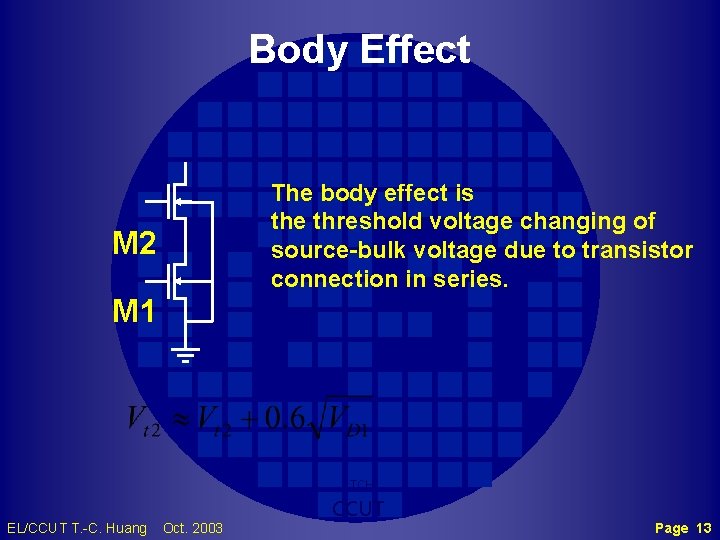

Body Effect The body effect is the threshold voltage changing of source-bulk voltage due to transistor connection in series. M 2 M 1 TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 13

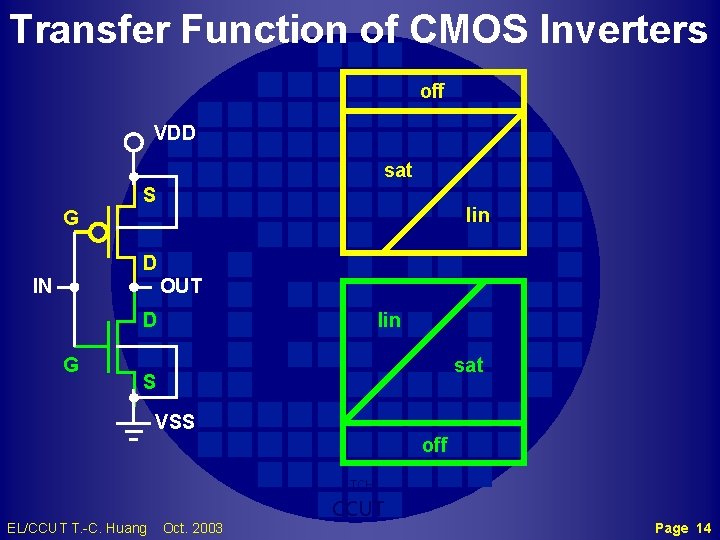

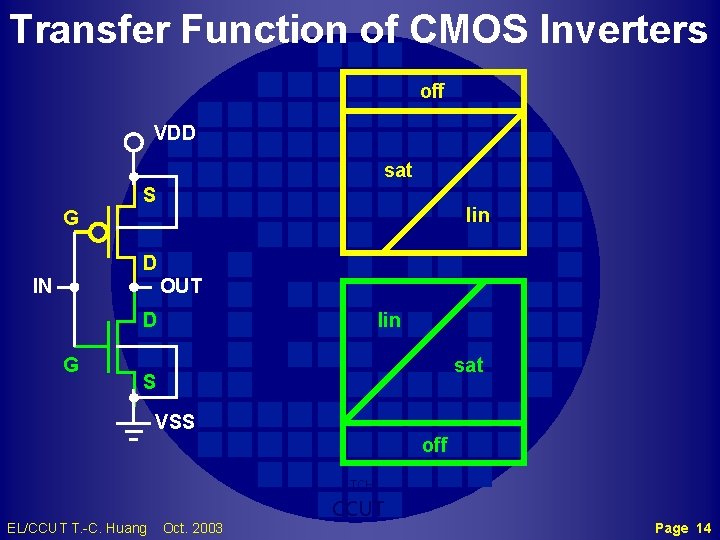

Transfer Function of CMOS Inverters off VDD sat S lin G D IN OUT D G lin sat S VSS off TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 14

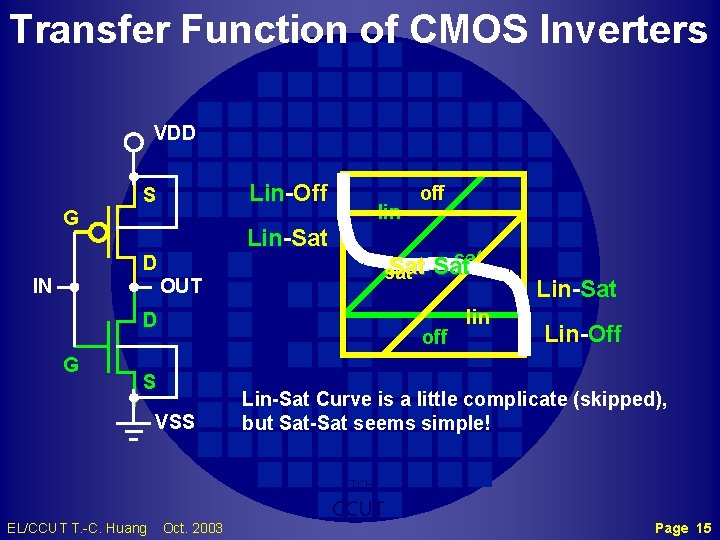

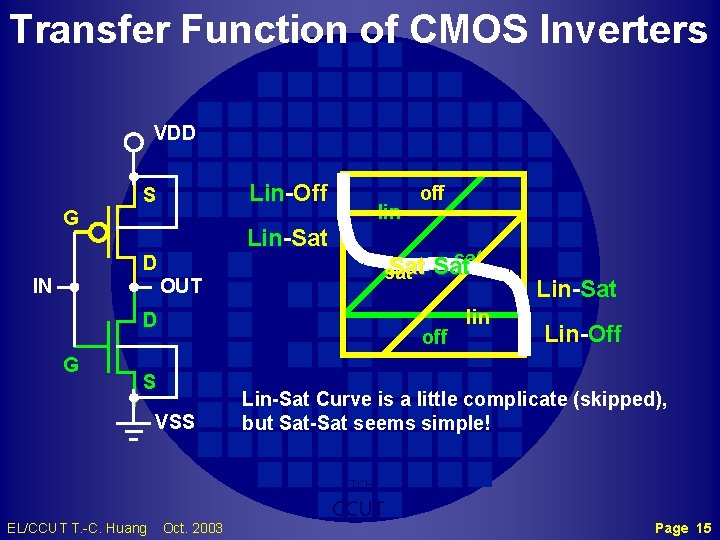

Transfer Function of CMOS Inverters VDD Lin-Off S G lin Lin-Sat sat Sat-Sat sat D IN OUT D G off S VSS lin Lin-Sat Lin-Off Lin-Sat Curve is a little complicate (skipped), but Sat-Sat seems simple! TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 15

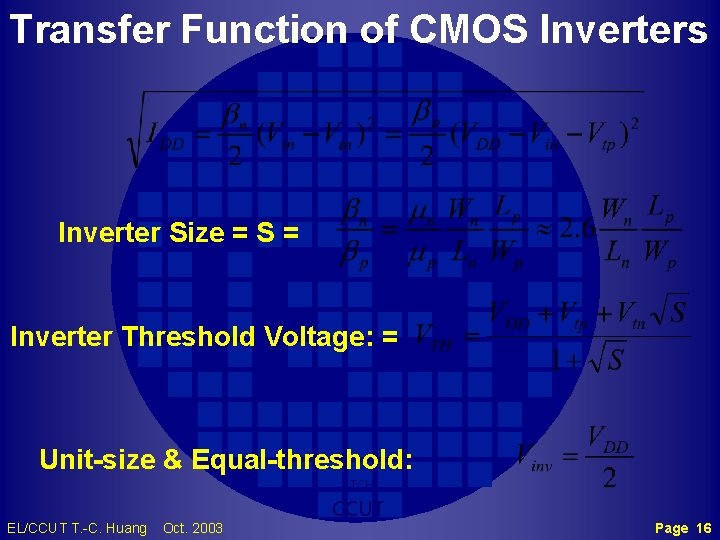

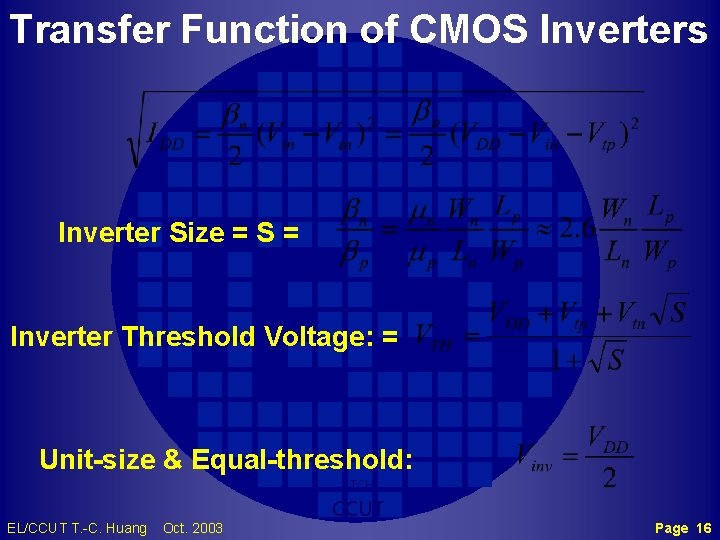

Transfer Function of CMOS Inverters Inverter Size = S = Inverter Threshold Voltage: = Unit-size & Equal-threshold: TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 16

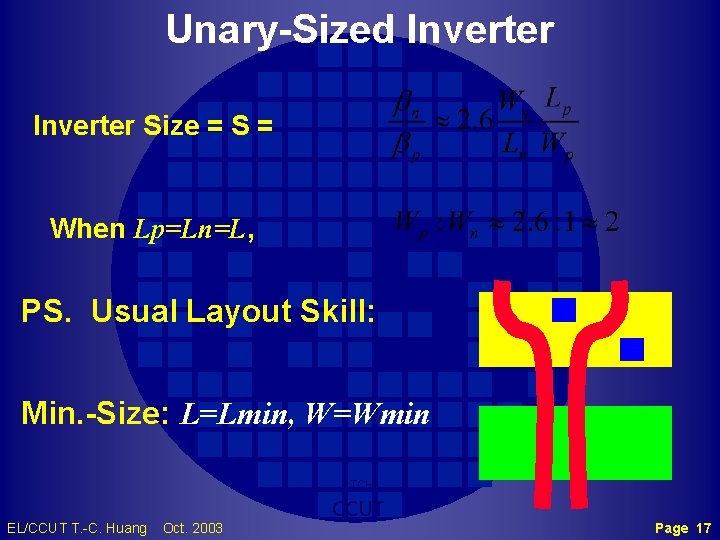

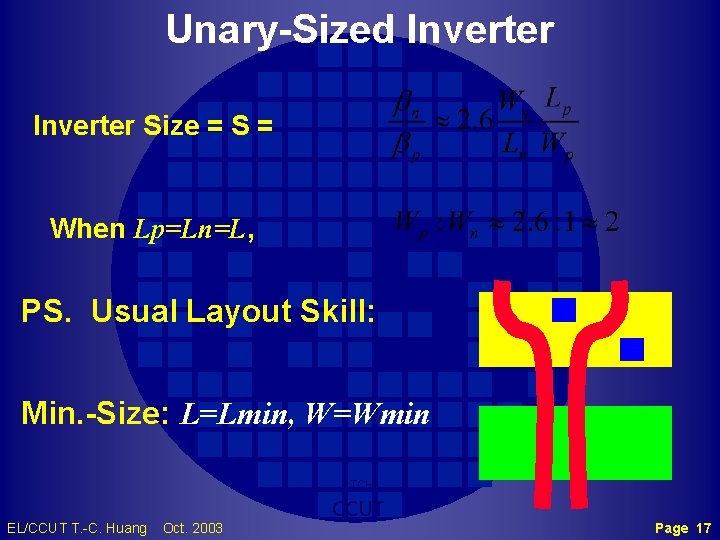

Unary-Sized Inverter Size = S = When Lp=Ln=L, PS. Usual Layout Skill: Min. -Size: L=Lmin, W=Wmin TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 17

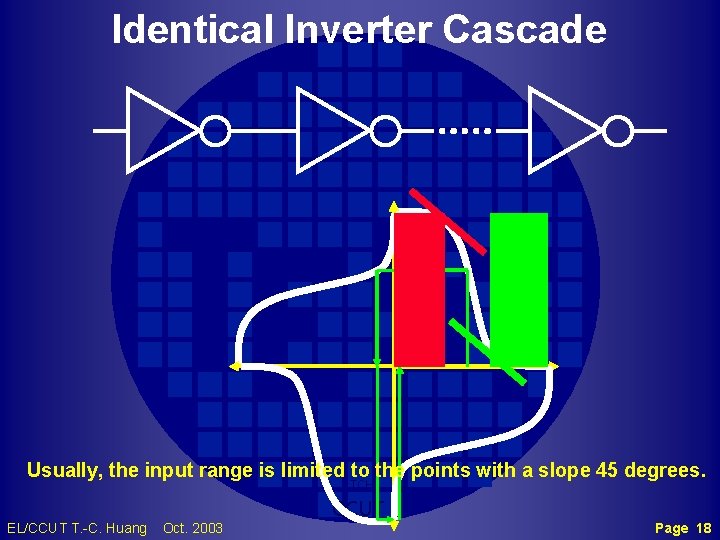

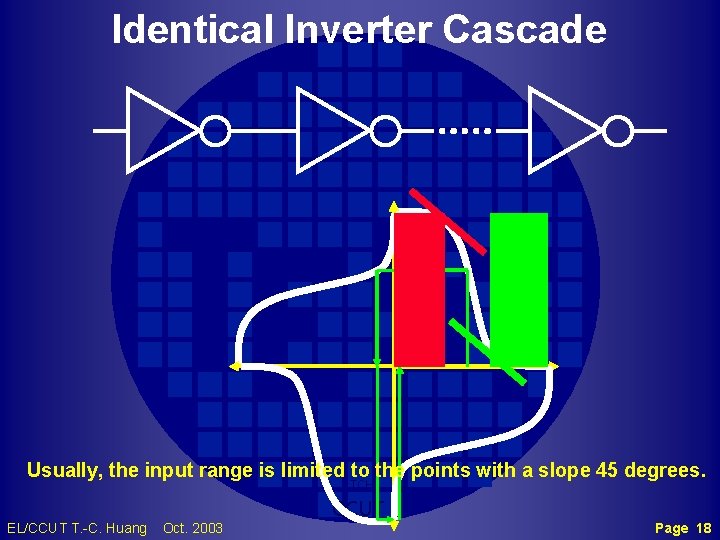

Identical Inverter Cascade Usually, the input range is limited to the points with a slope 45 degrees. TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 18

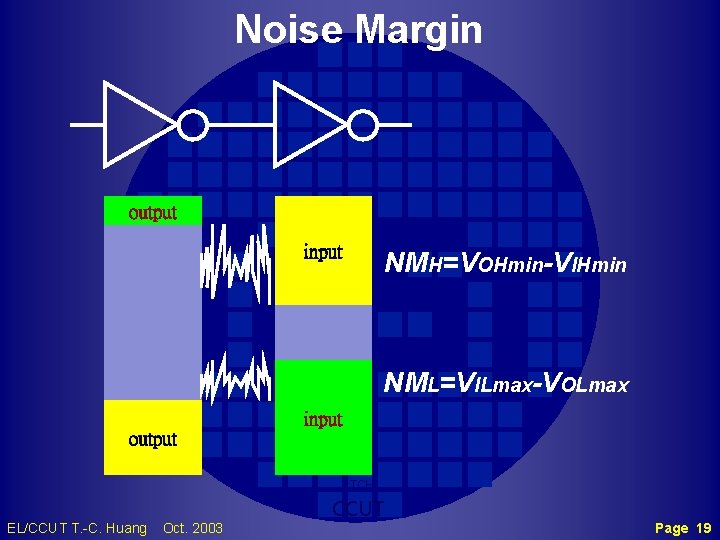

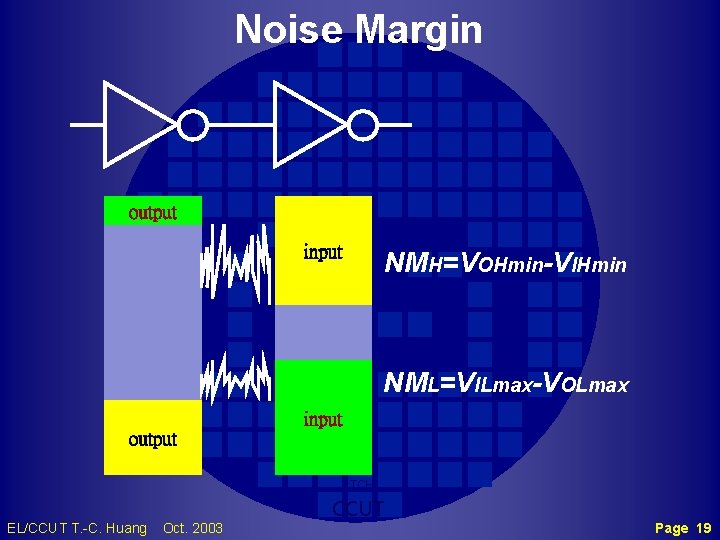

Noise Margin output input NMH=VOHmin-VIHmin NML=VILmax-VOLmax output input TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 19

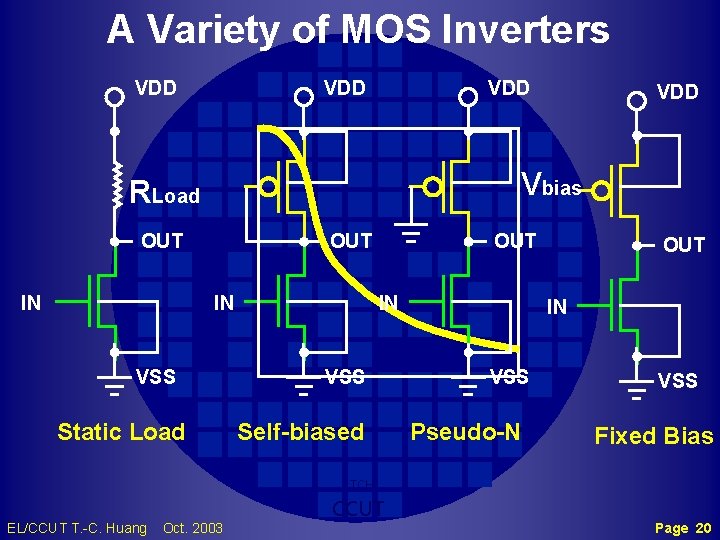

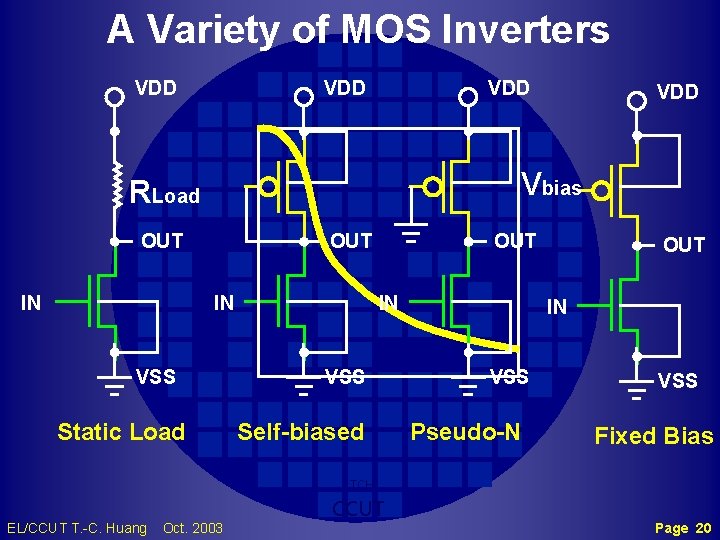

A Variety of MOS Inverters VDD VDD Vbias RLoad OUT IN VDD OUT IN VSS Static Load IN VSS Self-biased OUT IN VSS Pseudo-N VSS Fixed Bias TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 20

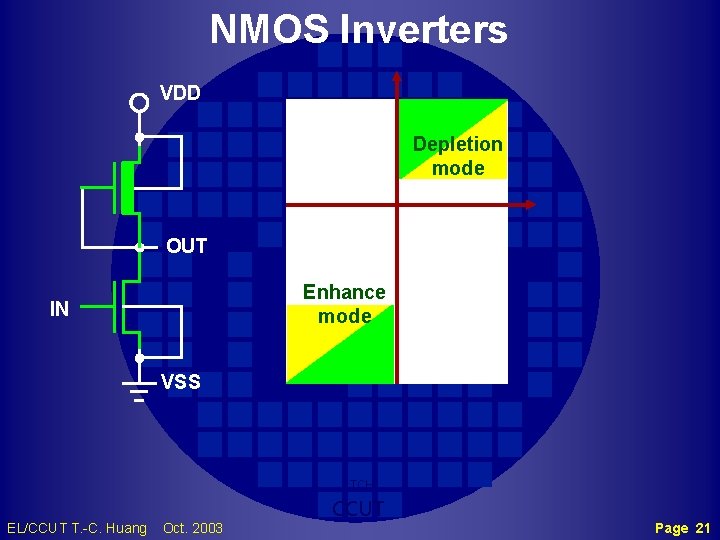

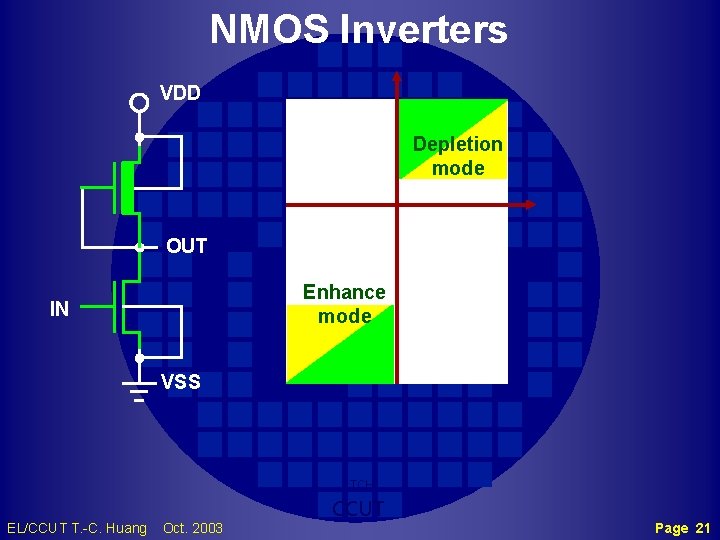

NMOS Inverters VDD Depletion mode OUT Enhance mode IN VSS TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 21

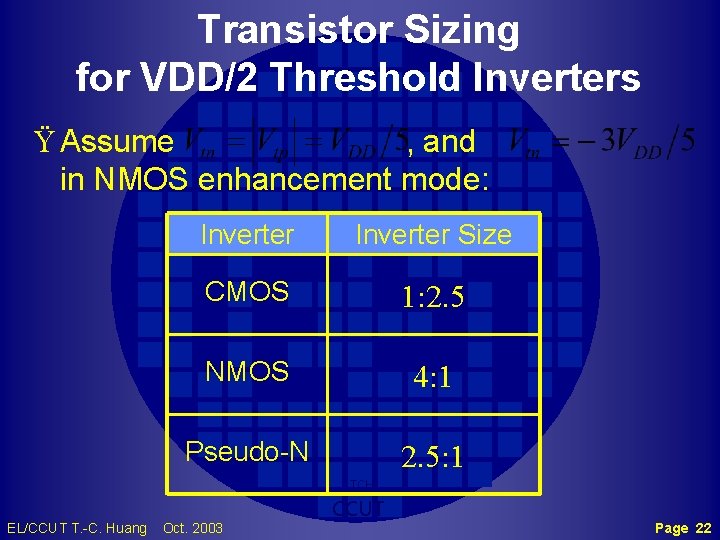

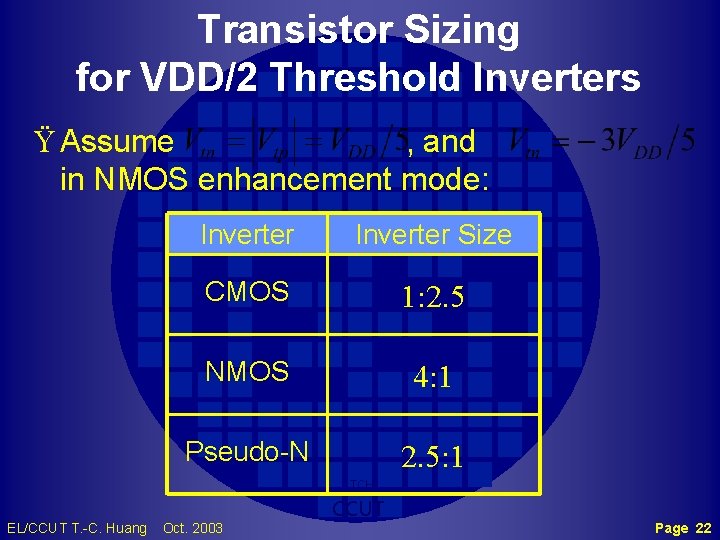

Transistor Sizing for VDD/2 Threshold Inverters Ÿ Assume , and in NMOS enhancement mode: Inverter Size CMOS 1: 2. 5 NMOS 4: 1 Pseudo-N 2. 5: 1 TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 22

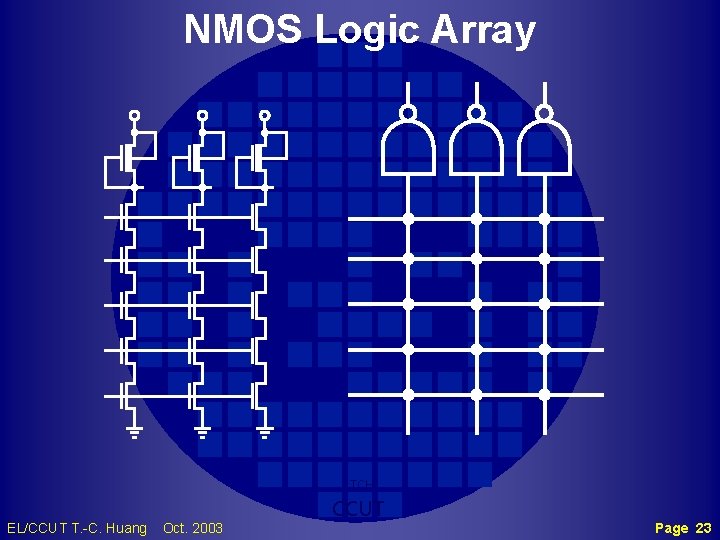

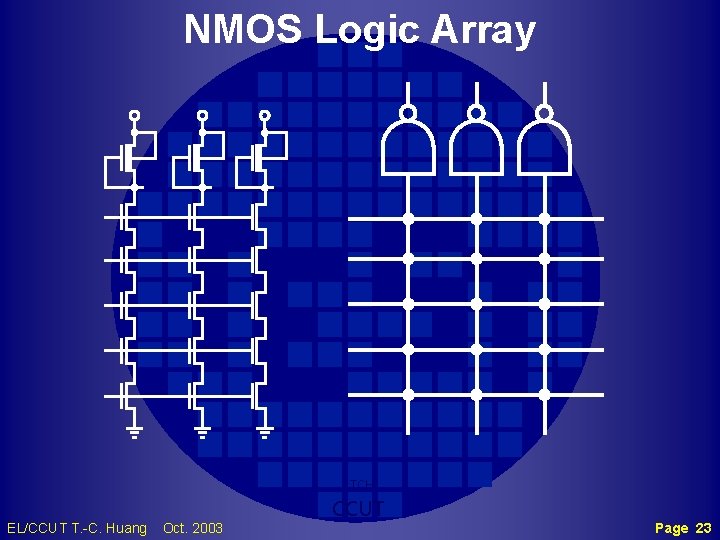

NMOS Logic Array TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 23

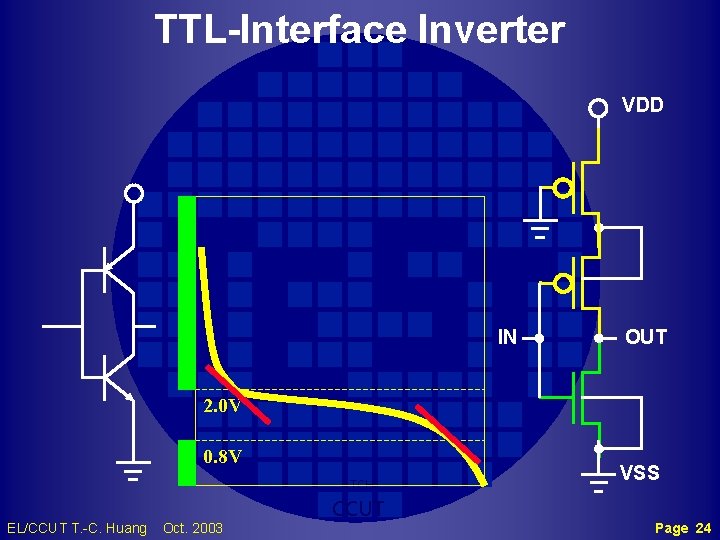

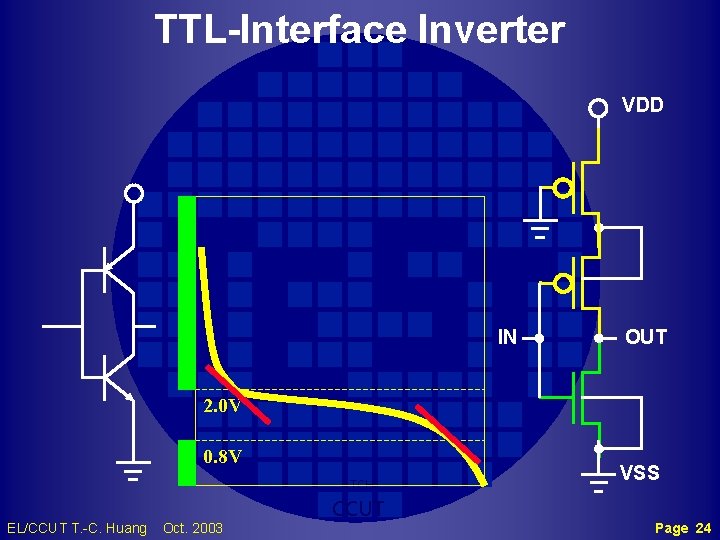

TTL-Interface Inverter VDD IN OUT 2. 0 V 0. 8 V TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT VSS Page 24

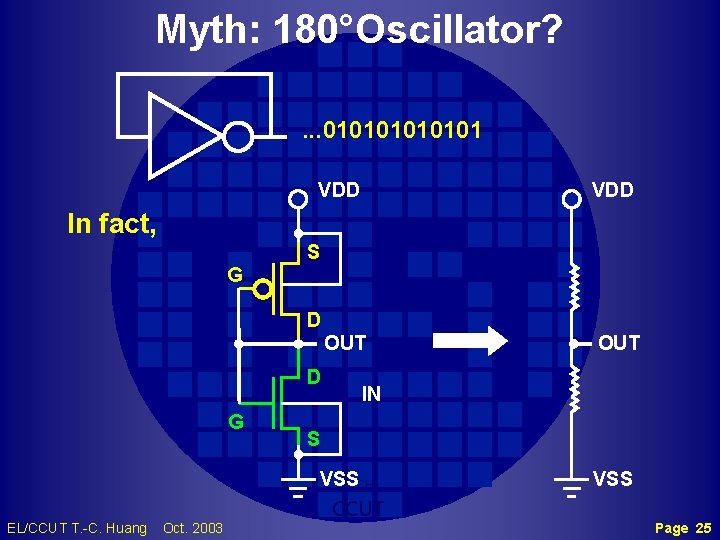

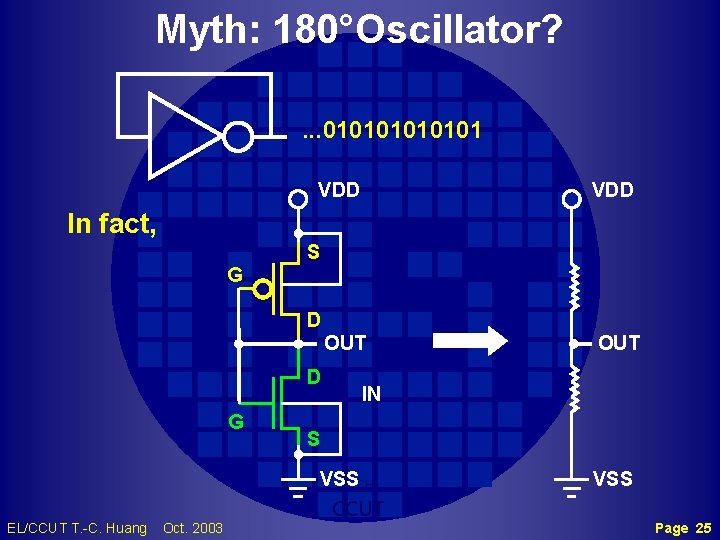

Myth: 180°Oscillator? . . . 010101 VDD In fact, S G D OUT D G IN S VSSTCH EL/CCUT T. -C. Huang Oct. 2003 OUT CCUT VSS Page 25

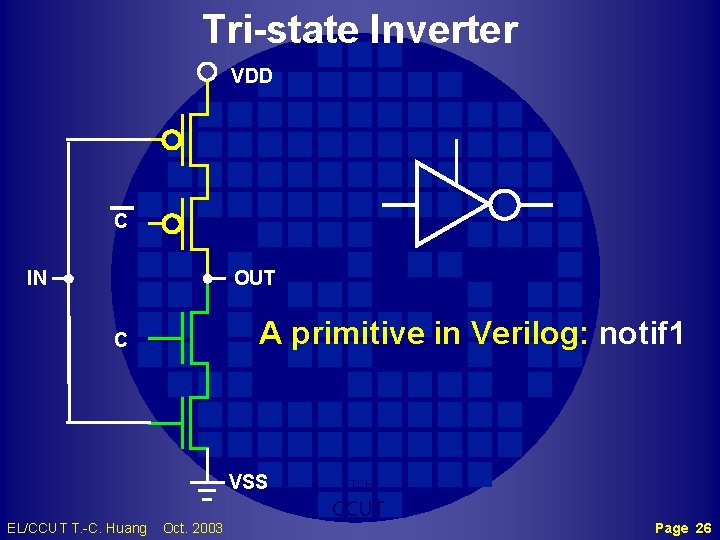

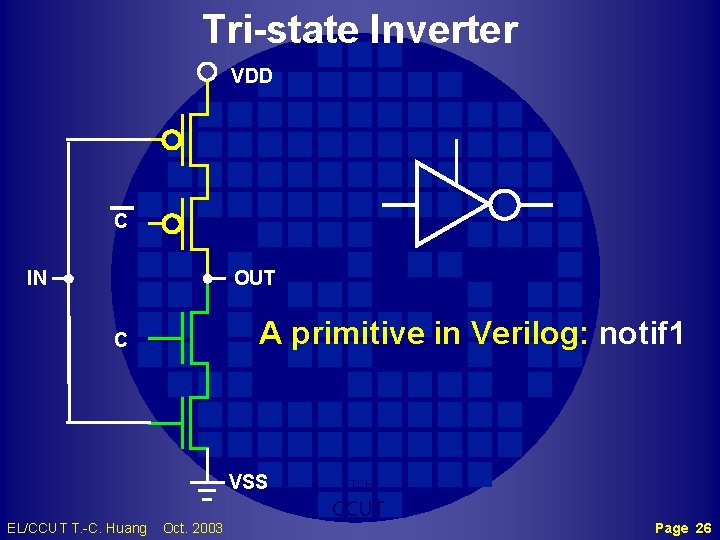

Tri-state Inverter VDD C IN OUT A primitive in Verilog: notif 1 C VSS EL/CCUT T. -C. Huang Oct. 2003 TCH CCUT Page 26

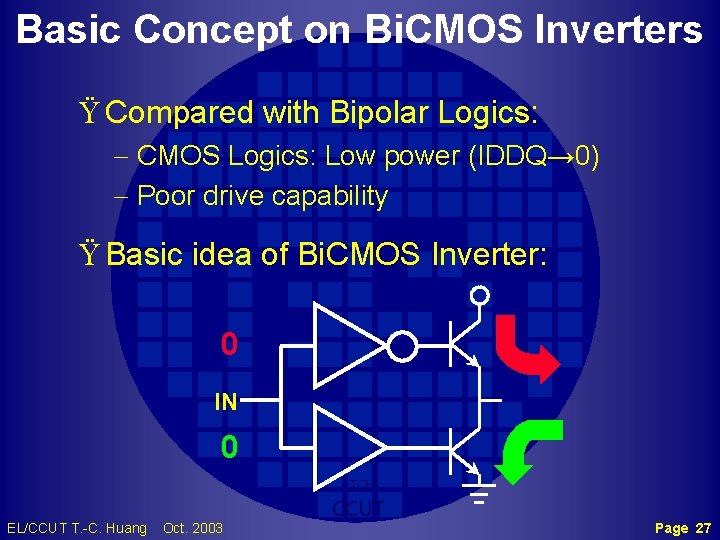

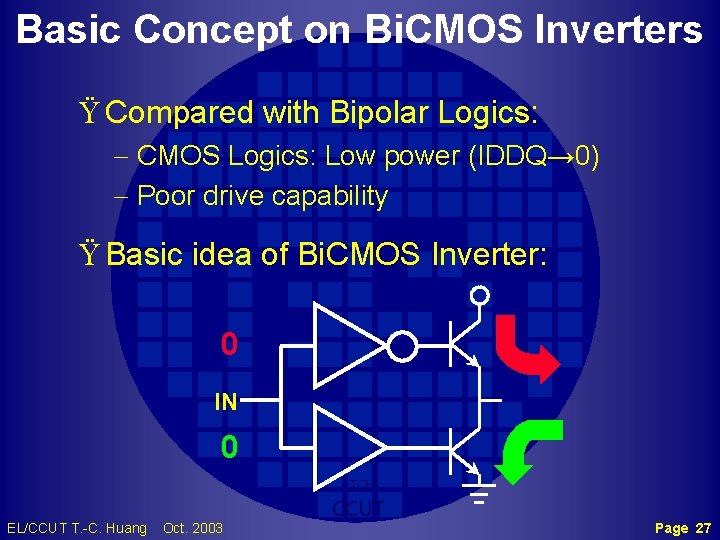

Basic Concept on Bi. CMOS Inverters Ÿ Compared with Bipolar Logics: - CMOS Logics: Low power (IDDQ→ 0) - Poor drive capability Ÿ Basic idea of Bi. CMOS Inverter: 0 IN 0 TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 27

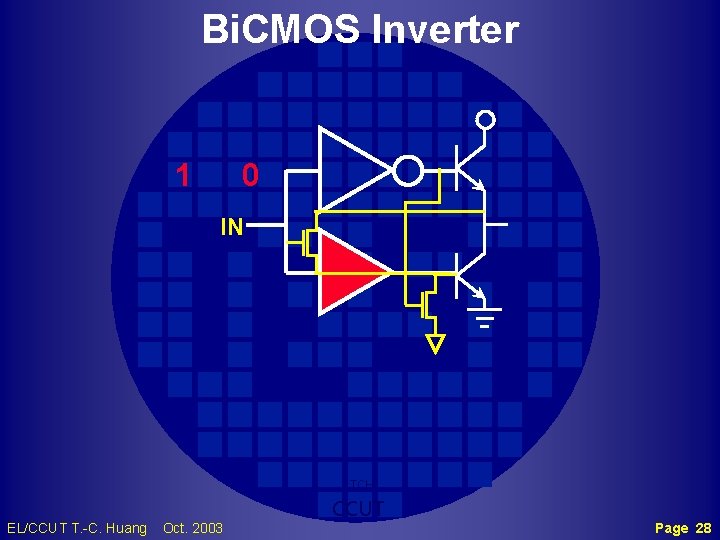

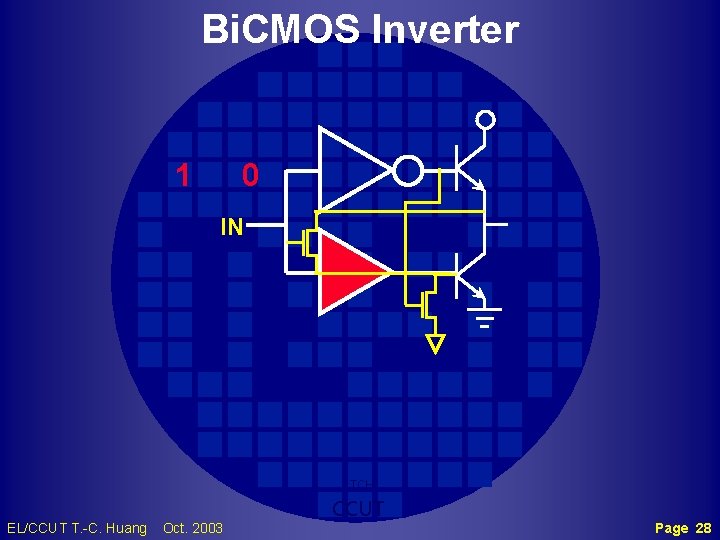

Bi. CMOS Inverter 1 0 IN TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 28

Transistor Sizing & Reordering Ÿ Minimizing Area Ÿ Maximizing/Equalizing Noise Margin Ÿ Minimizing/Equalizing Rising & Falling Time Ÿ Minimizing Propagation Time Ÿ Minimizing Power Dissipation Ÿ Reducing Glich Ÿ Minimizing Charge Sharing Effect Ÿ Increasing Regularity for EDA TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 29

Roughly Area Estimation Ÿ In several synthesis tools (2000): An N-input CMOS Primitive Cell: (0. 5+0. 5 N) units (compared to a unit inverter) Ÿ Dependent on Layout Style TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 30

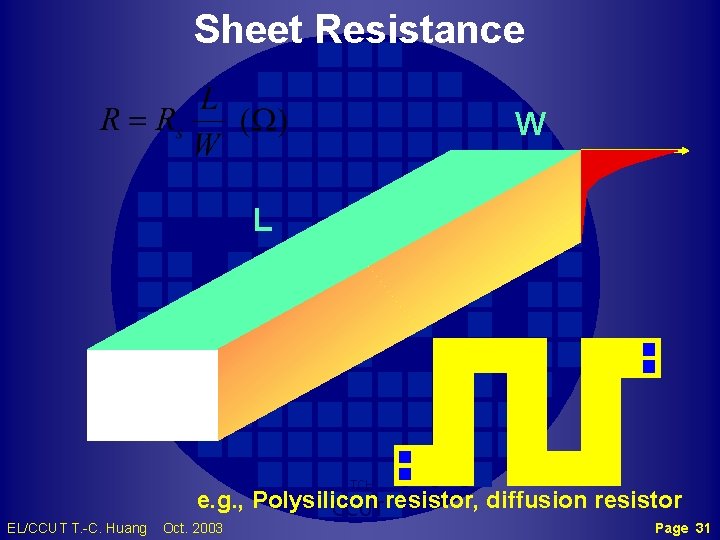

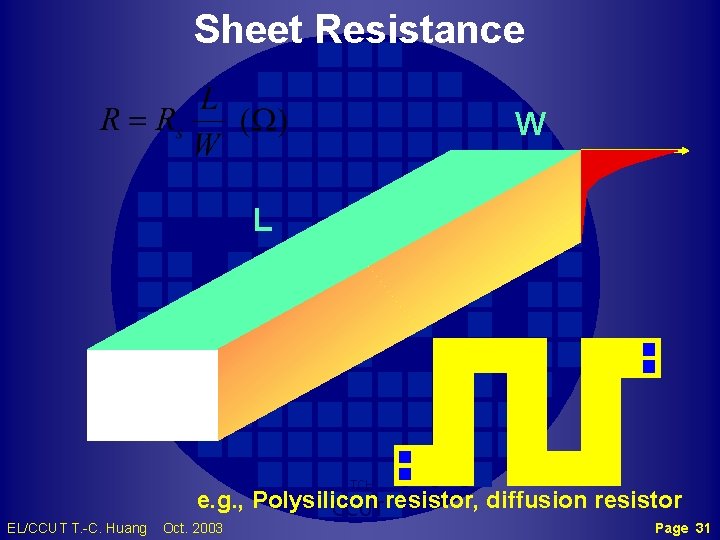

Sheet Resistance W L TCH EL/CCUT T. -C. Huang e. g. , Polysilicon CCUTresistor, diffusion resistor Oct. 2003 Page 31

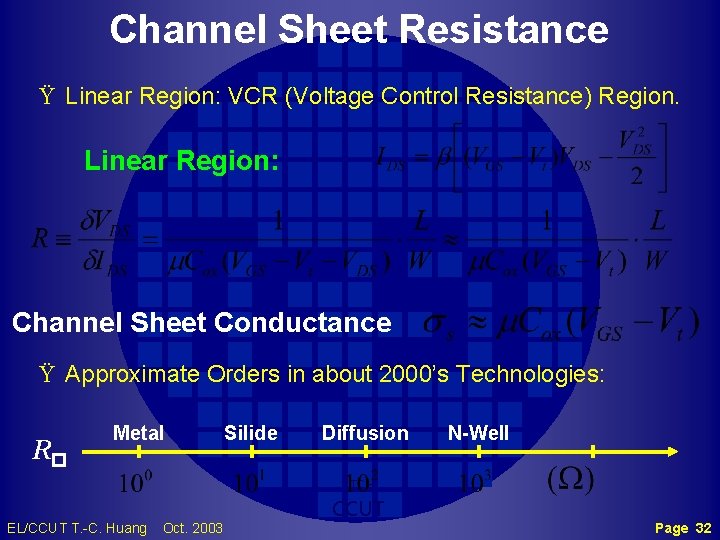

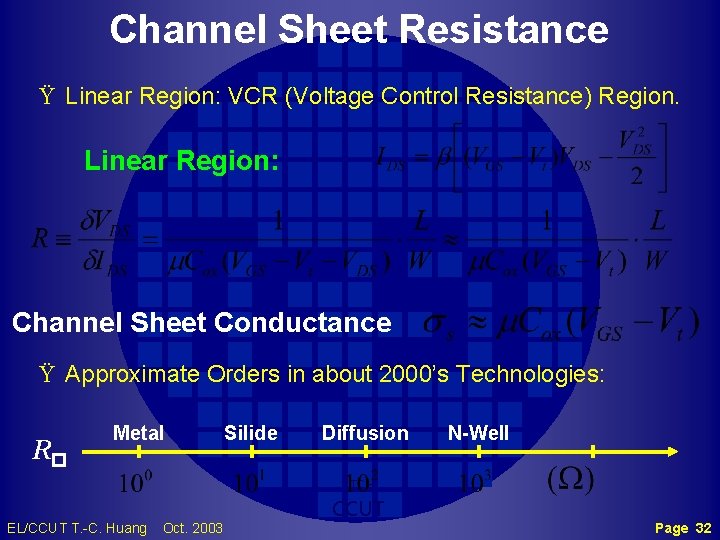

Channel Sheet Resistance Ÿ Linear Region: VCR (Voltage Control Resistance) Region. Linear Region: Channel Sheet Conductance Ÿ Approximate Orders in about 2000’s Technologies: R Metal Silide Diffusion N-Well TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 32

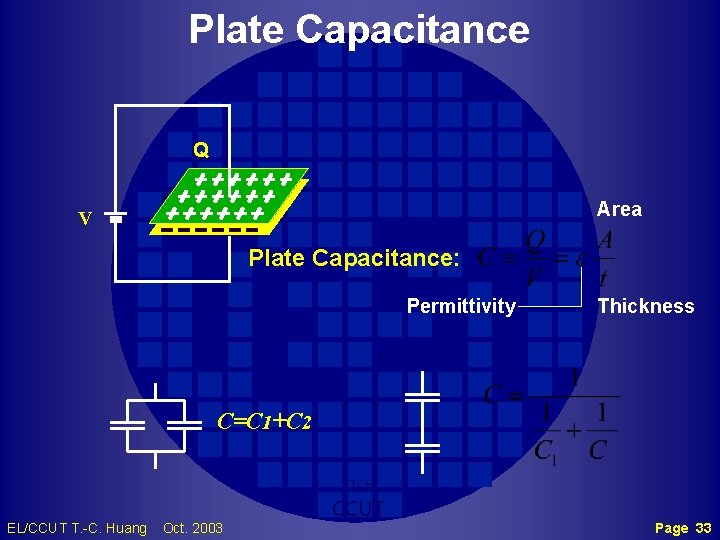

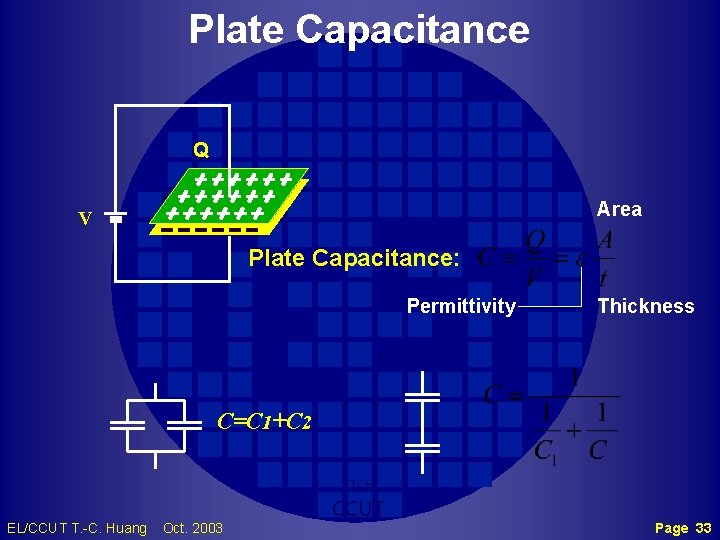

Plate Capacitance Q Area V Plate Capacitance: Permittivity Thickness C=C 1+C 2 TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 33

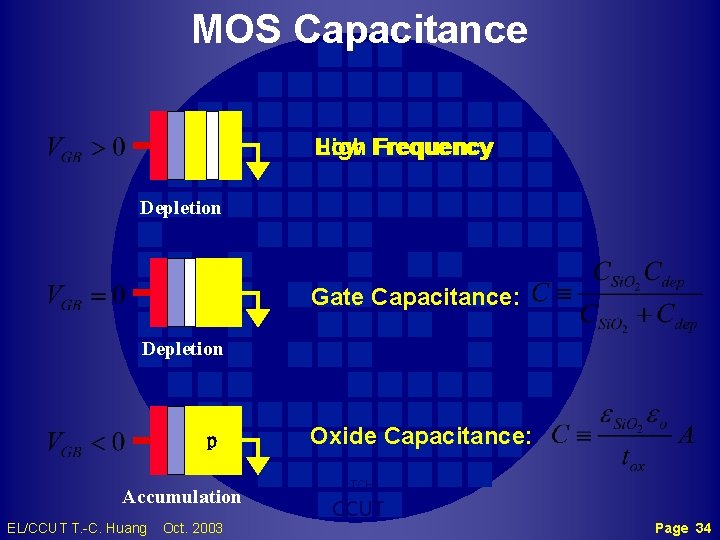

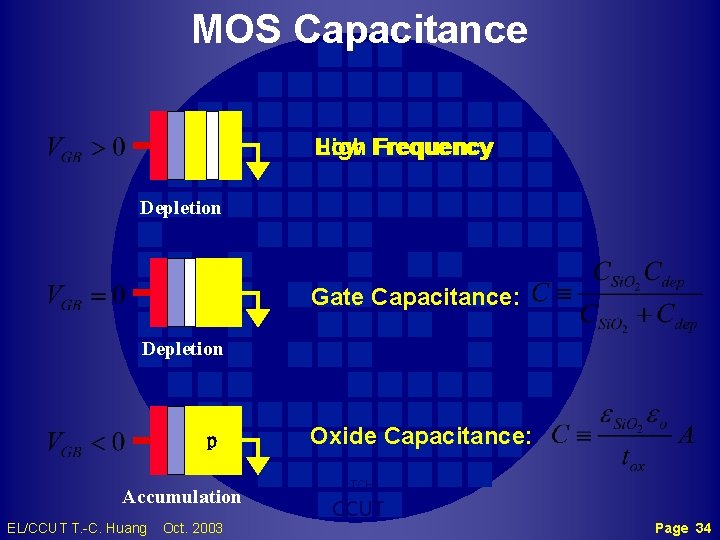

MOS Capacitance High Low Frequency Depletion Gate Capacitance: Depletion p Accumulation EL/CCUT T. -C. Huang Oct. 2003 Oxide Capacitance: TCH CCUT Page 34

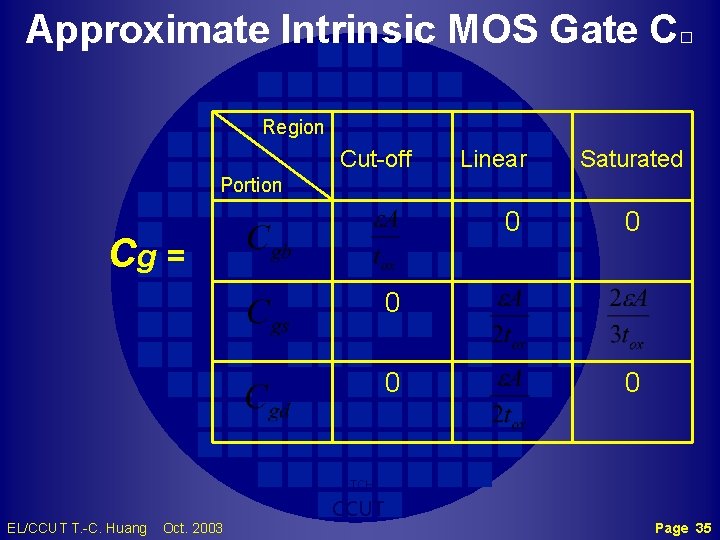

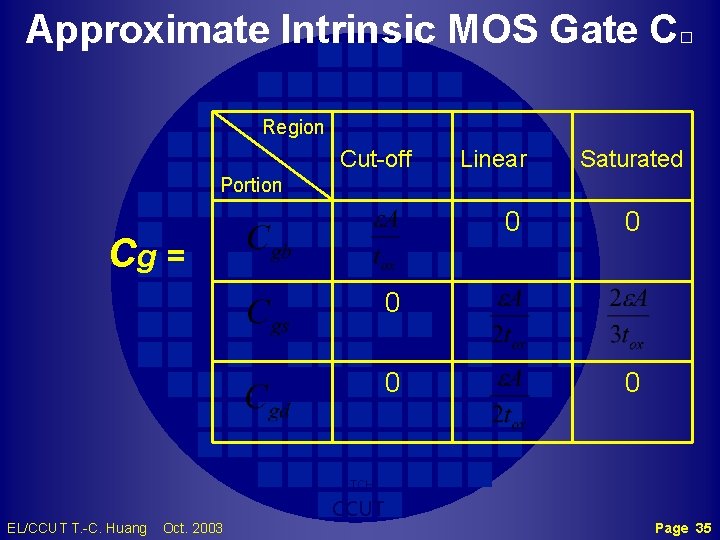

Approximate Intrinsic MOS Gate C□ Region Cut-off Linear Saturated Portion 0 Cg = 0 0 TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 35

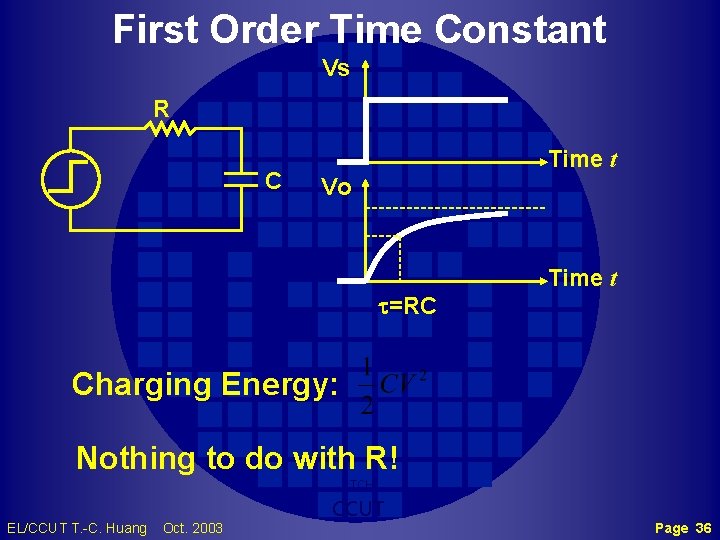

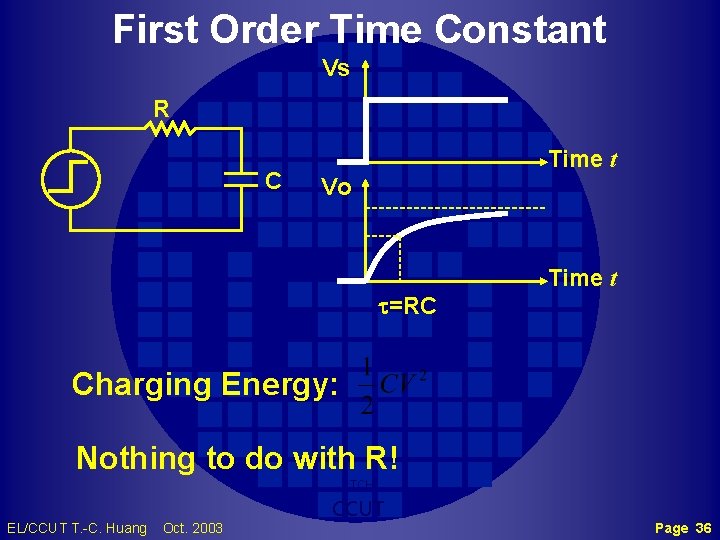

First Order Time Constant Vs R C Time t Vo t=RC Time t Charging Energy: Nothing to do with R! TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 36

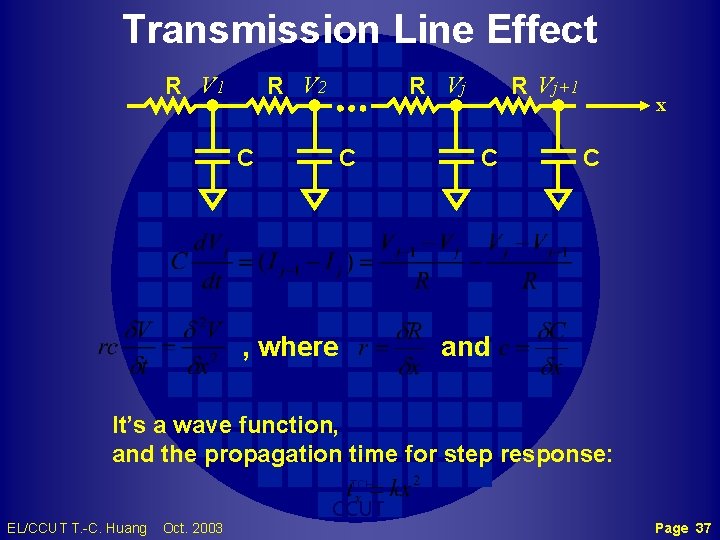

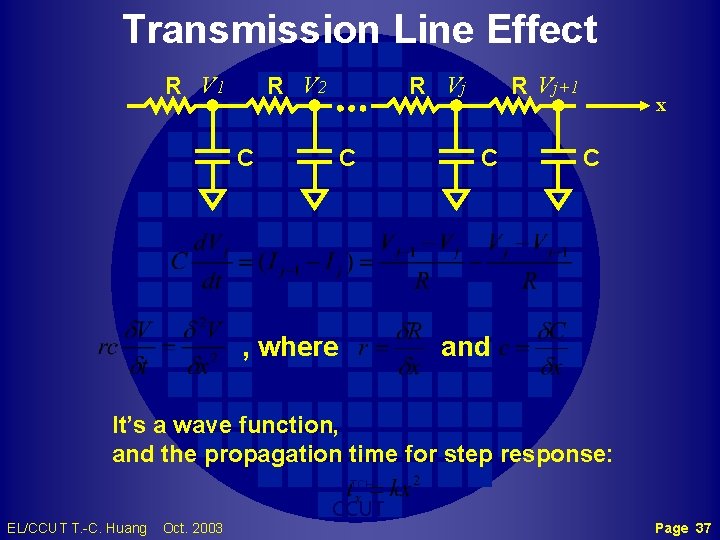

Transmission Line Effect R V 1 R V 2 R Vj C C , where R Vj+1 C x C and It’s a wave function, and the propagation time for step response: TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 37

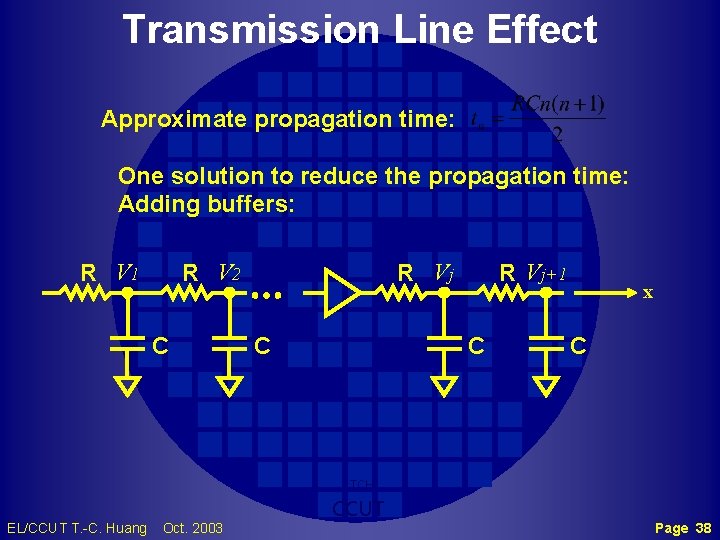

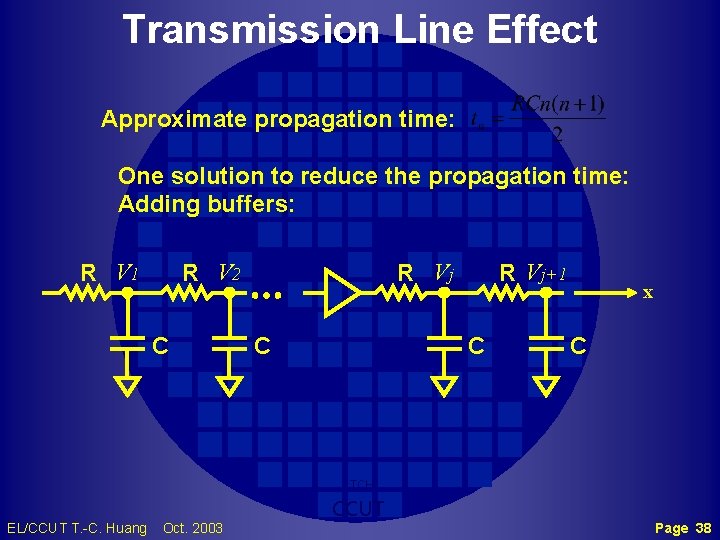

Transmission Line Effect Approximate propagation time: One solution to reduce the propagation time: Adding buffers: R V 1 R V 2 C R Vj+1 C x C TCH EL/CCUT T. -C. Huang Oct. 2003 CCUT Page 38