Introduction to Electronic Design Automation CADET Week 1

![A dense placement good wirelength impossible to route [Rohe] 17 A dense placement good wirelength impossible to route [Rohe] 17](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-17.jpg)

![Possible solution easy to route bad wirelength/timing [Rohe] 18 Possible solution easy to route bad wirelength/timing [Rohe] 18](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-18.jpg)

![Placement step 0 [Rohe] 20 Placement step 0 [Rohe] 20](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-20.jpg)

![Placement step 1 [Rohe] 21 Placement step 1 [Rohe] 21](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-21.jpg)

![Placement step 2 [Rohe] 22 Placement step 2 [Rohe] 22](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-22.jpg)

![Placement step 3 [Rohe] 23 Placement step 3 [Rohe] 23](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-23.jpg)

![Placement step 4 [Rohe] 24 Placement step 4 [Rohe] 24](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-24.jpg)

![Placement step 5 [Rohe] 25 Placement step 5 [Rohe] 25](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-25.jpg)

![Placement step 6 [Rohe] 26 Placement step 6 [Rohe] 26](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-26.jpg)

![Placement step 7 [Rohe] 27 Placement step 7 [Rohe] 27](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-27.jpg)

![Partitioning-based placement • More problems: – Direction of the cut? [Yildiz, DAC’ 01] 1 Partitioning-based placement • More problems: – Direction of the cut? [Yildiz, DAC’ 01] 1](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-34.jpg)

![Representative approaches • Constructive methods – Network flow [K. Doll et al, TCAD’ 94] Representative approaches • Constructive methods – Network flow [K. Doll et al, TCAD’ 94]](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-38.jpg)

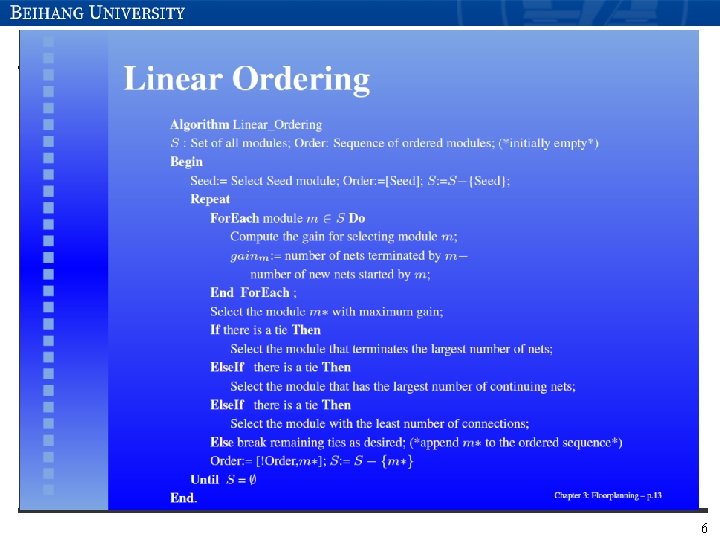

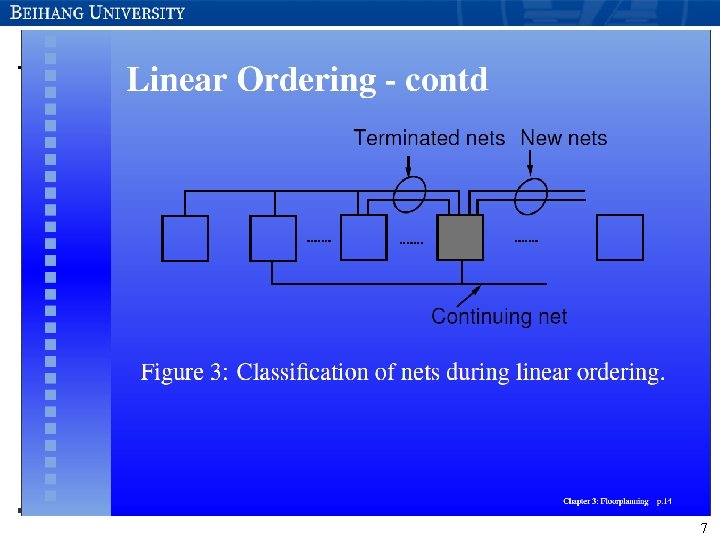

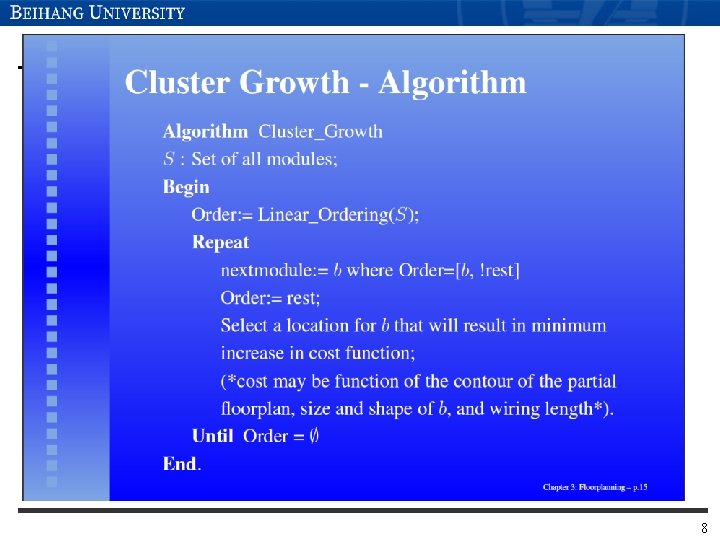

- Slides: 43

Introduction to Electronic Design Automation 北京航空航天大学微电子学院 CADET实验室 成元庆 主讲

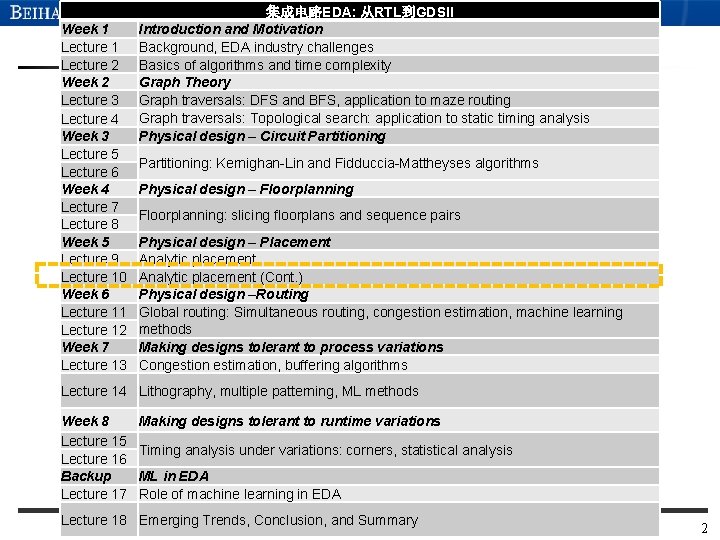

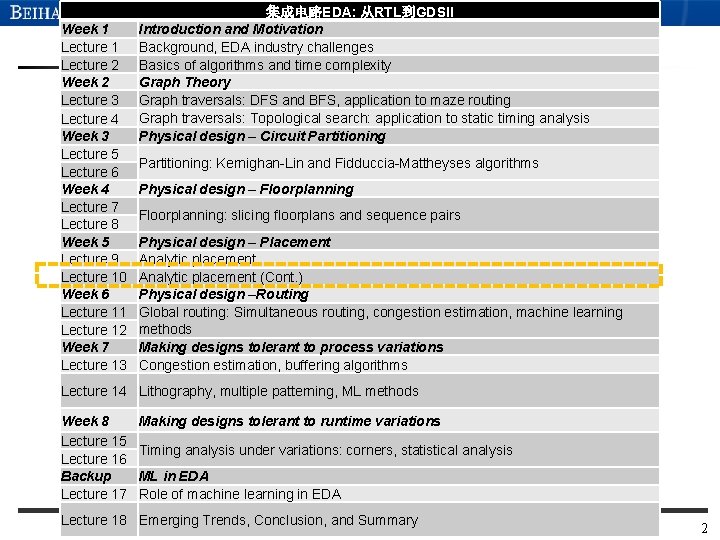

Week 1 Lecture 2 Week 2 Lecture 3 Lecture 4 Week 3 Lecture 5 Lecture 6 Week 4 Lecture 7 Lecture 8 Week 5 Lecture 9 Lecture 10 Week 6 Lecture 11 Lecture 12 Week 7 Lecture 13 集成电路EDA: 从RTL到GDSII Introduction and Motivation Background, EDA industry challenges Basics of algorithms and time complexity Graph Theory Graph traversals: DFS and BFS, application to maze routing Graph traversals: Topological search: application to static timing analysis Physical design – Circuit Partitioning: Kernighan-Lin and Fidduccia-Mattheyses algorithms Physical design – Floorplanning: slicing floorplans and sequence pairs Physical design – Placement Analytic placement (Cont. ) Physical design –Routing Global routing: Simultaneous routing, congestion estimation, machine learning methods Making designs tolerant to process variations Congestion estimation, buffering algorithms Lecture 14 Lithography, multiple patterning, ML methods Week 8 Lecture 15 Lecture 16 Backup Lecture 17 Making designs tolerant to runtime variations Timing analysis under variations: corners, statistical analysis ML in EDA Role of machine learning in EDA Lecture 18 Emerging Trends, Conclusion, and Summary 2

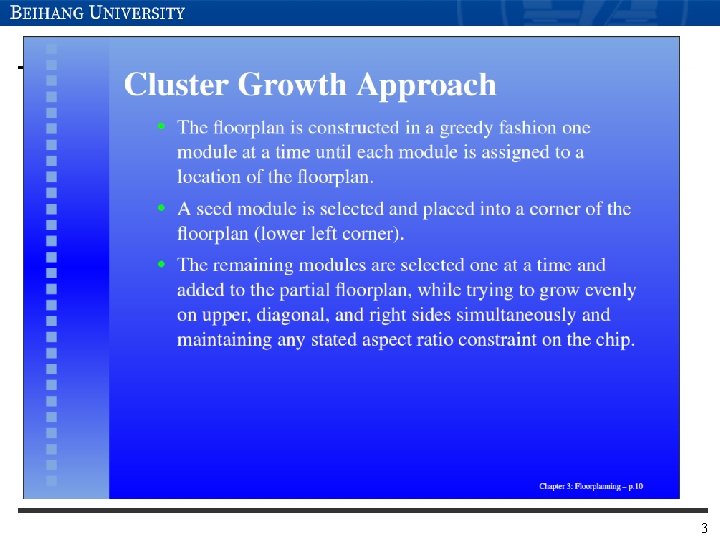

3

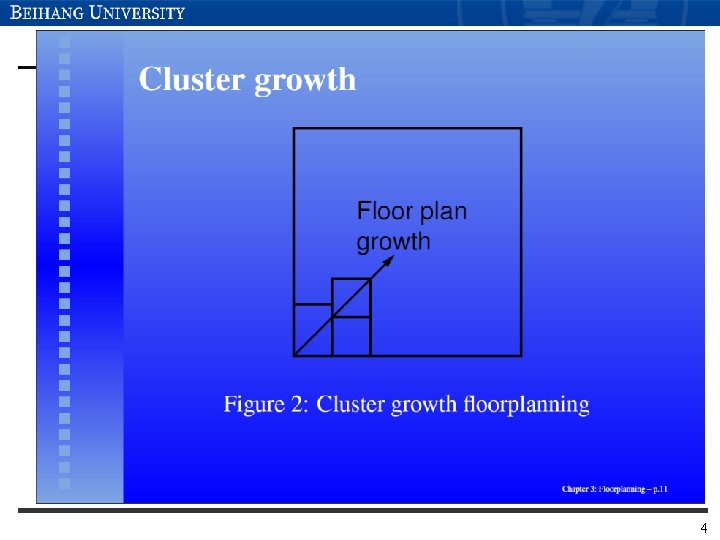

4

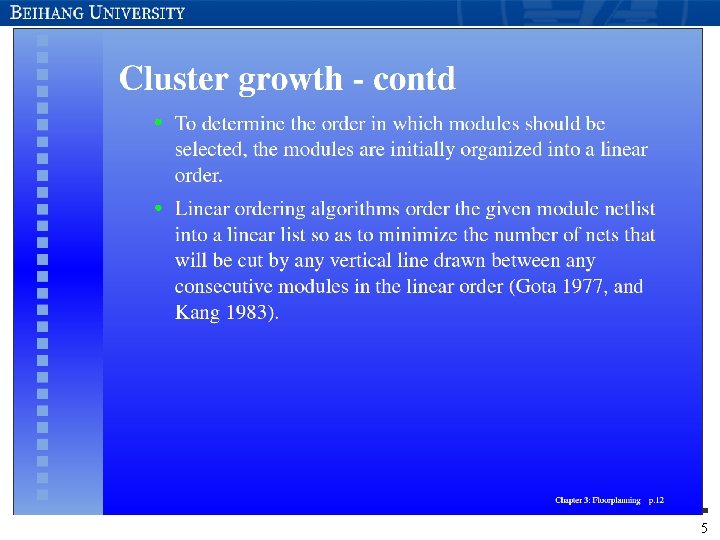

5

6

7

8

Placement II

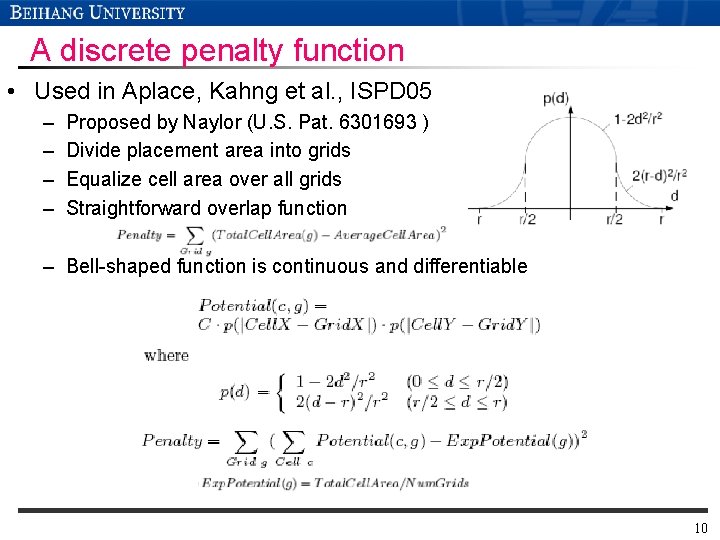

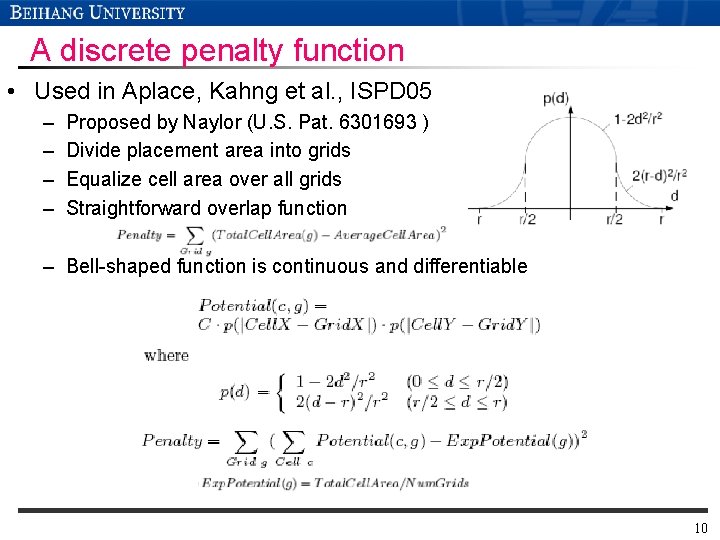

A discrete penalty function • Used in Aplace, Kahng et al. , ISPD 05 – – Proposed by Naylor (U. S. Pat. 6301693 ) Divide placement area into grids Equalize cell area over all grids Straightforward overlap function – Bell-shaped function is continuous and differentiable 10

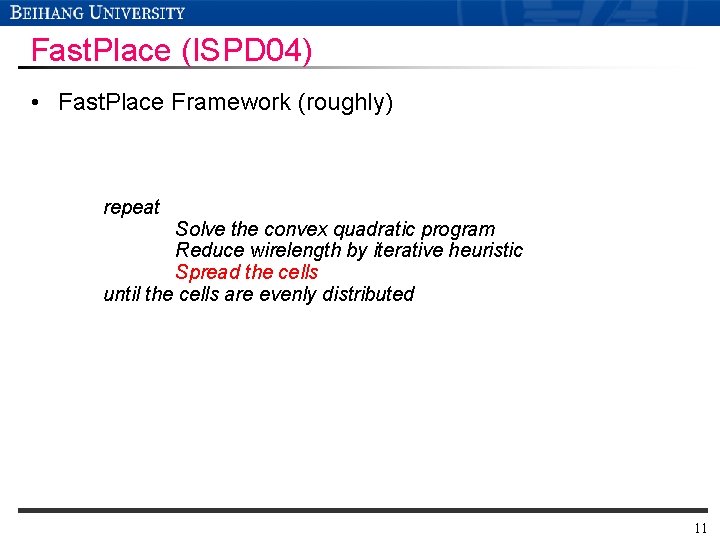

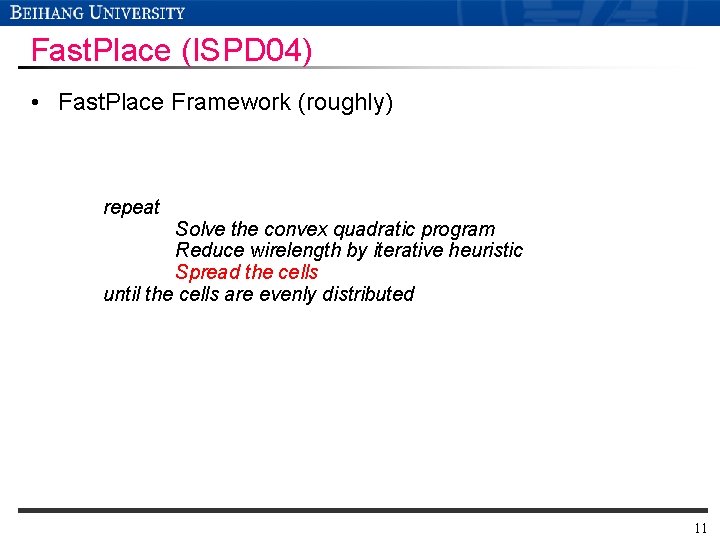

Fast. Place (ISPD 04) • Fast. Place Framework (roughly) repeat Solve the convex quadratic program Reduce wirelength by iterative heuristic Spread the cells until the cells are evenly distributed 11

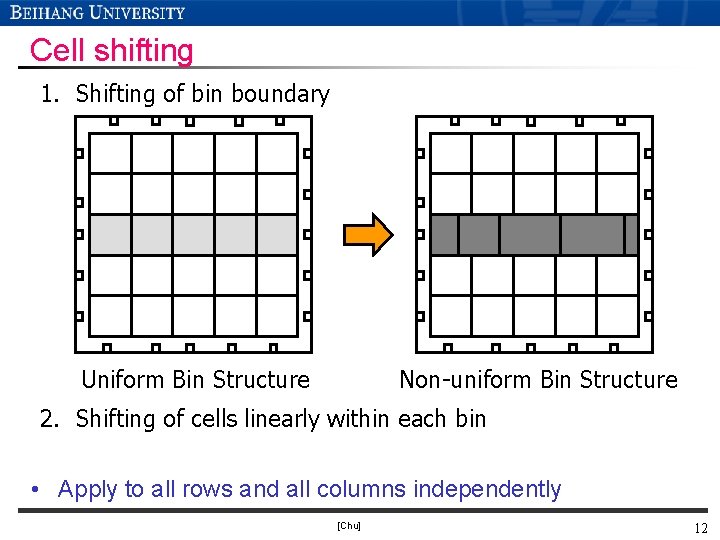

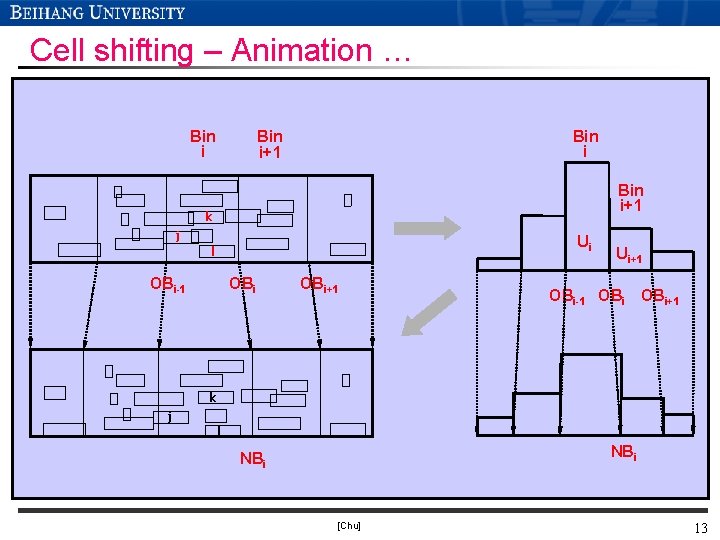

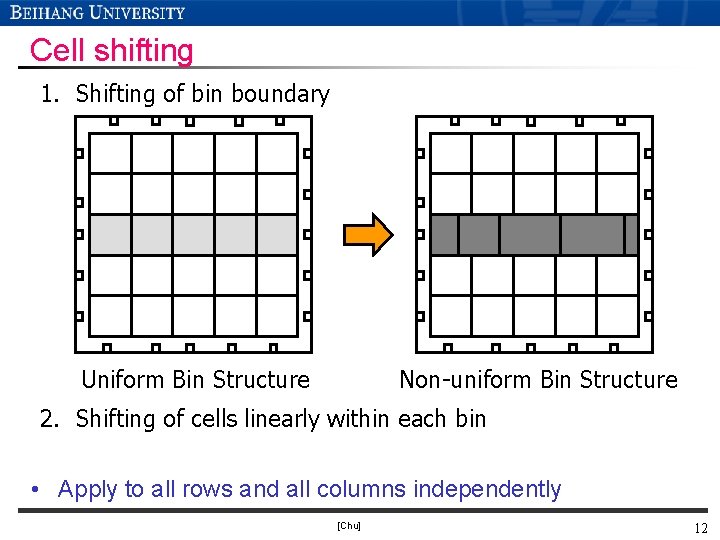

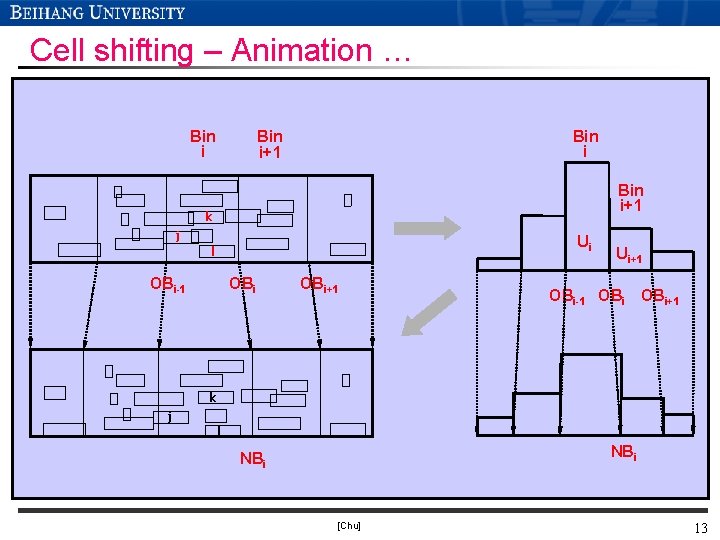

Cell shifting 1. Shifting of bin boundary Uniform Bin Structure Non-uniform Bin Structure 2. Shifting of cells linearly within each bin • Apply to all rows and all columns independently [Chu] 12

Cell shifting – Animation … Bin i+1 k j Ui l OBi-1 OBi+1 Ui+1 OBi-1 OBi+1 k j l NBi [Chu] 13

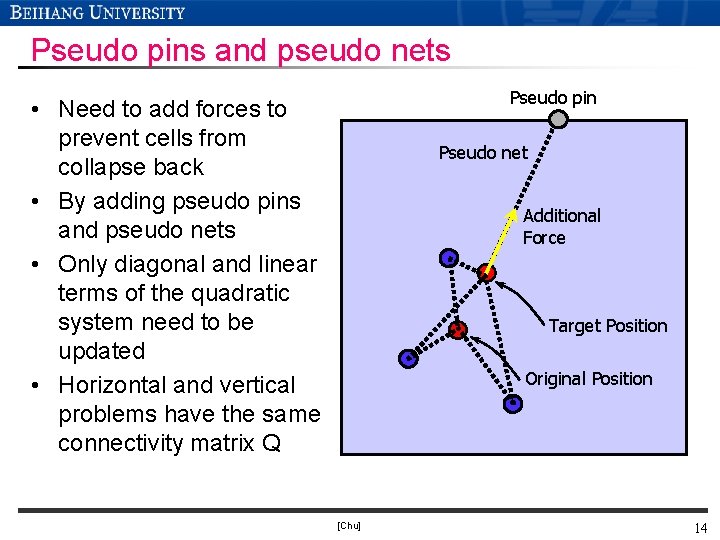

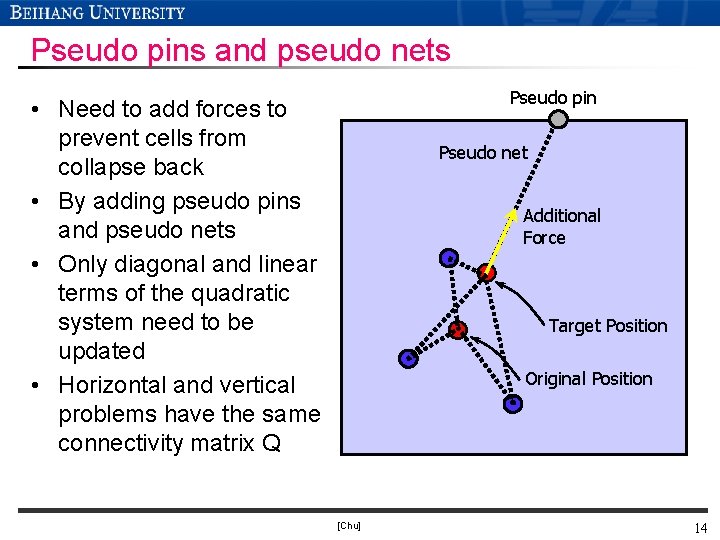

Pseudo pins and pseudo nets Pseudo pin • Need to add forces to prevent cells from collapse back • By adding pseudo pins and pseudo nets • Only diagonal and linear terms of the quadratic system need to be updated • Horizontal and vertical problems have the same connectivity matrix Q Pseudo net Additional Force Target Position Original Position [Chu] 14

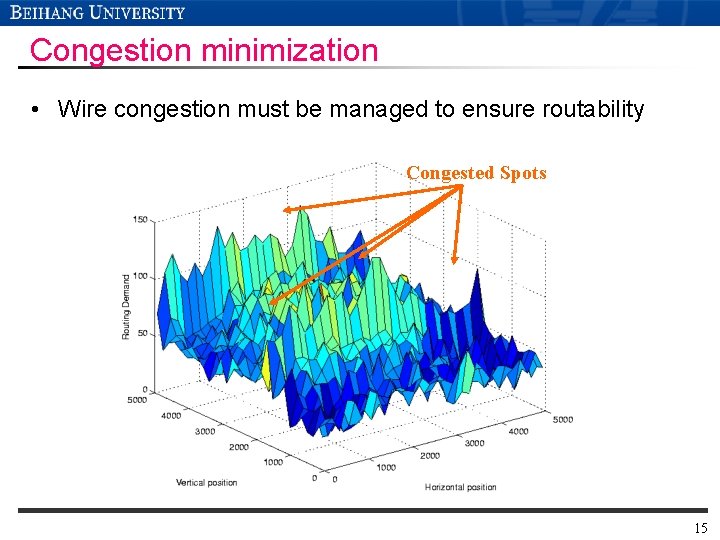

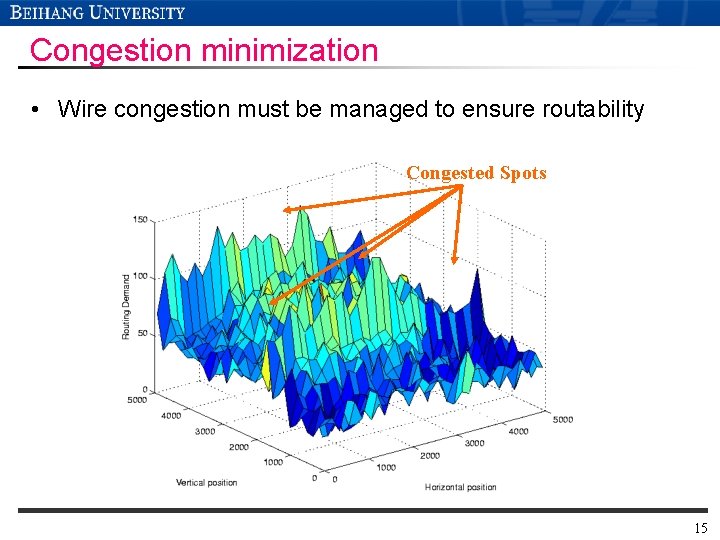

Congestion minimization • Wire congestion must be managed to ensure routability Congested Spots 15

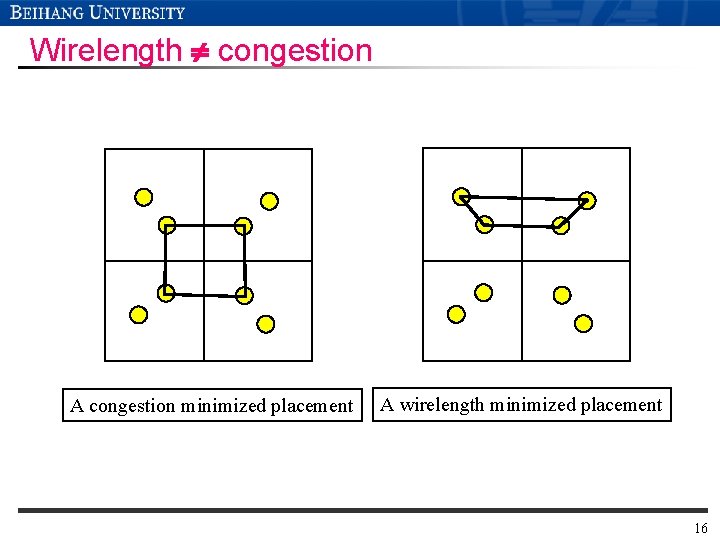

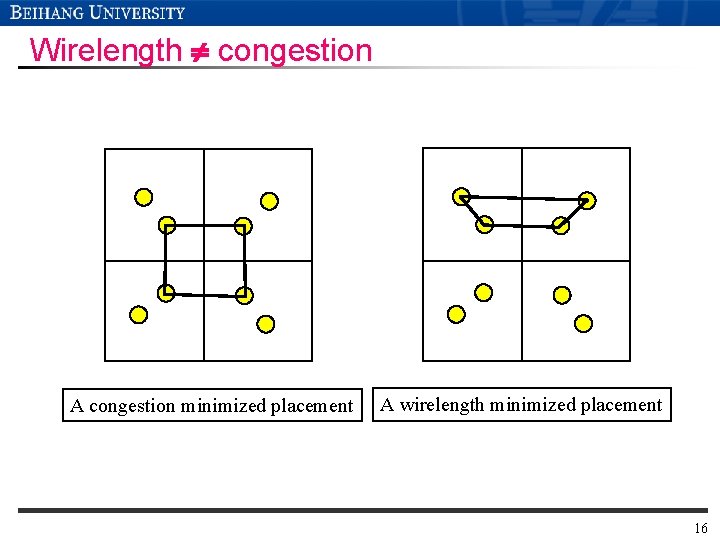

Wirelength congestion A congestion minimized placement A wirelength minimized placement 16

![A dense placement good wirelength impossible to route Rohe 17 A dense placement good wirelength impossible to route [Rohe] 17](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-17.jpg)

A dense placement good wirelength impossible to route [Rohe] 17

![Possible solution easy to route bad wirelengthtiming Rohe 18 Possible solution easy to route bad wirelength/timing [Rohe] 18](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-18.jpg)

Possible solution easy to route bad wirelength/timing [Rohe] 18

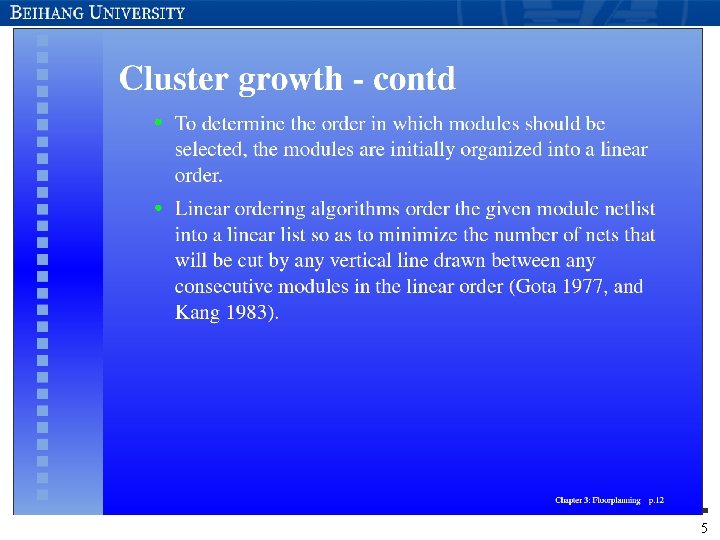

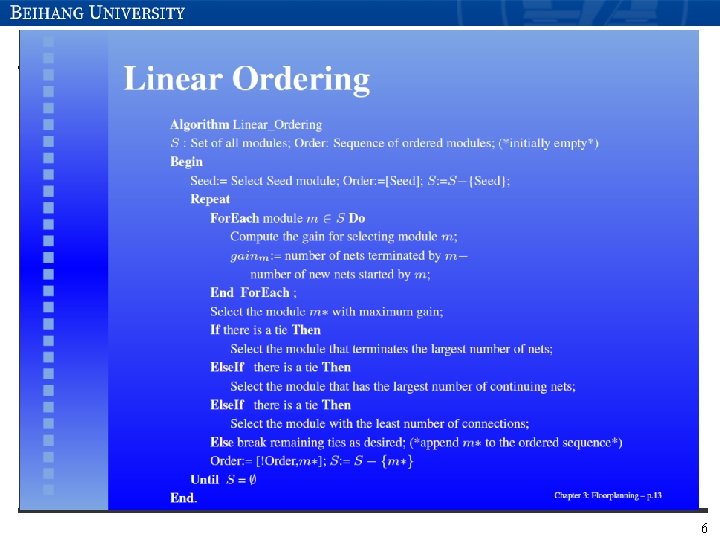

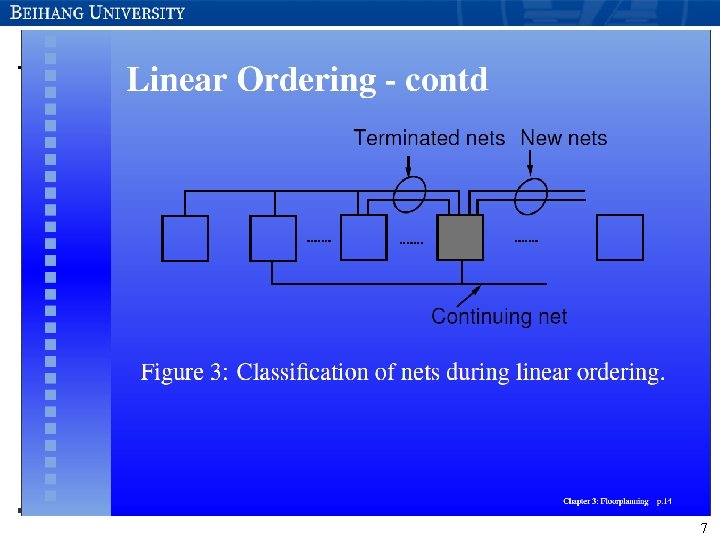

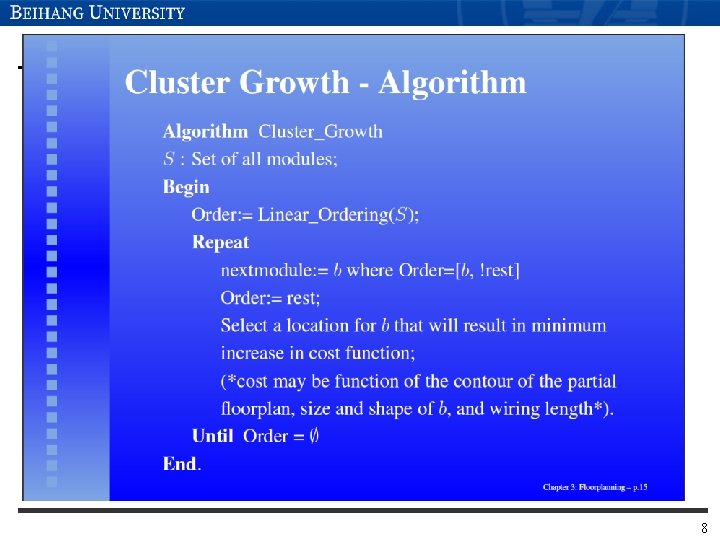

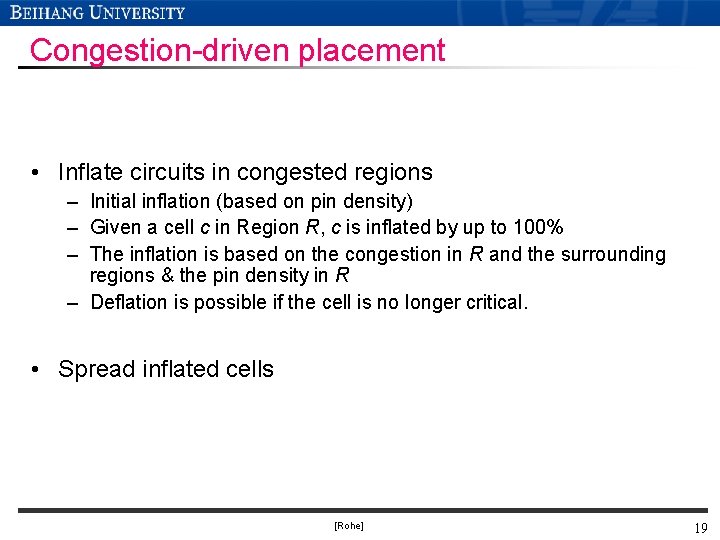

Congestion-driven placement • Inflate circuits in congested regions – Initial inflation (based on pin density) – Given a cell c in Region R, c is inflated by up to 100% – The inflation is based on the congestion in R and the surrounding regions & the pin density in R – Deflation is possible if the cell is no longer critical. • Spread inflated cells [Rohe] 19

![Placement step 0 Rohe 20 Placement step 0 [Rohe] 20](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-20.jpg)

Placement step 0 [Rohe] 20

![Placement step 1 Rohe 21 Placement step 1 [Rohe] 21](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-21.jpg)

Placement step 1 [Rohe] 21

![Placement step 2 Rohe 22 Placement step 2 [Rohe] 22](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-22.jpg)

Placement step 2 [Rohe] 22

![Placement step 3 Rohe 23 Placement step 3 [Rohe] 23](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-23.jpg)

Placement step 3 [Rohe] 23

![Placement step 4 Rohe 24 Placement step 4 [Rohe] 24](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-24.jpg)

Placement step 4 [Rohe] 24

![Placement step 5 Rohe 25 Placement step 5 [Rohe] 25](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-25.jpg)

Placement step 5 [Rohe] 25

![Placement step 6 Rohe 26 Placement step 6 [Rohe] 26](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-26.jpg)

Placement step 6 [Rohe] 26

![Placement step 7 Rohe 27 Placement step 7 [Rohe] 27](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-27.jpg)

Placement step 7 [Rohe] 27

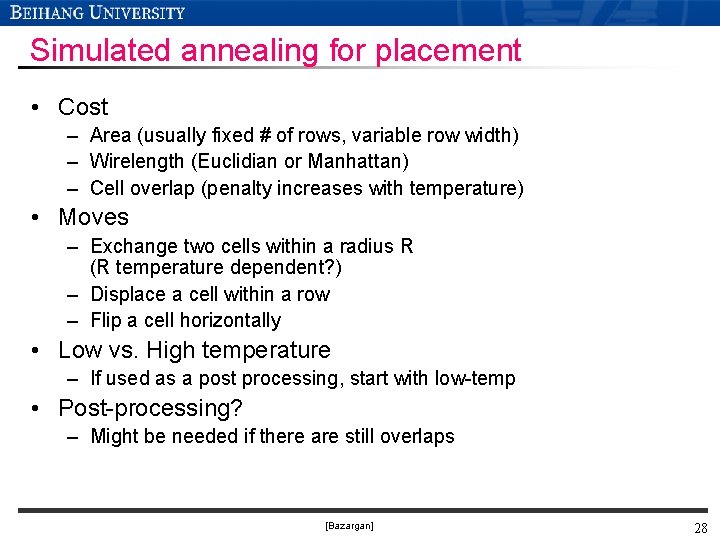

Simulated annealing for placement • Cost – Area (usually fixed # of rows, variable row width) – Wirelength (Euclidian or Manhattan) – Cell overlap (penalty increases with temperature) • Moves – Exchange two cells within a radius R (R temperature dependent? ) – Displace a cell within a row – Flip a cell horizontally • Low vs. High temperature – If used as a post processing, start with low-temp • Post-processing? – Might be needed if there are still overlaps [Bazargan] 28

Timber. Wolf • • “The Timberwolf Placement and Routing Package”, Sechen, Sangiovanni; IEEE Journal of Solid-State Circuits, vol SC-20, No. 2(1985) 510 -522 “Timber wolf 3. 2: A New Standard Cell Placement and Global Routing Package” Sechen, Sangiovanni, 23 rd DAC, 1986, 432 -439 Timber wolf Stage 1 § Modules are moved between different rows as well as within the same row § Modules overlaps are allowed § When the temperature is reduced below a certain value, stage 2 begins Stage 2 § Remove overlaps § Annealing process continues, but only interchanges adjacent modules within the same row [He] 29

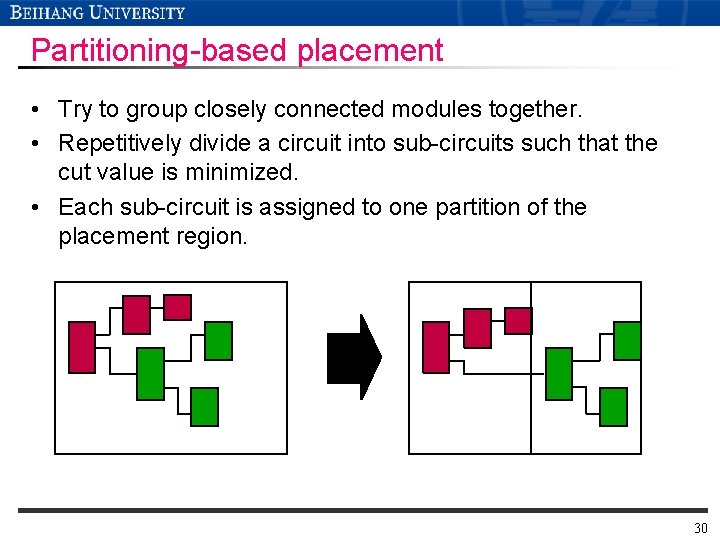

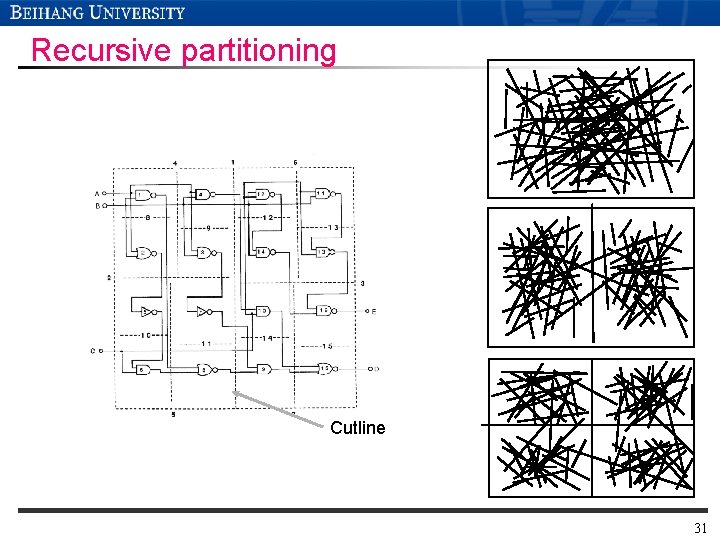

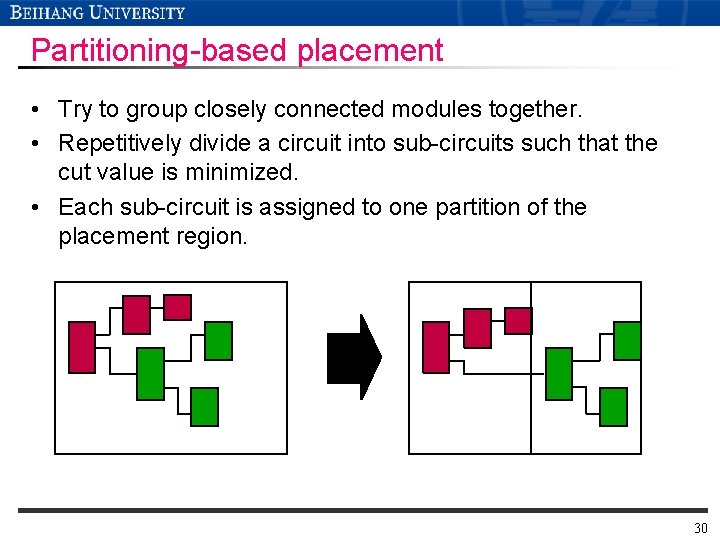

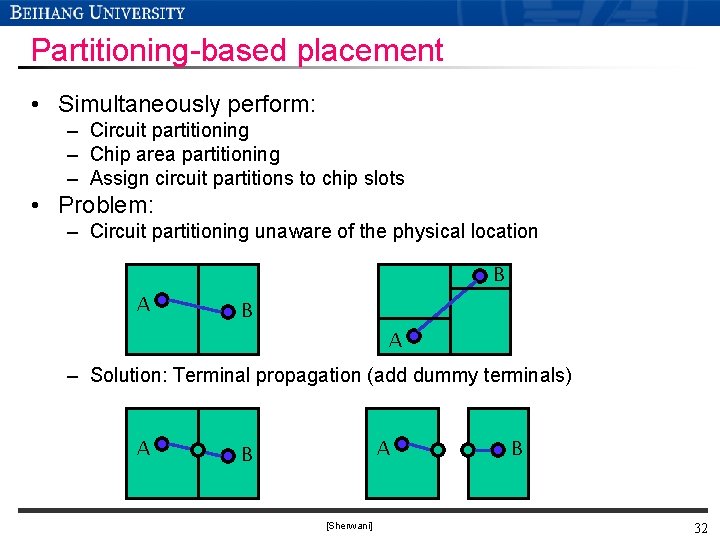

Partitioning-based placement • Try to group closely connected modules together. • Repetitively divide a circuit into sub-circuits such that the cut value is minimized. • Each sub-circuit is assigned to one partition of the placement region. 30

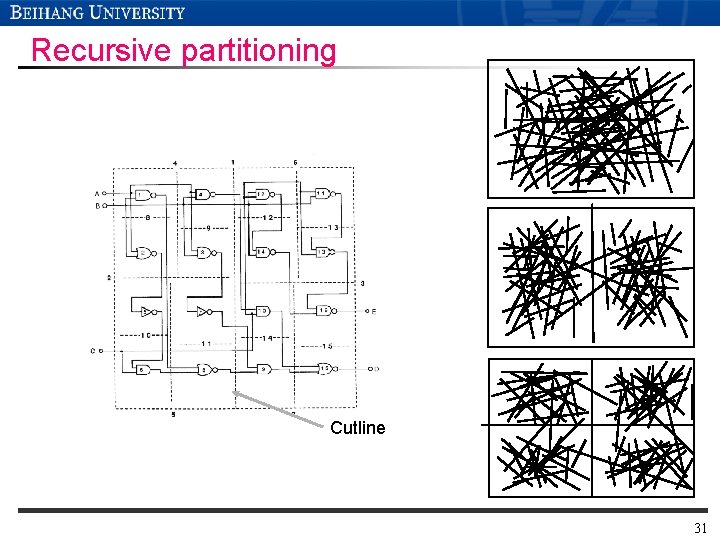

Recursive partitioning Cutline 31

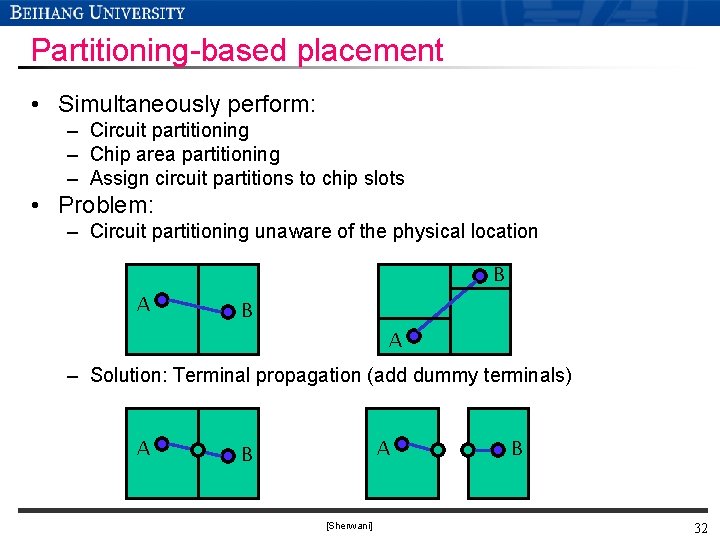

Partitioning-based placement • Simultaneously perform: – Circuit partitioning – Chip area partitioning – Assign circuit partitions to chip slots • Problem: – Circuit partitioning unaware of the physical location A B B A – Solution: Terminal propagation (add dummy terminals) A A B [Sherwani] B 32

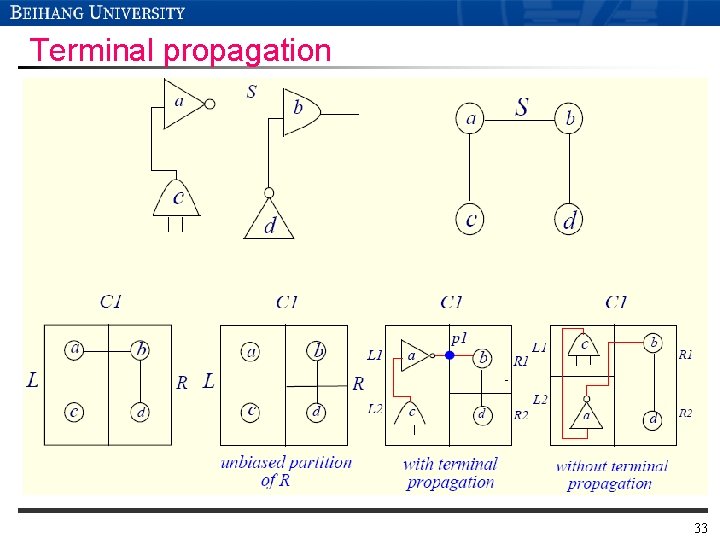

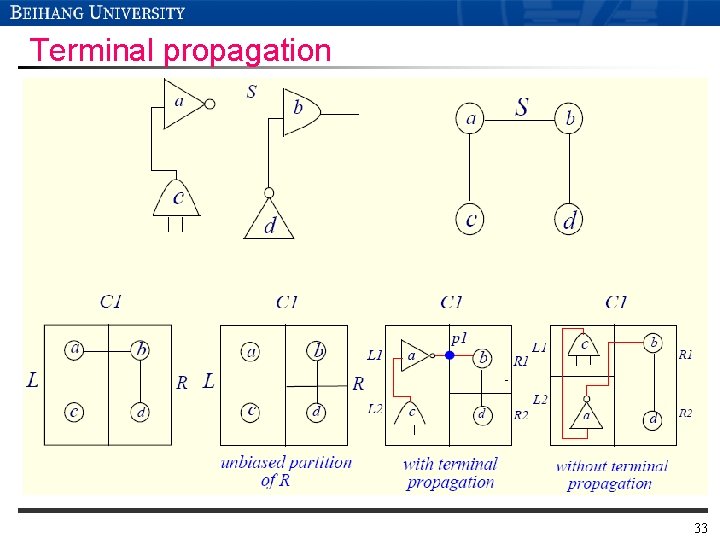

Terminal propagation 33

![Partitioningbased placement More problems Direction of the cut Yildiz DAC 01 1 Partitioning-based placement • More problems: – Direction of the cut? [Yildiz, DAC’ 01] 1](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-34.jpg)

Partitioning-based placement • More problems: – Direction of the cut? [Yildiz, DAC’ 01] 1 2 4 6 3 (a) 5 2 7 4 1 3 5 (b) 5 6 7 8 9 1 2 3 4 (c) 3 (d) – How to handle fixed blocks? (partition area may not be enough) – How to correct a bad decision made at a higher level? • Pros: Fast, scales nearly linearly with problem size • Cons: Not stable (if there is minor change) – Concept of placement stability: if the input netlist experiences a small change, the placement should not change substantially [Bazargan] 34

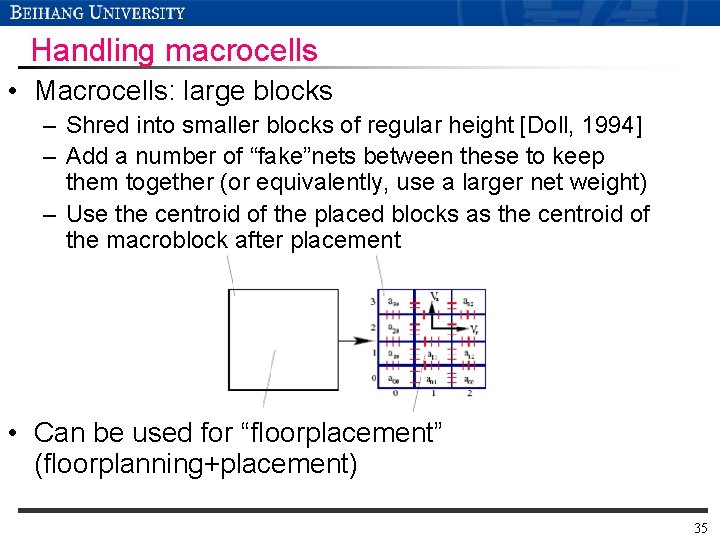

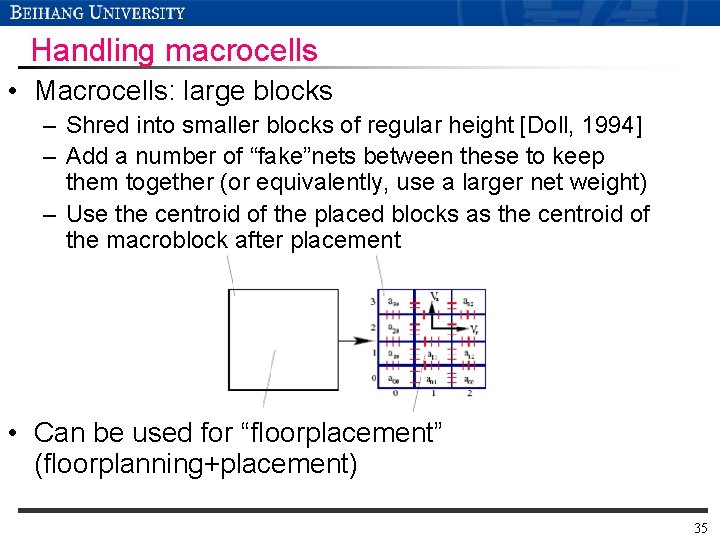

Handling macrocells • Macrocells: large blocks – Shred into smaller blocks of regular height [Doll, 1994] – Add a number of “fake”nets between these to keep them together (or equivalently, use a larger net weight) – Use the centroid of the placed blocks as the centroid of the macroblock after placement • Can be used for “floorplacement” (floorplanning+placement) 35

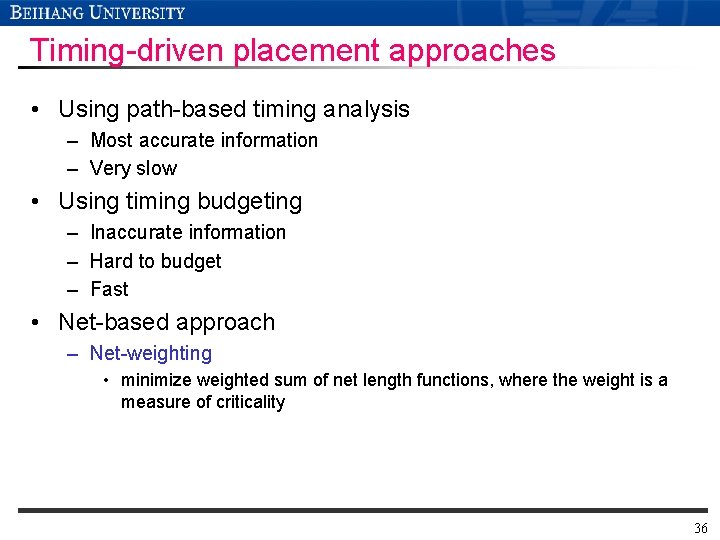

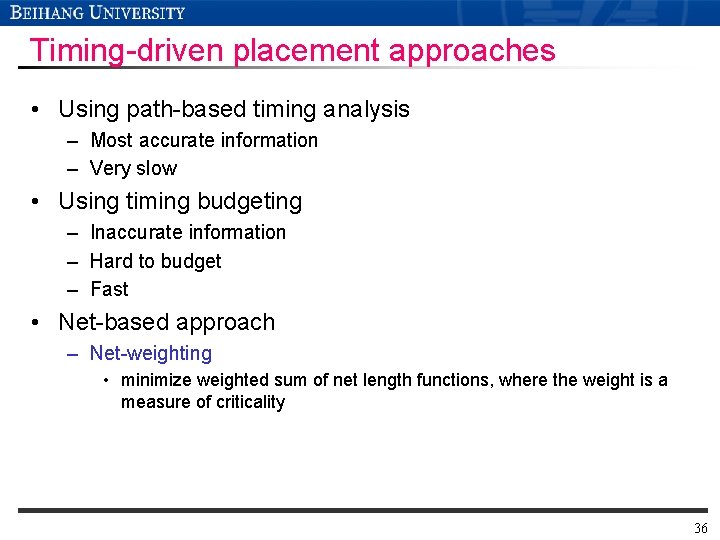

Timing-driven placement approaches • Using path-based timing analysis – Most accurate information – Very slow • Using timing budgeting – Inaccurate information – Hard to budget – Fast • Net-based approach – Net-weighting • minimize weighted sum of net length functions, where the weight is a measure of criticality 36

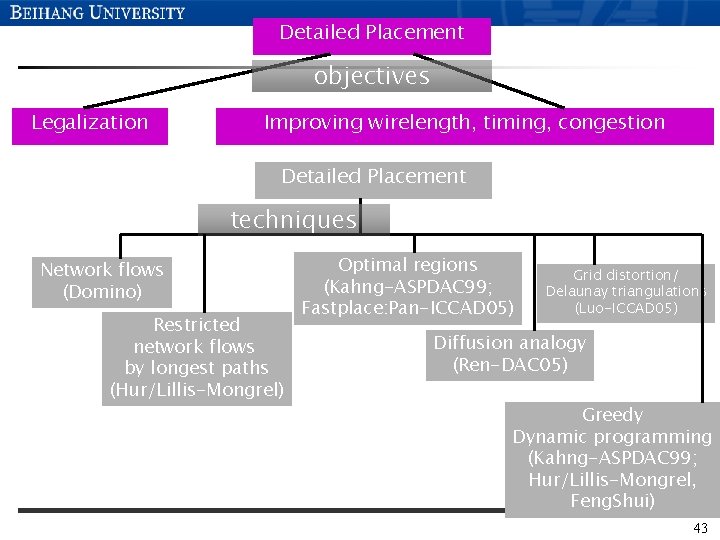

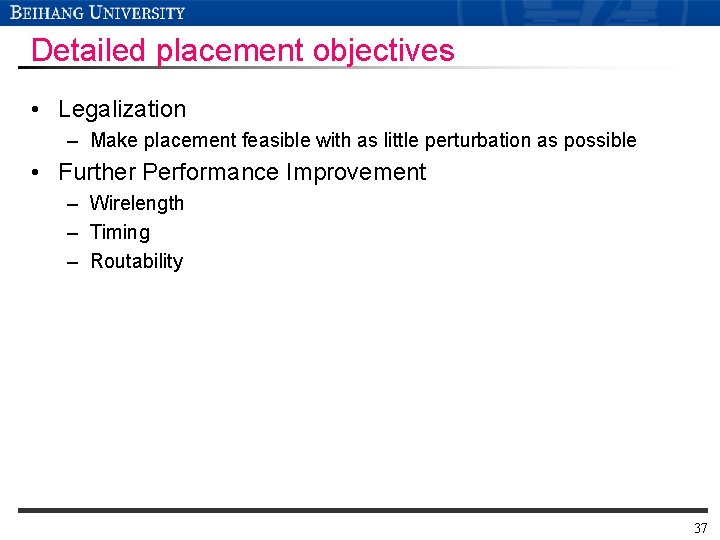

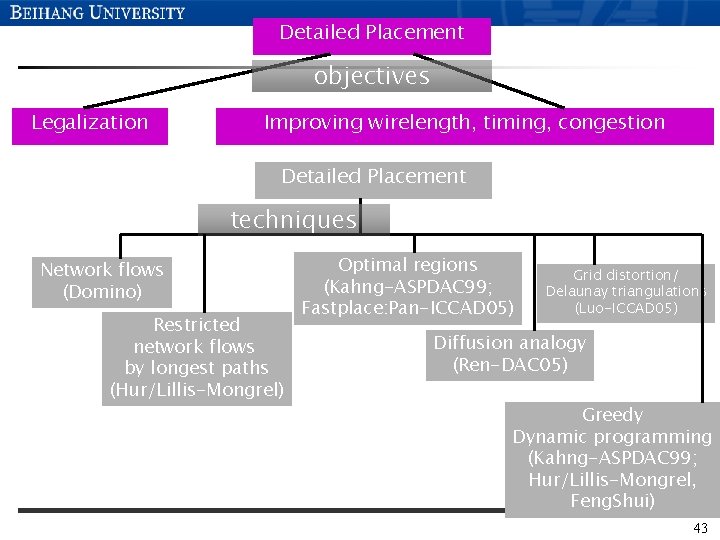

Detailed placement objectives • Legalization – Make placement feasible with as little perturbation as possible • Further Performance Improvement – Wirelength – Timing – Routability 37

![Representative approaches Constructive methods Network flow K Doll et al TCAD 94 Representative approaches • Constructive methods – Network flow [K. Doll et al, TCAD’ 94]](https://slidetodoc.com/presentation_image_h/26e8f4dc81a483c6392bace44cea6c8d/image-38.jpg)

Representative approaches • Constructive methods – Network flow [K. Doll et al, TCAD’ 94] – Linear placement [A. Kahng et al, ASPDAC’ 99] – Window interleaving [S. Hur et al, ICCAD’ 00’] • Iterative method – Simulated annealing [W. Sun & C. Sechen, ICCAD’ 93] • Hybrid method – Network flow + Dynamic programming + Linear programming [J. Vygen, DATE’ 98] [Brenner et al, ISPD’ 04] • Placement migration/spreading – Diffusion-based [Ren et al, DAC’ 05] – Delaunay [Luo et al, ICCAD’ 05] 38

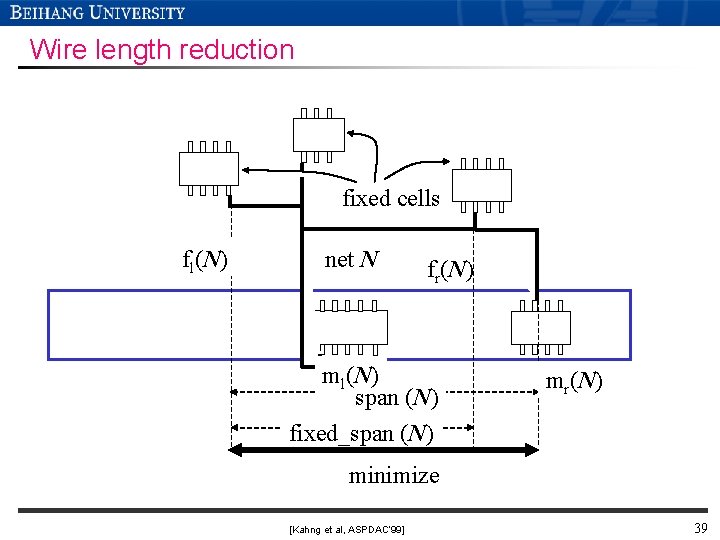

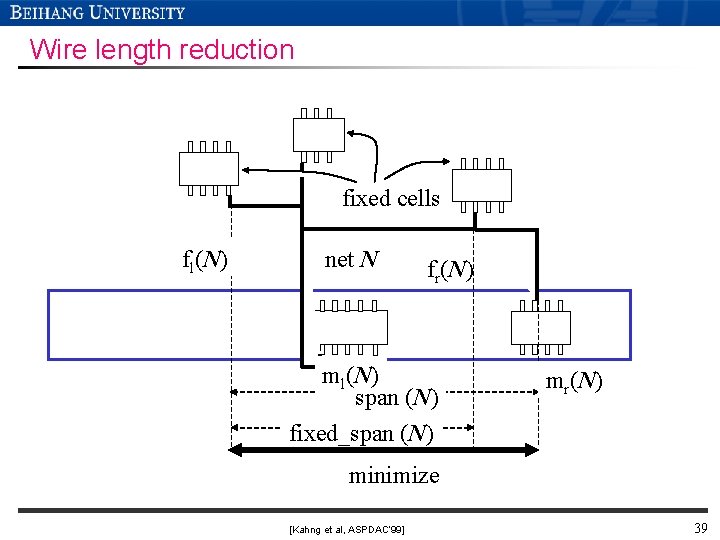

Wire length reduction fixed cells fl(N) net N fr(N) ml(N) span (N) fixed_span (N) mr(N) minimize [Kahng et al, ASPDAC’ 99] 39

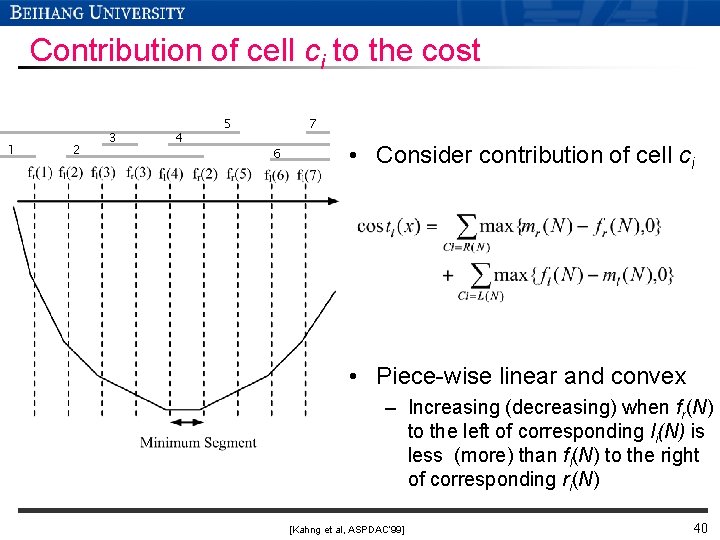

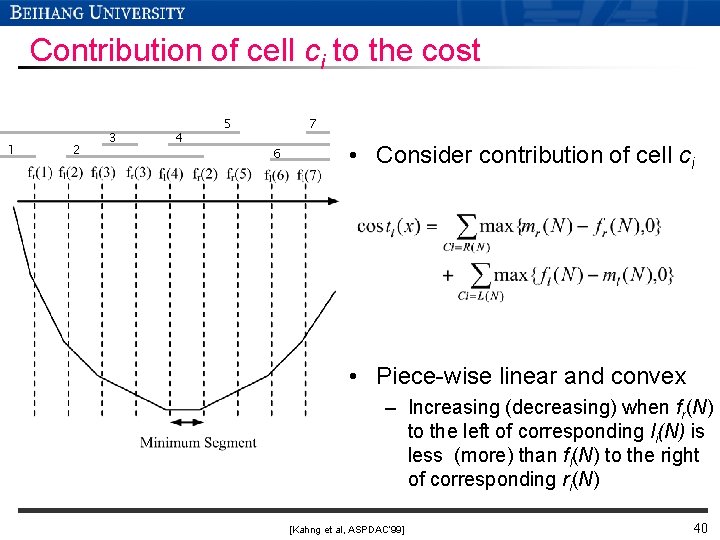

Contribution of cell ci to the cost 1 2 3 4 5 7 6 • Consider contribution of cell ci • Piece-wise linear and convex – Increasing (decreasing) when fr(N) to the left of corresponding li(N) is less (more) than fl(N) to the right of corresponding ri(N) [Kahng et al, ASPDAC’ 99] 40

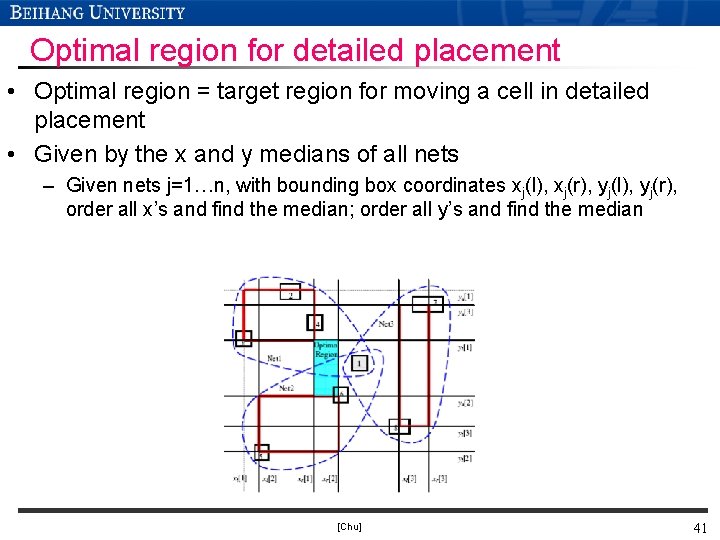

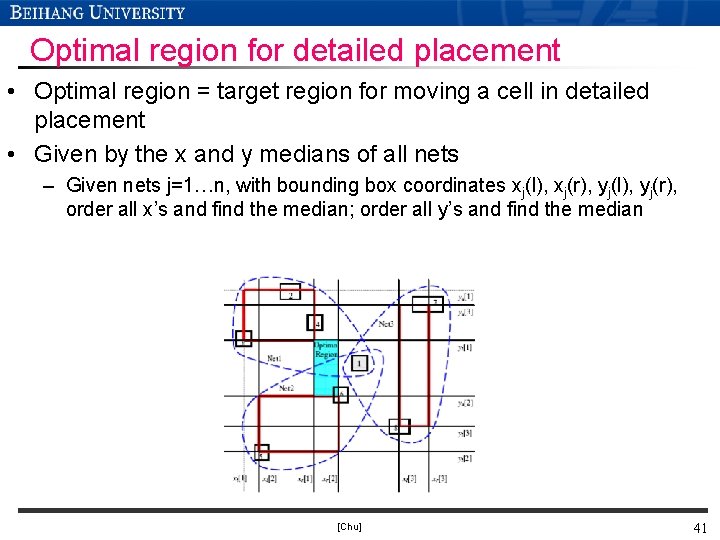

Optimal region for detailed placement • Optimal region = target region for moving a cell in detailed placement • Given by the x and y medians of all nets – Given nets j=1…n, with bounding box coordinates xj(l), xj(r), yj(l), yj(r), order all x’s and find the median; order all y’s and find the median [Chu] 41

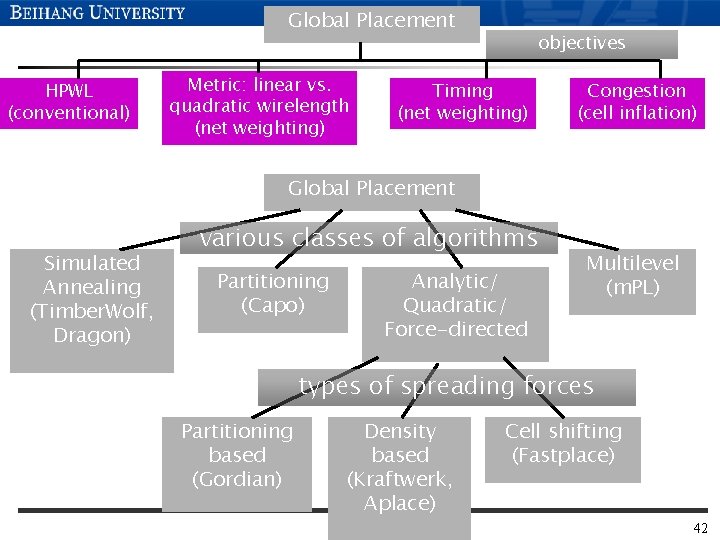

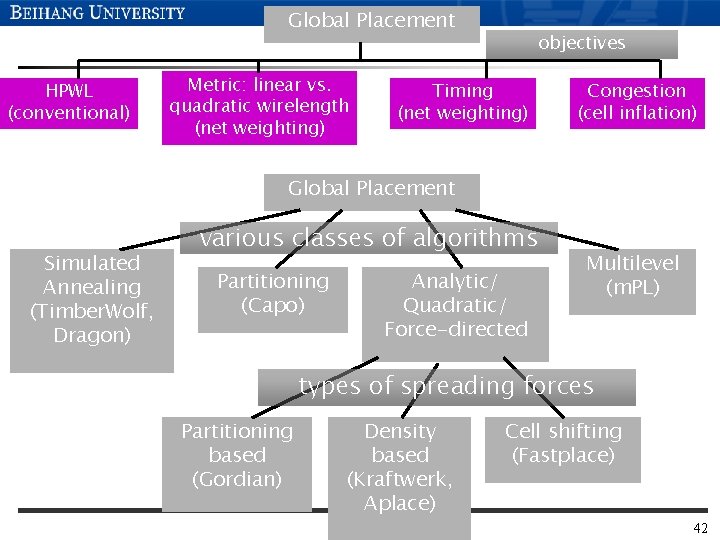

Global Placement HPWL (conventional) Metric: linear vs. quadratic wirelength (net weighting) objectives Timing (net weighting) Congestion (cell inflation) Global Placement Simulated Annealing (Timber. Wolf, Dragon) various classes of algorithms Partitioning (Capo) Analytic/ Quadratic/ Force-directed Multilevel (m. PL) types of spreading forces Partitioning based (Gordian) Density based (Kraftwerk, Aplace) Cell shifting (Fastplace) 42

Detailed Placement objectives Legalization Improving wirelength, timing, congestion Detailed Placement techniques Network flows (Domino) Restricted network flows by longest paths (Hur/Lillis-Mongrel) Optimal regions (Kahng-ASPDAC 99; Fastplace: Pan-ICCAD 05) Grid distortion/ Delaunay triangulations (Luo-ICCAD 05) Diffusion analogy (Ren-DAC 05) Greedy Dynamic programming (Kahng-ASPDAC 99; Hur/Lillis-Mongrel, Feng. Shui) 43