Introduction to Computer Systems Department of Computer Science

- Slides: 27

Introduction to Computer Systems Department of Computer Science and Information Systems Lecturer: Steve Maybank sjmaybank@dcs. bbk. ac. uk Spring 2020 Week 5 b: Types of Instruction 11 February 2020 Birkbeck College, U. London 1

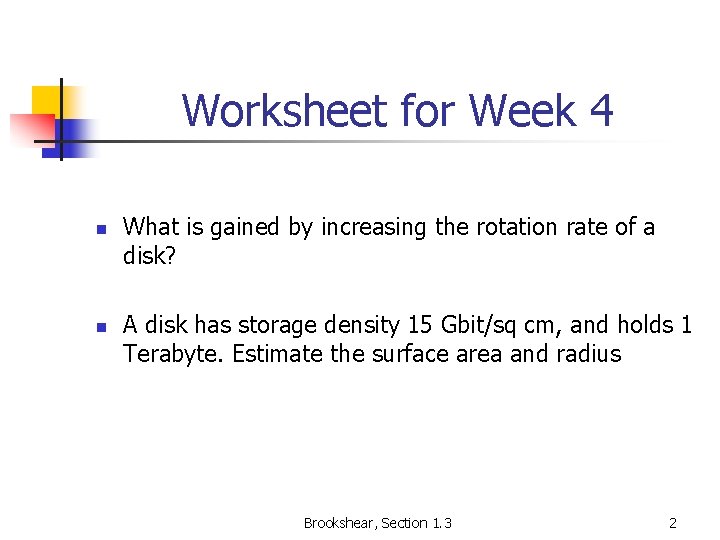

Worksheet for Week 4 n n What is gained by increasing the rotation rate of a disk? A disk has storage density 15 Gbit/sq cm, and holds 1 Terabyte. Estimate the surface area and radius Brookshear, Section 1. 3 2

Worksheet for Week 4 n n Find the bits per second for a video with 30 frames per second where each frame has 1920 x 1080 pixels and 24 bits per pixel. A machine executes 500 instructions each microsecond. How many instructions are executed per character for a person typing 40 words per minute with 5 characters per word. Brookshear, Ch 2 review problems 3

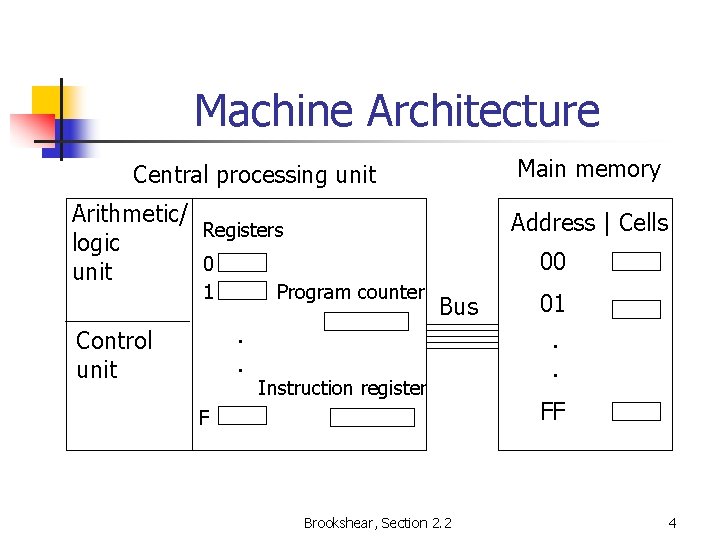

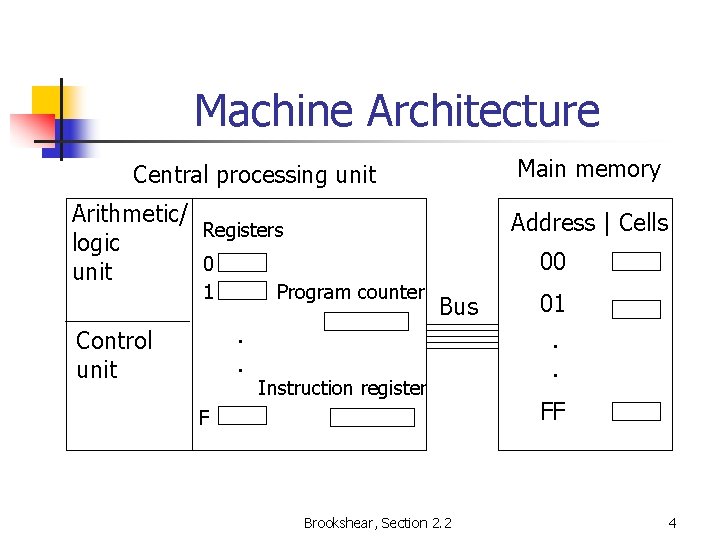

Machine Architecture Main memory Central processing unit Arithmetic/ Registers logic 0 unit 1 00 Program counter . . Control unit Address | Cells Bus Instruction register F Brookshear, Section 2. 2 01. . FF 4

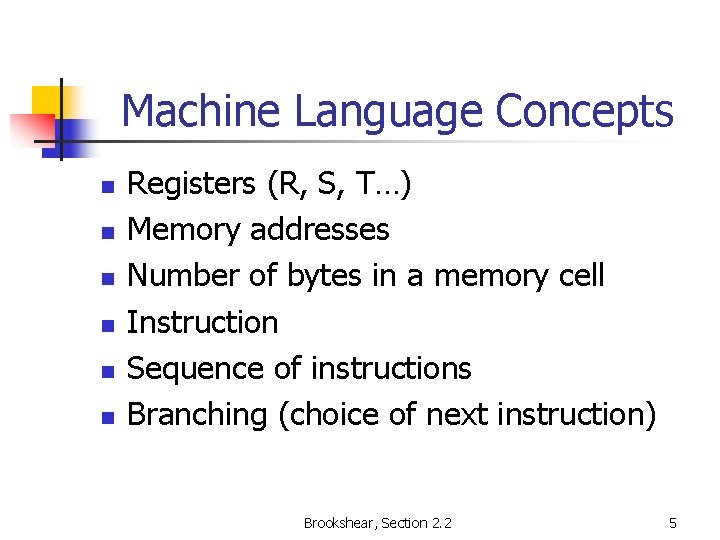

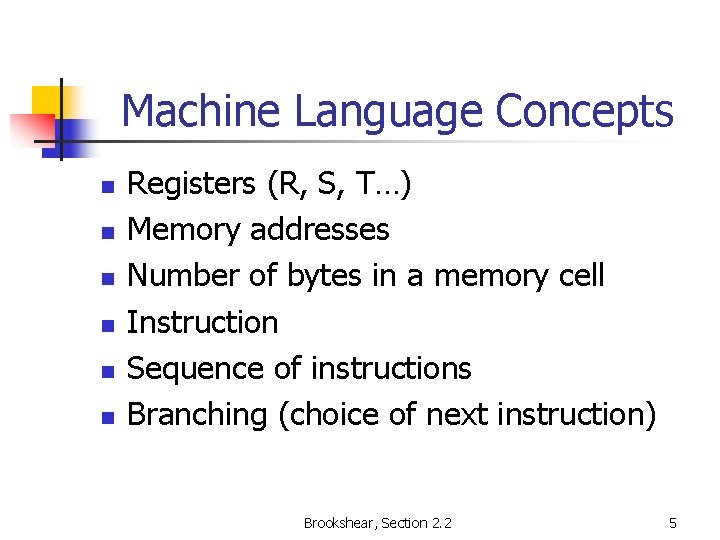

Machine Language Concepts n n n Registers (R, S, T…) Memory addresses Number of bytes in a memory cell Instruction Sequence of instructions Branching (choice of next instruction) Brookshear, Section 2. 2 5

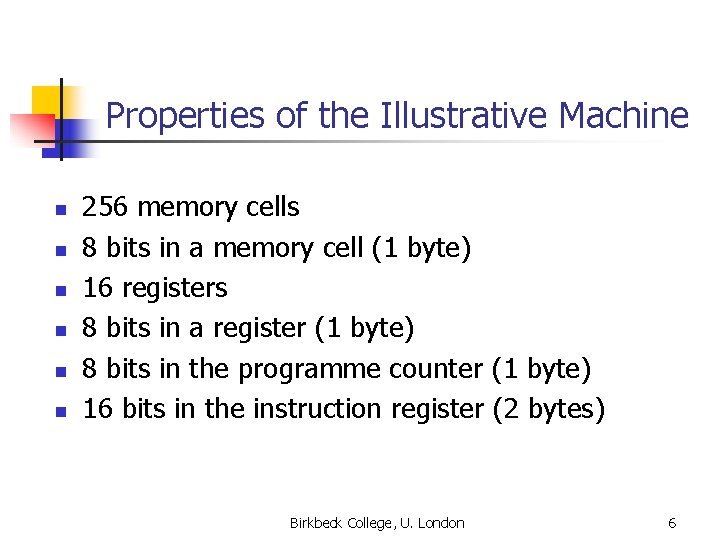

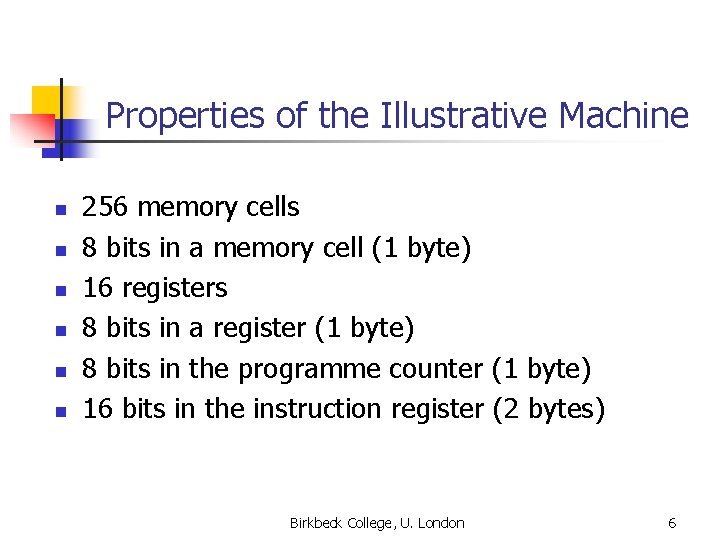

Properties of the Illustrative Machine n n n 256 memory cells 8 bits in a memory cell (1 byte) 16 registers 8 bits in a register (1 byte) 8 bits in the programme counter (1 byte) 16 bits in the instruction register (2 bytes) Birkbeck College, U. London 6

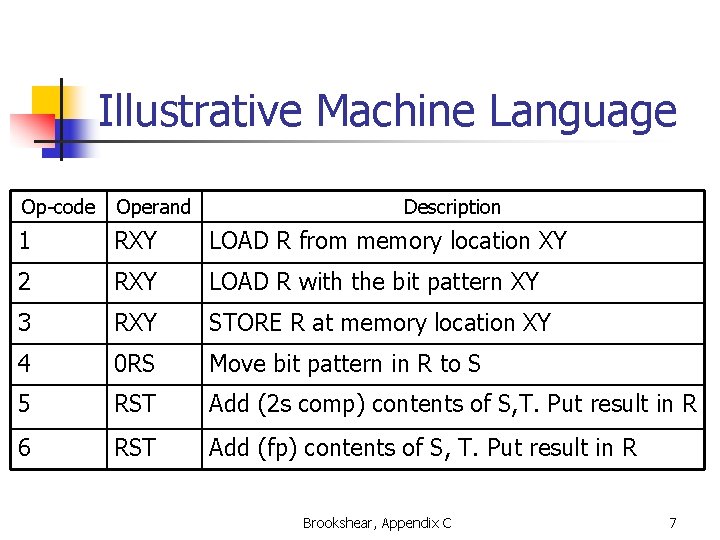

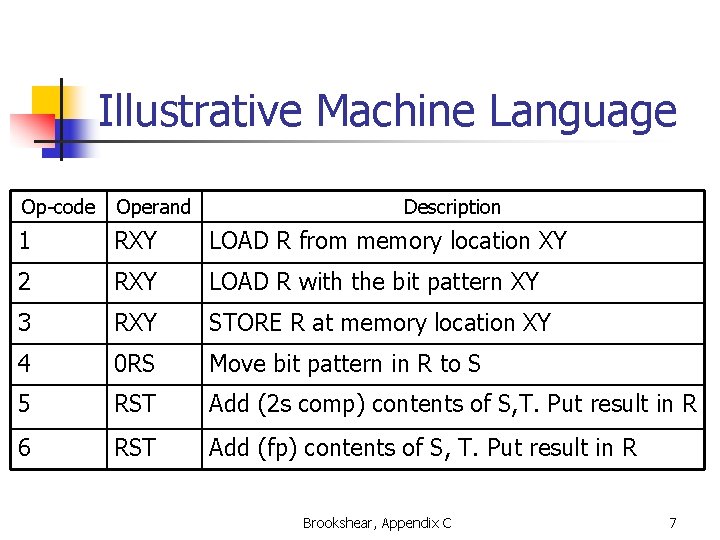

Illustrative Machine Language Op-code Operand Description 1 RXY LOAD R from memory location XY 2 RXY LOAD R with the bit pattern XY 3 RXY STORE R at memory location XY 4 0 RS Move bit pattern in R to S 5 RST Add (2 s comp) contents of S, T. Put result in R 6 RST Add (fp) contents of S, T. Put result in R Brookshear, Appendix C 7

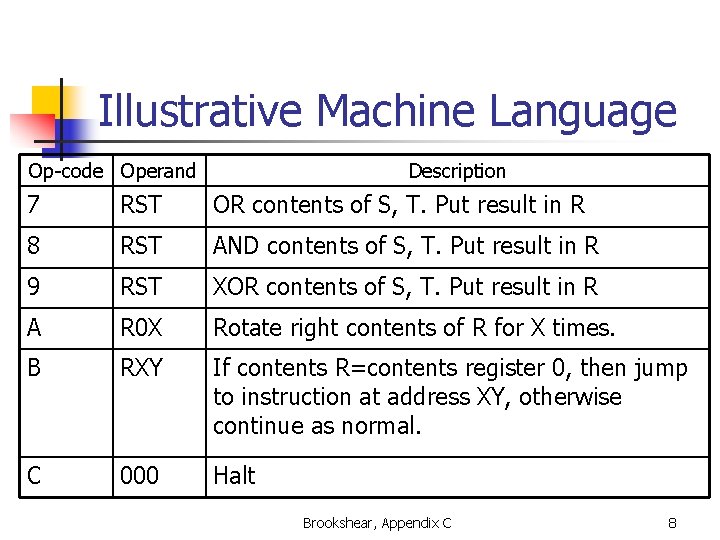

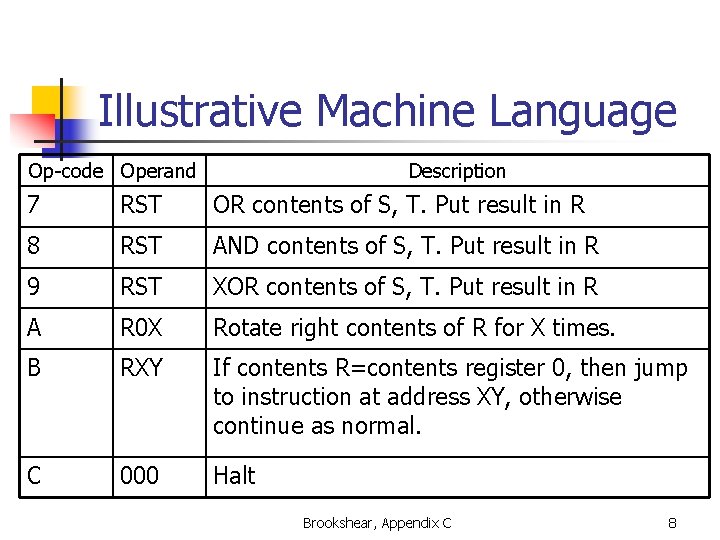

Illustrative Machine Language Op-code Operand Description 7 RST OR contents of S, T. Put result in R 8 RST AND contents of S, T. Put result in R 9 RST XOR contents of S, T. Put result in R A R 0 X Rotate right contents of R for X times. B RXY If contents R=contents register 0, then jump to instruction at address XY, otherwise continue as normal. C 000 Halt Brookshear, Appendix C 8

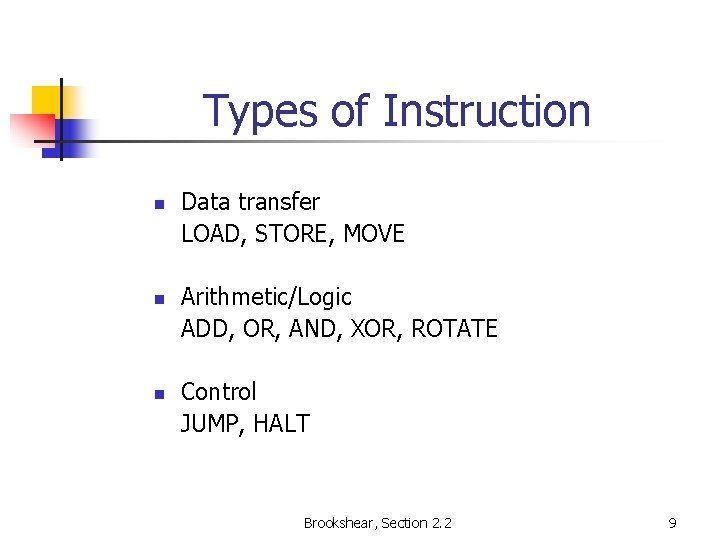

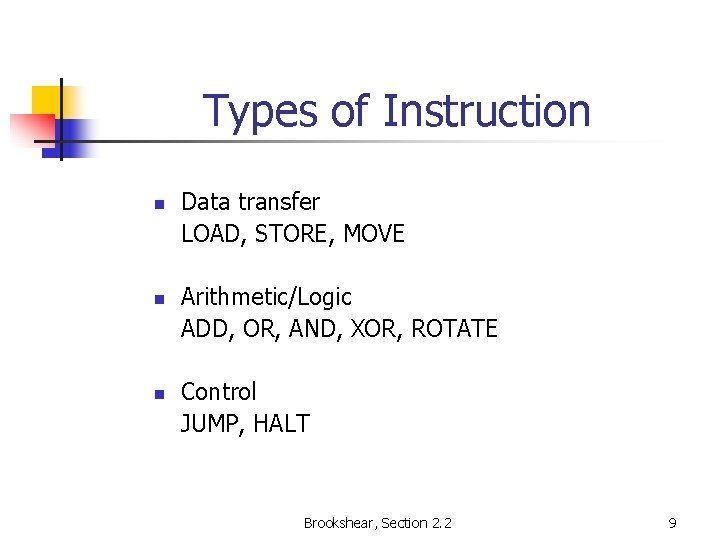

Types of Instruction n Data transfer LOAD, STORE, MOVE Arithmetic/Logic ADD, OR, AND, XOR, ROTATE Control JUMP, HALT Brookshear, Section 2. 2 9

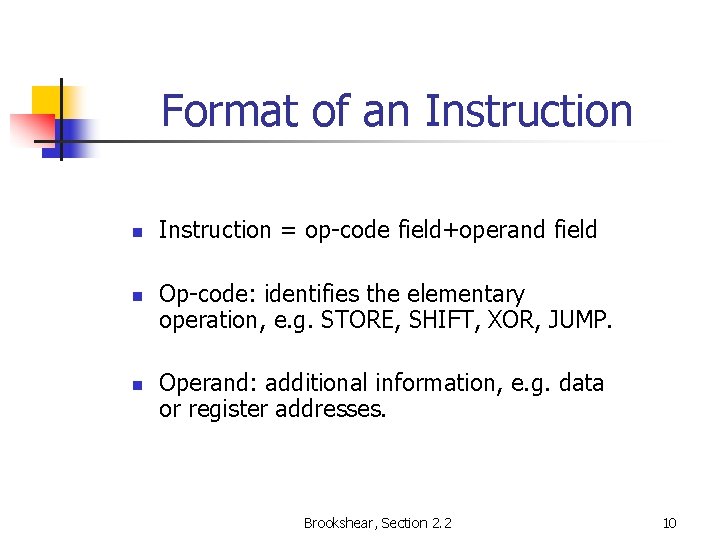

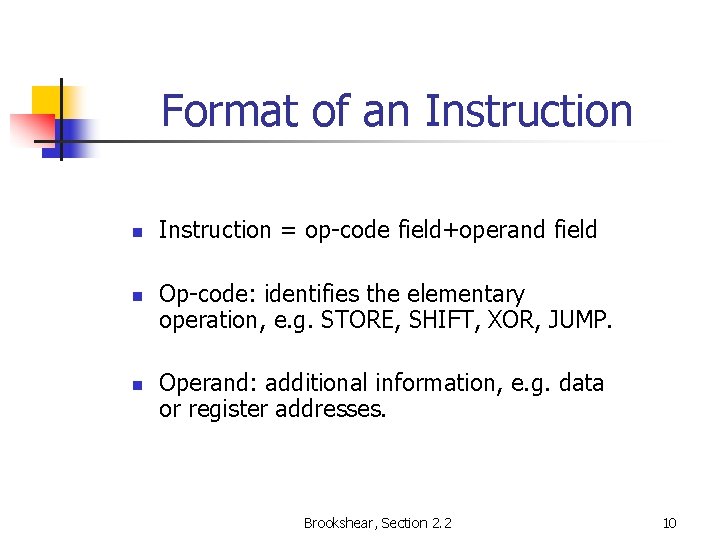

Format of an Instruction = op-code field+operand field Op-code: identifies the elementary operation, e. g. STORE, SHIFT, XOR, JUMP. Operand: additional information, e. g. data or register addresses. Brookshear, Section 2. 2 10

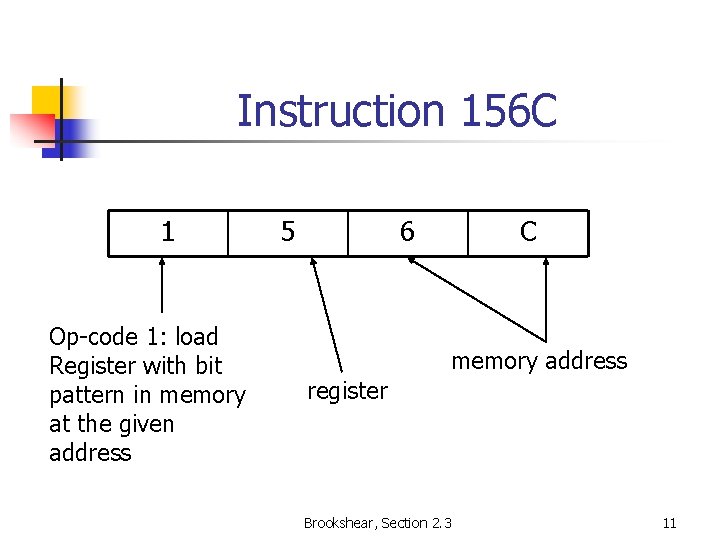

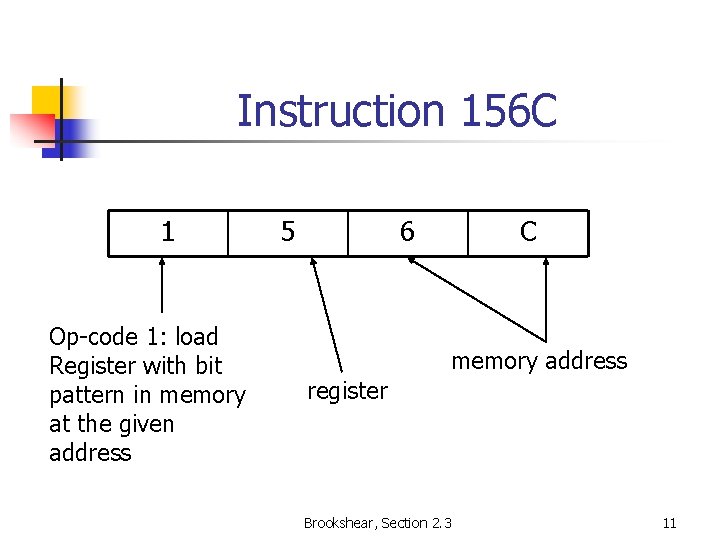

Instruction 156 C 1 Op-code 1: load Register with bit pattern in memory at the given address 5 6 C memory address register Brookshear, Section 2. 3 11

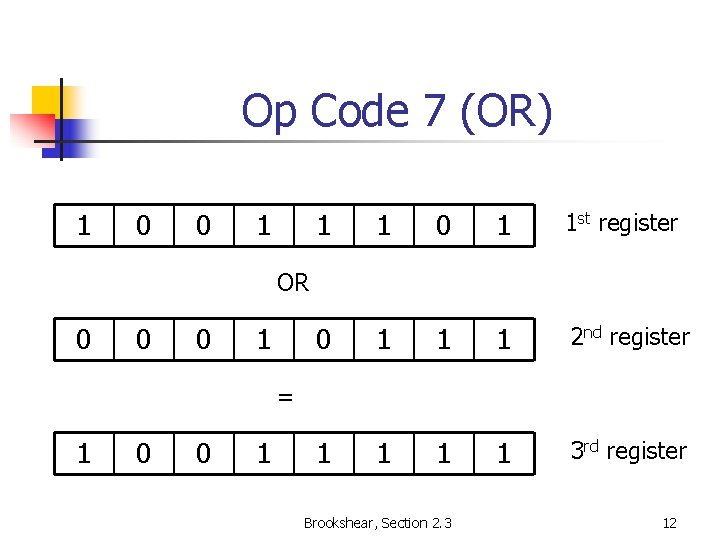

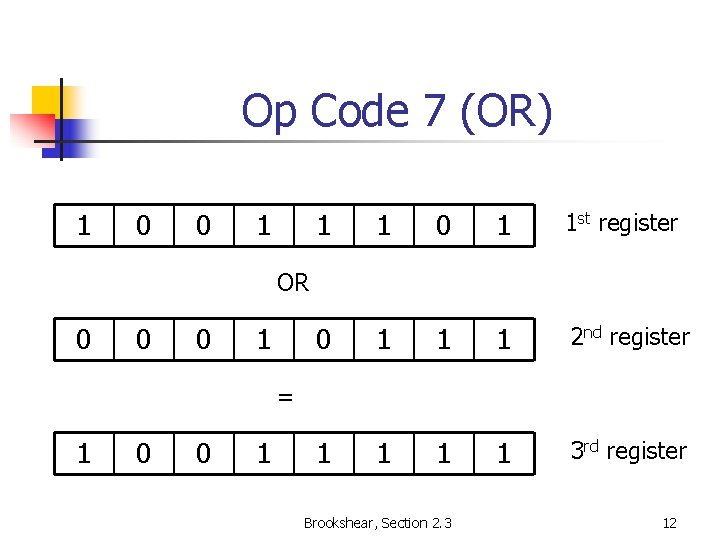

Op Code 7 (OR) 1 0 0 1 1 1 0 1 1 st register 0 1 1 1 2 nd register 1 1 3 rd register OR 0 0 0 1 = 1 0 0 1 Brookshear, Section 2. 3 12

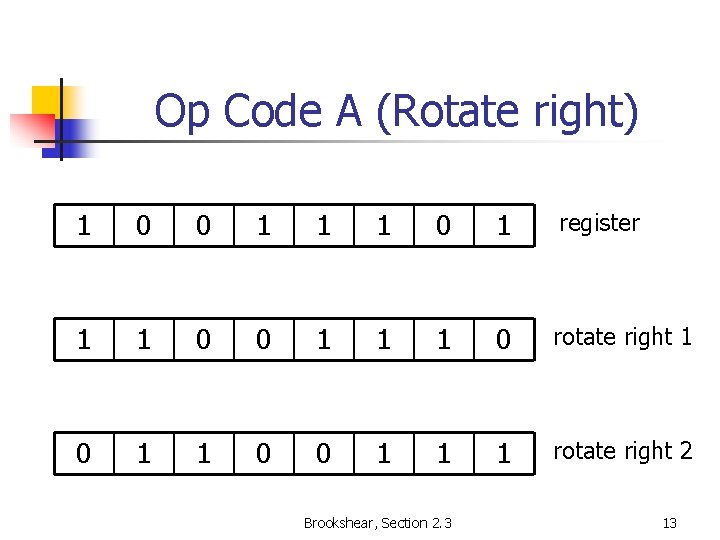

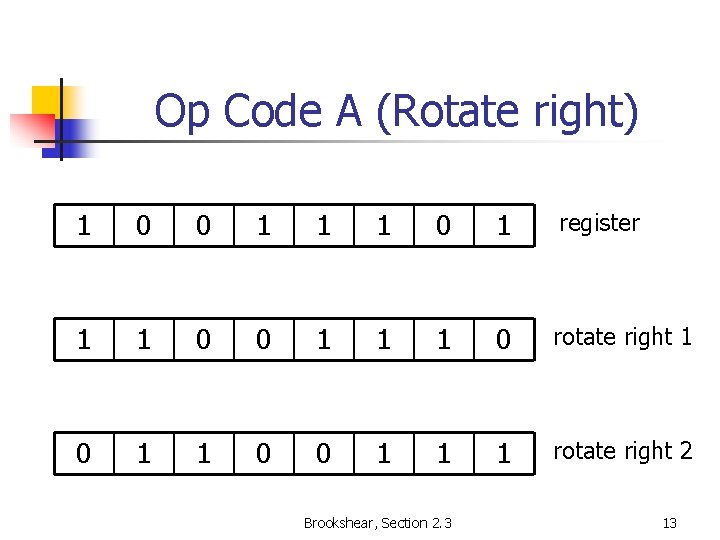

Op Code A (Rotate right) 1 0 0 1 1 1 0 1 register 1 1 0 0 1 1 1 0 rotate right 1 0 1 1 0 0 1 1 1 rotate right 2 Brookshear, Section 2. 3 13

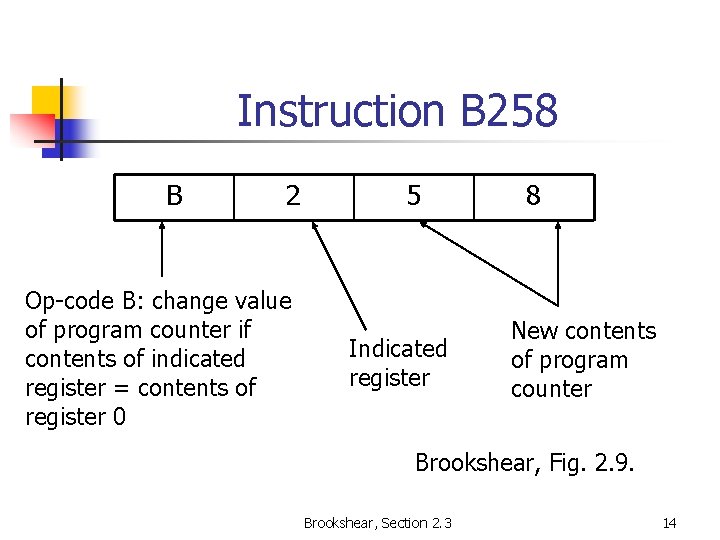

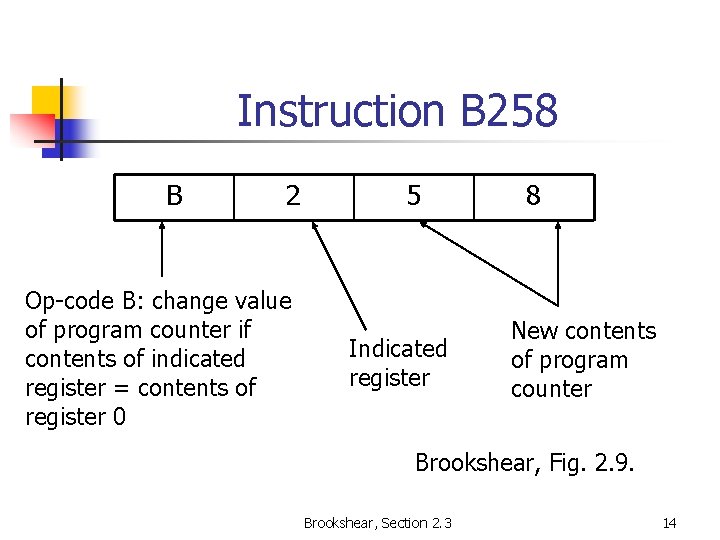

Instruction B 258 B 2 Op-code B: change value of program counter if contents of indicated register = contents of register 0 5 Indicated register 8 New contents of program counter Brookshear, Fig. 2. 9. Brookshear, Section 2. 3 14

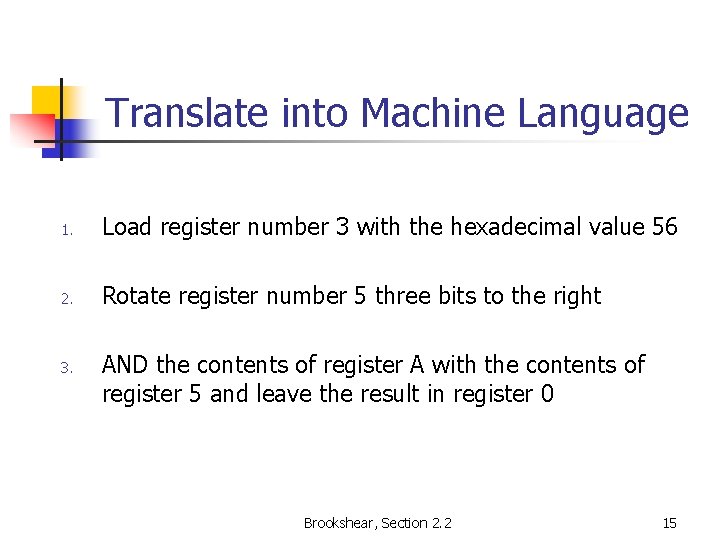

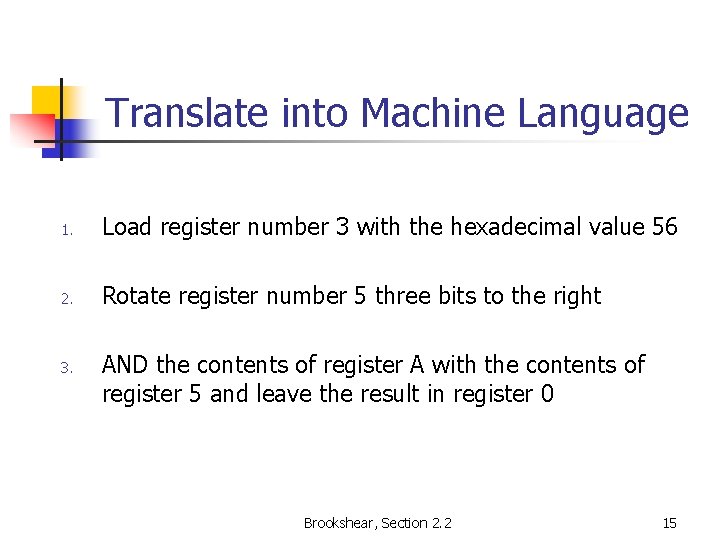

Translate into Machine Language 1. Load register number 3 with the hexadecimal value 56 2. Rotate register number 5 three bits to the right 3. AND the contents of register A with the contents of register 5 and leave the result in register 0 Brookshear, Section 2. 2 15

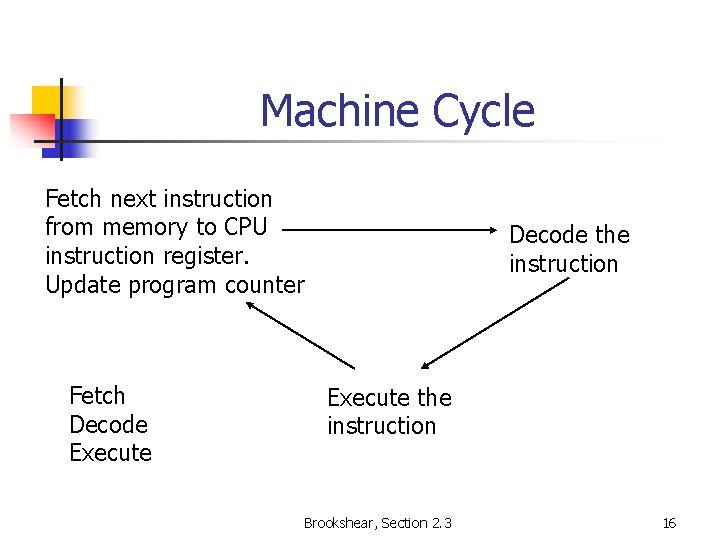

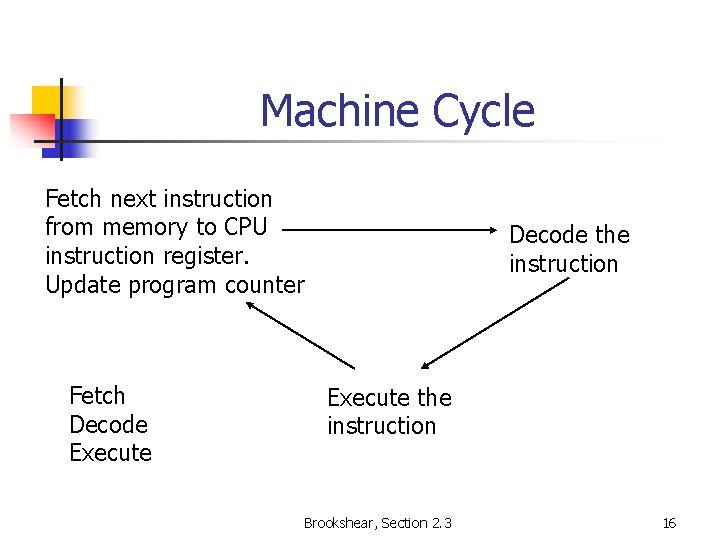

Machine Cycle Fetch next instruction from memory to CPU instruction register. Update program counter Fetch Decode Execute Decode the instruction Execute the instruction Brookshear, Section 2. 3 16

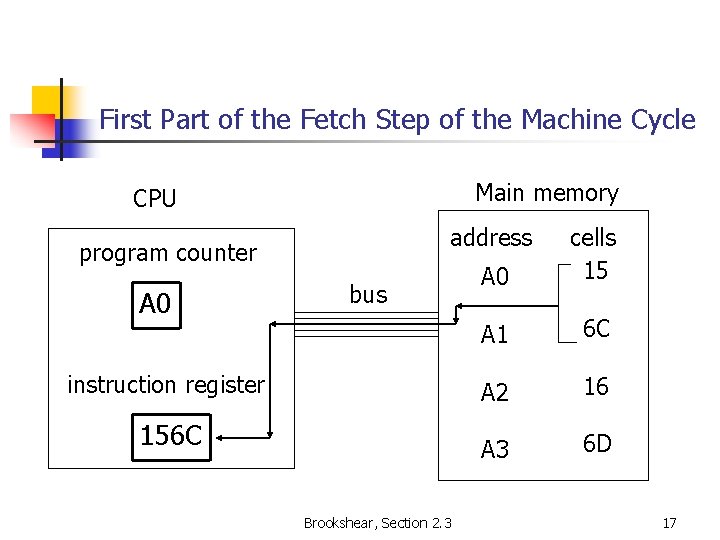

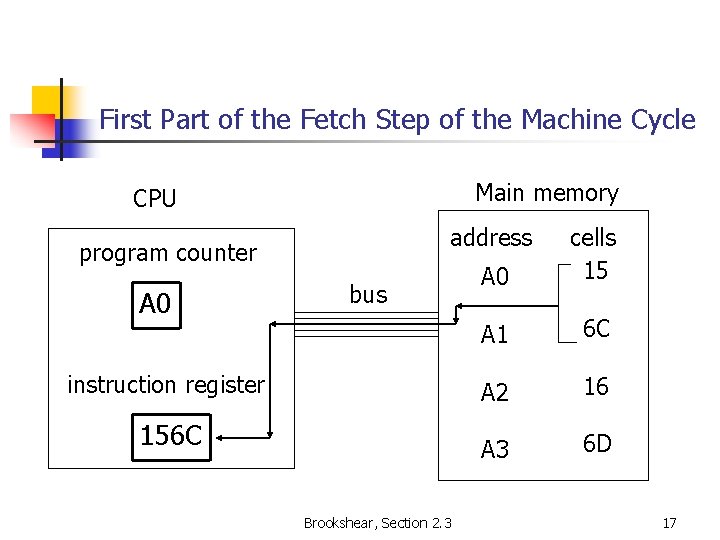

First Part of the Fetch Step of the Machine Cycle Main memory CPU address A 0 cells 15 A 1 6 C instruction register A 2 16 156 C A 3 6 D program counter A 0 bus Brookshear, Section 2. 3 17

Completion of the Fetch Step Main memory CPU address A 0 cells 15 A 1 6 C instruction register A 2 16 156 C A 3 6 D program counter A 2 bus Brookshear, Section 2. 3 18

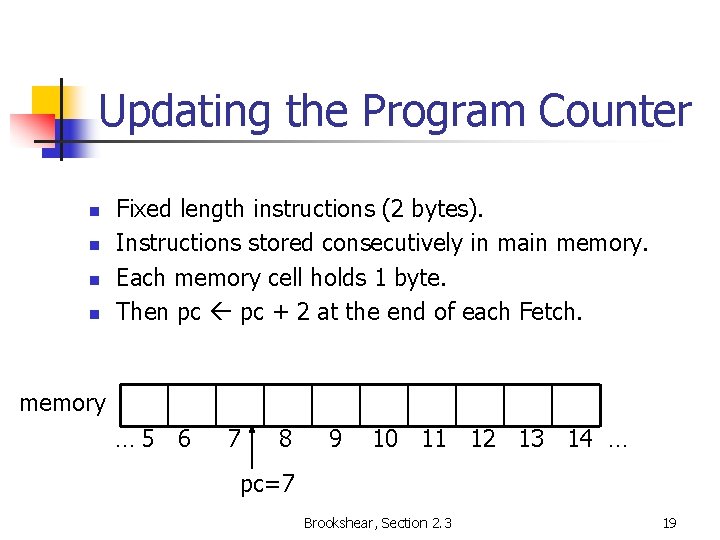

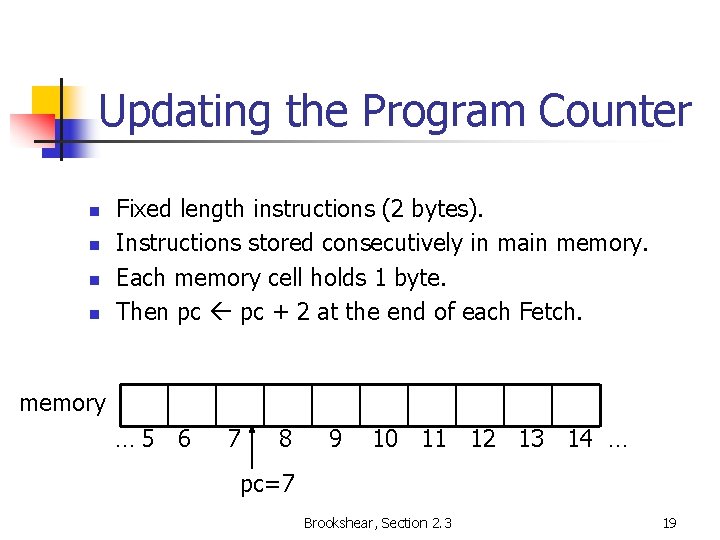

Updating the Program Counter n n Fixed length instructions (2 bytes). Instructions stored consecutively in main memory. Each memory cell holds 1 byte. Then pc + 2 at the end of each Fetch. memory … 5 6 7 8 9 10 11 12 13 14 … pc=7 Brookshear, Section 2. 3 19

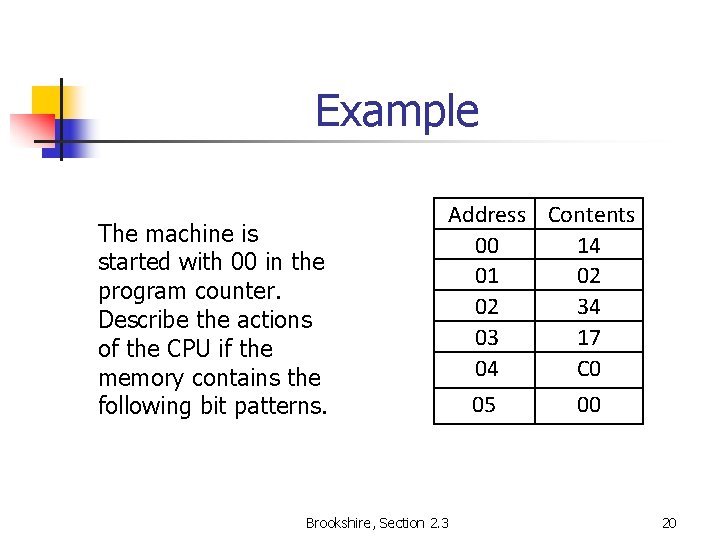

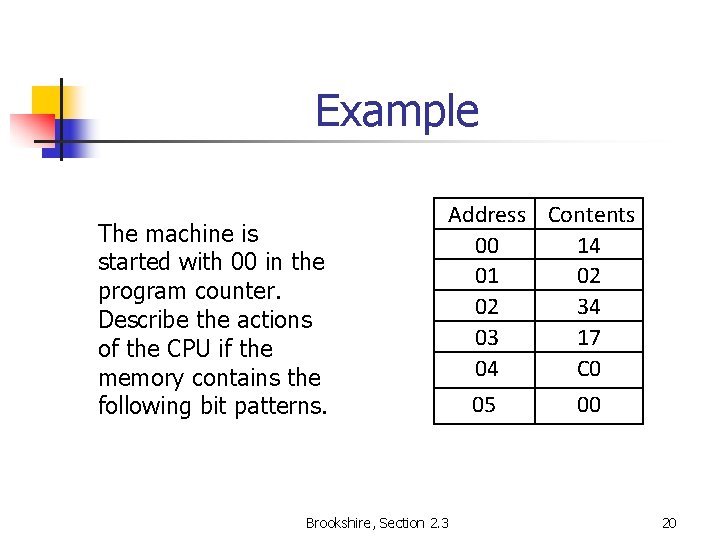

Example The machine is started with 00 in the program counter. Describe the actions of the CPU if the memory contains the following bit patterns. Address Contents 00 14 01 02 02 34 03 17 04 C 0 05 00 Brookshire, Section 2. 3 20

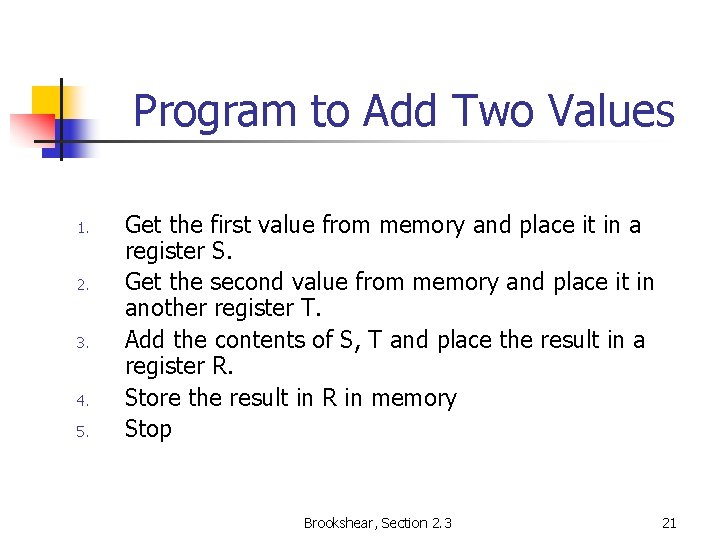

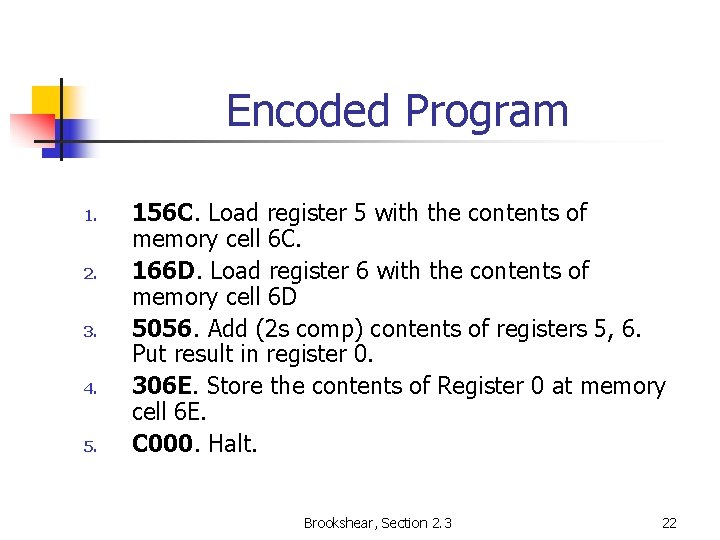

Program to Add Two Values 1. 2. 3. 4. 5. Get the first value from memory and place it in a register S. Get the second value from memory and place it in another register T. Add the contents of S, T and place the result in a register R. Store the result in R in memory Stop Brookshear, Section 2. 3 21

Encoded Program 1. 2. 3. 4. 5. 156 C. Load register 5 with the contents of memory cell 6 C. 166 D. Load register 6 with the contents of memory cell 6 D 5056. Add (2 s comp) contents of registers 5, 6. Put result in register 0. 306 E. Store the contents of Register 0 at memory cell 6 E. C 000. Halt. Brookshear, Section 2. 3 22

Without Instruction B § A program containing n instructions would run for n machine cycles § The program would be unable to change the calculations in rsponse to the data Birkbeck College, U. London 23

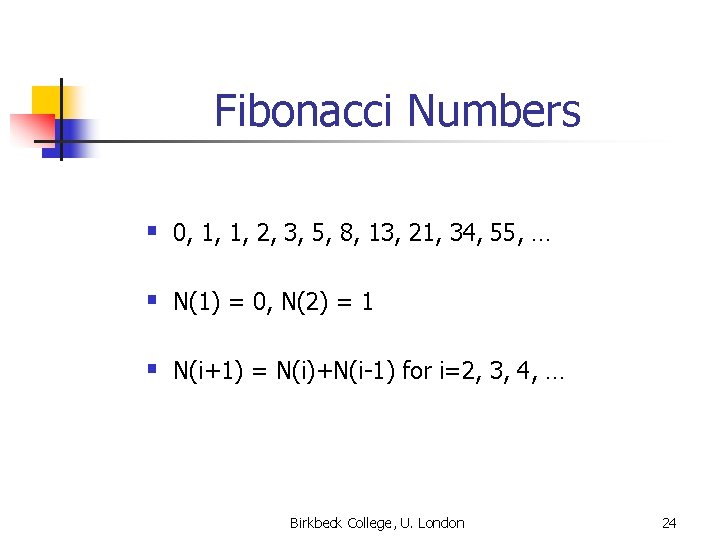

Fibonacci Numbers § 0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, … § N(1) = 0, N(2) = 1 § N(i+1) = N(i)+N(i-1) for i=2, 3, 4, … Birkbeck College, U. London 24

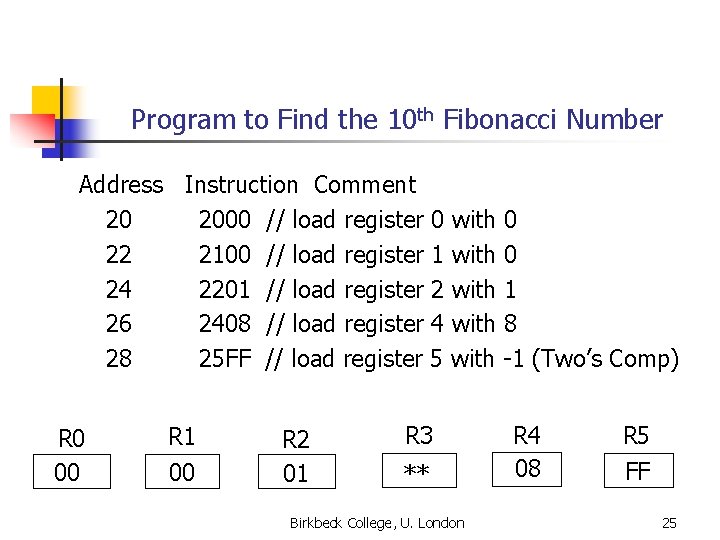

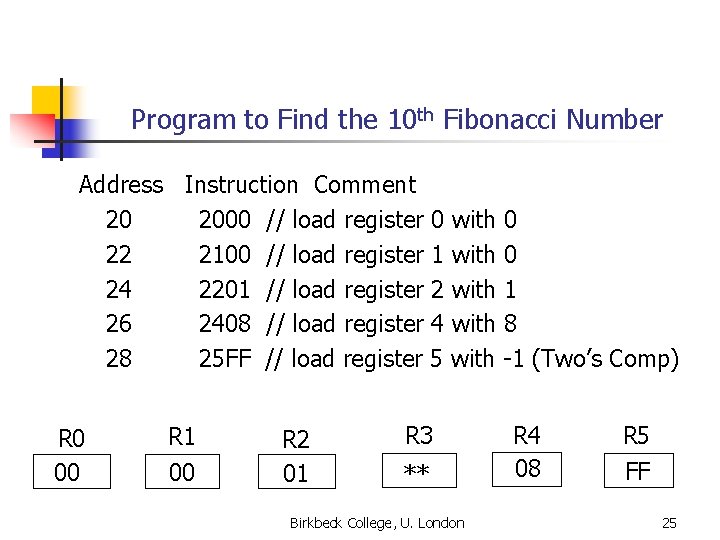

Program to Find the 10 th Fibonacci Number Address Instruction Comment 20 2000 // load register 0 with 0 22 2100 // load register 1 with 0 24 2201 // load register 2 with 1 26 2408 // load register 4 with 8 28 25 FF // load register 5 with -1 (Two’s Comp) R 0 00 R 1 00 R 2 01 R 3 ** Birkbeck College, U. London R 4 08 R 5 FF 25

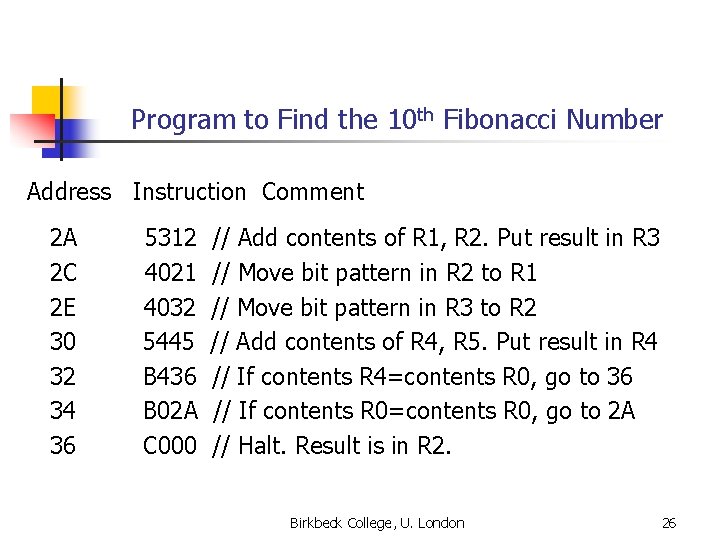

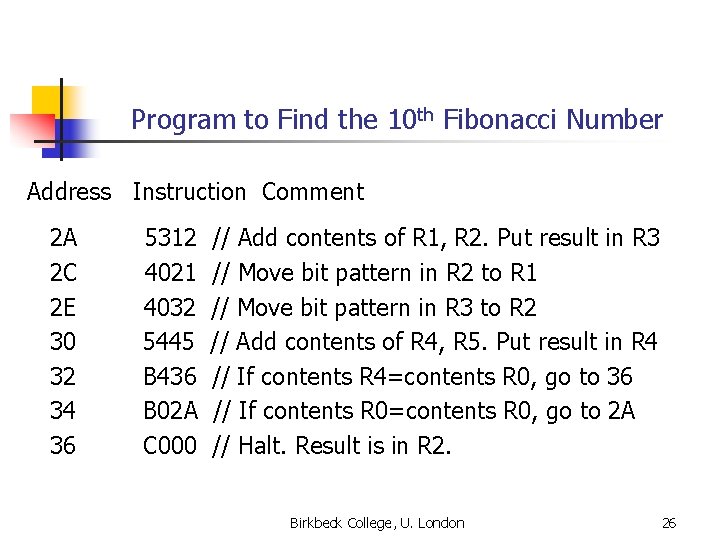

Program to Find the 10 th Fibonacci Number Address Instruction Comment 2 A 2 C 2 E 30 32 34 36 5312 4021 4032 5445 B 436 B 02 A C 000 // Add contents of R 1, R 2. Put result in R 3 // Move bit pattern in R 2 to R 1 // Move bit pattern in R 3 to R 2 // Add contents of R 4, R 5. Put result in R 4 // If contents R 4=contents R 0, go to 36 // If contents R 0=contents R 0, go to 2 A // Halt. Result is in R 2. Birkbeck College, U. London 26

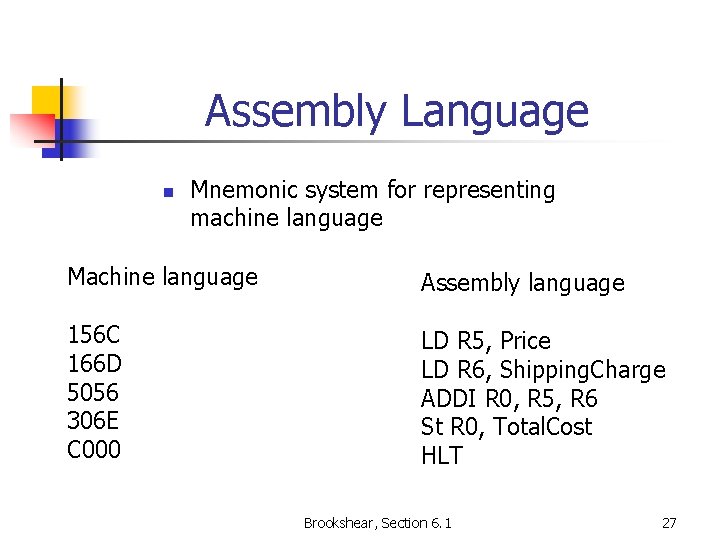

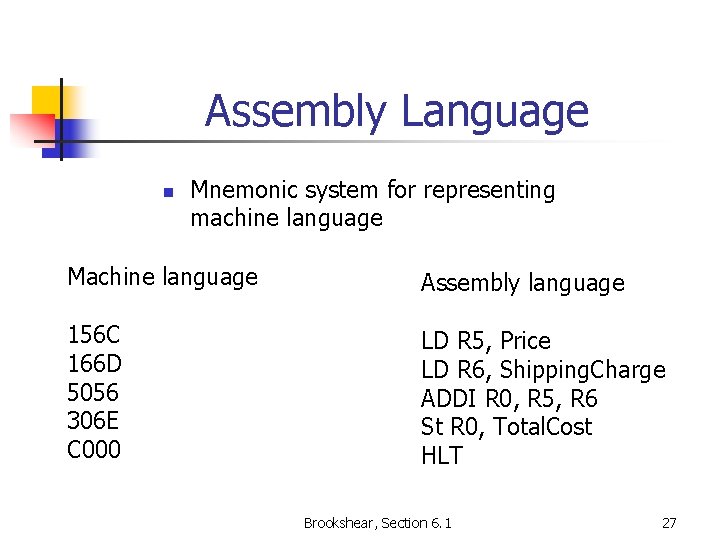

Assembly Language n Mnemonic system for representing machine language Machine language Assembly language 156 C 166 D 5056 306 E C 000 LD R 5, Price LD R 6, Shipping. Charge ADDI R 0, R 5, R 6 St R 0, Total. Cost HLT Brookshear, Section 6. 1 27