Introduction to Computer Organization and Architecture Micro Program

- Slides: 63

Introduction to Computer Organization and Architecture ภาษาเครอง Micro Program �����

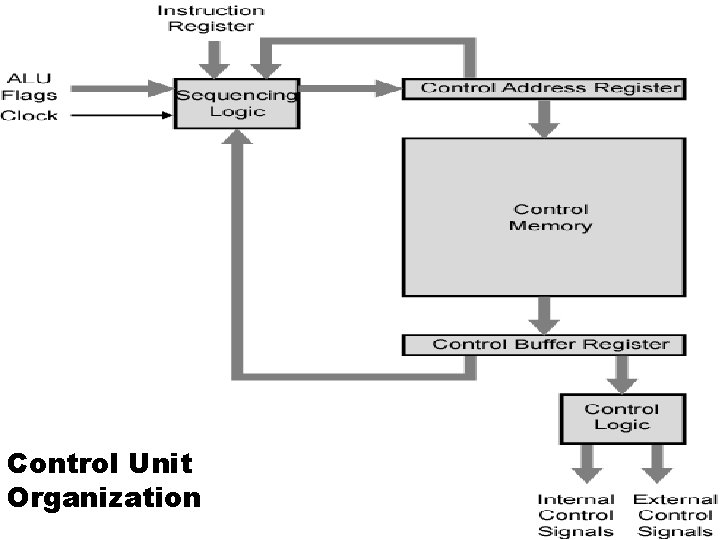

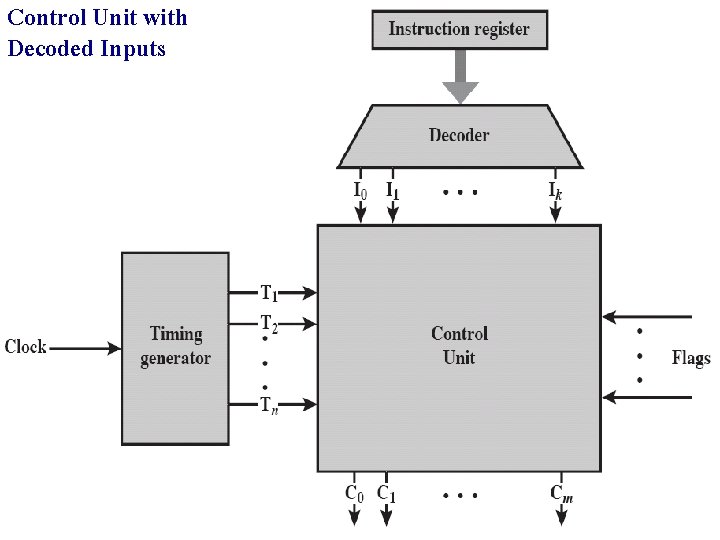

Model of Control Unit How the Control Unit Generate the control signal?

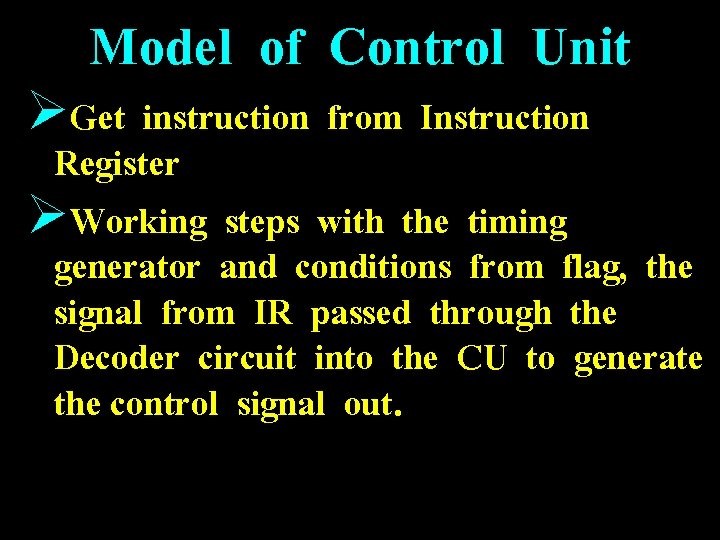

Model of Control Unit ØGet instruction from Instruction Register ØWorking steps with the timing generator and conditions from flag, the signal from IR passed through the Decoder circuit into the CU to generate the control signal out.

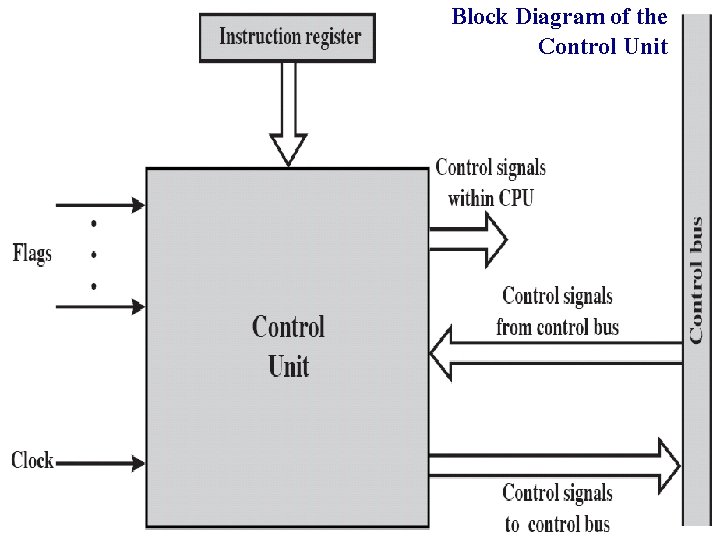

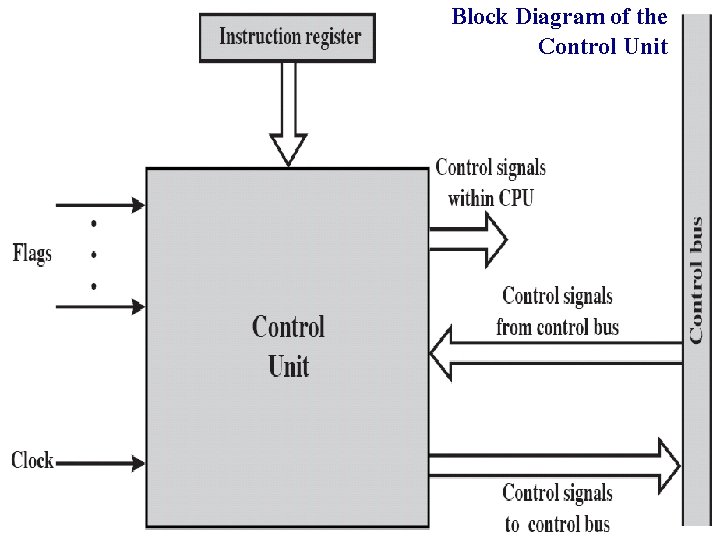

Block Diagram of the Control Unit

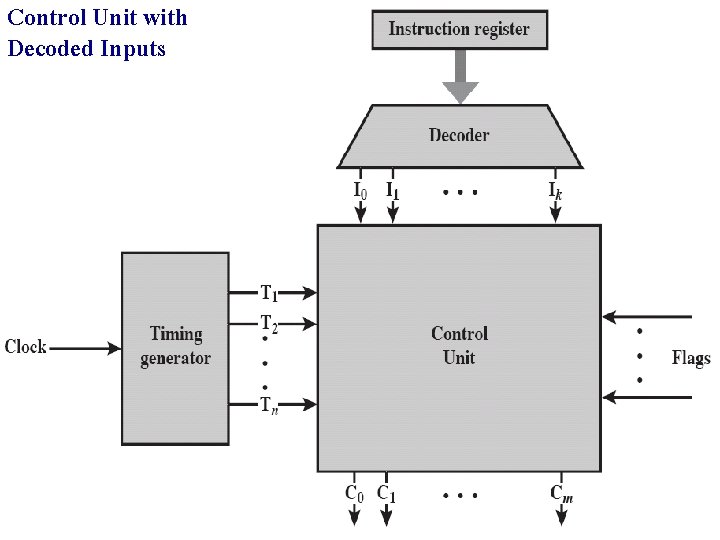

Control Unit with Decoded Inputs

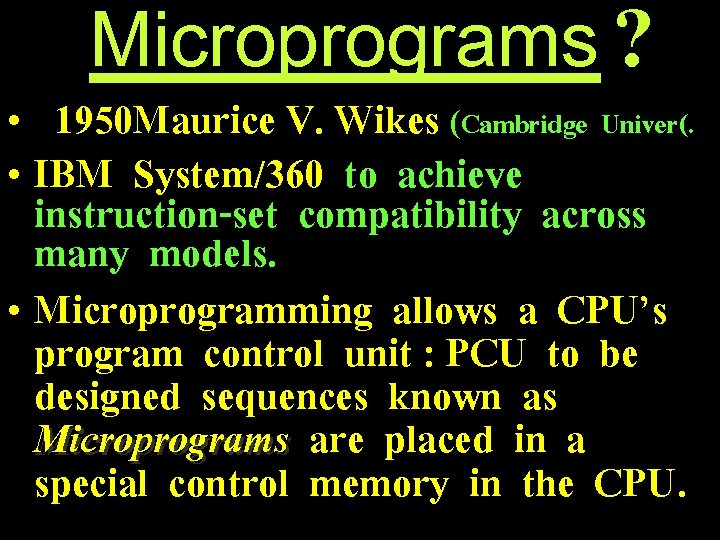

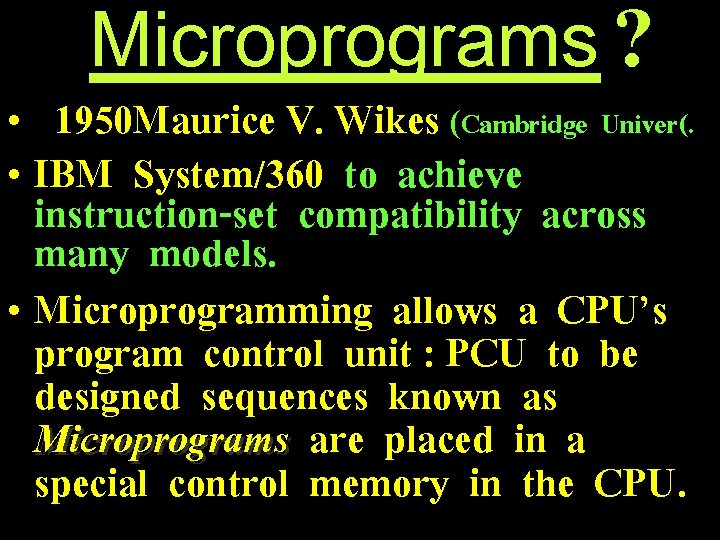

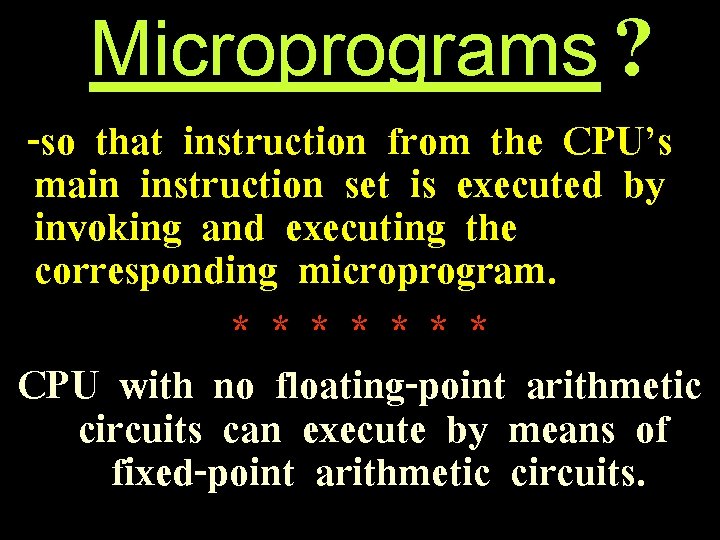

Microprograms ? • 1950 Maurice V. Wikes (Cambridge Univer(. • IBM System/360 to achieve instruction-set compatibility across many models. • Microprogramming allows a CPU’s program control unit : PCU to be designed sequences known as Microprograms are placed in a special control memory in the CPU.

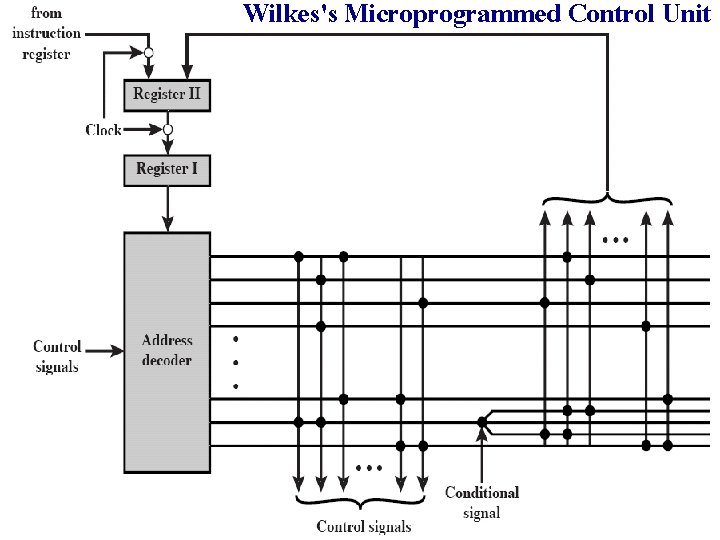

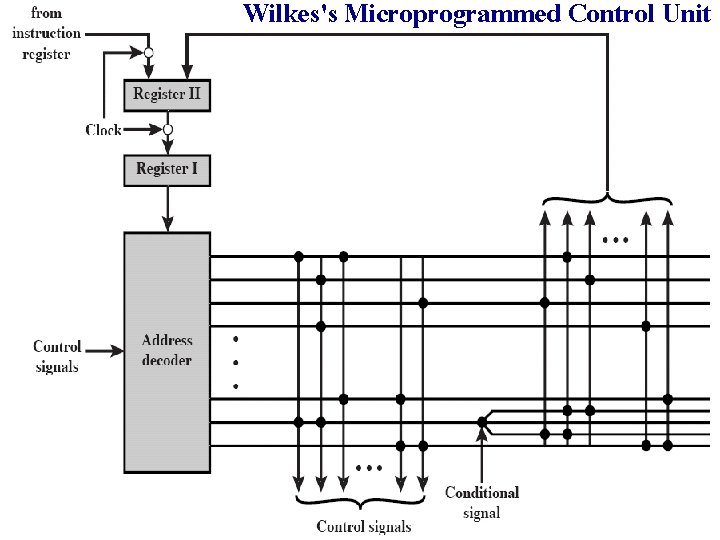

Wilkes's Microprogrammed Control Unit

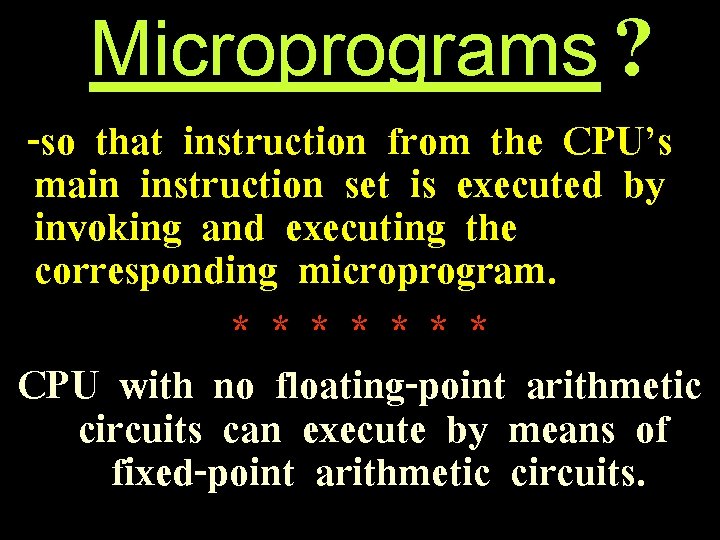

Microprograms ? -so that instruction from the CPU’s main instruction set is executed by invoking and executing the corresponding microprogram. ******* CPU with no floating-point arithmetic circuits can execute by means of fixed-point arithmetic circuits.

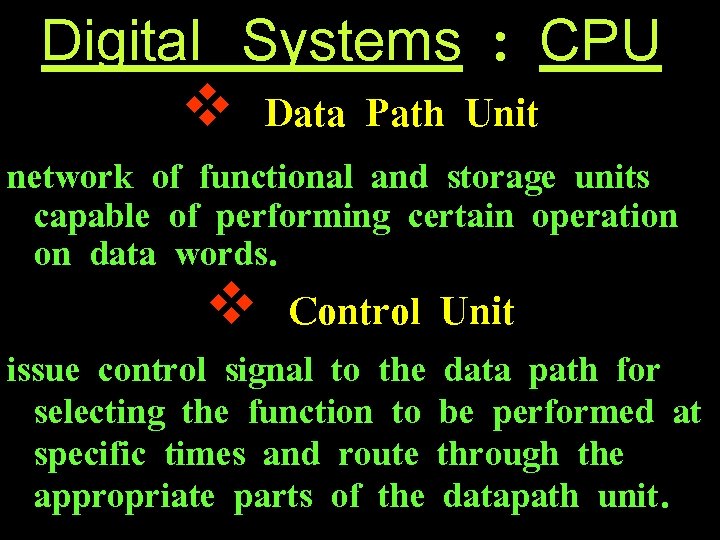

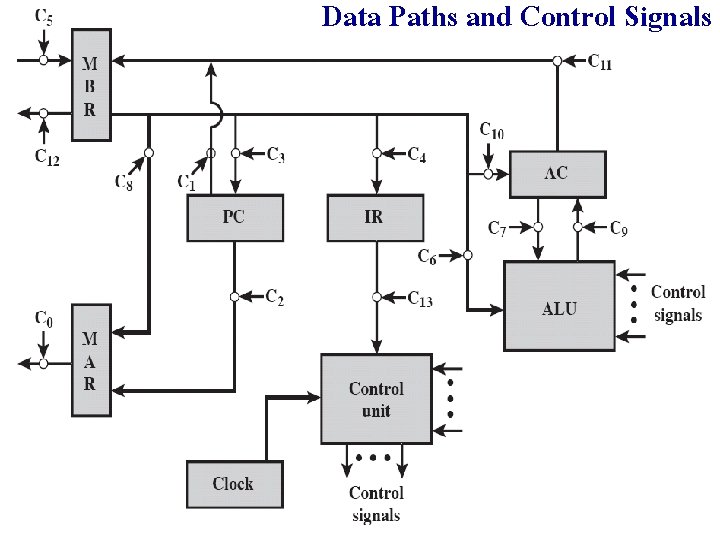

Digital Systems : CPU v Data Path Unit network of functional and storage units capable of performing certain operation on data words. v Control Unit issue control signal to the data path for selecting the function to be performed at specific times and route through the appropriate parts of the datapath unit.

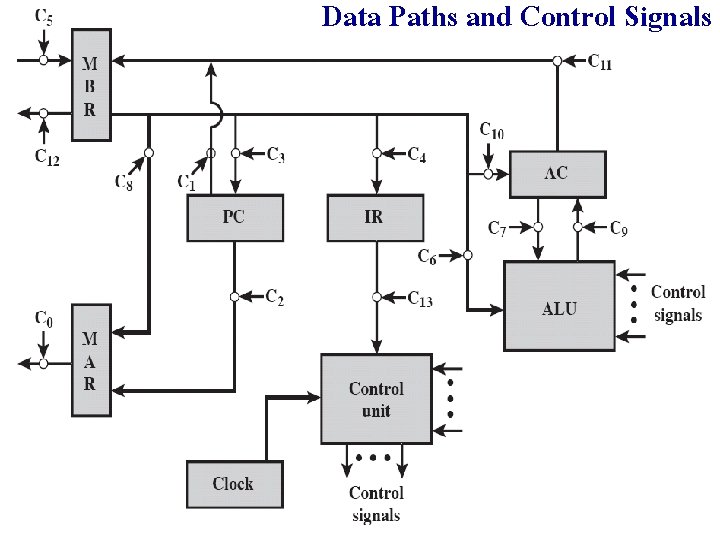

Data Paths and Control Signals

Digital Systems : CPU A Hardwired fixed logic circuits to generate the control signals. A Microprogrammed stores the control signals in sequence of micro-instructions (microprograms) microprograms in a control memory. *provide a systematic & flexible method*

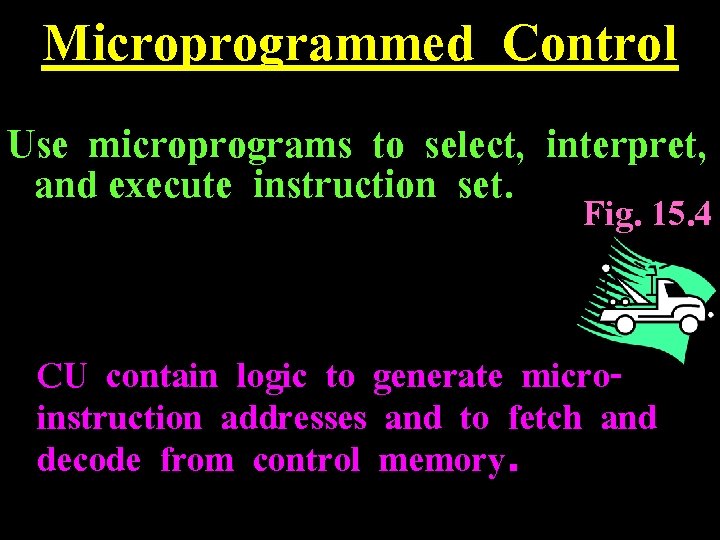

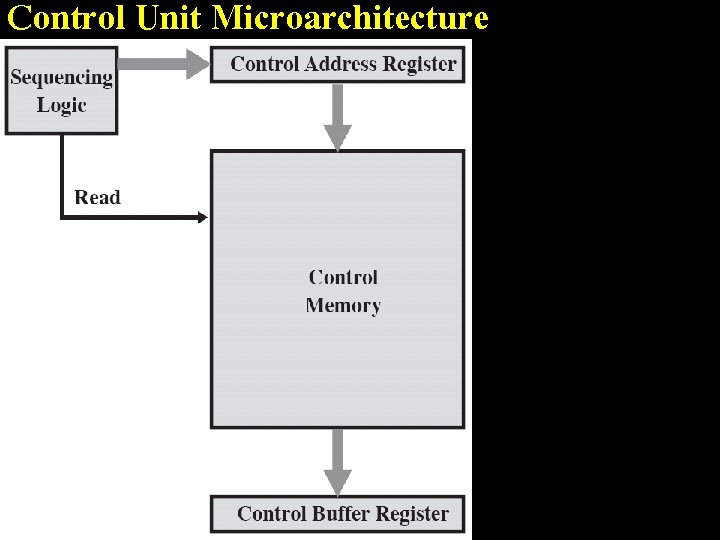

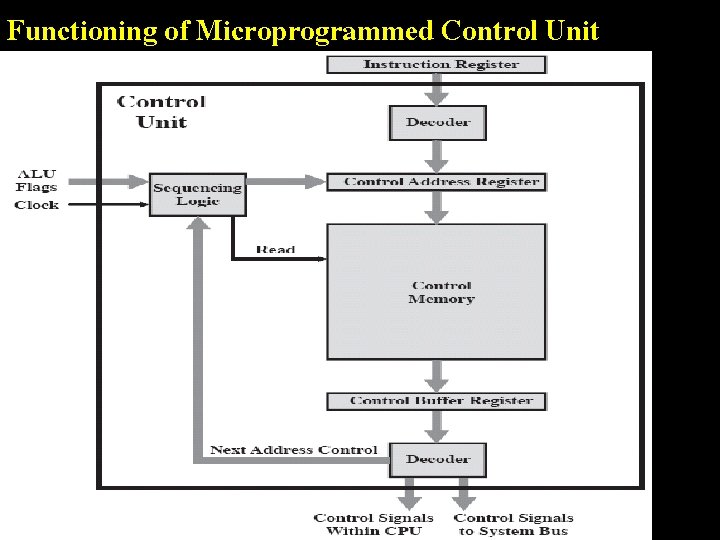

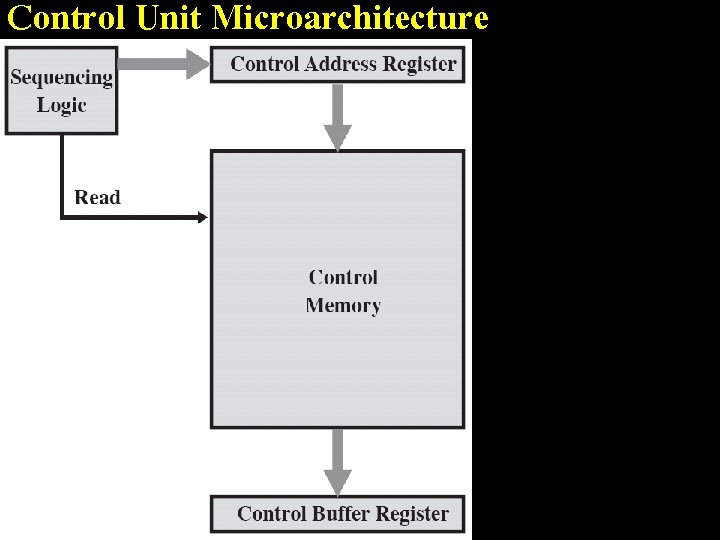

Microprogrammed Control Use microprograms to select, interpret, and execute instruction set. Fig. 15. 4 CU contain logic to generate microinstruction addresses and to fetch and decode from control memory.

Control Unit Microarchitecture

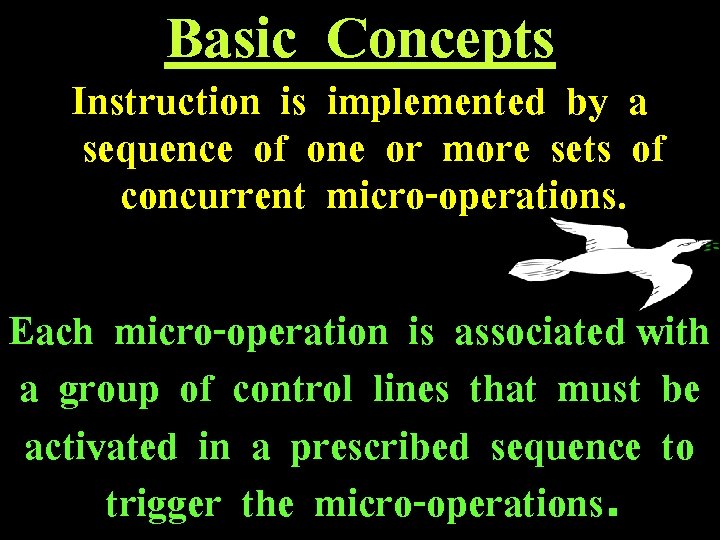

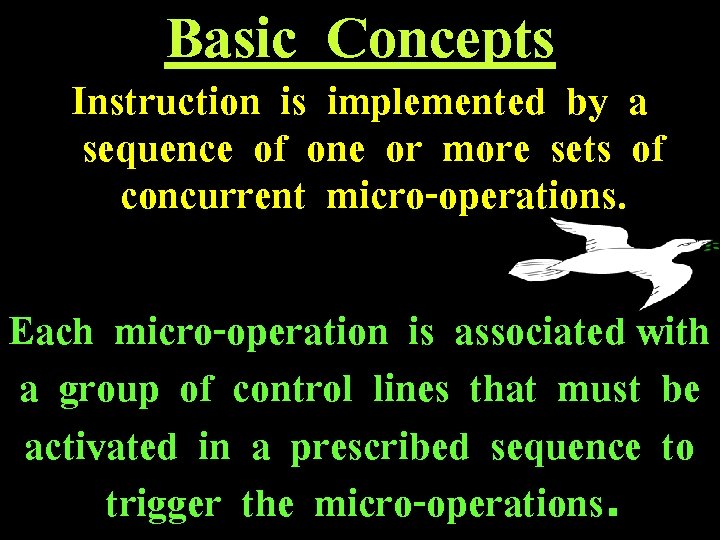

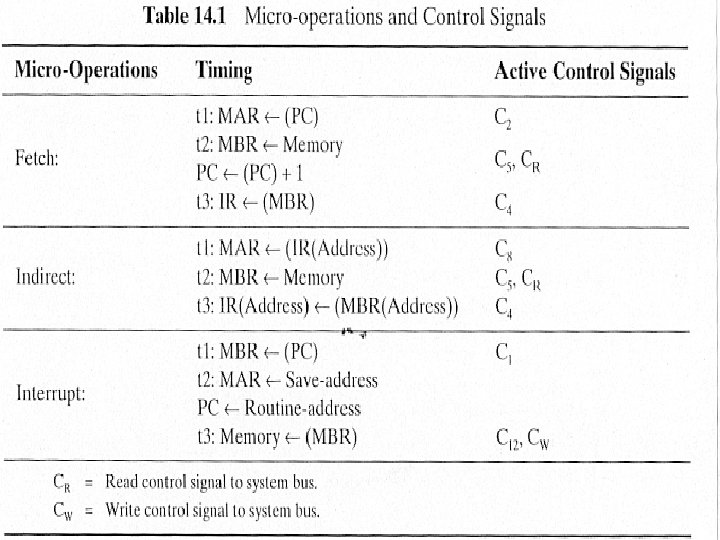

Basic Concepts Instruction is implemented by a sequence of one or more sets of concurrent micro-operations. Each micro-operation is associated with a group of control lines that must be activated in a prescribed sequence to trigger the micro-operations.

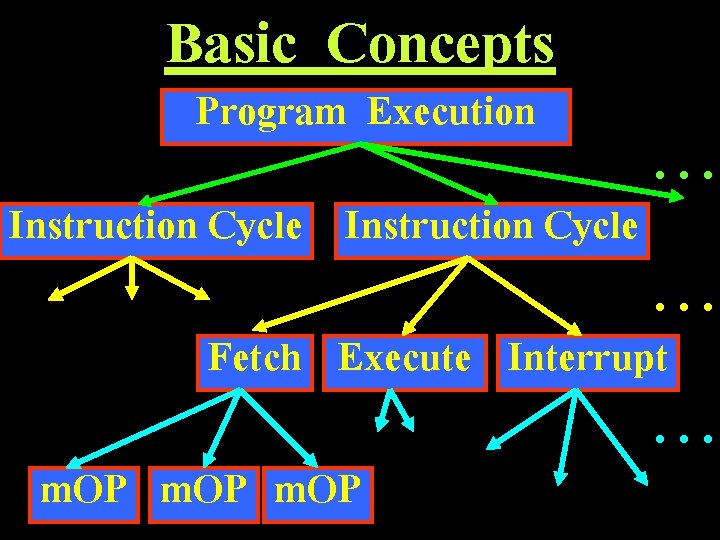

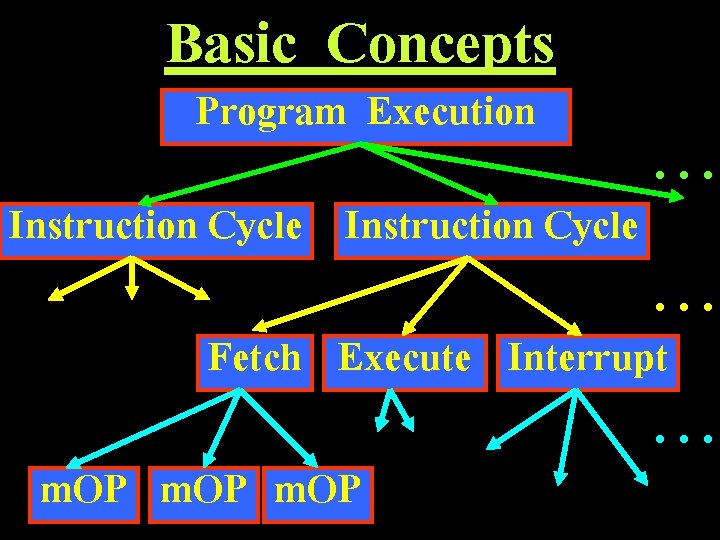

Basic Concepts Program Execution Instruction Cycle . . . Fetch Execute Interrupt m. OP . . .

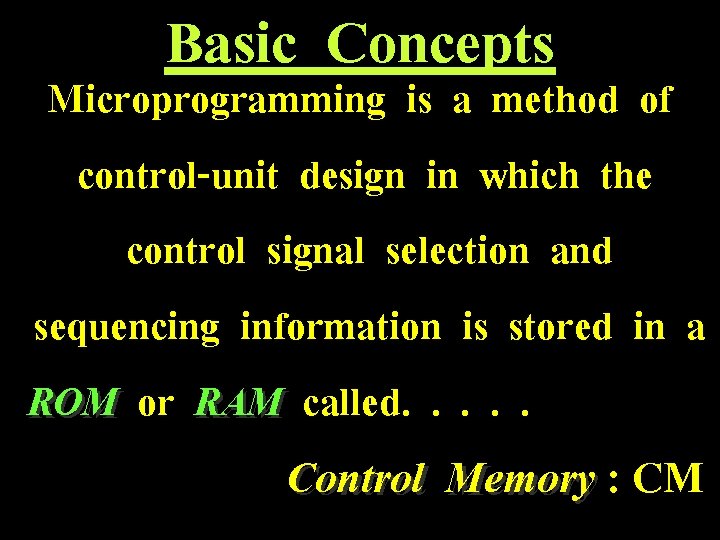

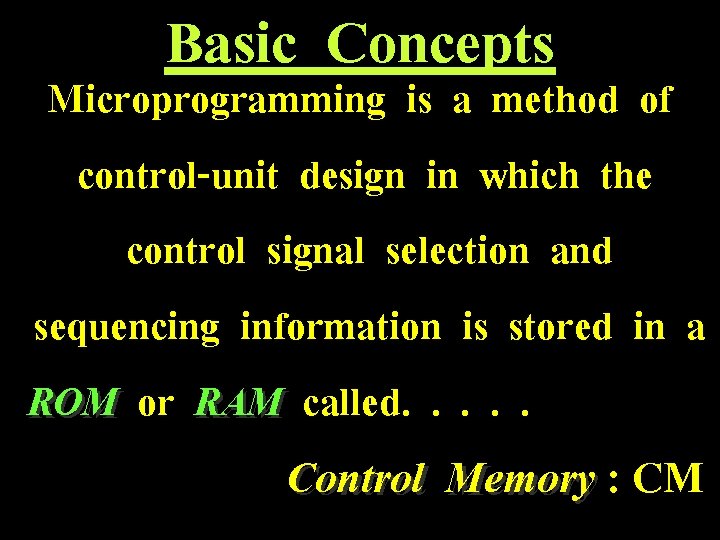

Basic Concepts Microprogramming is a method of control-unit design in which the control signal selection and sequencing information is stored in a ROM or RAM called. . . Control Memory : CM

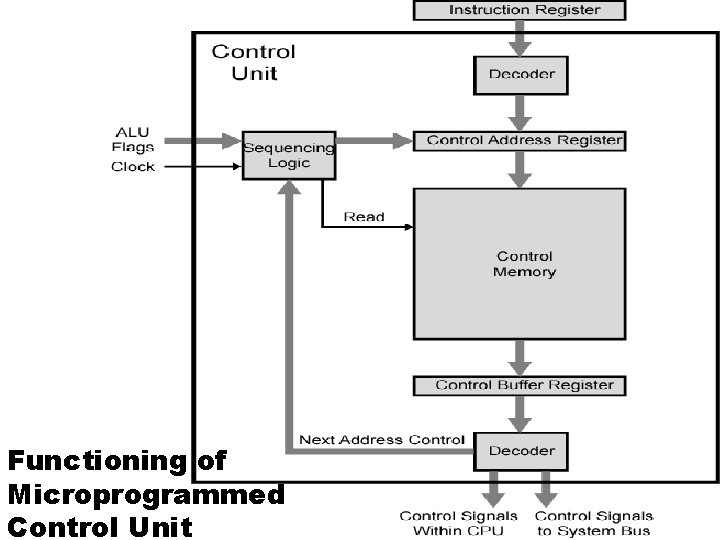

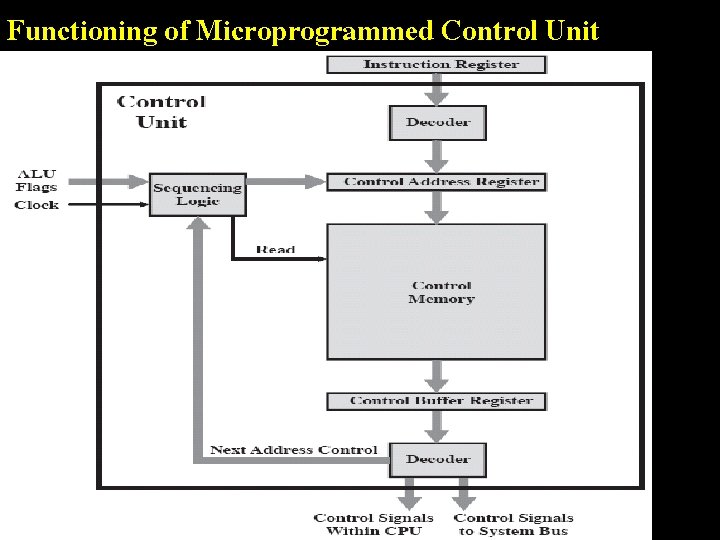

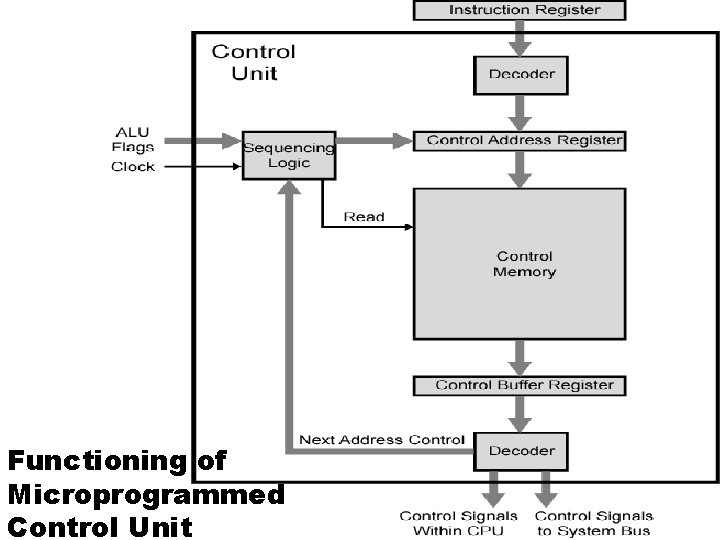

Functioning of Microprogrammed Control Unit

Basic Concepts The control signals could be activated at any time that are specified by a microinstruction, which is fetched from CM in much the same way an instruction is fetched from main memory.

Basic Concepts Instruction Cycle • Fetch • Indirect • Execute • Interrupt

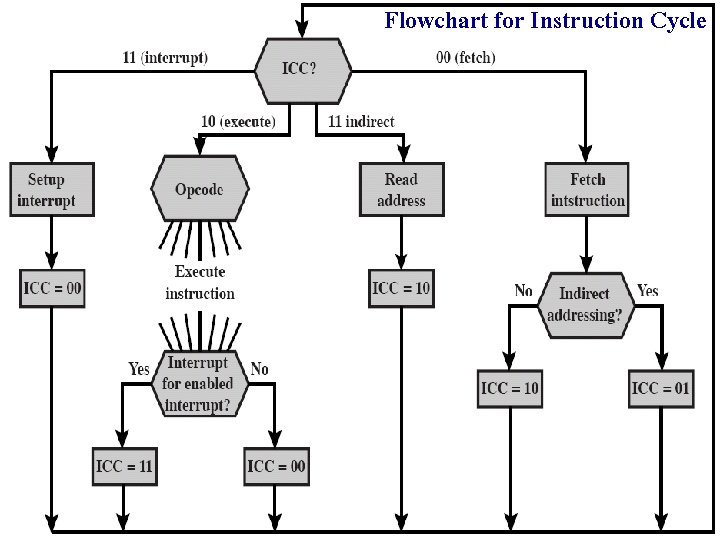

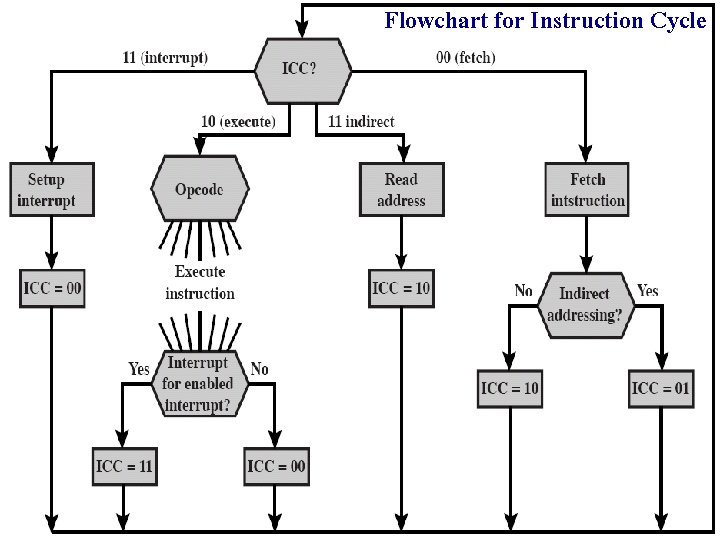

Flowchart for Instruction Cycle

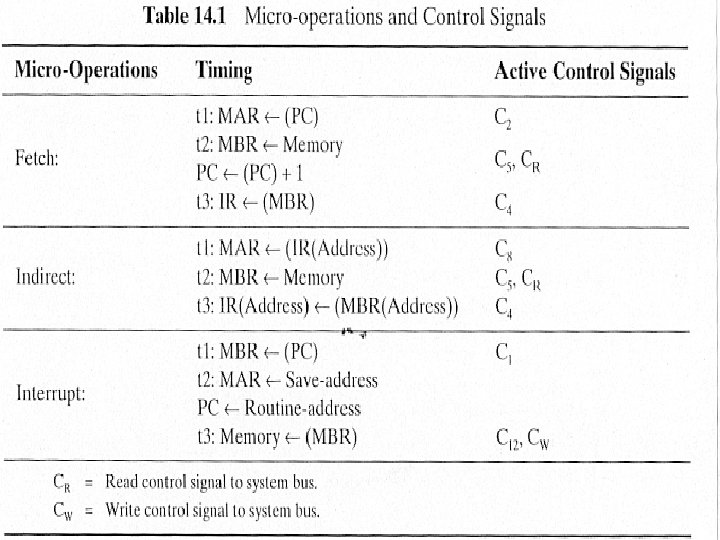

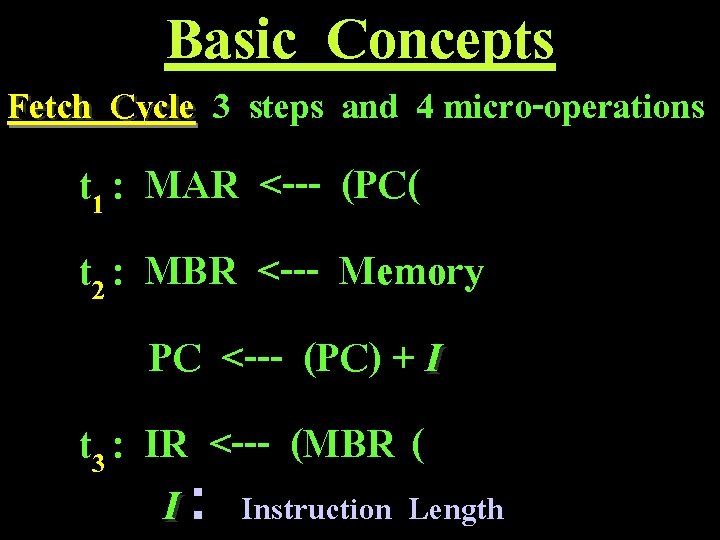

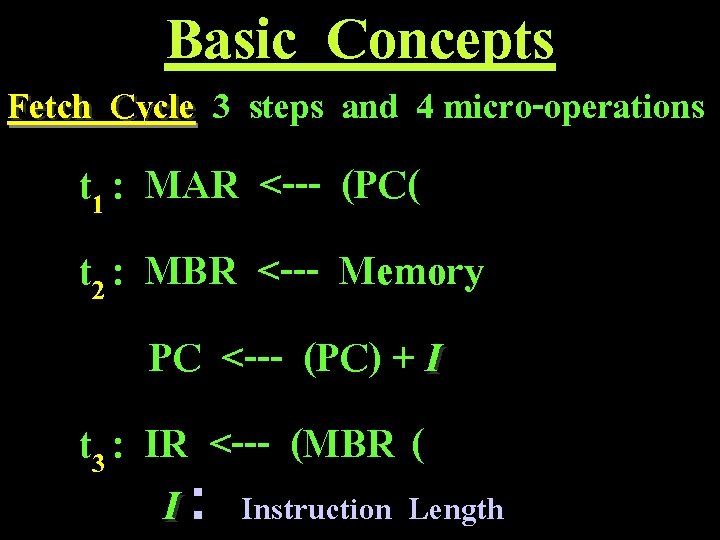

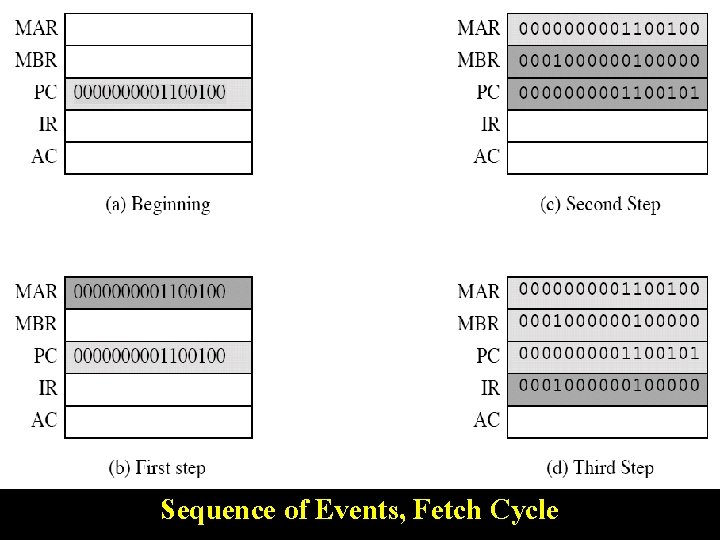

Basic Concepts Fetch Cycle 3 steps and 4 micro-operations t 1 : MAR <--- (PC( t 2 : MBR <--- Memory PC <--- (PC) + I t 3 : IR <--- (MBR ( I : Instruction Length

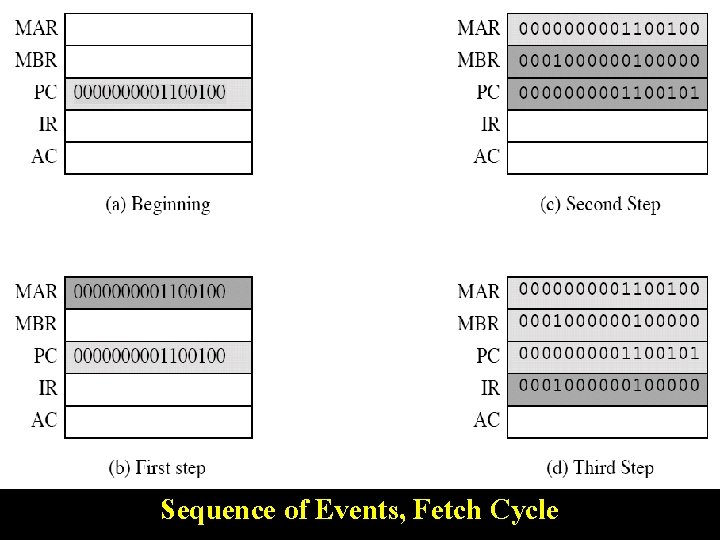

Sequence of Events, Fetch Cycle

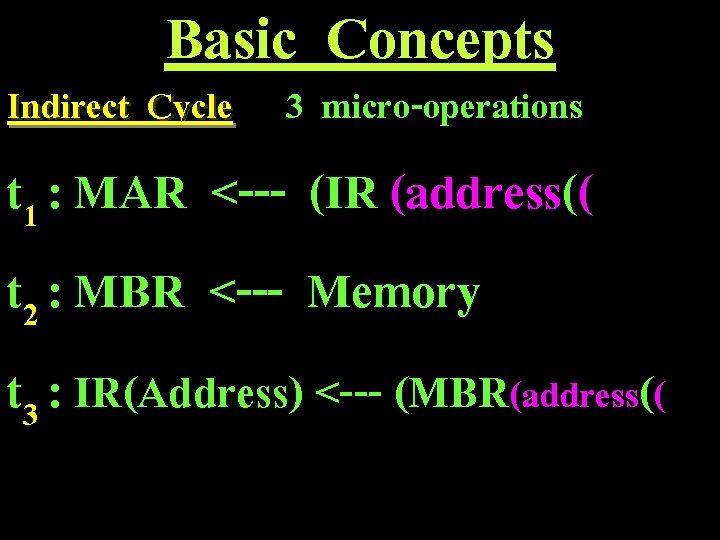

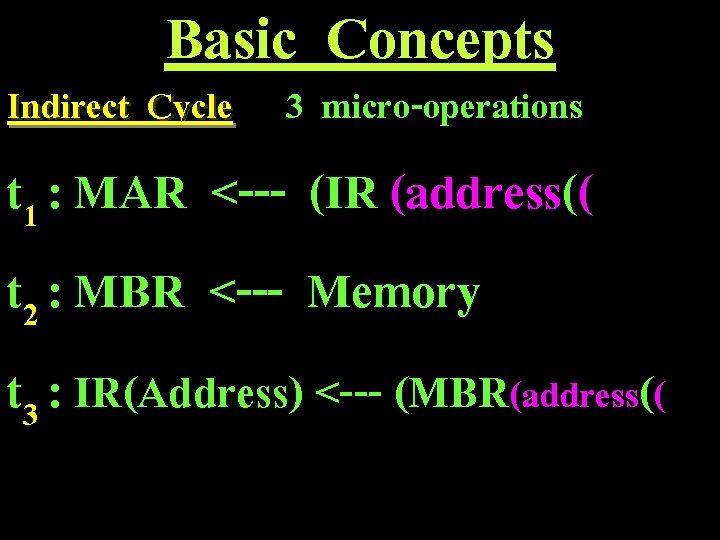

Basic Concepts Indirect Cycle 3 micro-operations t 1 : MAR <--- (IR (address(( t 2 : MBR <--- Memory t 3 : IR(Address) <--- (MBR(address((

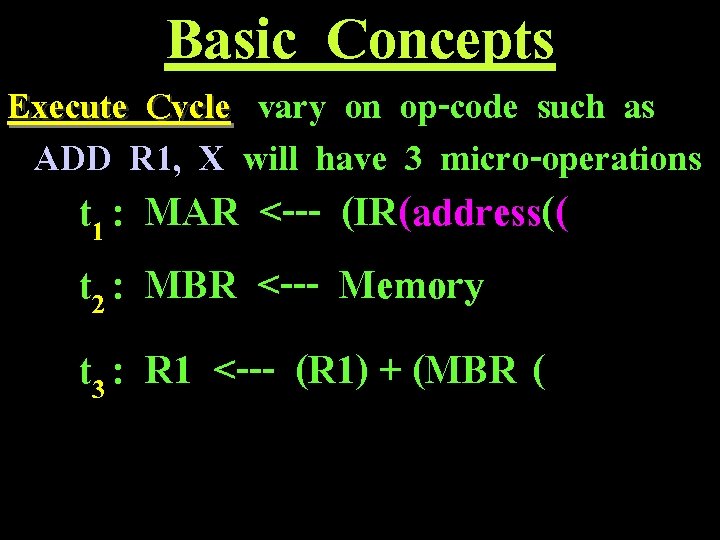

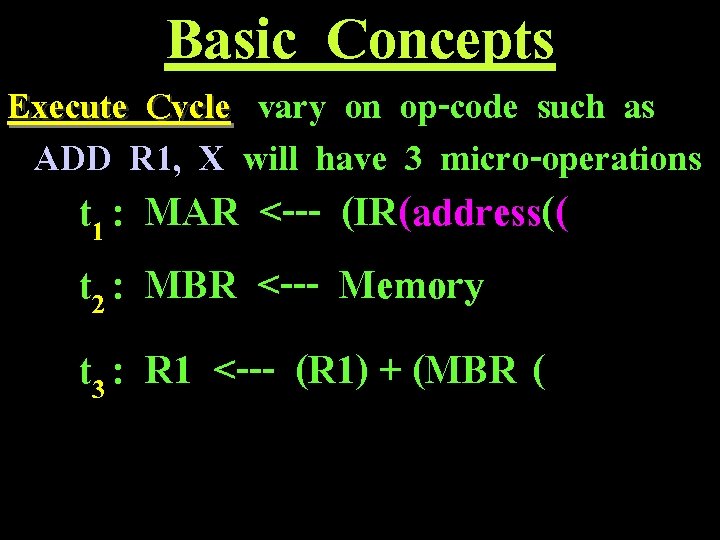

Basic Concepts Execute Cycle vary on op-code such as ADD R 1, X will have 3 micro-operations t 1 : MAR <--- (IR(address(( t 2 : MBR <--- Memory t 3 : R 1 <--- (R 1) + (MBR (

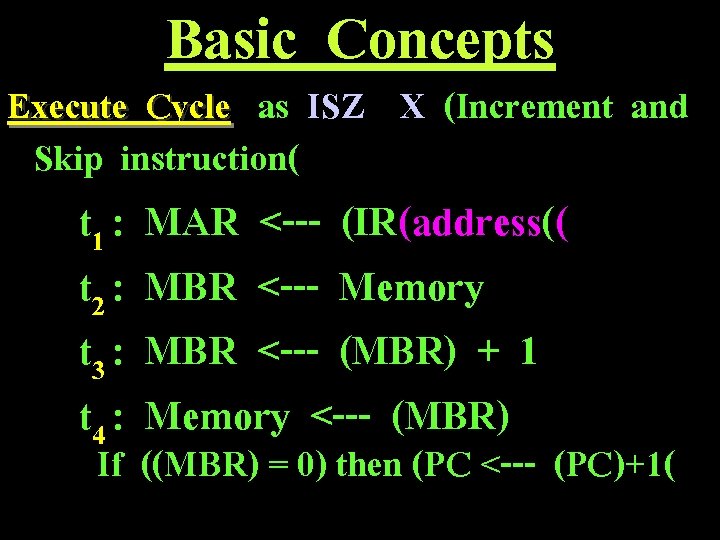

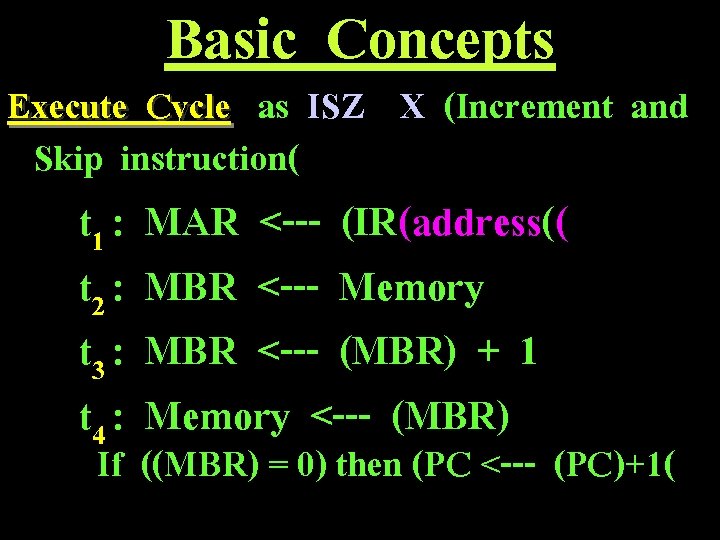

Basic Concepts Execute Cycle as ISZ X (Increment and Skip instruction( t 1 : t 2 : t 3 : t 4 : MAR <--- (IR(address(( MBR <--- Memory MBR <--- (MBR) + 1 Memory <--- (MBR) If ((MBR) = 0) then (PC <--- (PC)+1(

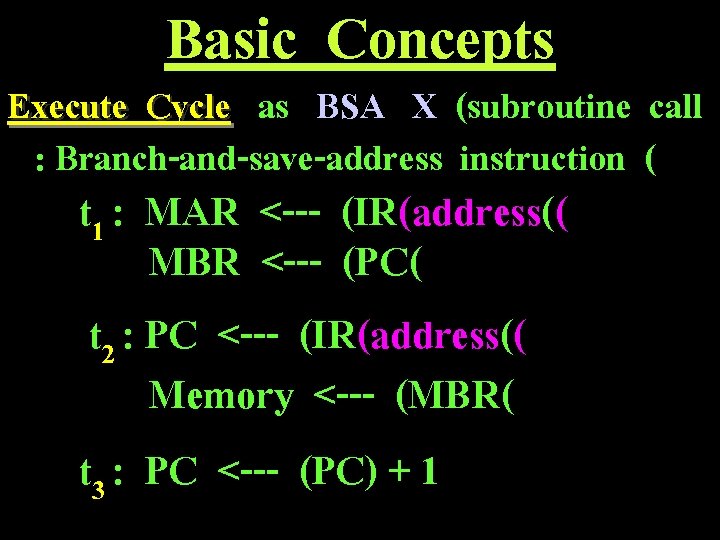

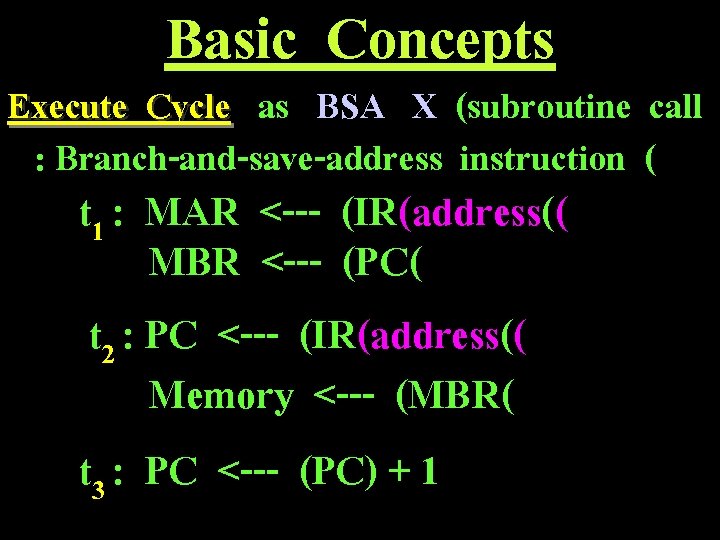

Basic Concepts Execute Cycle as BSA X (subroutine call : Branch-and-save-address instruction ( t 1 : MAR <--- (IR(address(( MBR <--- (PC( t 2 : PC <--- (IR(address(( Memory <--- (MBR( t 3 : PC <--- (PC) + 1

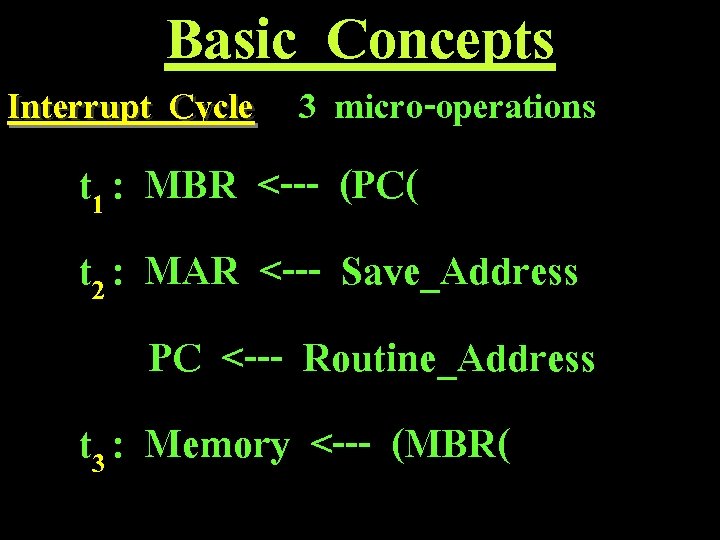

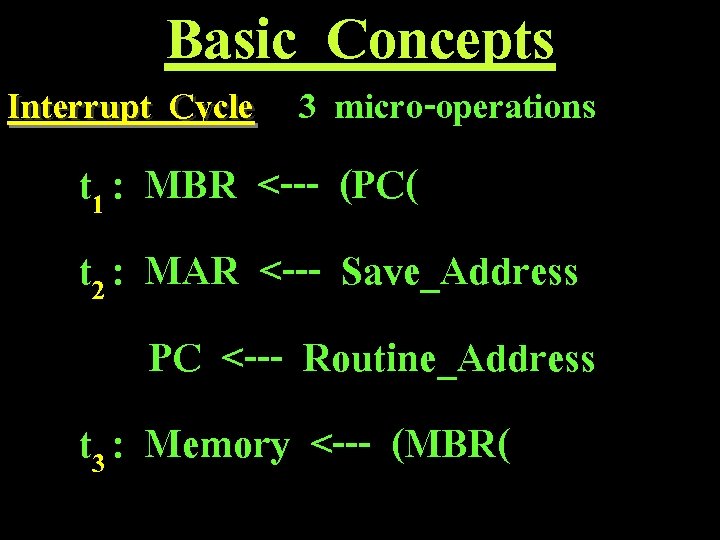

Basic Concepts Interrupt Cycle 3 micro-operations t 1 : MBR <--- (PC( t 2 : MAR <--- Save_Address PC <--- Routine_Address t 3 : Memory <--- (MBR(

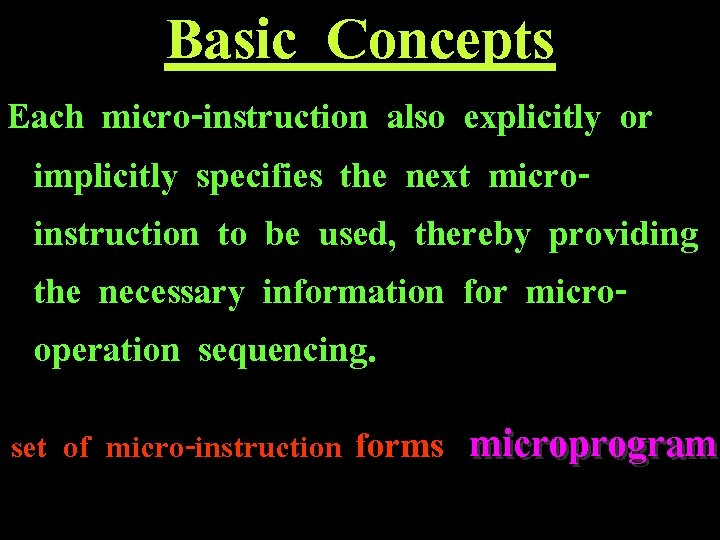

Basic Concepts Each micro-instruction also explicitly or implicitly specifies the next microinstruction to be used, thereby providing the necessary information for microoperation sequencing. set of micro-instruction forms microprogram

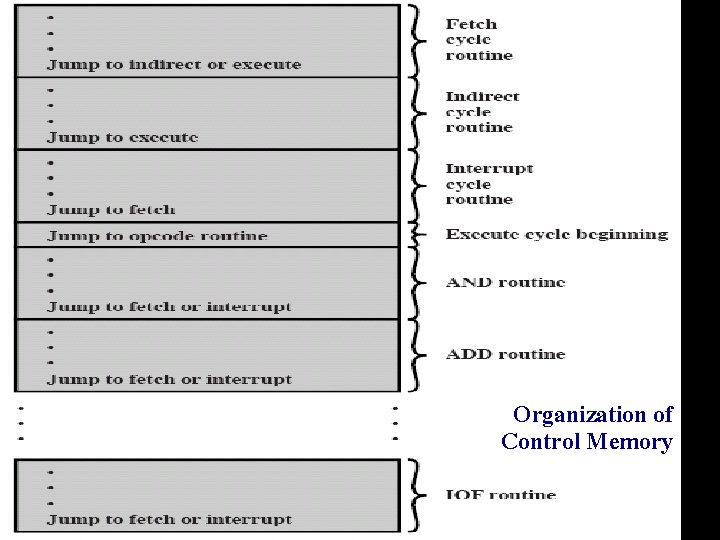

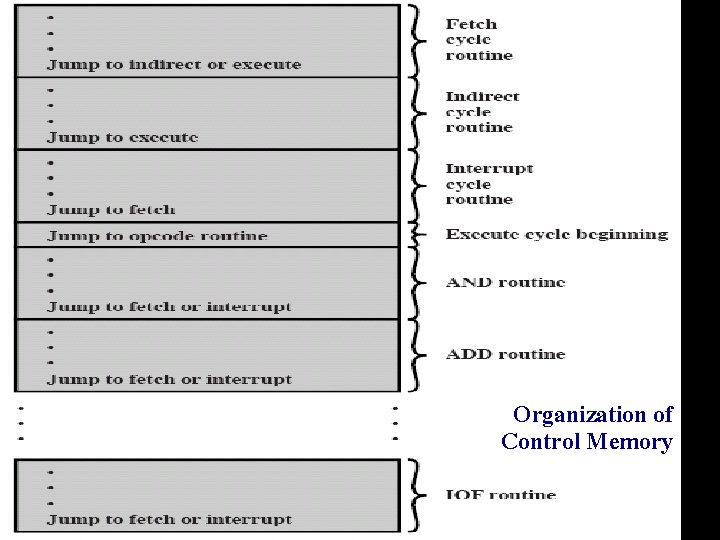

Organization of Control Memory

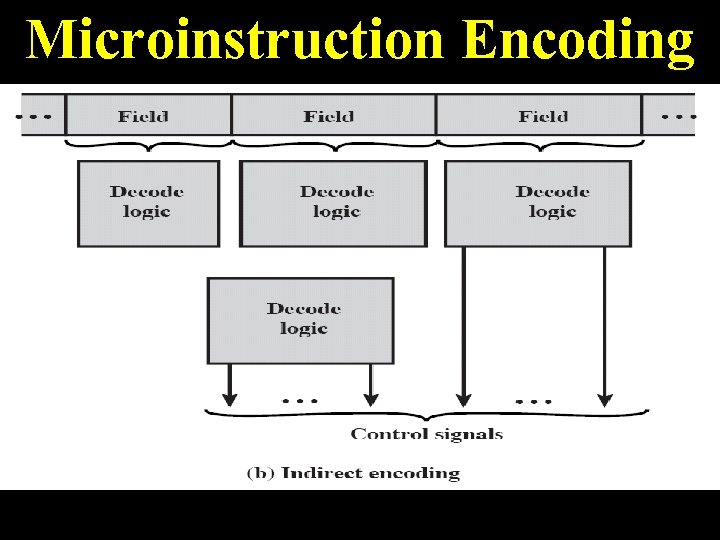

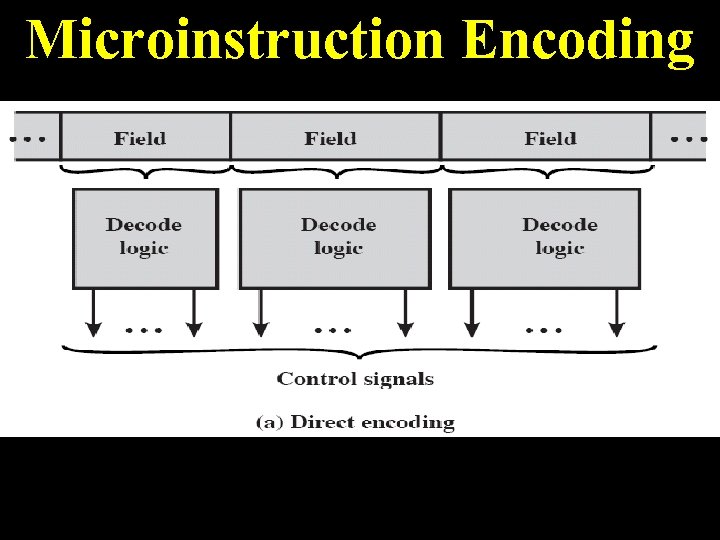

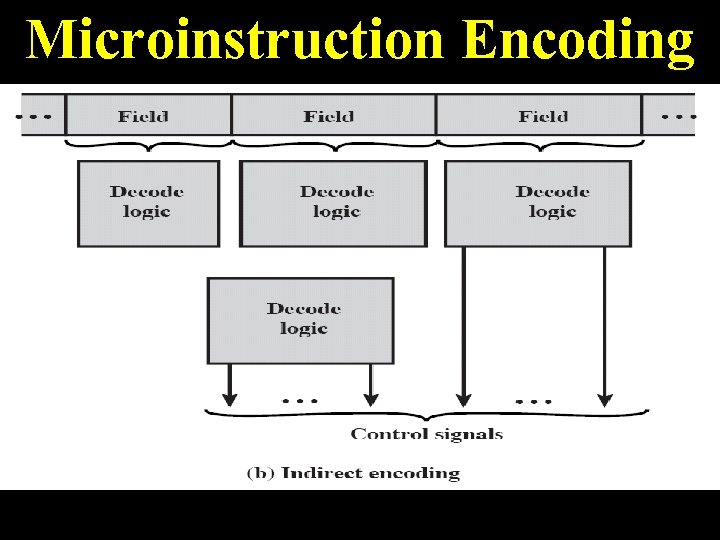

Microinstruction Encoding

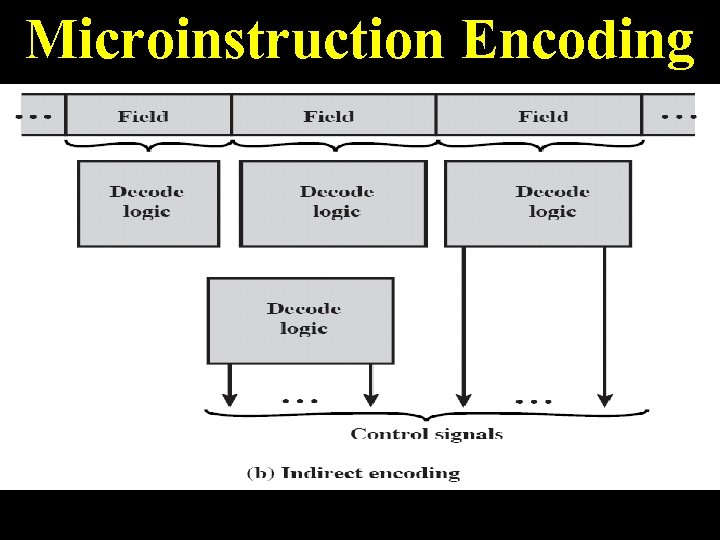

Microinstruction Encoding

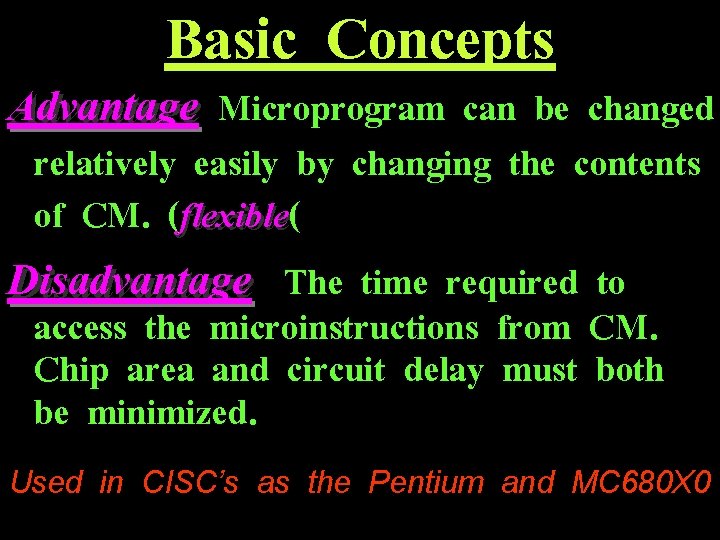

Basic Concepts Advantage Microprogram can be changed relatively easily by changing the contents of CM. (flexible( flexible Disadvantage The time required to access the microinstructions from CM. Chip area and circuit delay must both be minimized. Used in CISC’s as the Pentium and MC 680 X 0

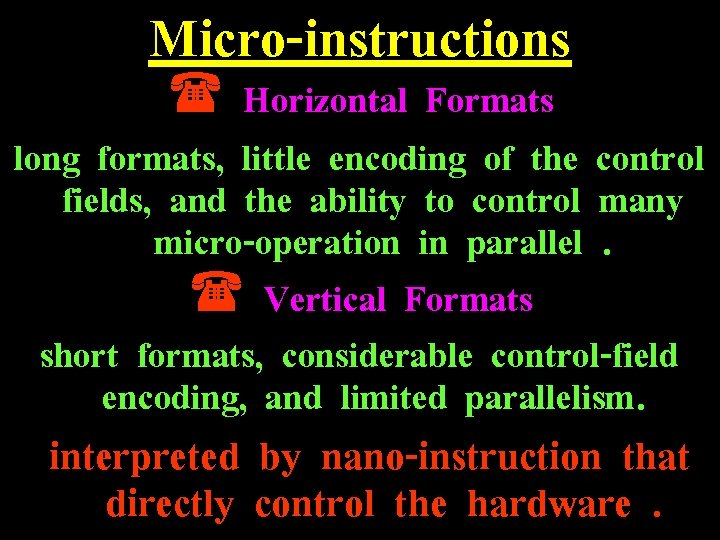

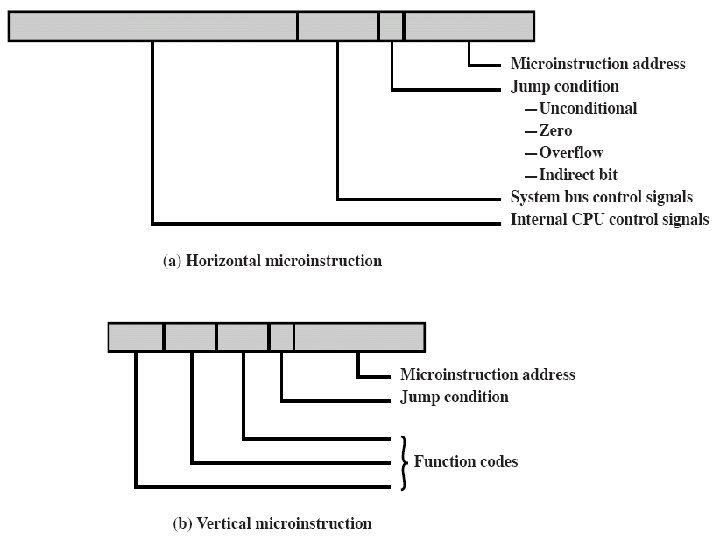

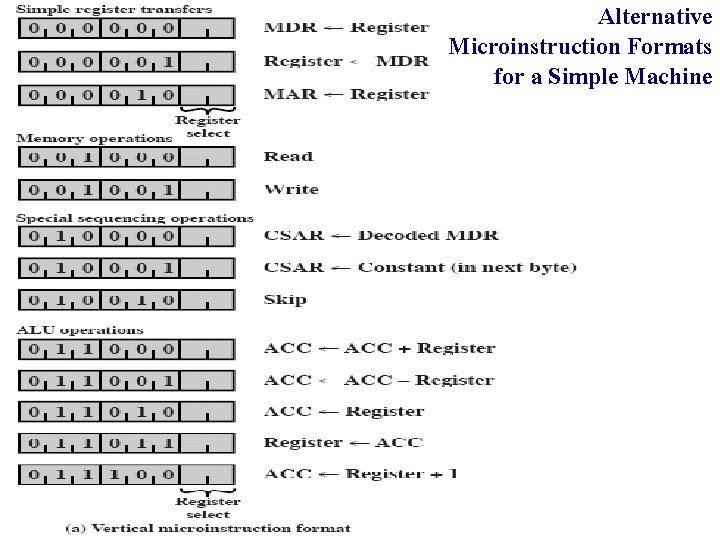

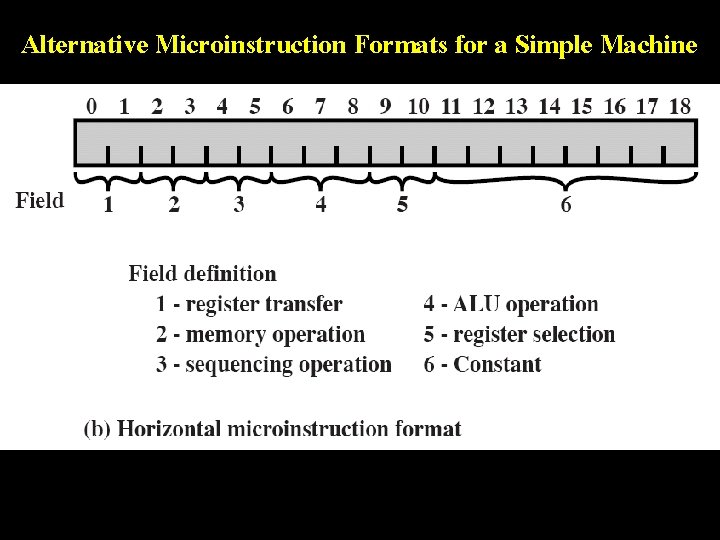

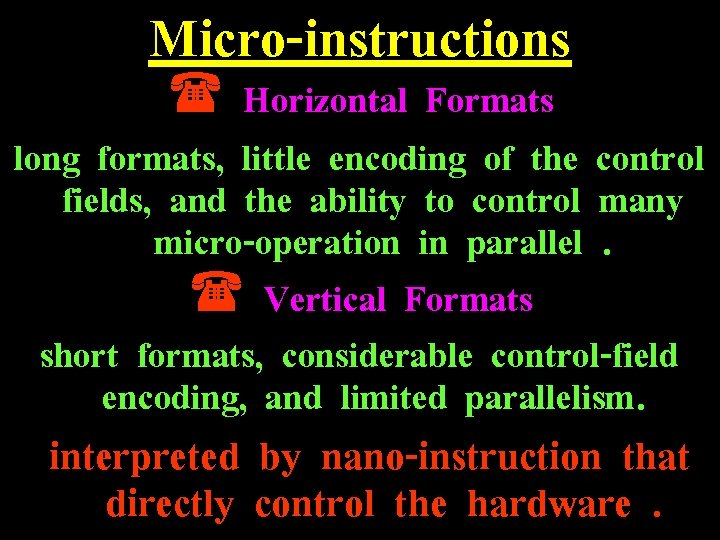

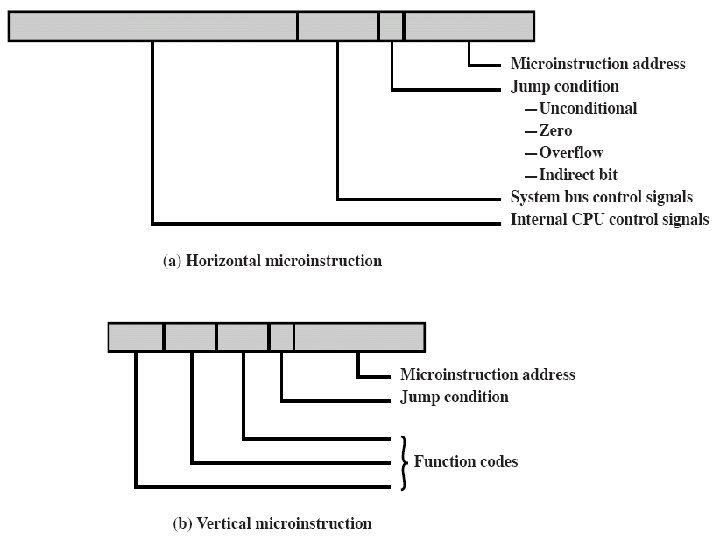

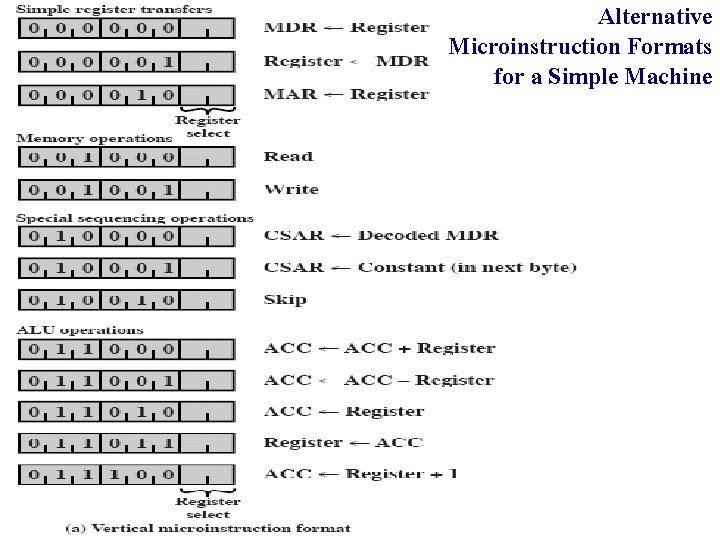

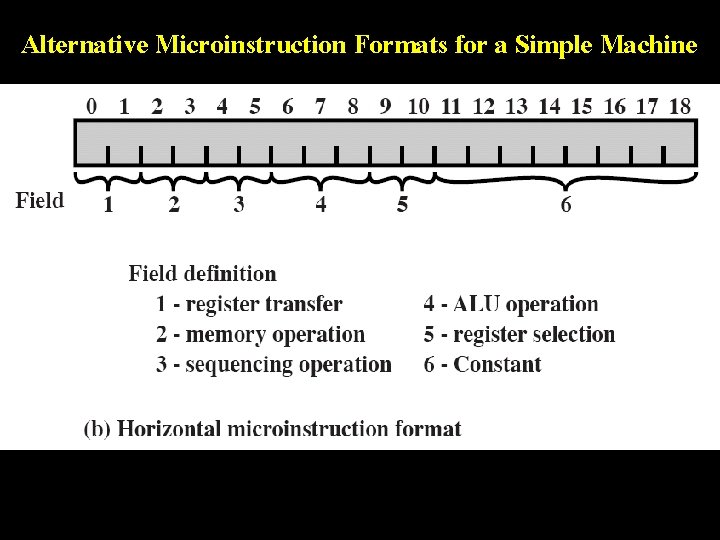

Micro-instructions ( Horizontal Formats long formats, little encoding of the control fields, and the ability to control many micro-operation in parallel. ( Vertical Formats short formats, considerable control-field encoding, and limited parallelism. interpreted by nano-instruction that directly control the hardware.

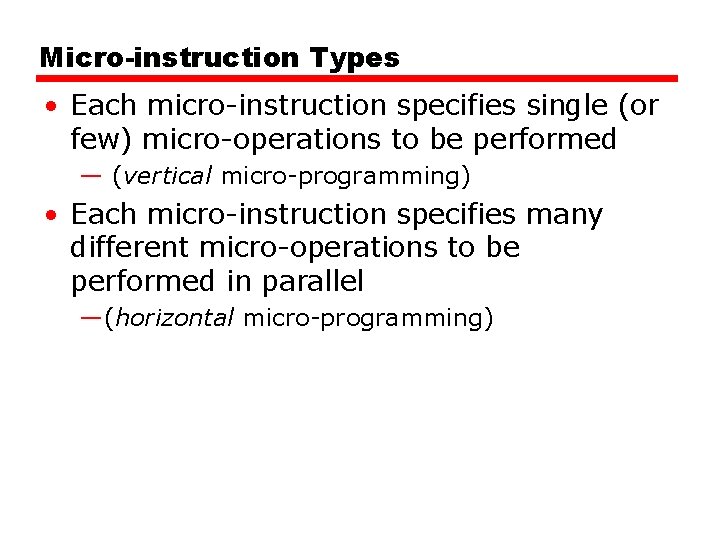

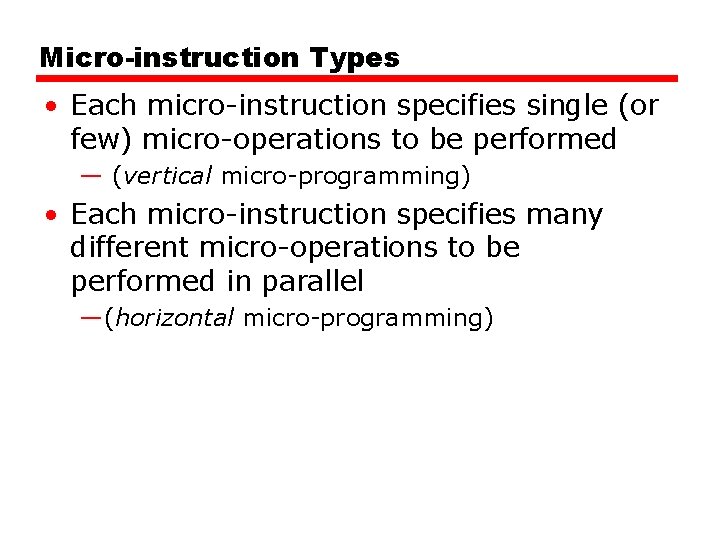

Micro-instruction Types • Each micro-instruction specifies single (or few) micro-operations to be performed — (vertical micro-programming) • Each micro-instruction specifies many different micro-operations to be performed in parallel —(horizontal micro-programming)

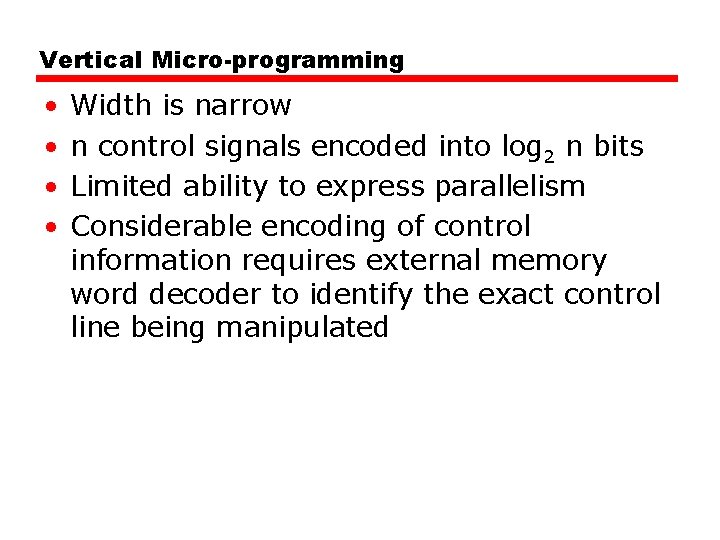

Vertical Micro-programming • • Width is narrow n control signals encoded into log 2 n bits Limited ability to express parallelism Considerable encoding of control information requires external memory word decoder to identify the exact control line being manipulated

Horizontal Micro-programming • Wide memory word • High degree of parallel operations possible • Little encoding of control information

Alternative Microinstruction Formats for a Simple Machine

Alternative Microinstruction Formats for a Simple Machine

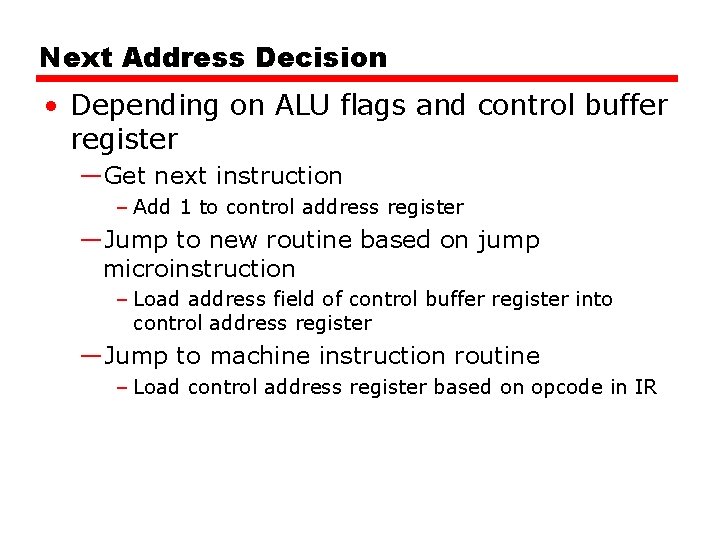

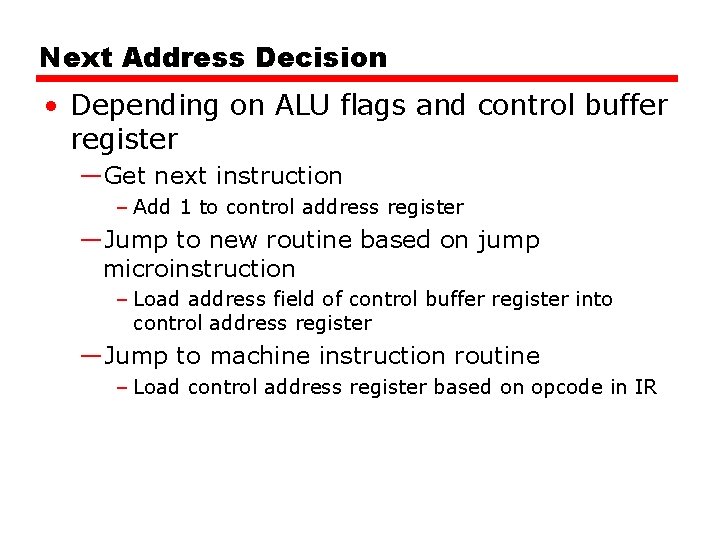

Next Address Decision • Depending on ALU flags and control buffer register —Get next instruction – Add 1 to control address register —Jump to new routine based on jump microinstruction – Load address field of control buffer register into control address register —Jump to machine instruction routine – Load control address register based on opcode in IR

Functioning of Microprogrammed Control Unit

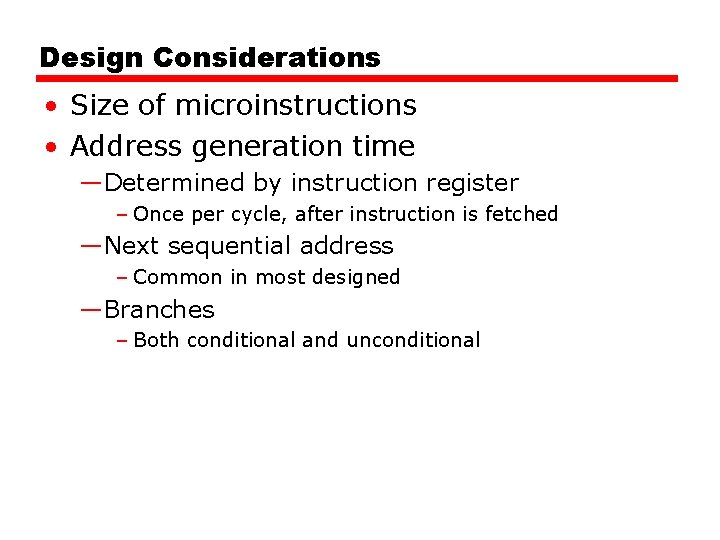

Design Considerations • Size of microinstructions • Address generation time —Determined by instruction register – Once per cycle, after instruction is fetched —Next sequential address – Common in most designed —Branches – Both conditional and unconditional

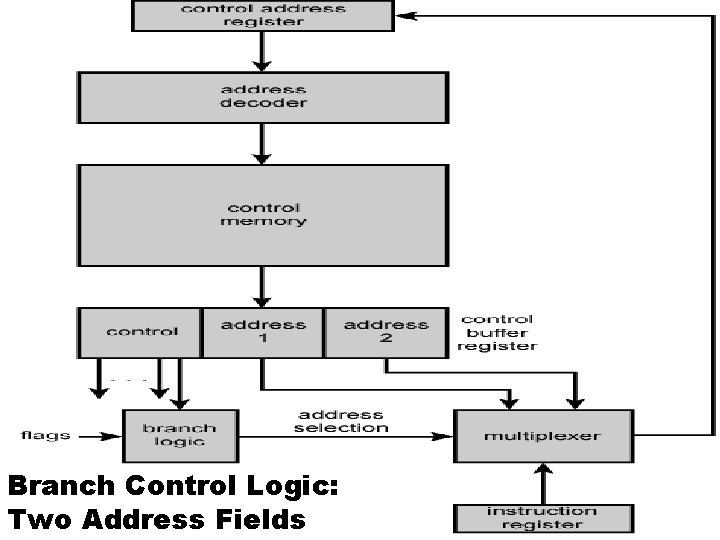

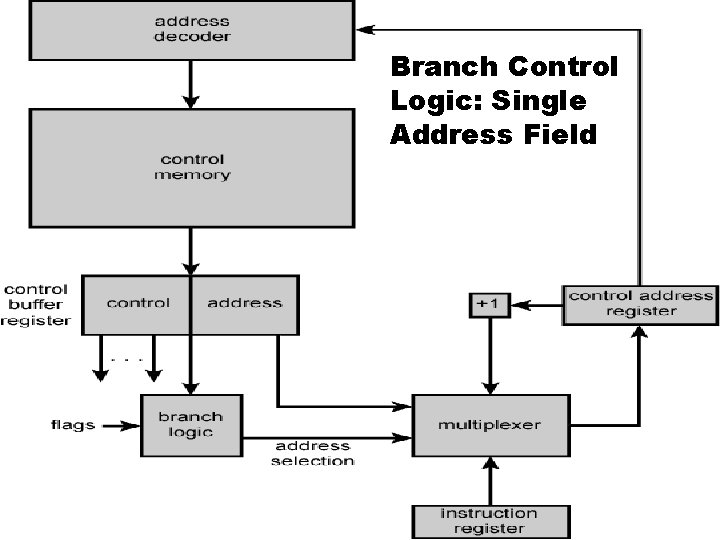

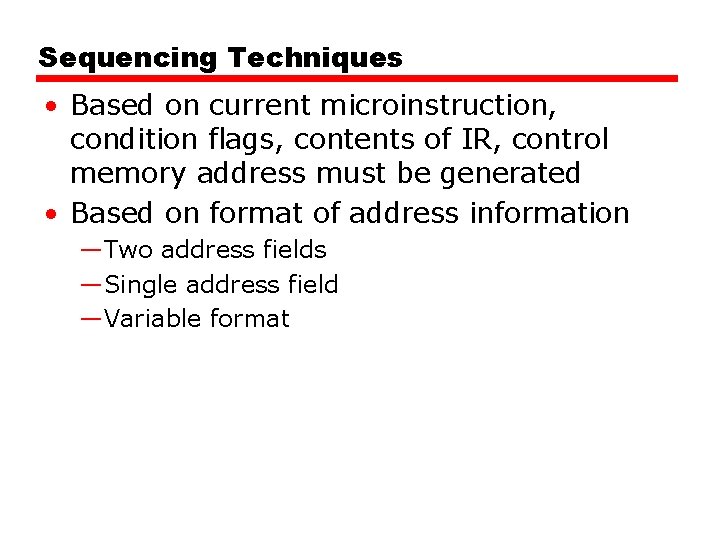

Sequencing Techniques • Based on current microinstruction, condition flags, contents of IR, control memory address must be generated • Based on format of address information —Two address fields —Single address field —Variable format

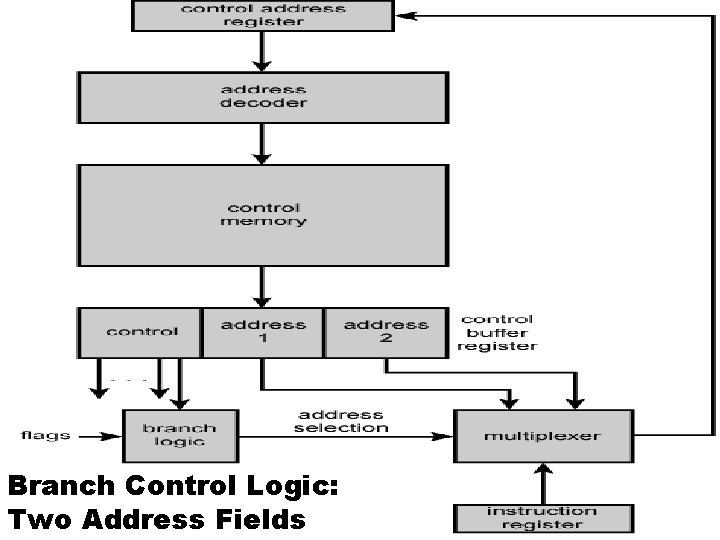

Branch Control Logic: Two Address Fields

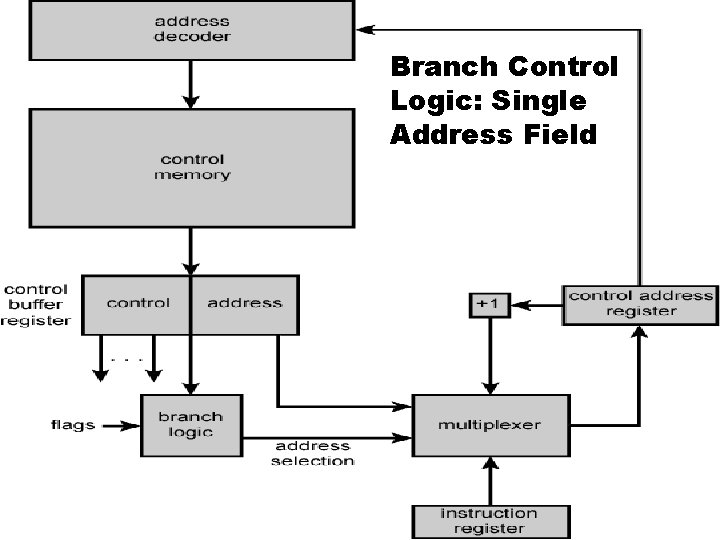

Branch Control Logic: Single Address Field

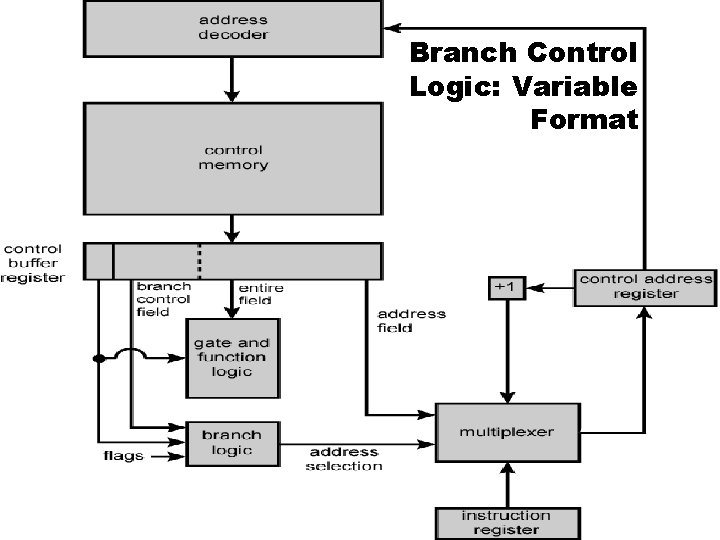

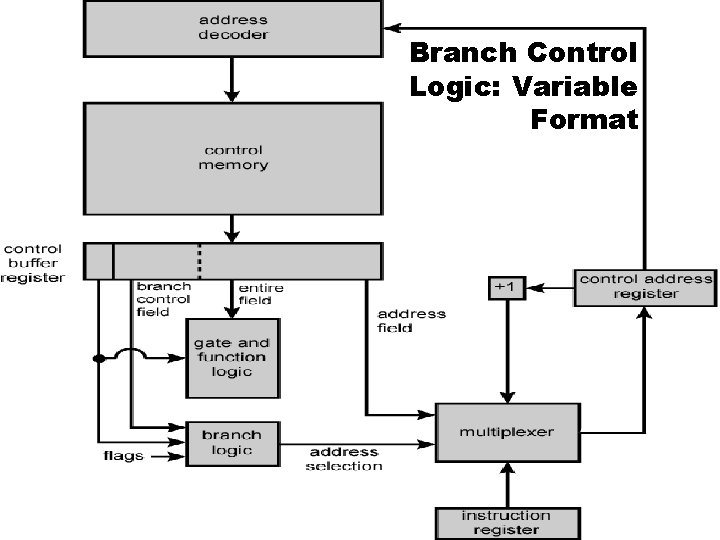

Branch Control Logic: Variable Format

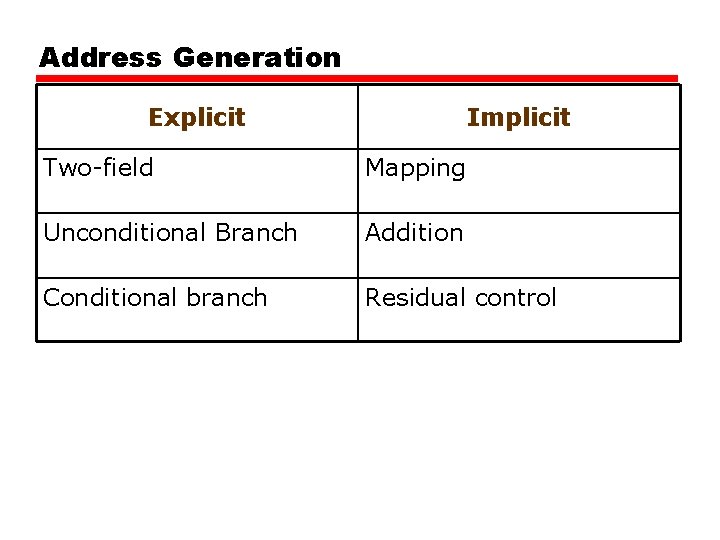

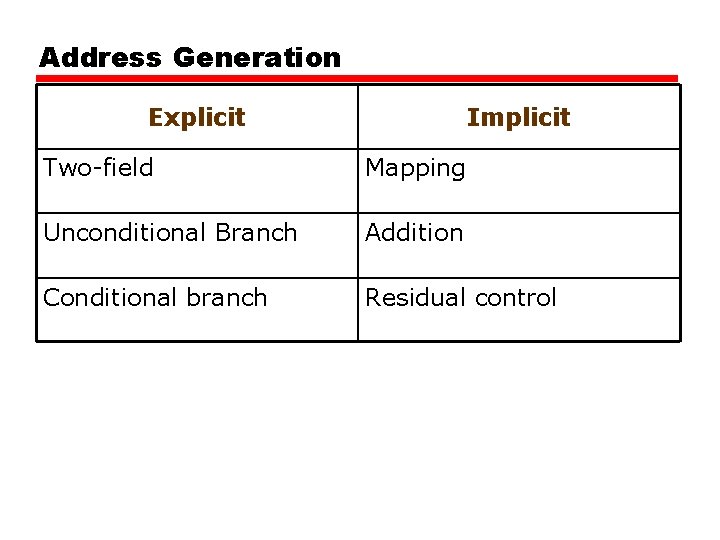

Address Generation Explicit Implicit Two-field Mapping Unconditional Branch Addition Conditional branch Residual control

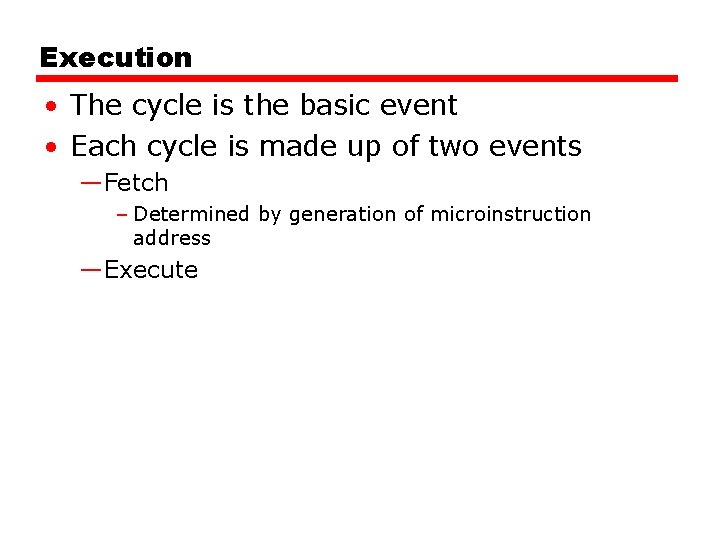

Execution • The cycle is the basic event • Each cycle is made up of two events —Fetch – Determined by generation of microinstruction address —Execute

Execute • Effect is to generate control signals • Some control points internal to processor • Rest go to external control bus or other interface

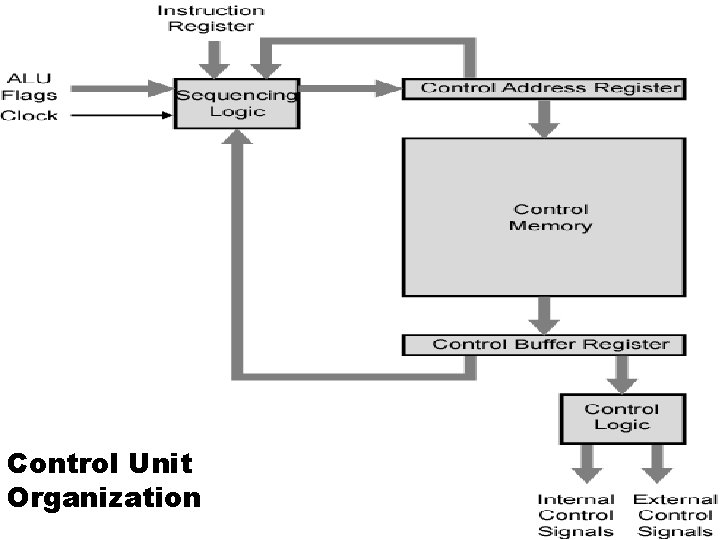

Control Unit Organization

A Taxonomy of Microinstructions • • Vertical/horizontal Packed/unpacked Hard/soft microprogramming Direct/indirect encoding

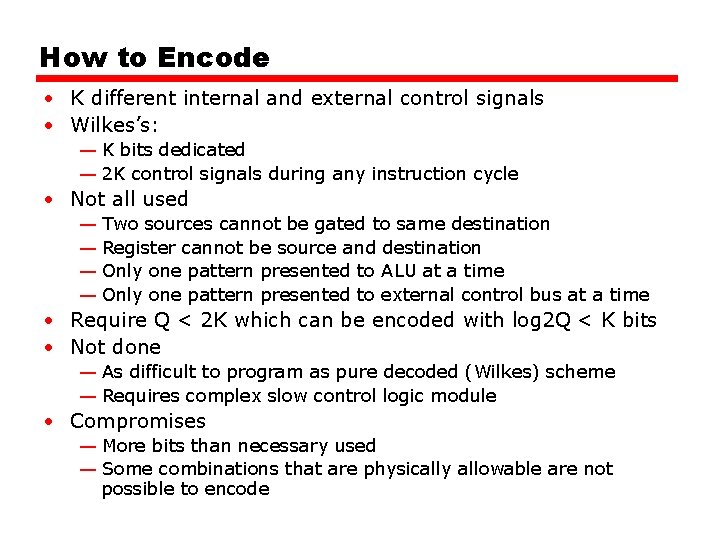

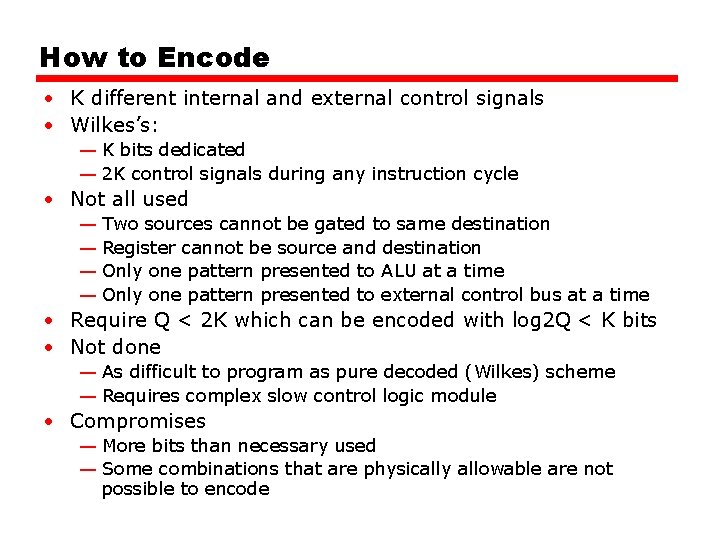

How to Encode • K different internal and external control signals • Wilkes’s: — K bits dedicated — 2 K control signals during any instruction cycle • Not all used — Two sources cannot be gated to same destination — Register cannot be source and destination — Only one pattern presented to ALU at a time — Only one pattern presented to external control bus at a time • Require Q < 2 K which can be encoded with log 2 Q < K bits • Not done — As difficult to program as pure decoded (Wilkes) scheme — Requires complex slow control logic module • Compromises — More bits than necessary used — Some combinations that are physically allowable are not possible to encode

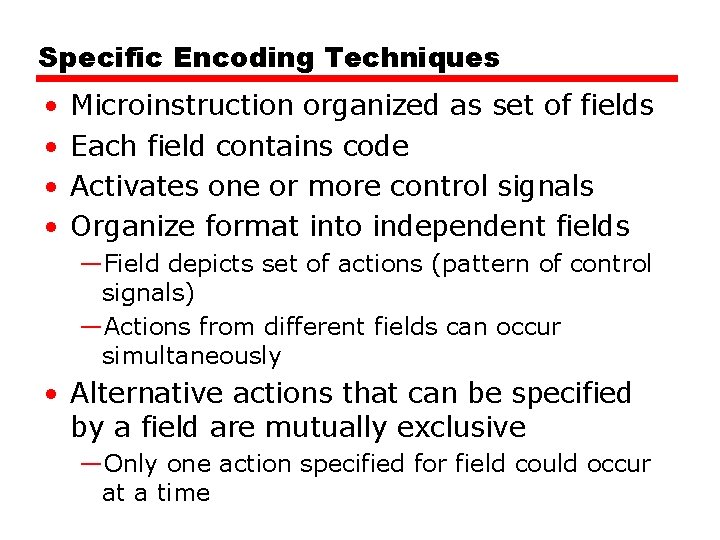

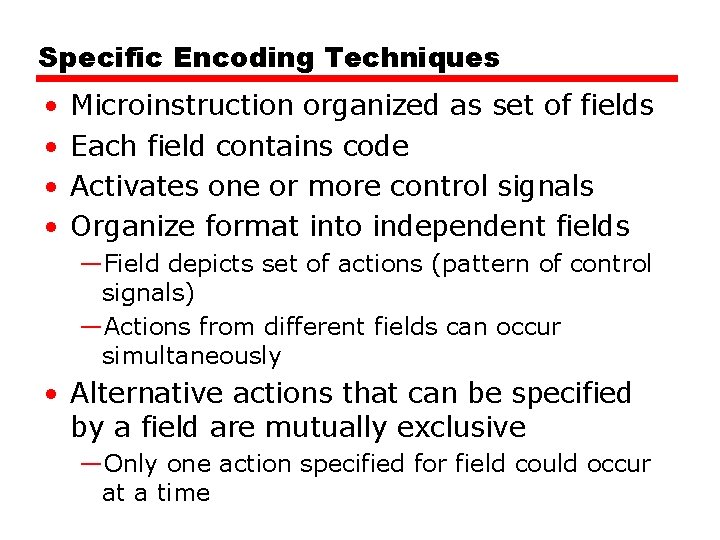

Specific Encoding Techniques • • Microinstruction organized as set of fields Each field contains code Activates one or more control signals Organize format into independent fields —Field depicts set of actions (pattern of control signals) —Actions from different fields can occur simultaneously • Alternative actions that can be specified by a field are mutually exclusive —Only one action specified for field could occur at a time

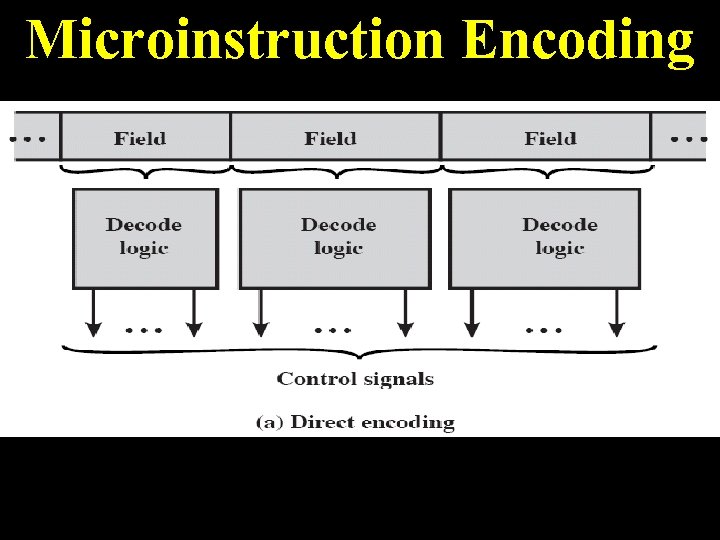

Microinstruction Encoding

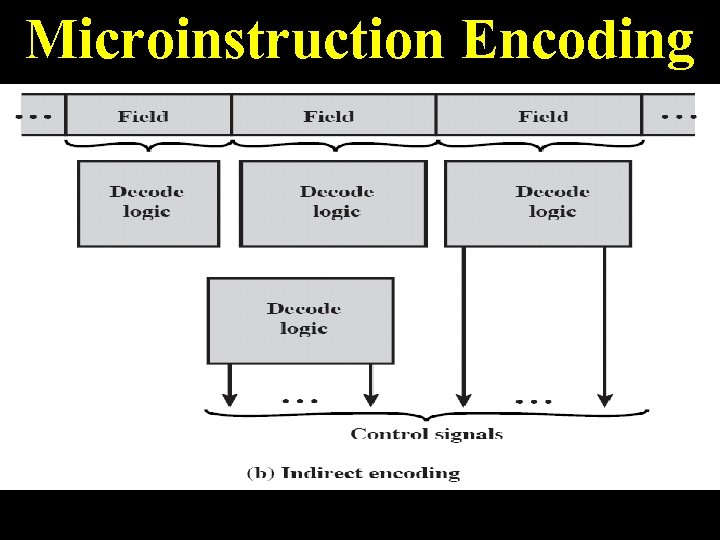

Microinstruction Encoding

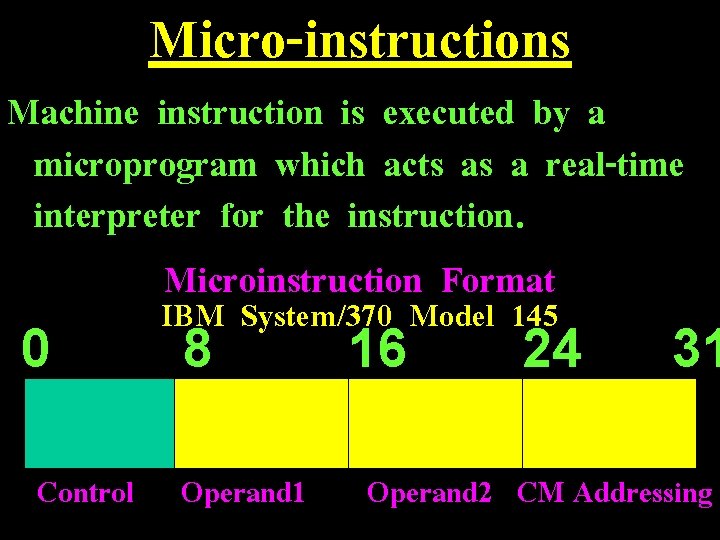

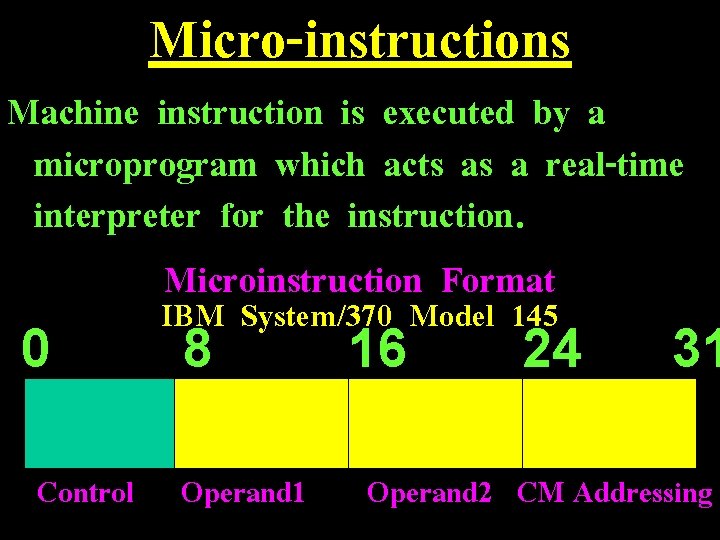

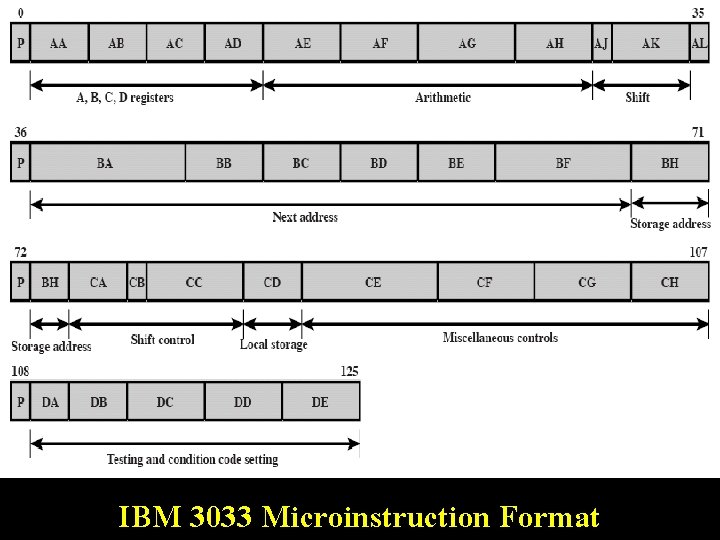

Micro-instructions Machine instruction is executed by a microprogram which acts as a real-time interpreter for the instruction. Microinstruction Format IBM System/370 Model 145 0 8 16 24 31 Control Operand 1 Operand 2 CM Addressing

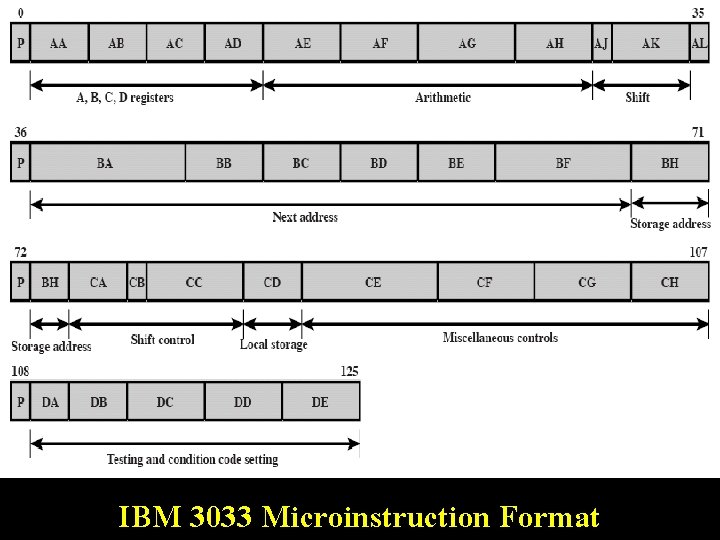

IBM 3033 Microinstruction Format

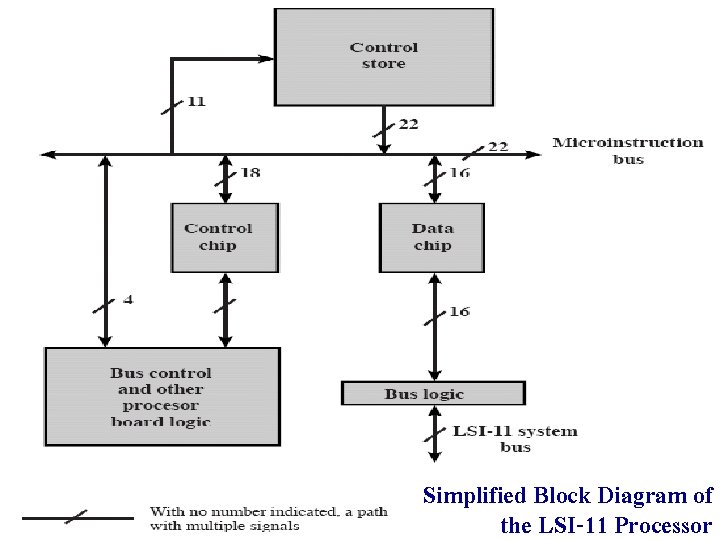

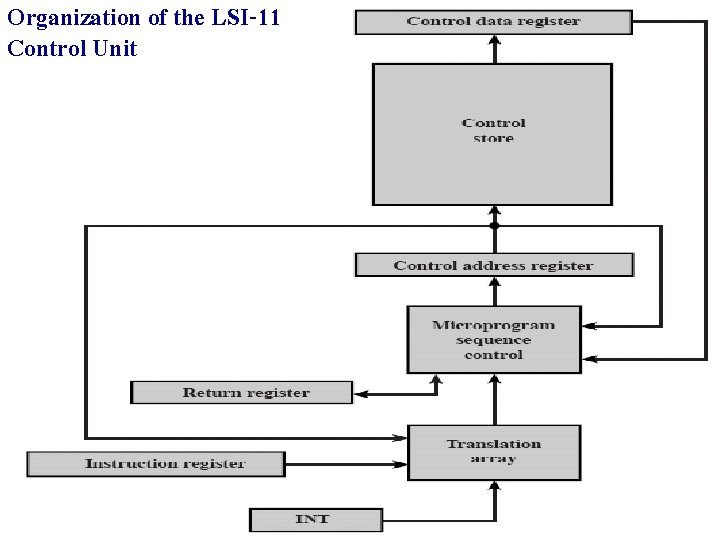

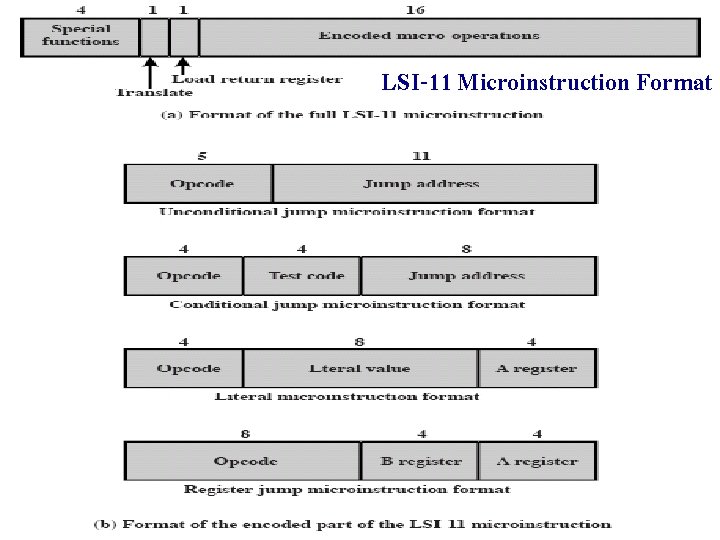

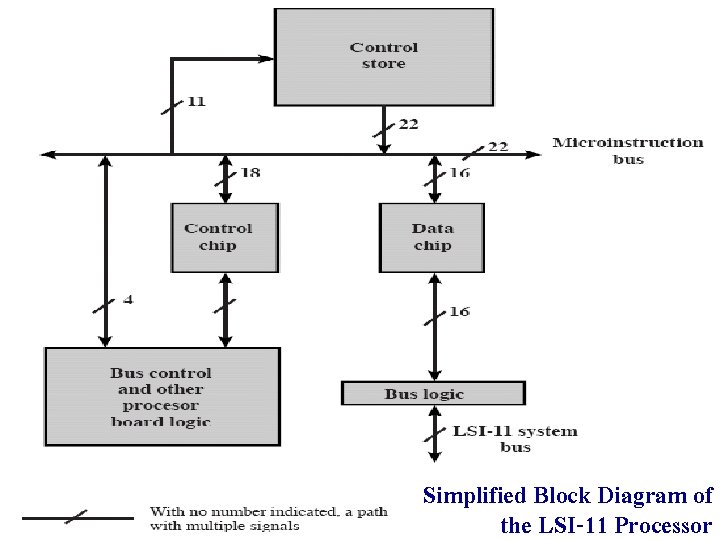

Other Samples • LSI computer

Simplified Block Diagram of the LSI-11 Processor

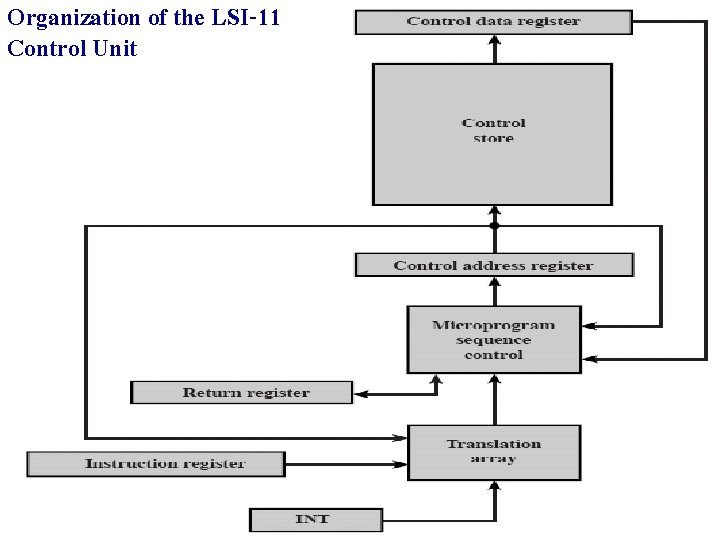

Organization of the LSI-11 Control Unit

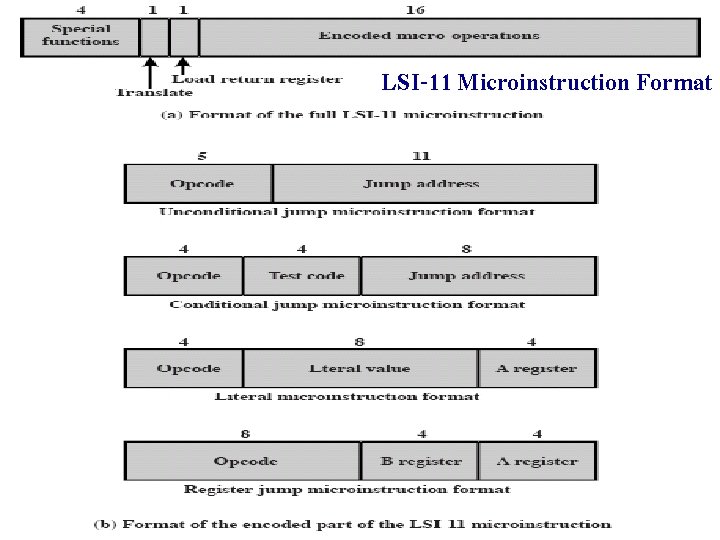

LSI-11 Microinstruction Format

Introduction to Computer Organization and Architecture ������ Machine �� Language