Introduction to Computer Organization and Architecture 2 Physical

- Slides: 57

Introduction to Computer Organization and Architecture ���� 2 ������ Physical ���� Representation

����� § ������ (Logic Gates) Ø AND, OR, NAND, NOR, XOR etc. § ������� (Boolean Algebra) Ø Functions, Truth Table § �������� (Logic Circuits) Ø Multiplexer, Adder, Registers, Counter, etc.

Introduction to Computer Organization and Architecture ���� 2 ������ Logic Circuits �

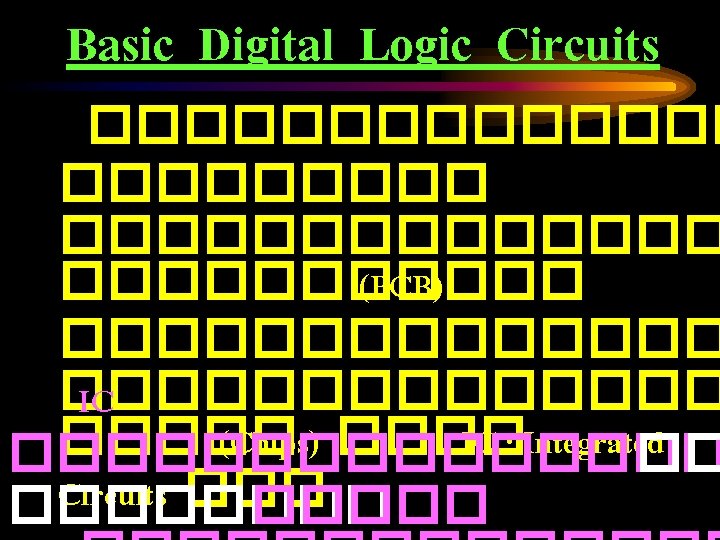

Basic Digital Logic Circuits ������� IC ������� • SSI : Small Scale Integrated (1 -100 Gates) • MSI : Medium Scale Integrated (100 -1, 000) • LSI : Large Scale Integrated (1, 000 -10, 000) • VLSI : Very Large Scale Integrated

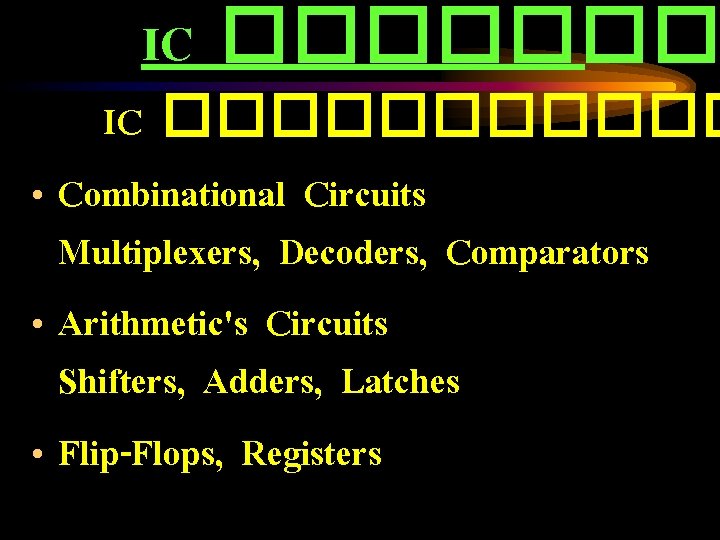

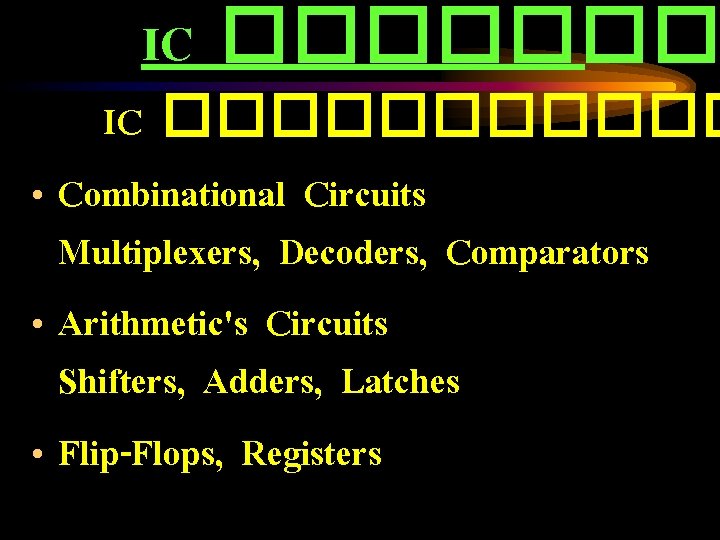

IC ������� IC ������ • Combinational Circuits Multiplexers, Decoders, Comparators • Arithmetic's Circuits Shifters, Adders, Latches • Flip-Flops, Registers

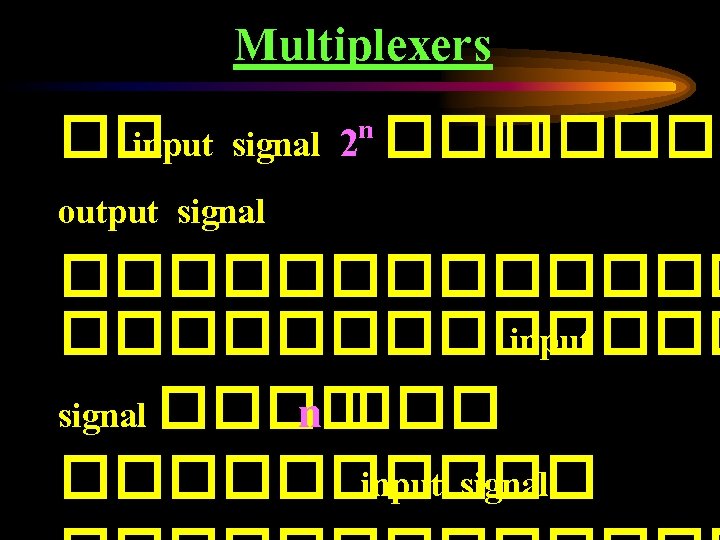

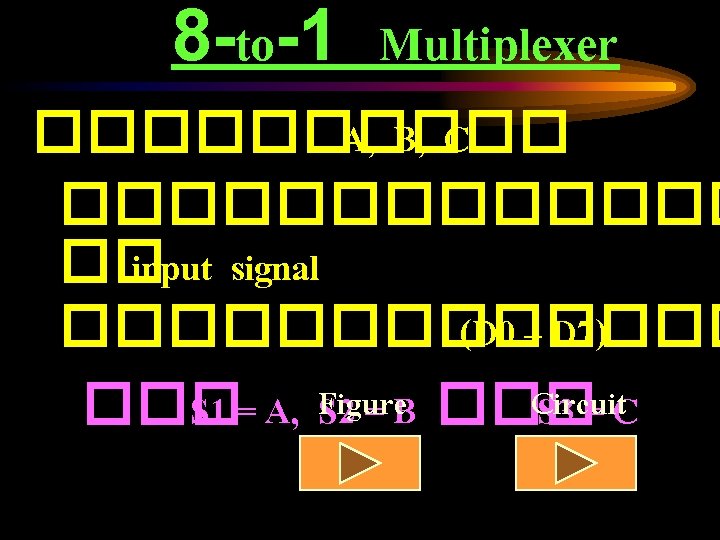

Multiplexers n 2 ����� �� input signal output signal ������������� input signal ���� n ���������� input signal

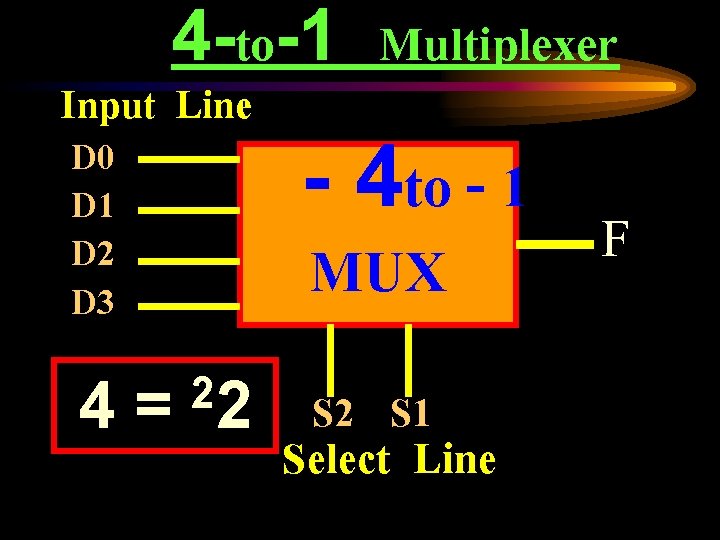

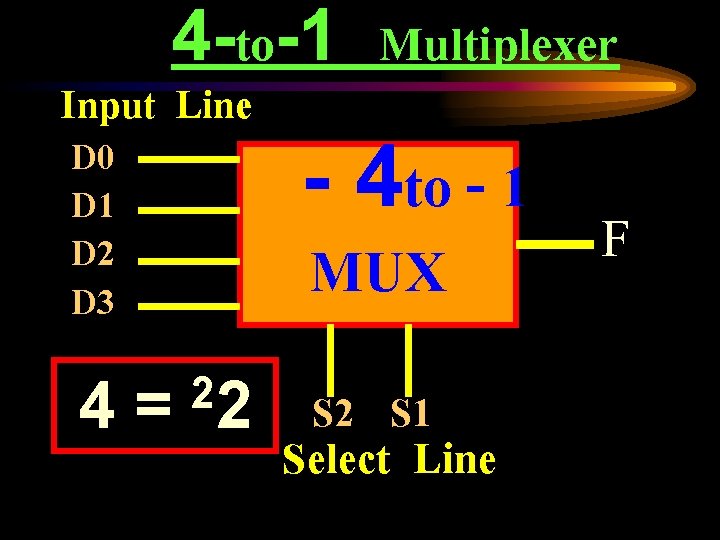

4 -to-1 Multiplexer Input Line D 0 D 1 D 2 D 3 4= 22 - 4 to - 1 F MUX S 2 S 1 Select Line

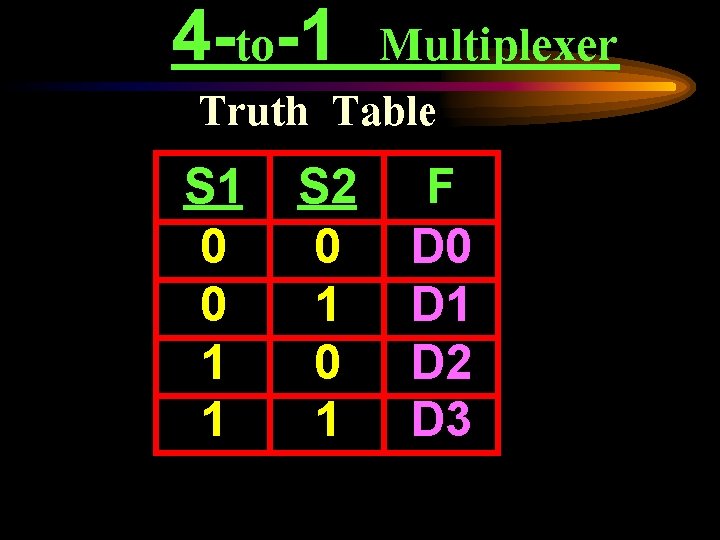

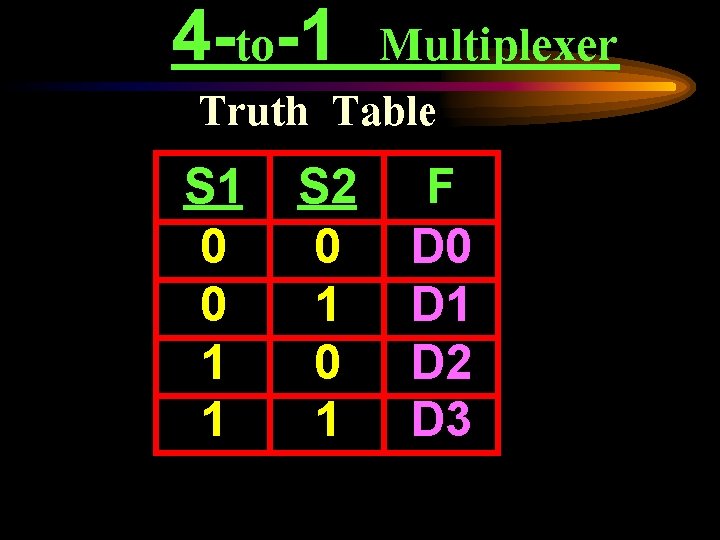

4 -to-1 Multiplexer Truth Table S 1 0 0 1 1 S 2 0 1 F D 0 D 1 D 2 D 3

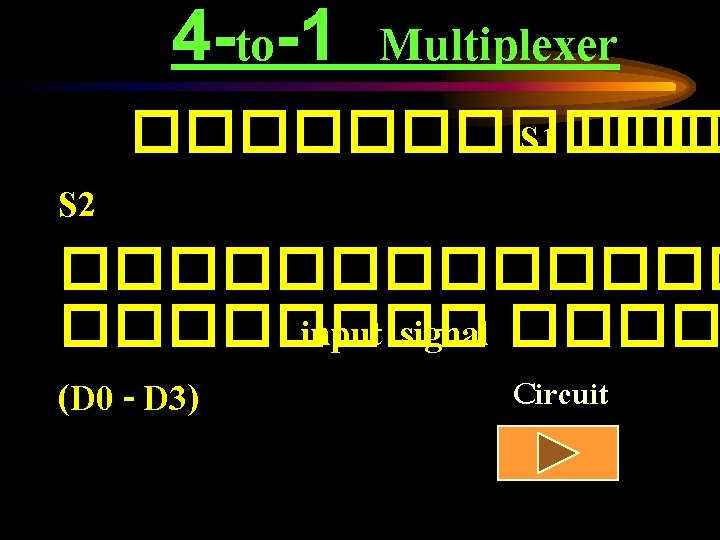

4 -to-1 Multiplexer ������ S 1 ��� S 2 ������� input signal ���� Circuit (D 0 - D 3)

����� Multiplexers Multiplexer ����� Control Signal ���� Data Routing ��������� PC : Program Counter ������� PC �������

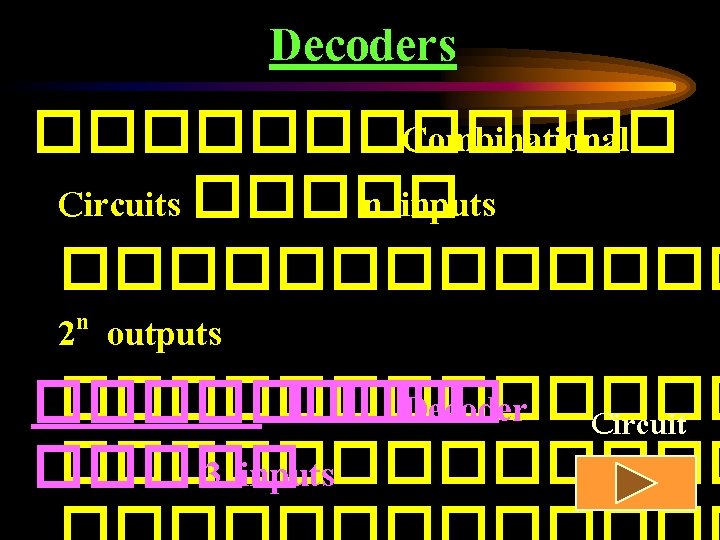

Decoders ������ Combinational Circuits ����� n inputs ������� n 2 outputs ������� ���� Decoder Circuit ������� 3 inputs

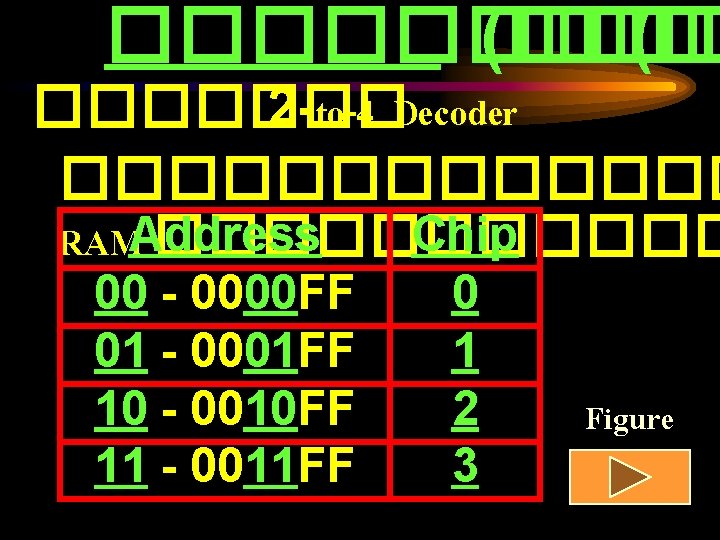

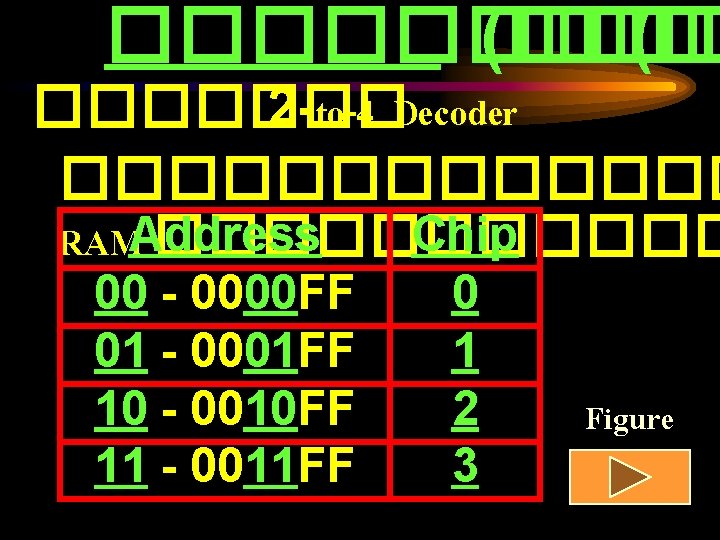

����� (��� ( ������� 2 -to-4 Decoder ������� Chip RAMAddress ������ 00 - 0000 FF 01 - 0001 FF 10 - 0010 FF 11 - 0011 FF 0 1 2 3 Figure

PLA : Programable Logic Array Gates ������������ SSI : Small Scale Integrated ������������� ��� Figure ������ ,

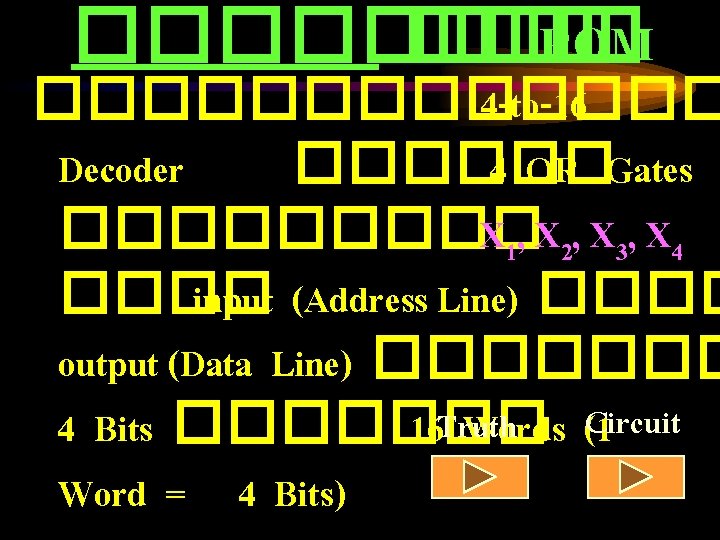

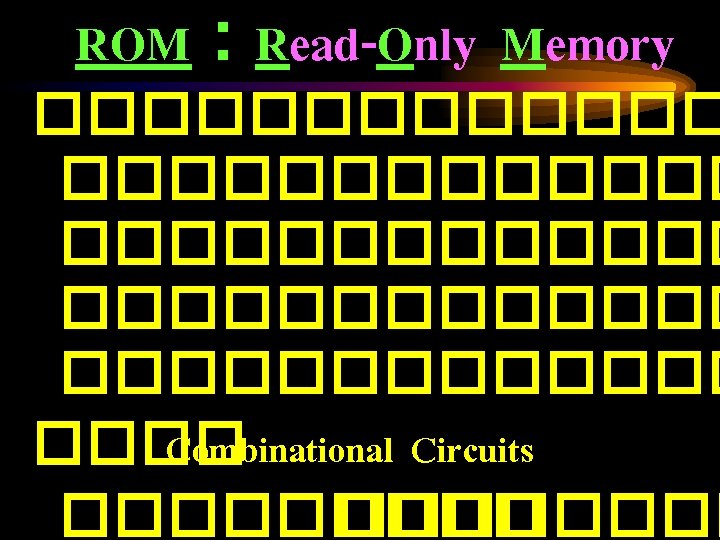

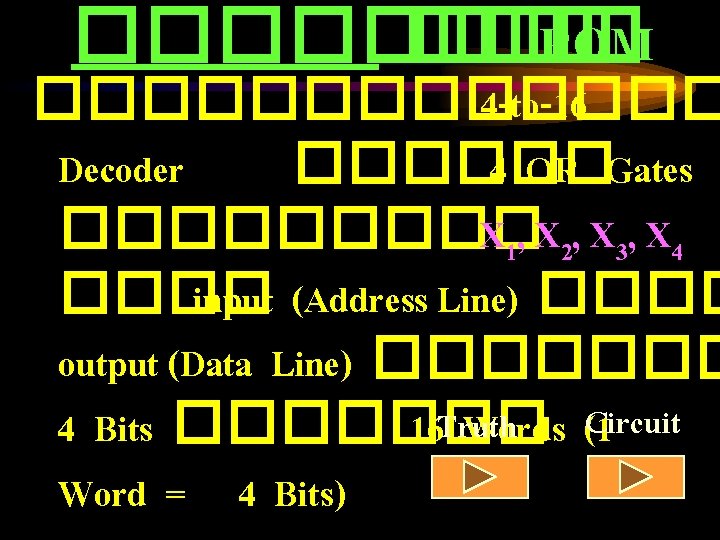

���� ��� ROM ������� 4 -to-16 Decoder ������ 4 OR Gates ����� X 1, X 2, X 3, X 4 ���� input (Address Line) ���� output (Data Line) ������� Circuit 4 Bits ������� 16 Truth Words (1 Word = 4 Bits)

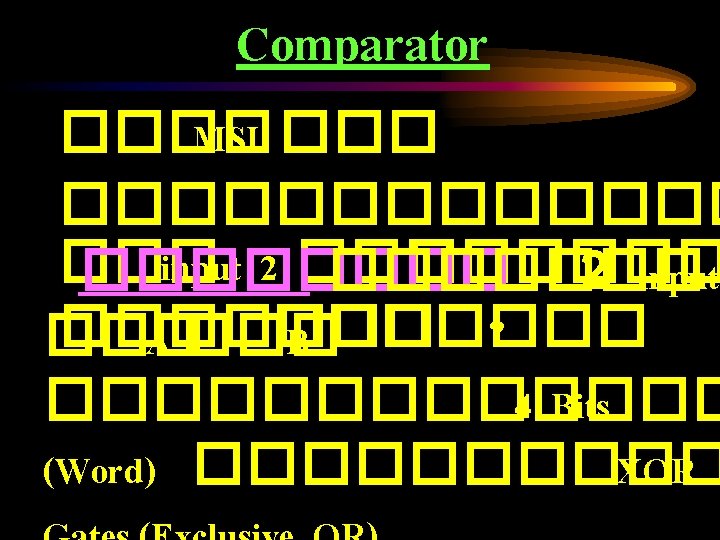

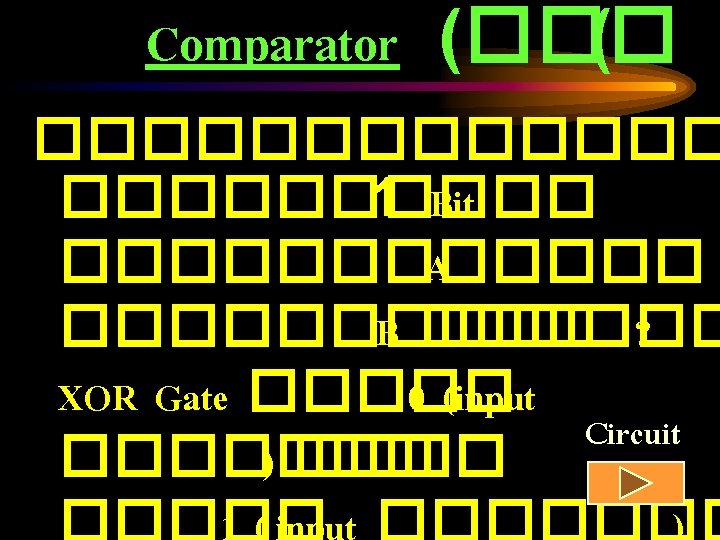

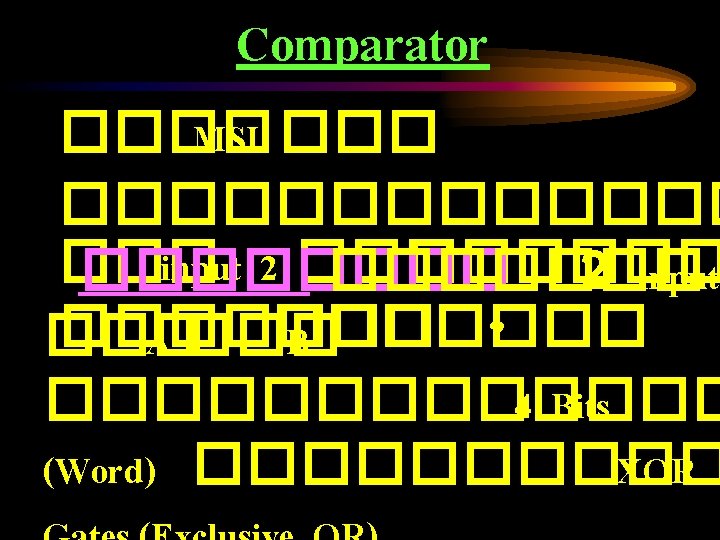

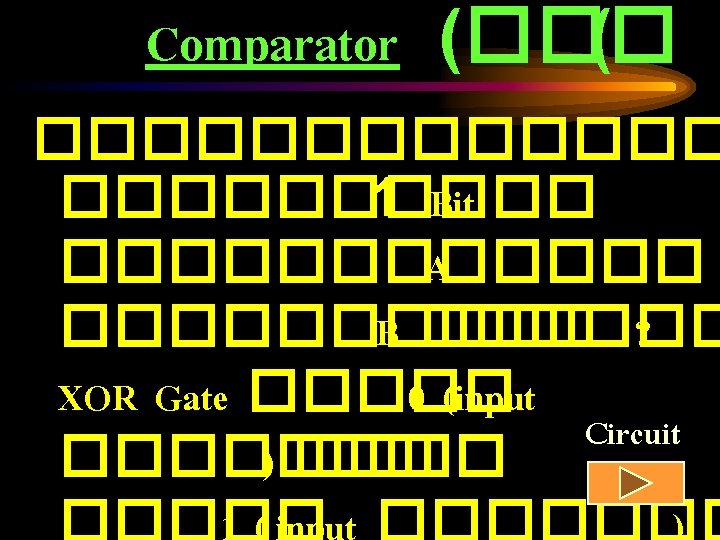

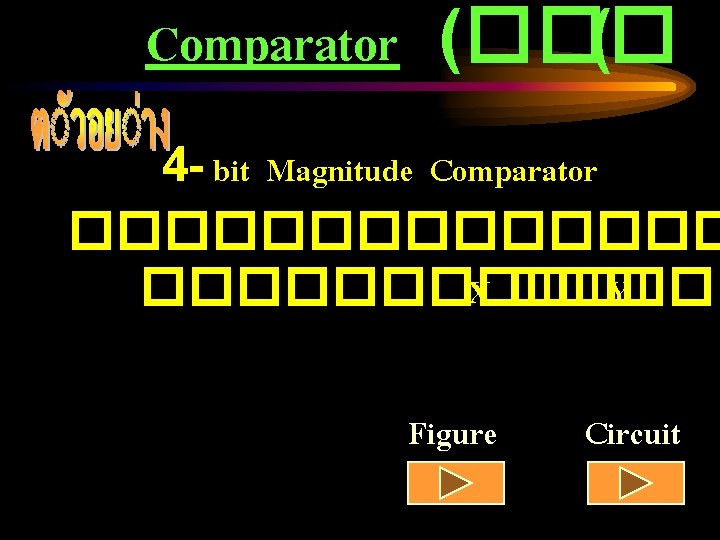

Comparator (��� ( 4 - bit Magnitude Comparator ������� X ��� Y Figure Circuit

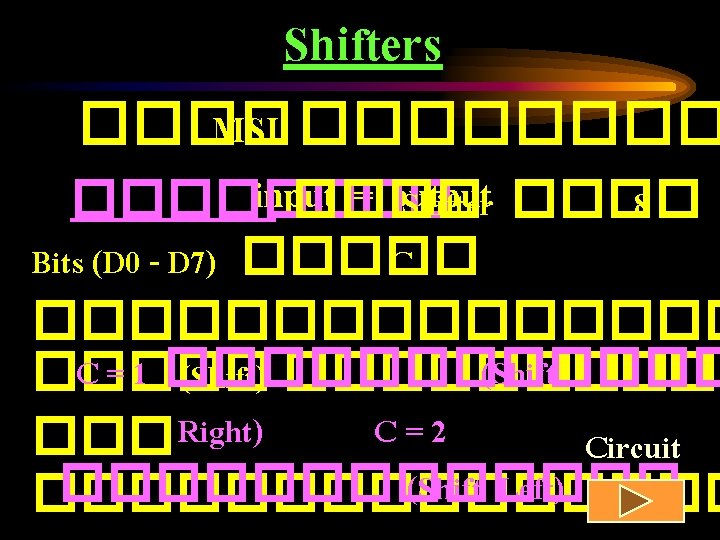

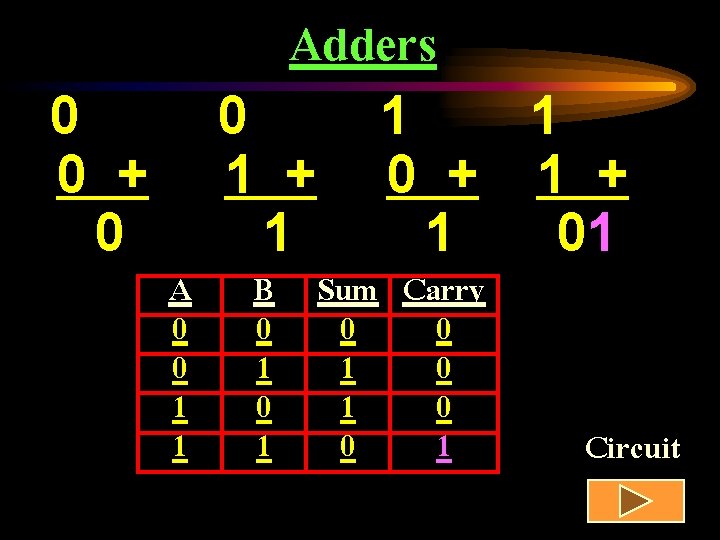

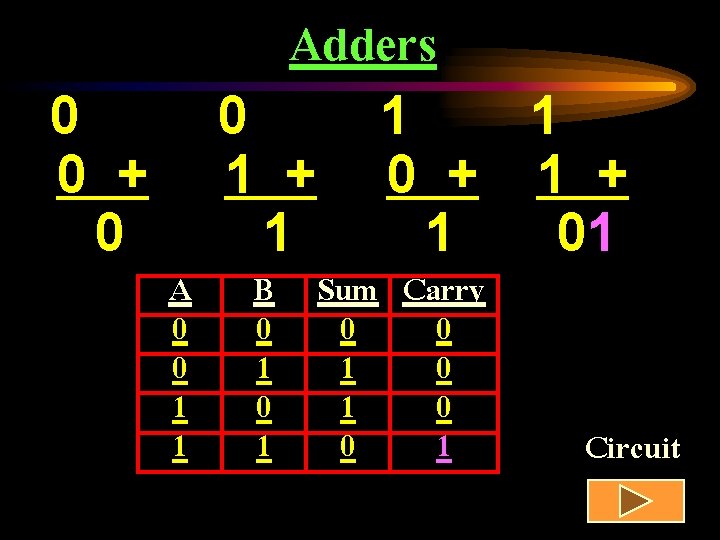

0 0 + 0 Adders A 0 0 1 1 0 1 + 1 1 1 0 + 1 01 B Sum Carry 0 0 0 1 1 0 0 1 0 1 Circuit

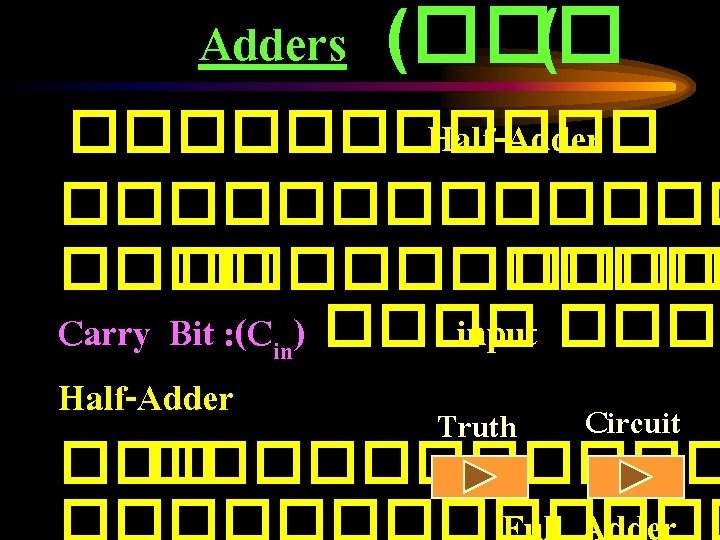

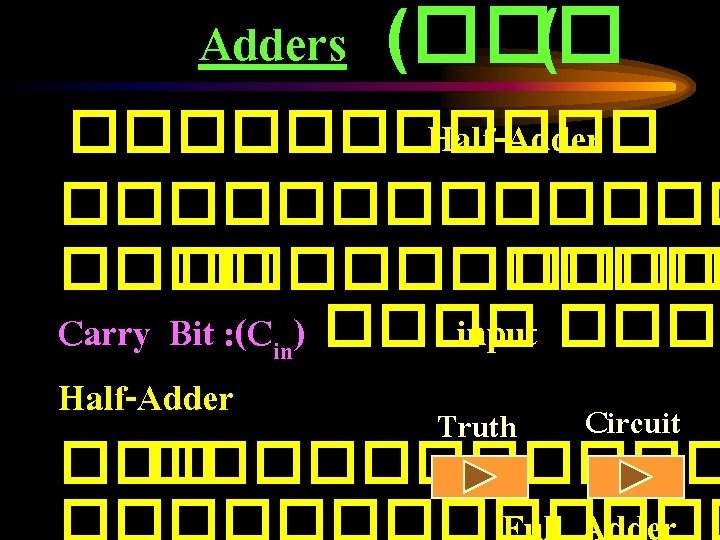

Adders (��� ( ������ Half-Adder ������� ���� Carry Bit : (Cin) ���� input ��� Half-Adder Truth Circuit ������� Full Adder

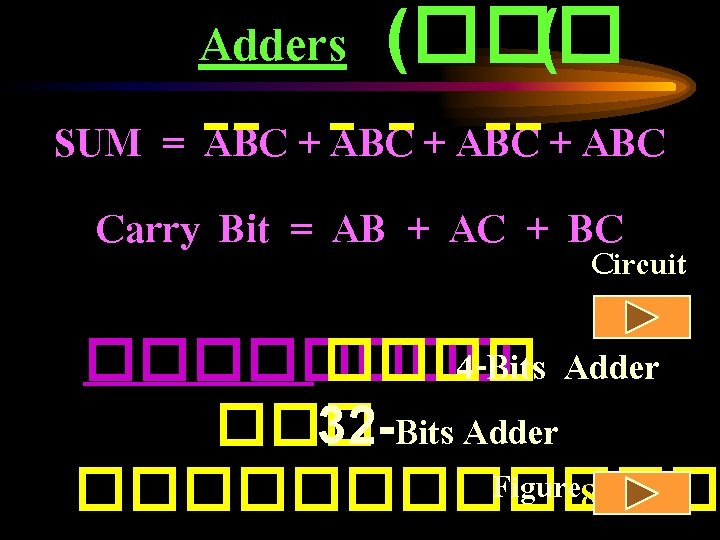

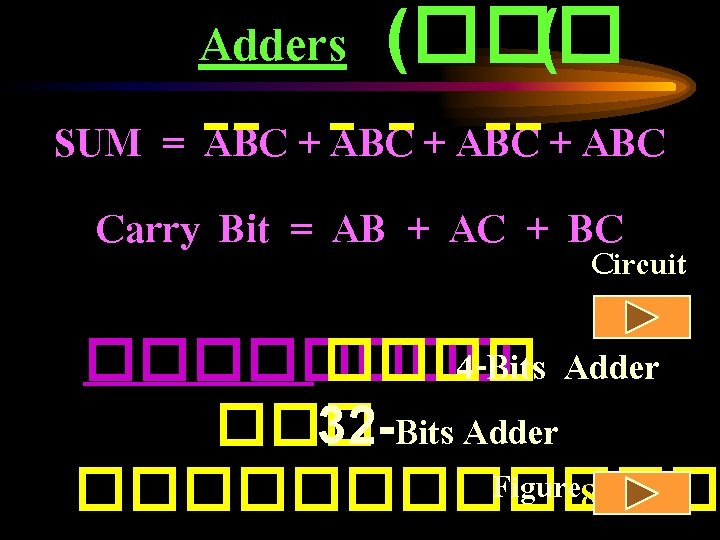

Adders (��� ( SUM = ABC + ABC Carry Bit = AB + AC + BC Circuit ���� 4 -Bits Adder ��� 32 -Bits Adder Figure 8 -Bits ������

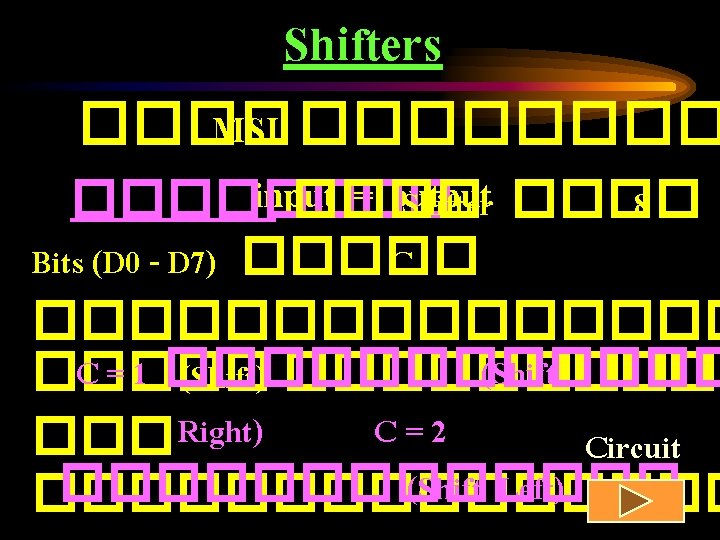

Circuits • Multiplexers • Decoders • PLA : Programable Logic Arrays • Comparators • Shifters • Adders etc.

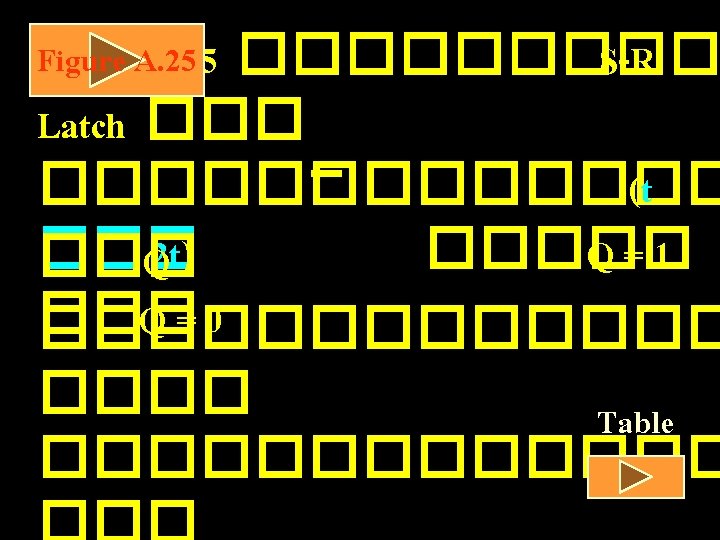

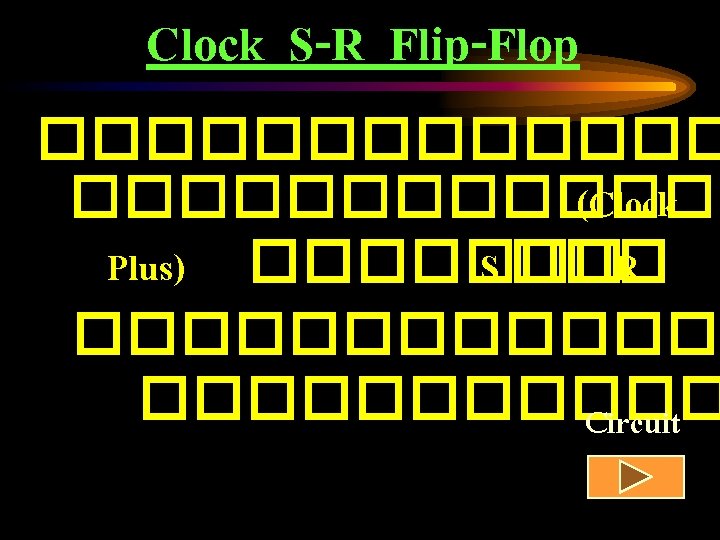

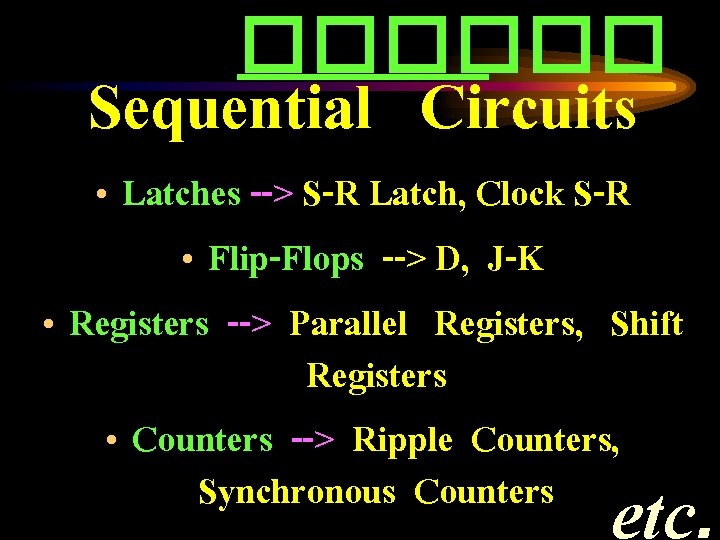

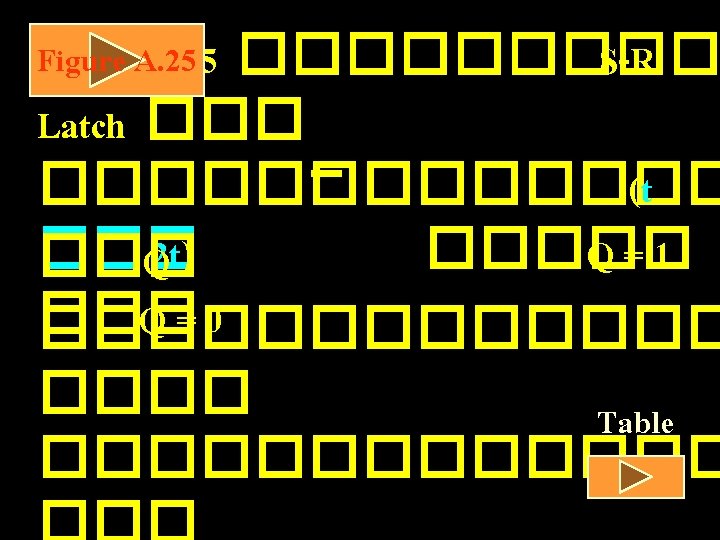

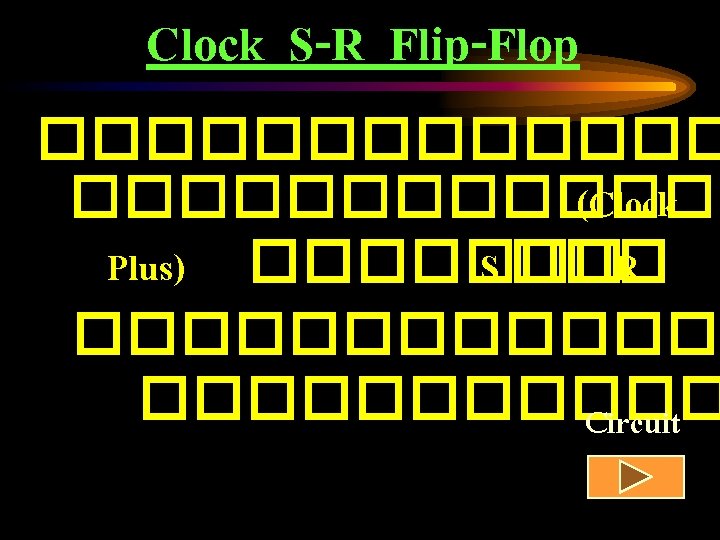

������ Sequential Circuits • Latches --> S-R Latch, Clock S-R • Flip-Flops --> D, J-K • Registers --> Parallel Registers, Shift Registers • Counters --> Ripple Counters, Synchronous Counters etc.

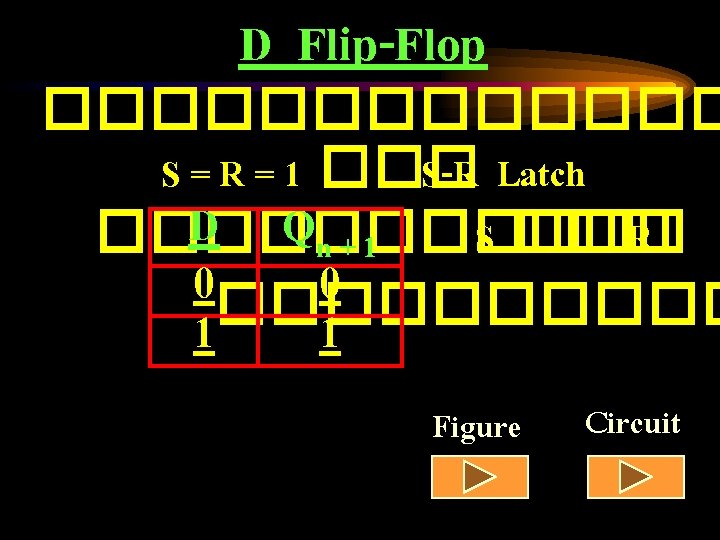

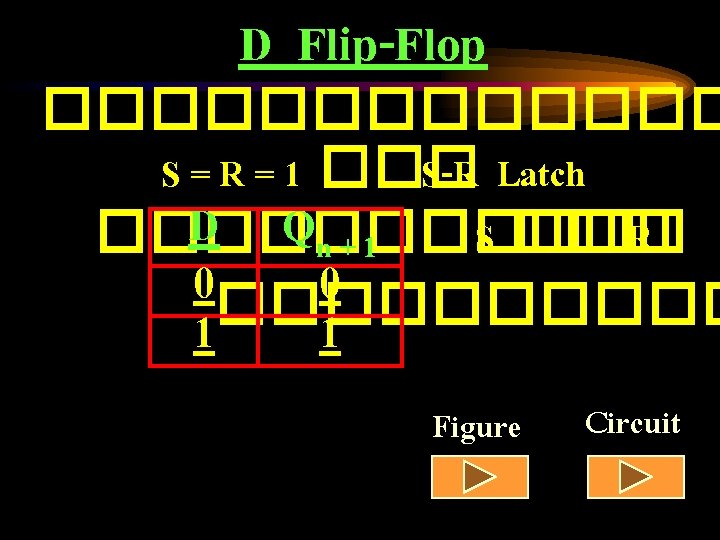

D Flip-Flop ���� �� �� 2 ������������� (Clear and Present Signal) Figure

Flip-Flops • S-R Flip-Flop • D Flip-Flop • J-K Flip-Flop Figure

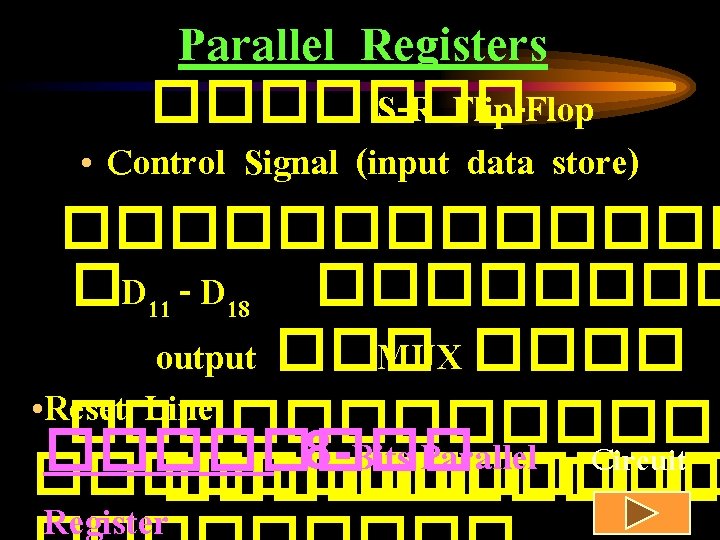

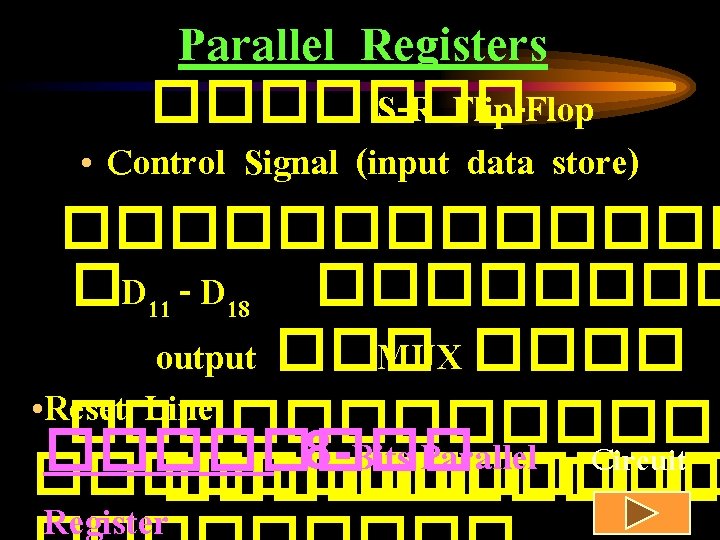

Parallel Registers ������� S-R Flip-Flop • Control Signal (input data store) ������� �D 11 - D 18 ���� output ��� MUX ���� • Reset Line ������� 8 -Bits Parallel Circuit ������� Register

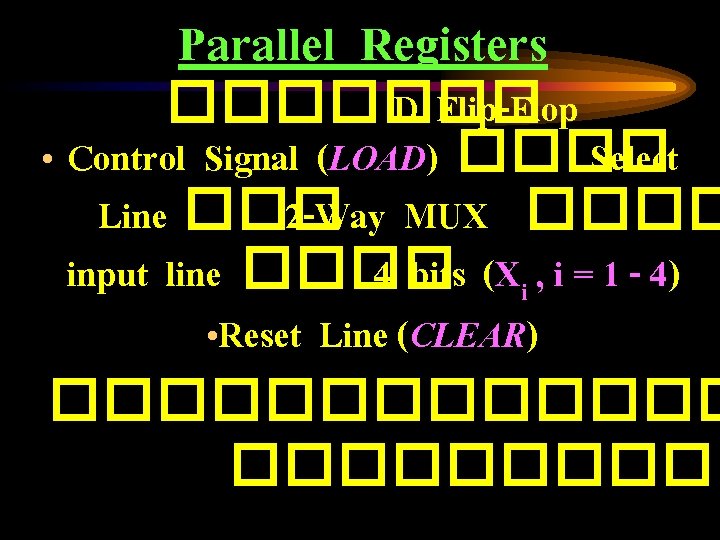

Parallel Registers ������� D Flip-Flop • Control Signal (LOAD) ���� Select Line ��� 2 -Way MUX ���� input line ���� 4 bits (Xi , i = 1 - 4) • Reset Line (CLEAR) �������

Parallel Registers Figure ���� 4 -Bits D Register with parallel I/O Figure ���� 4 -Bits D Register with parallel Load

Shift Registers ���� 4 -Bits Right-Shift Figure Register ���� 5 -Bits Shift Figure Register

������� Counters • Asynchronous Counters ����� Flip-Flop ������� Flip-Flop ���� (Ripple) • Synchronous Counters ���� Flip-

Ripple Counter Figure A. 32 ����� 4 -bits Counter ������ J-K Flip-Flop ������� Timing Diagram ��� Counter ������� (Clock Pulse)

Synchronous Counters Ripple Counter ������ 3 -Bits Synchronous ������ Counter ������ J-K Flip-Flop ������ A, B, C ������� output Figure �������

Introduction to Computer Organization and Architecture ���� 2 ������ Physical ���� Representation

Introduction to Computer Organization and Architecture Coming Soon ���� 3 ������ Computer Systems ����