Introduction to CMOS VLSI Design Adnan Aziz The

- Slides: 32

Introduction to CMOS VLSI Design Adnan Aziz The University of Texas at Austin Introduction CMOS VLSI Design 1

Organization q Prerequisites: logic design, basic computer organization – See sample questions q Architecture design versus chip design – Example: innovative processor q Overview of material – Bottom-up approach, CAD tools – See syllabus for individual topics q Course organization – Website, TA, office hours, HW, projects q Acknowledgements – J. Abraham (UT), D. Harris (HMC), R. Tupuri (AMD) Introduction CMOS VLSI Design 2

Course relevance q 2007 world wide sales of chips: ~250 B$ – Primarily digital – High-margin business – Basis for systems q Most CE graduates work in – VLSI design: Intel, Qualcomm – System design: HP, Cisco – Software: Microsoft, Google Introduction CMOS VLSI Design 3

Systems and Chips q This course: designing ICs – Part of a system: chips + board + software + … – System companies: HP, Cisco – Chip companies: Intel, Qualcomm – n. Vidia vs. Hercules q Example: high-end data switch – Marketing gives range of specs, architect tries to meet them – Off the shelf chips, embedded software – Why don’t we teach system design? Introduction CMOS VLSI Design 4

Course Goals q Learn to design and analyze state-of-the-art digital VLSI chips using CMOS technology q Employ hierarchical design methods – Understand design issues at the layout, transistor, logic and register-transfer levels – Use integrated circuit cells as building blocks – Use commercial design software in the lab q Understand the complete design flow – Won’t cover architecture, solid-state physics, analog design – Superficial treatment of transistor functioning Introduction CMOS VLSI Design 5

Course Information q Instructor: Adnan Aziz – (512) 465 -9774, Adnan@ece. utexas. edu – http: //www. ece. utexas. edu/~adnan q Course Web Page – Link from my page q Book: Weste and Harris, CMOS VLSI Design: A Circuits and Systems Perspective, AW, 3 rd edition Introduction CMOS VLSI Design 6

Work in the Course q Lectures: largely from text (not always in sequence) q Homework: roughly 6 HWs – Relatively straightforward review questions q Laboratory exercises – Three major exercises dealing with various aspects of VLSI design – Complete each section before the deadline q Grad students: VLSI design project – Design an IP core, architecture to layout Course involves a large amount of work throughout the semester Introduction CMOS VLSI Design 7

What Will We Cover? q Designing chips containing lots of transistors – How basic components work (transistors, gates, flops, memories, adders, – Complexity management: hierarchy and CAD tools q Key issues: – Creating logical structures from transistors – Performance analysis and optimization – Testing: functional and manufacturing – Power consumption, clocking, I/O, etc. Introduction CMOS VLSI Design 8

Exams and Grading q Two midterm tests: in class, open book/notes; samples will be posted – Dates for exams in syllabus – Final: exam (360 R), project (382 M) q Lab dates in syllabus – Bonus/penalty for early/late submission q Weights for homework, exams, project are in syllabus – Relative weights of MT 1/2, Lab 1/2/3 intentionally not specified Introduction CMOS VLSI Design 9

Academic Honesty q Cheating will not be tolerated – OK to discuss homework, laboratory exercises with classmates, TAs and the instructors – However: write the homework and lab exercises by yourself q We check for cheating, and report incidents Introduction CMOS VLSI Design 10

General Principles q Technology changes fast => important to understand general principles – optimization, tradeoffs – work as part of a group – leverage existing work: programs , building blocks q Concepts remain the same: – Example: relays -> tubes -> bipolar transistors -> MOS transistors Introduction CMOS VLSI Design 11

Types of IC Designs q IC Designs can be Analog or Digital q Digital designs can be one of three groups q Full Custom – Every transistor designed and laid out by hand q ASIC (Application-Specific Integrated Circuits) – Designs synthesized automatically from a high-level language description q Semi-Custom – Mixture of custom and synthesized modules Introduction CMOS VLSI Design 12

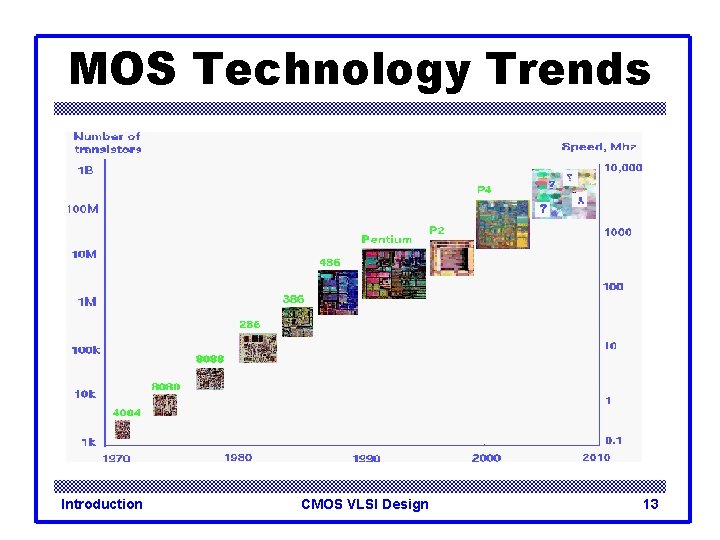

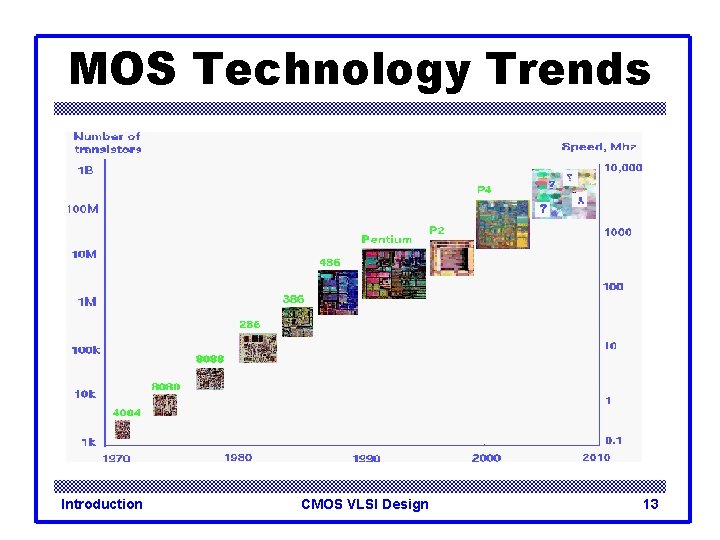

MOS Technology Trends Introduction CMOS VLSI Design 13

Steps in Design Introduction CMOS VLSI Design 14

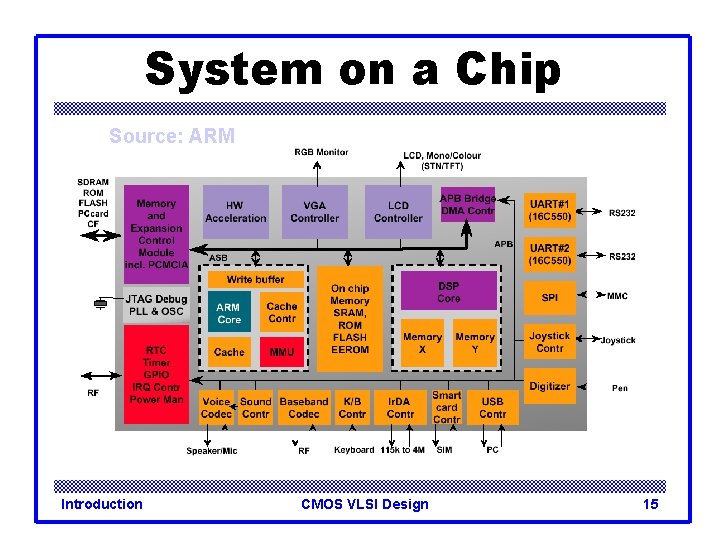

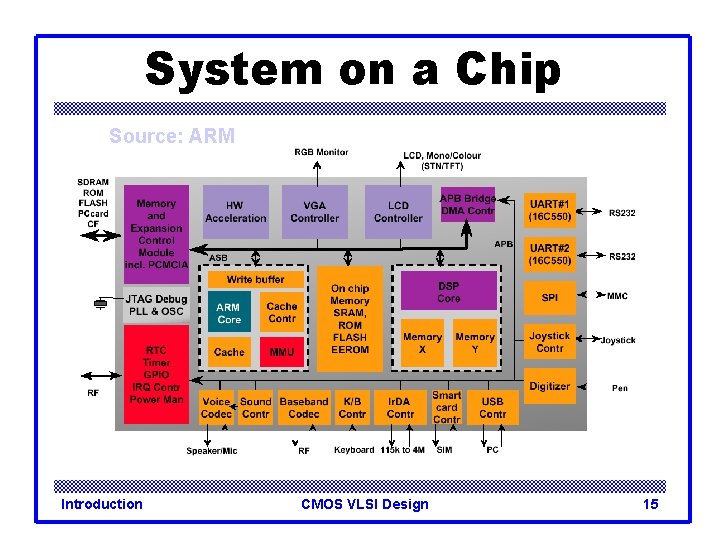

System on a Chip Source: ARM Introduction CMOS VLSI Design 15

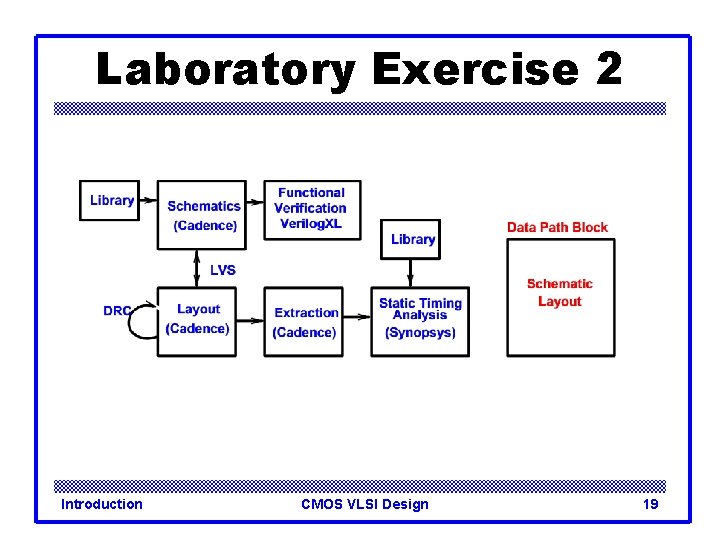

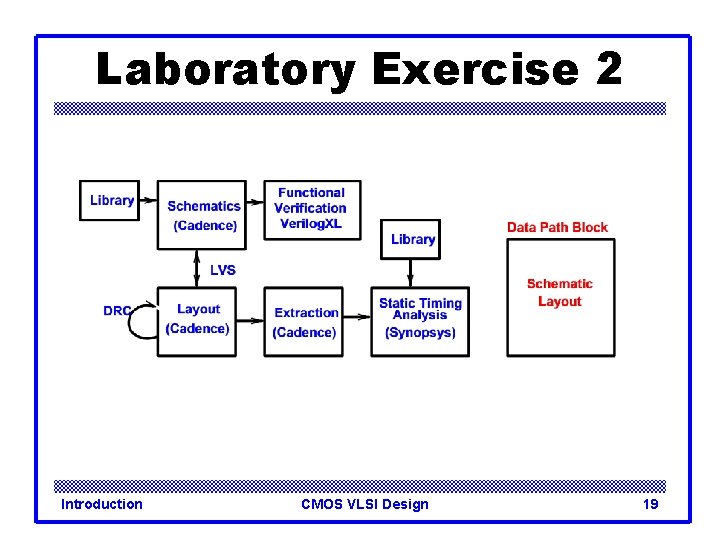

Laboratory Exercises q Layout and evaluation of standard cells – Familiarity with layout, circuit simulation, timing q Design and evaluation of an ALU, performance optimization – Learn schematic design, timing optimization q Design, synthesis and analysis of a simple controller as part of an So. C – Learn RT-level design, system simulation, logic synthesis and place-and-route q If you already have industrial experience with some of these tools, you can substitute lab for final project – Need my approval; will expect more from project Introduction CMOS VLSI Design 16

Laboratory Design Tools q We will use commercial CAD tools – Cadence, Synopsys, etc. q Commercial software is powerful, but very complex – Designers sent to long training classes – Students will benefit from using the software, but we don’t have the luxury of long training – TAs have experience with the software q Start work early in the lab – Unavailability of workstations is no excuse for late submissions – Plan designs carefully and save work frequently Introduction CMOS VLSI Design 17

Laboratory Exercise 1 Introduction CMOS VLSI Design 18

Laboratory Exercise 2 Introduction CMOS VLSI Design 19

Laboratory Exercise 3 Introduction CMOS VLSI Design 20

Need for transistors q Cannot make logic gates with voltage/current source, RLC components – Consider steady state behavior of L and C q Need a “switch”: something where a (small) signal can control the flow of another signal Introduction CMOS VLSI Design 21

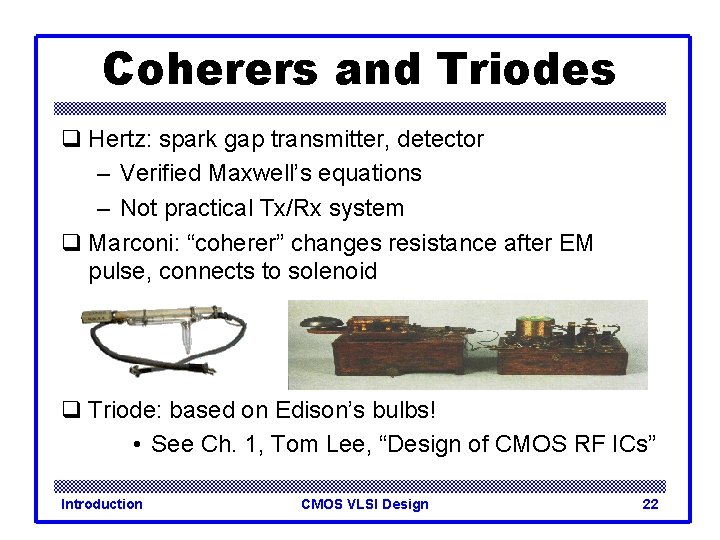

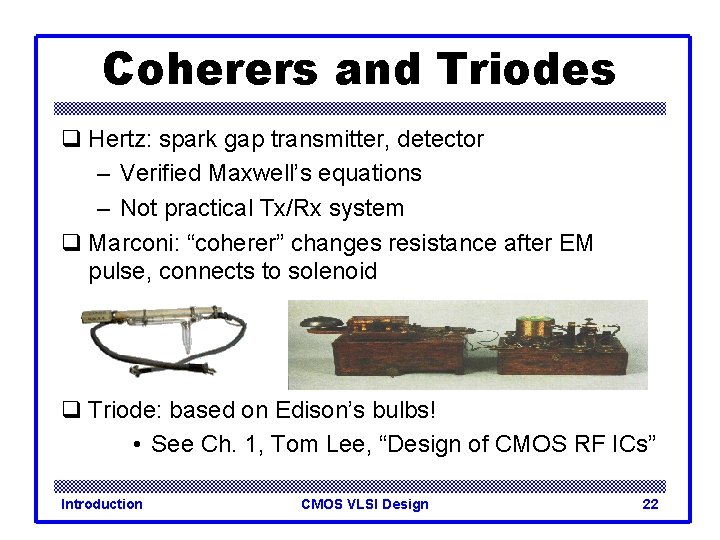

Coherers and Triodes q Hertz: spark gap transmitter, detector – Verified Maxwell’s equations – Not practical Tx/Rx system q Marconi: “coherer” changes resistance after EM pulse, connects to solenoid q Triode: based on Edison’s bulbs! • See Ch. 1, Tom Lee, “Design of CMOS RF ICs” Introduction CMOS VLSI Design 22

A Brief History of MOS Some of the events which led to the microprocessor Photographs from “State of the Art: A photographic history of the integrated circuit, ” Augarten, Ticknor & Fields, 1983. They can also be viewed on the Smithsonian web site, http: //smithsonianchips. si. edu/ Introduction CMOS VLSI Design 23

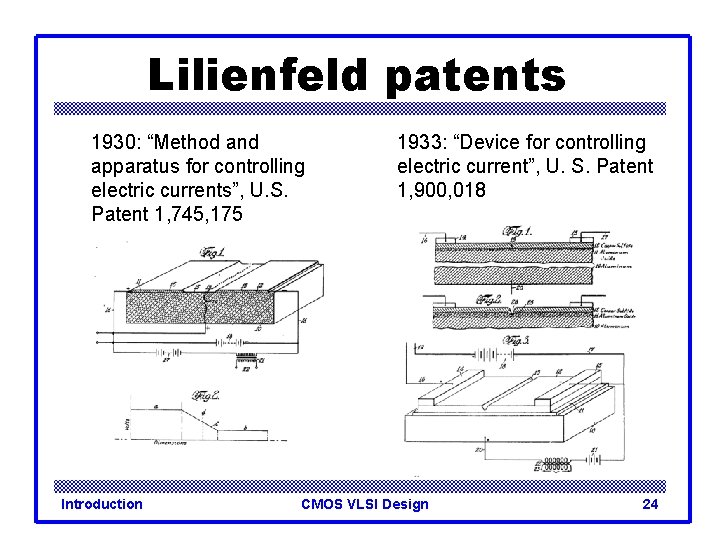

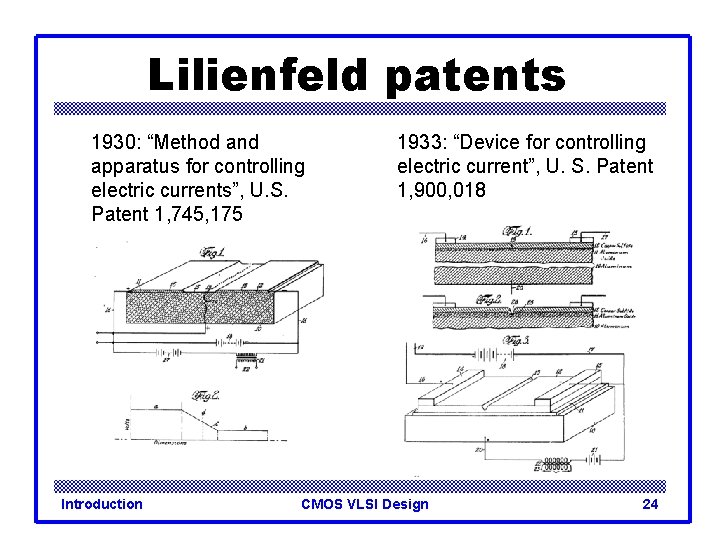

Lilienfeld patents 1930: “Method and apparatus for controlling electric currents”, U. S. Patent 1, 745, 175 Introduction 1933: “Device for controlling electric current”, U. S. Patent 1, 900, 018 CMOS VLSI Design 24

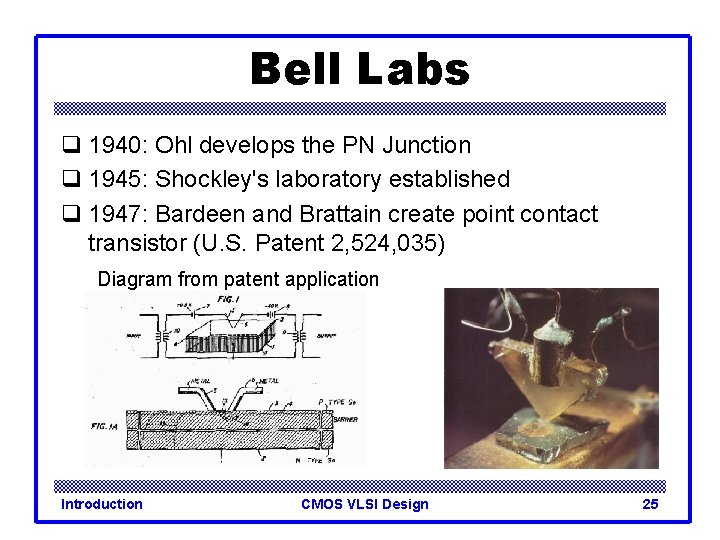

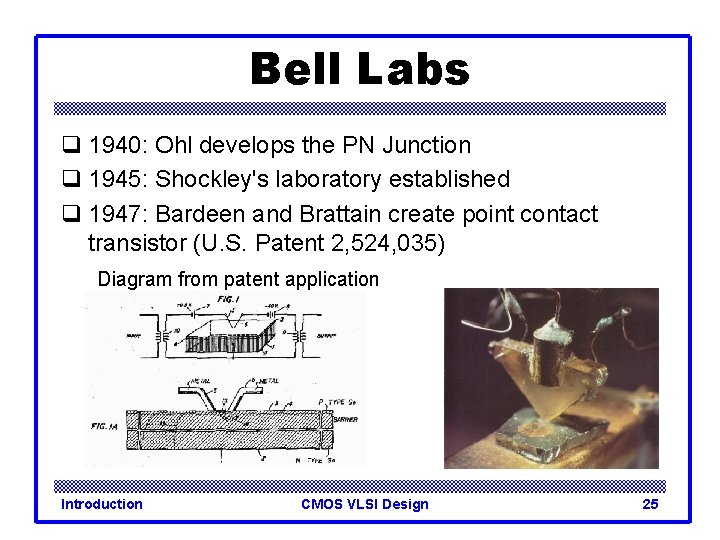

Bell Labs q 1940: Ohl develops the PN Junction q 1945: Shockley's laboratory established q 1947: Bardeen and Brattain create point contact transistor (U. S. Patent 2, 524, 035) Diagram from patent application Introduction CMOS VLSI Design 25

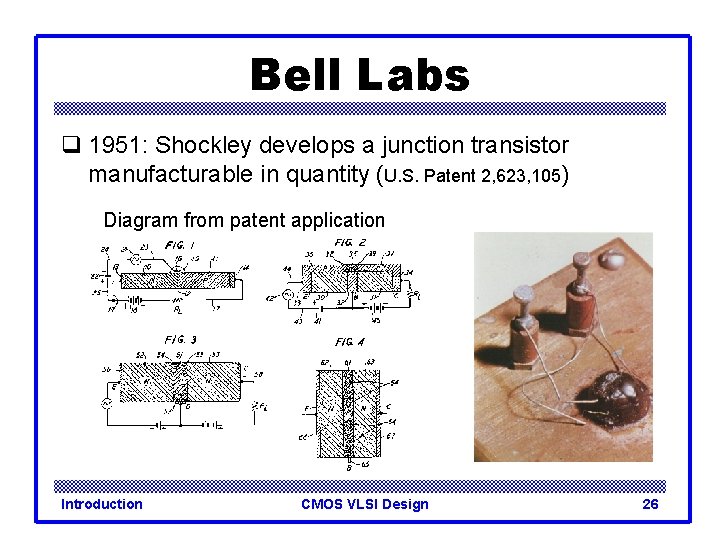

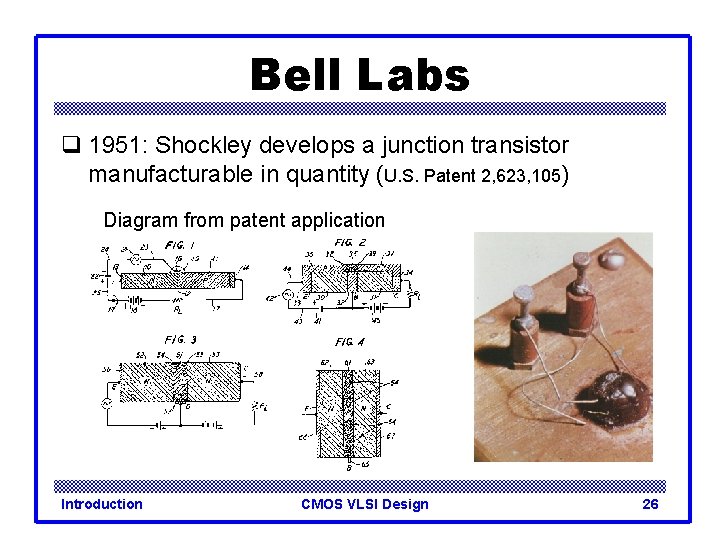

Bell Labs q 1951: Shockley develops a junction transistor manufacturable in quantity (U. S. Patent 2, 623, 105) Diagram from patent application Introduction CMOS VLSI Design 26

1950 s – Silicon Valley q q 1950 s: Shockley in Silicon Valley 1955: Noyce joins Shockley Laboratories 1954: The first transistor radio 1957: Noyce leaves Shockley Labs to form Fairchild with Jean Hoerni and Gordon Moore q 1958: Hoerni invents technique for diffusing impurities into Si to build planar transistors using a Si. O 2 insulator q 1959: Noyce develops first true IC using planar transistors, back-to-back PN junctions for isolation, diode-isolated Si resistors and Si. O 2 insulation with evaporated metal wiring on top Introduction CMOS VLSI Design 27

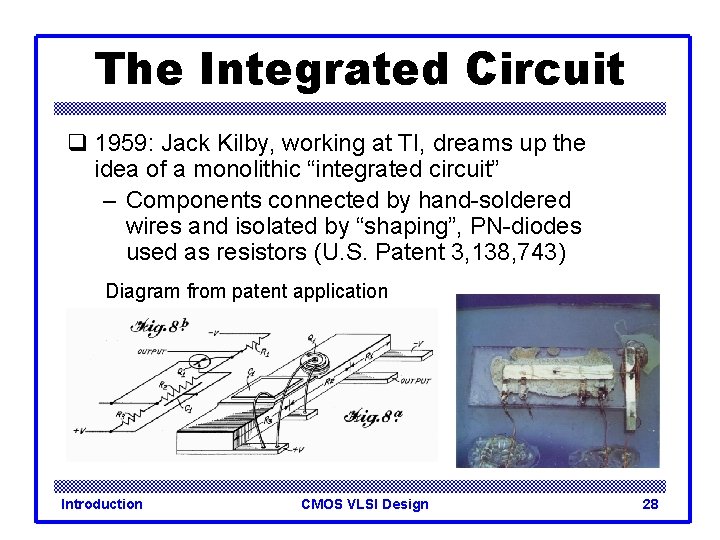

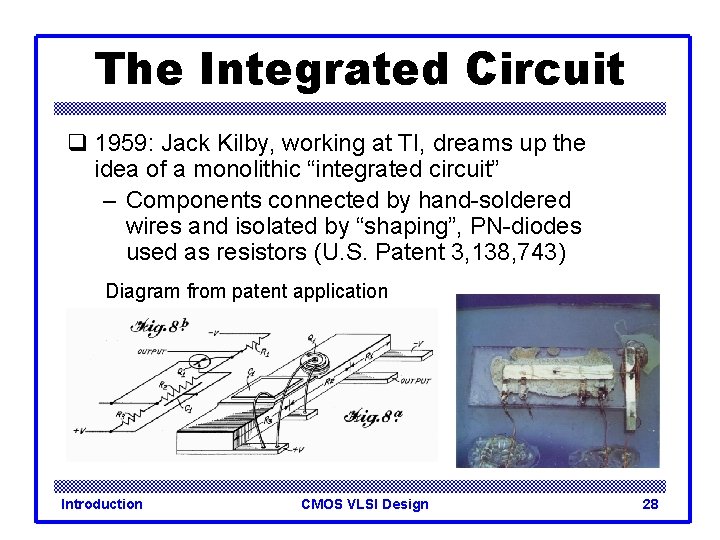

The Integrated Circuit q 1959: Jack Kilby, working at TI, dreams up the idea of a monolithic “integrated circuit” – Components connected by hand-soldered wires and isolated by “shaping”, PN-diodes used as resistors (U. S. Patent 3, 138, 743) Diagram from patent application Introduction CMOS VLSI Design 28

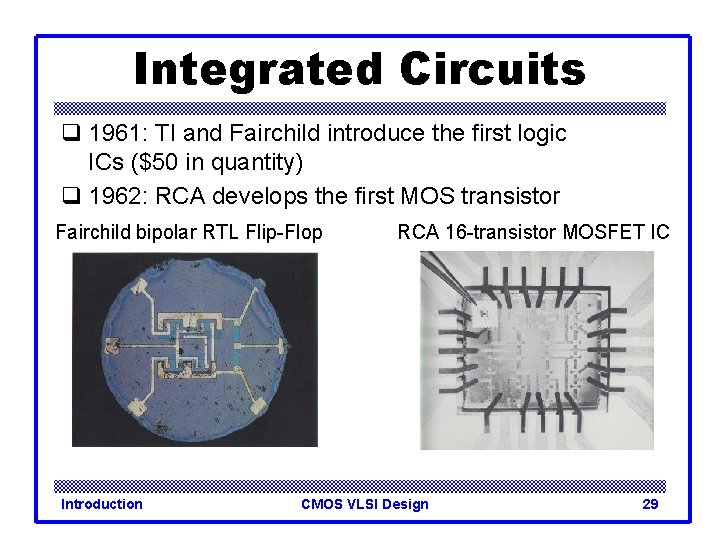

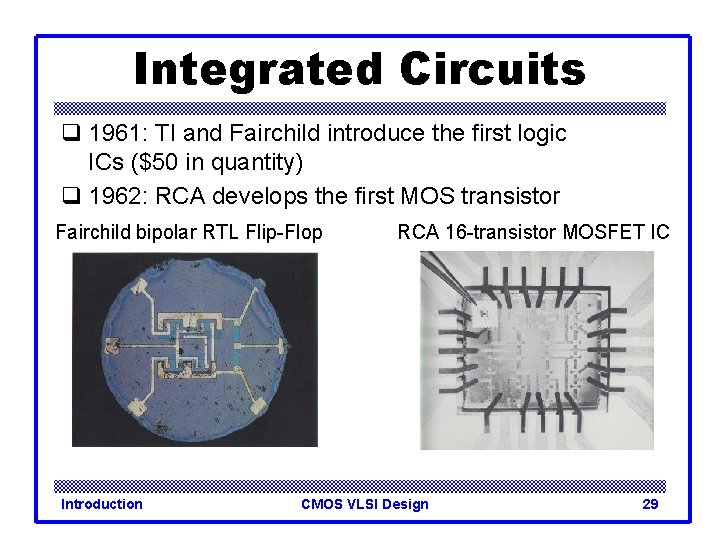

Integrated Circuits q 1961: TI and Fairchild introduce the first logic ICs ($50 in quantity) q 1962: RCA develops the first MOS transistor Fairchild bipolar RTL Flip-Flop Introduction RCA 16 -transistor MOSFET IC CMOS VLSI Design 29

Computer-Aided Design q 1967: Fairchild develops the “Micromosaic” IC using CAD – Final Al layer of interconnect could be customized for different applications q 1968: Noyce, Moore leave Fairchild, start Intel Introduction CMOS VLSI Design 30

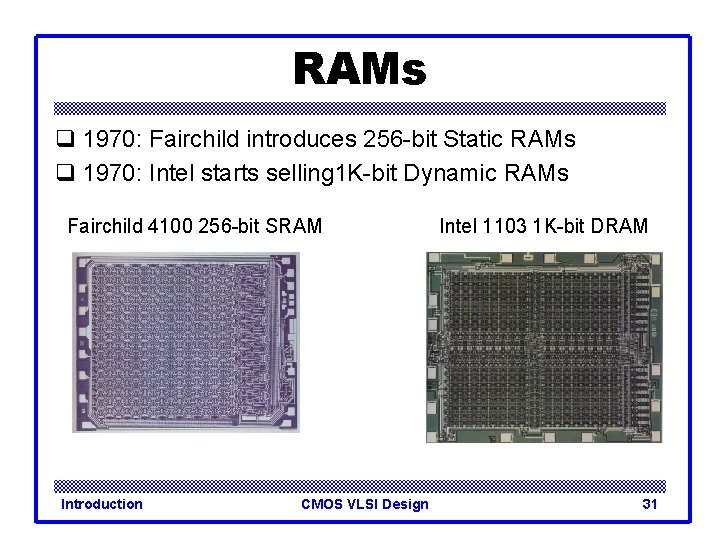

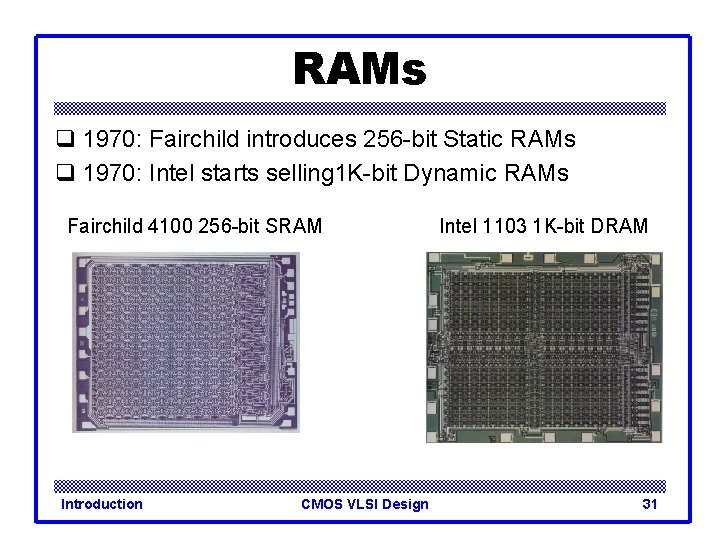

RAMs q 1970: Fairchild introduces 256 -bit Static RAMs q 1970: Intel starts selling 1 K-bit Dynamic RAMs Fairchild 4100 256 -bit SRAM Introduction CMOS VLSI Design Intel 1103 1 K-bit DRAM 31

The Microprocessor q 1971: Intel introduces the 4004 – General purpose programmable computer instead of custom chip for Japanese calculator company Introduction CMOS VLSI Design 32