Introduction to Assembly Language Programming 322021 1 High

Introduction to Assembly Language Programming 3/2/2021 1

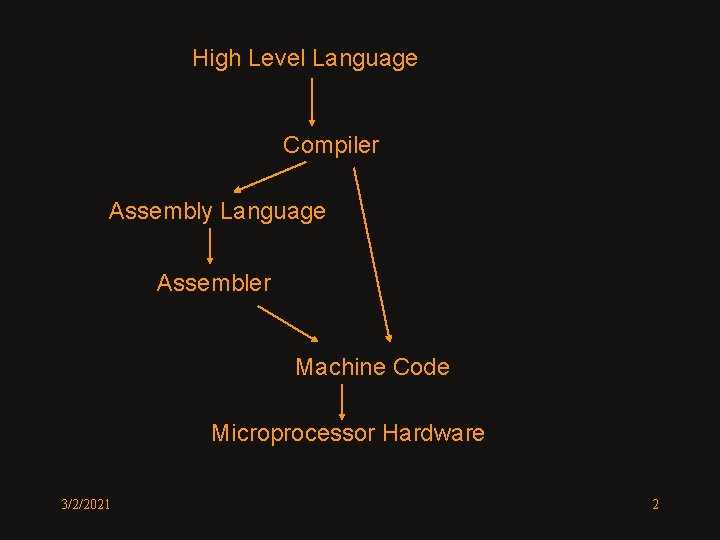

High Level Language Compiler Assembly Language Assembler Machine Code Microprocessor Hardware 3/2/2021 2

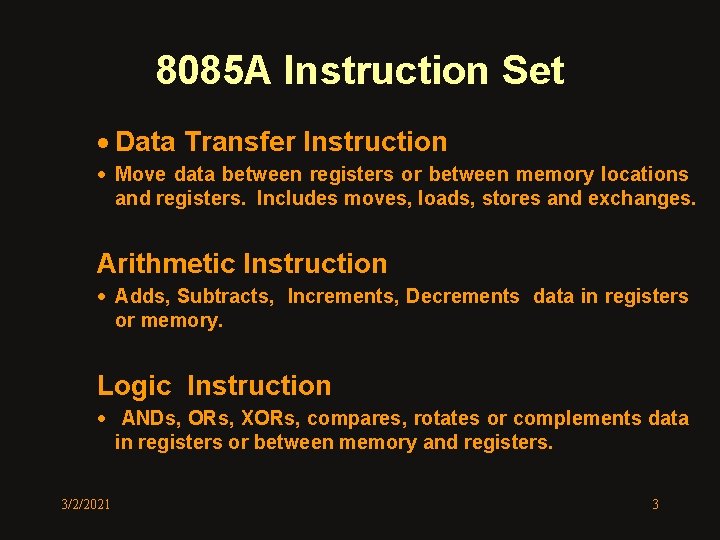

8085 A Instruction Set · Data Transfer Instruction · Move data between registers or between memory locations and registers. Includes moves, loads, stores and exchanges. Arithmetic Instruction · Adds, Subtracts, Increments, Decrements data in registers or memory. Logic Instruction · ANDs, ORs, XORs, compares, rotates or complements data in registers or between memory and registers. 3/2/2021 3

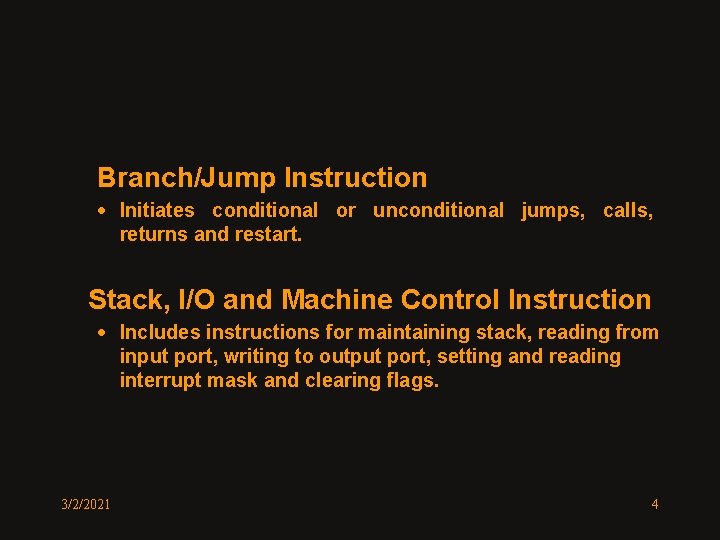

Branch/Jump Instruction · Initiates conditional or unconditional jumps, calls, returns and restart. Stack, I/O and Machine Control Instruction · Includes instructions for maintaining stack, reading from input port, writing to output port, setting and reading interrupt mask and clearing flags. 3/2/2021 4

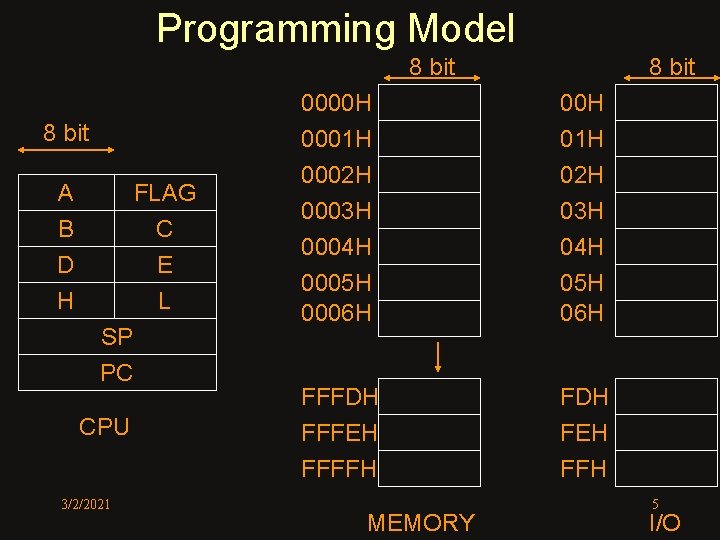

Programming Model 8 bit A B D H FLAG C E L SP PC CPU 3/2/2021 8 bit 0000 H 0001 H 00 H 01 H 0002 H 0003 H 0004 H 02 H 03 H 04 H 0005 H 0006 H 05 H 06 H FFFDH FFFEH FFFFH FDH MEMORY FEH FFH 5 I/O

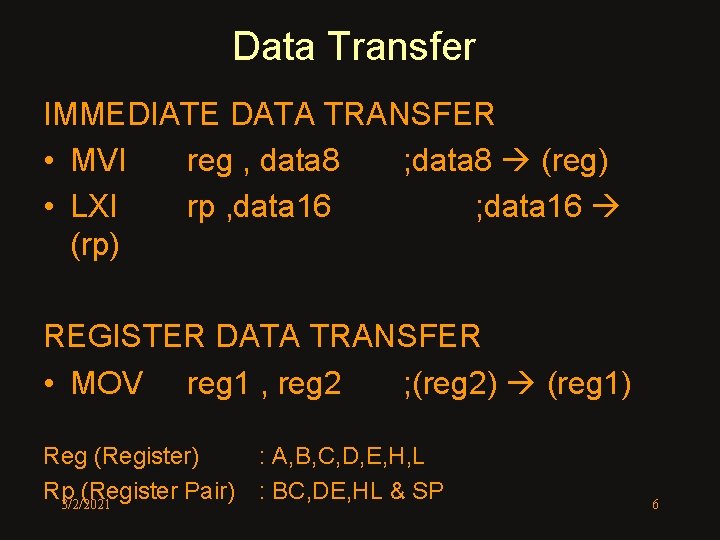

Data Transfer IMMEDIATE DATA TRANSFER • MVI reg , data 8 ; data 8 (reg) • LXI rp , data 16 ; data 16 (rp) REGISTER DATA TRANSFER • MOV reg 1 , reg 2 ; (reg 2) (reg 1) Reg (Register) Rp (Register Pair) 3/2/2021 : A, B, C, D, E, H, L : BC, DE, HL & SP 6

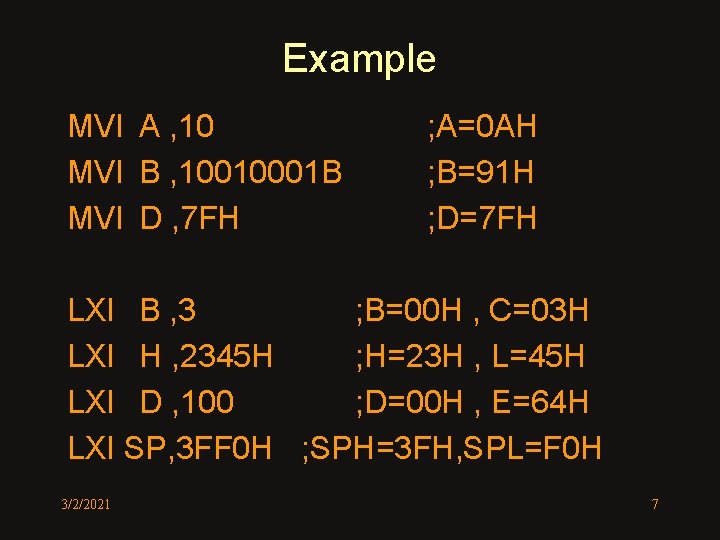

Example MVI A , 10 MVI B , 10010001 B MVI D , 7 FH ; A=0 AH ; B=91 H ; D=7 FH LXI B , 3 ; B=00 H , C=03 H LXI H , 2345 H ; H=23 H , L=45 H LXI D , 100 ; D=00 H , E=64 H LXI SP, 3 FF 0 H ; SPH=3 FH, SPL=F 0 H 3/2/2021 7

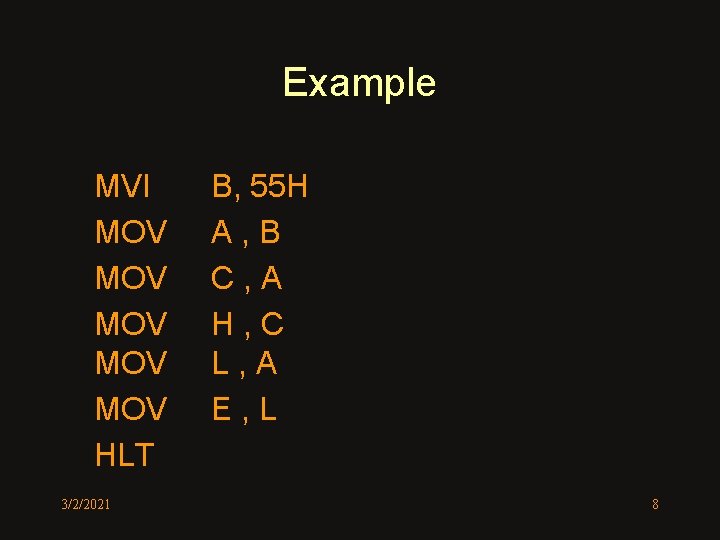

Example MVI MOV MOV MOV HLT 3/2/2021 B, 55 H A, B C, A H, C L, A E, L 8

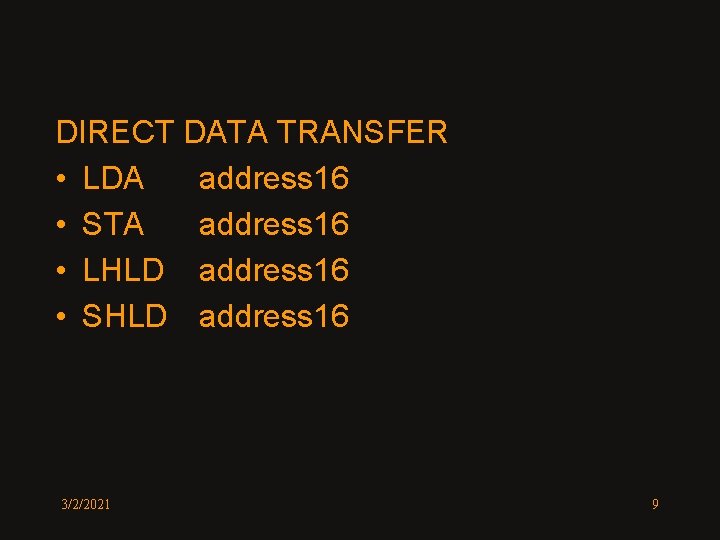

DIRECT DATA TRANSFER • LDA address 16 • STA address 16 • LHLD address 16 • SHLD address 16 3/2/2021 9

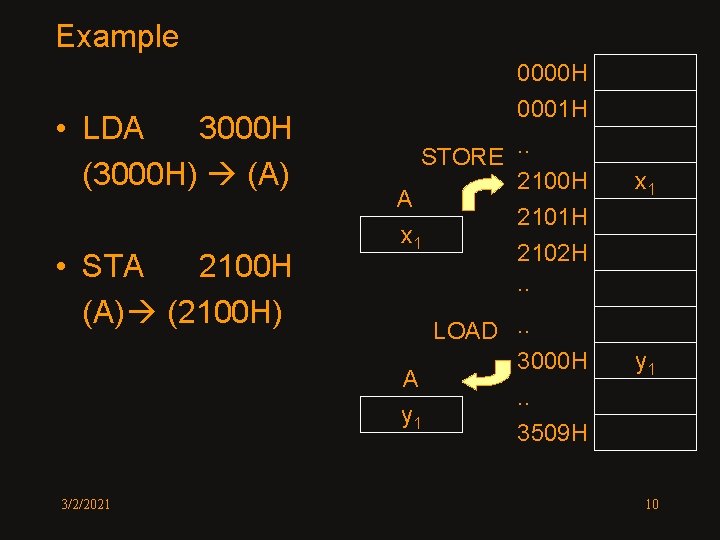

Example • LDA 3000 H (3000 H) (A) • STA 2100 H (A) (2100 H) 3/2/2021 0000 H 0001 H STORE. . 2100 H A 2101 H x 1 2102 H. . LOAD. . 3000 H A. . y 1 3509 H x 1 y 1 10

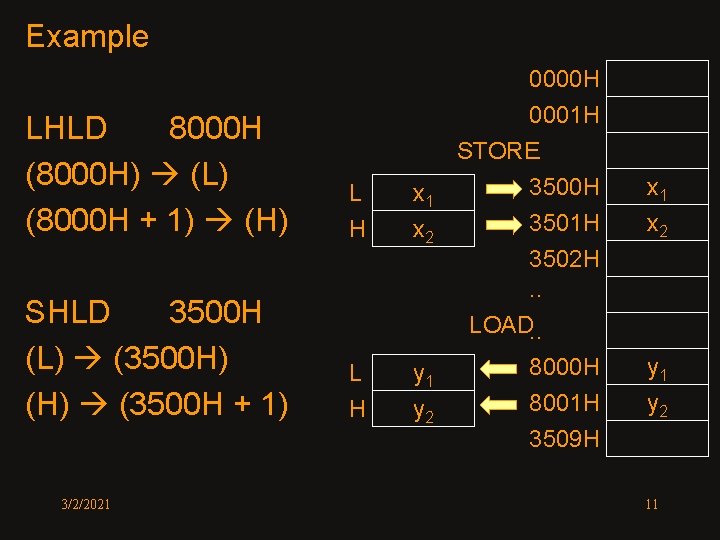

Example 0000 H 0001 H LHLD 8000 H (8000 H) (L) (8000 H + 1) (H) L H x 1 x 2 SHLD 3500 H (L) (3500 H) (H) (3500 H + 1) L H y 1 y 2 3/2/2021 STORE. . 3500 H 3501 H 3502 H. . LOAD. . 8000 H 8001 H 3509 H x 1 x 2 y 1 y 2 11

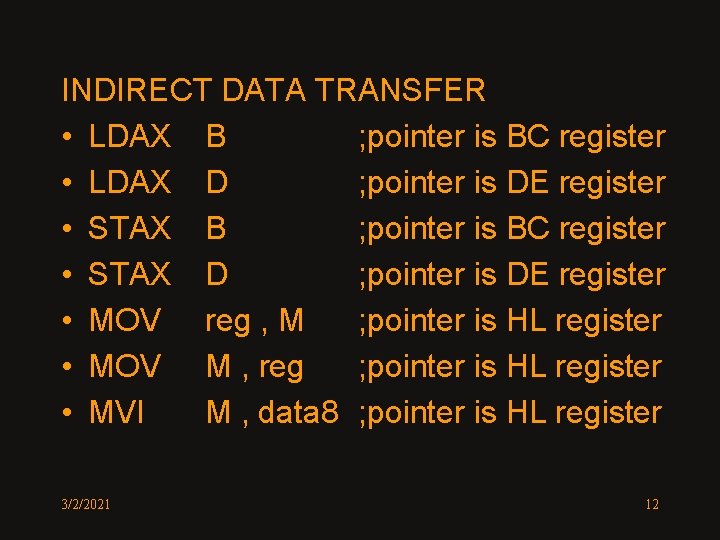

INDIRECT DATA TRANSFER • LDAX B ; pointer is BC register • LDAX D ; pointer is DE register • STAX B ; pointer is BC register • STAX D ; pointer is DE register • MOV reg , M ; pointer is HL register • MOV M , reg ; pointer is HL register • MVI M , data 8 ; pointer is HL register 3/2/2021 12

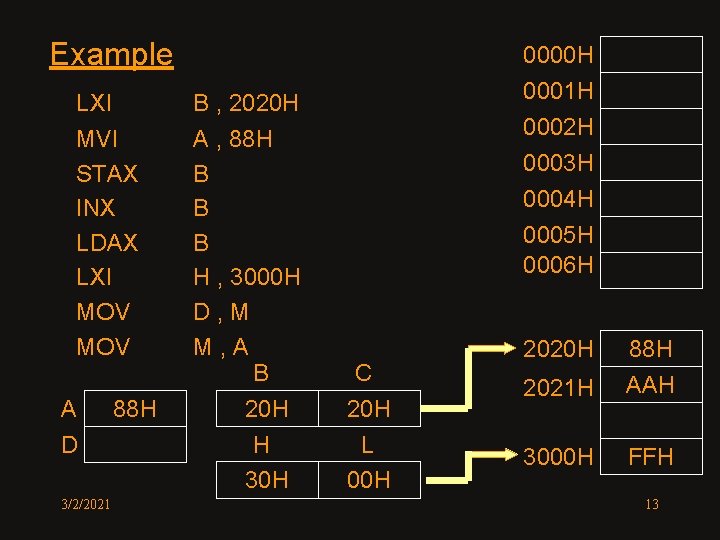

Example LXI B , 2020 H MVI STAX INX LDAX LXI MOV A , 88 H B B B H , 3000 H D, M M, A B A D 3/2/2021 88 H 20 H H 30 H 0001 H 0002 H 0003 H 0004 H 0005 H 0006 H C 20 H L 00 H 2021 H 88 H AAH 3000 H FFH 13

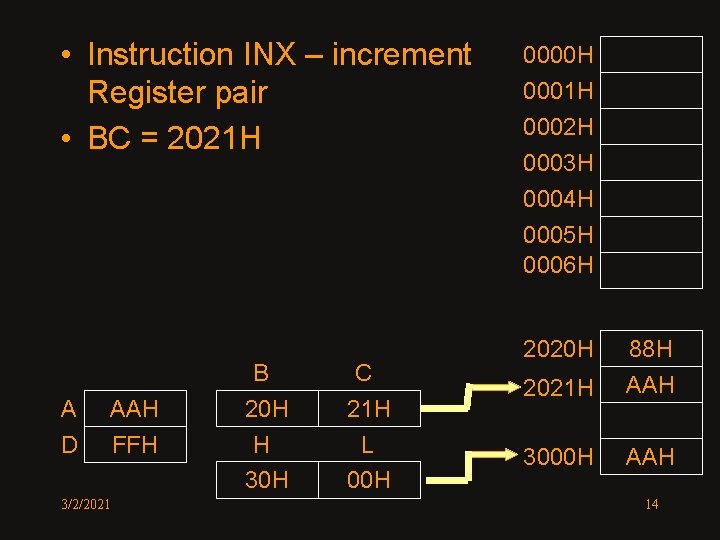

• Instruction INX – increment Register pair • BC = 2021 H A D AAH FFH 3/2/2021 B C 20 H H 30 H 21 H L 00 H 0001 H 0002 H 0003 H 0004 H 0005 H 0006 H 2020 H 2021 H 88 H AAH 3000 H AAH 14

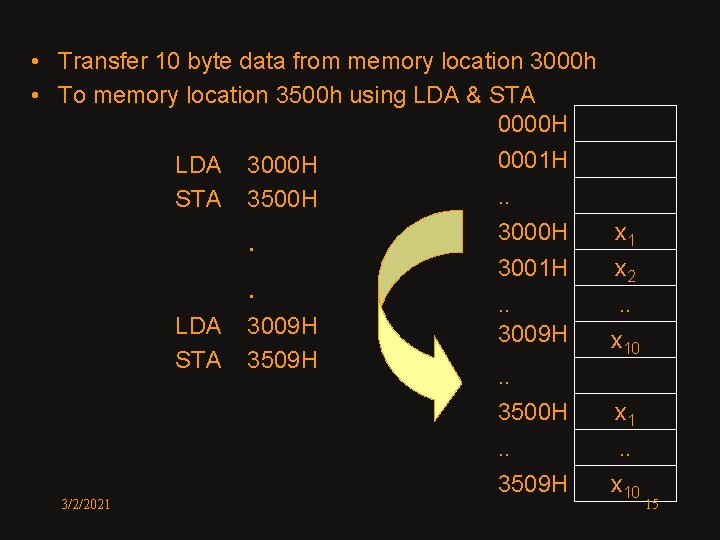

• Transfer 10 byte data from memory location 3000 h • To memory location 3500 h using LDA & STA 0000 H 0001 H LDA 3000 H. . STA 3500 H 3000 H. 3001 H. . . LDA 3009 H STA 3509 H. . 3500 H. . 3509 H 3/2/2021 x 2. . x 10 x 1. . x 10 15

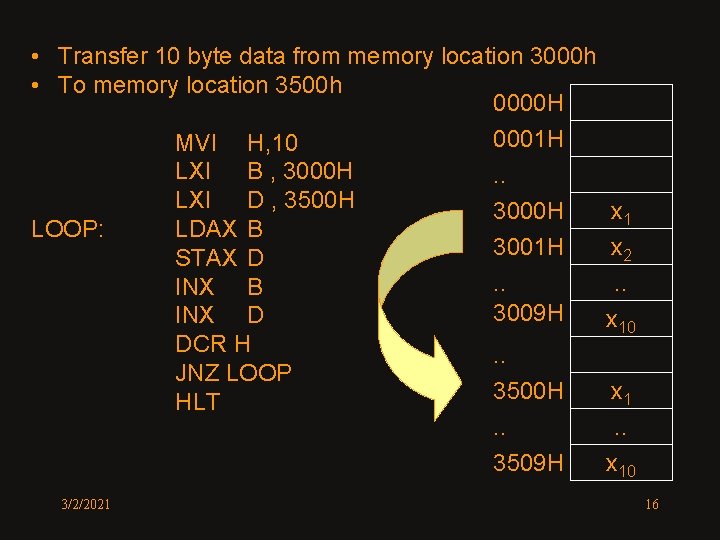

• Transfer 10 byte data from memory location 3000 h • To memory location 3500 h 0000 H 0001 H MVI H, 10 LXI B , 3000 H. . LXI D , 3500 H 3000 H LOOP: LDAX B 3001 H STAX D. . INX B 3009 H INX D DCR H. . JNZ LOOP 3500 H HLT. . 3509 H 3/2/2021 x 2. . x 10 x 1. . x 10 16

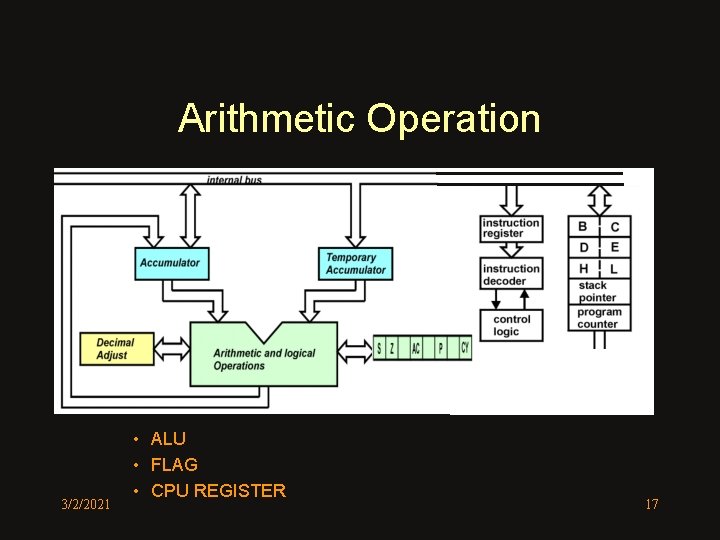

Arithmetic Operation 3/2/2021 • ALU • FLAG • CPU REGISTER 17

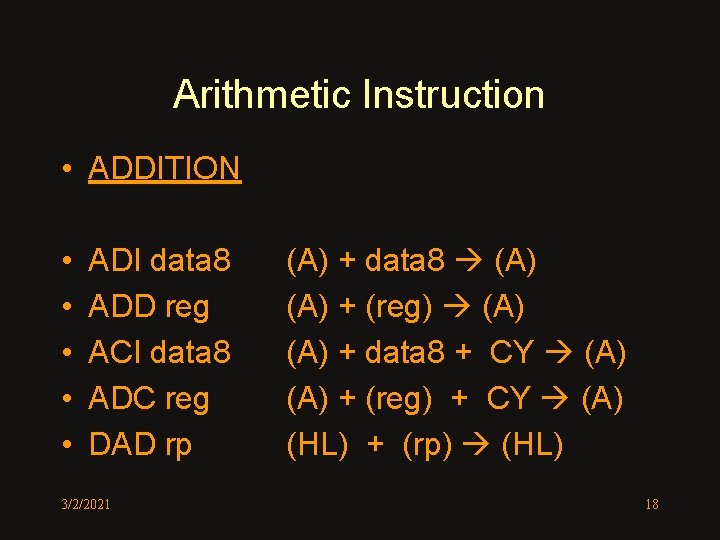

Arithmetic Instruction • ADDITION • • • ADI data 8 ADD reg ACI data 8 ADC reg DAD rp 3/2/2021 (A) + data 8 (A) + (reg) (A) + data 8 + CY (A) + (reg) + CY (A) (HL) + (rp) (HL) 18

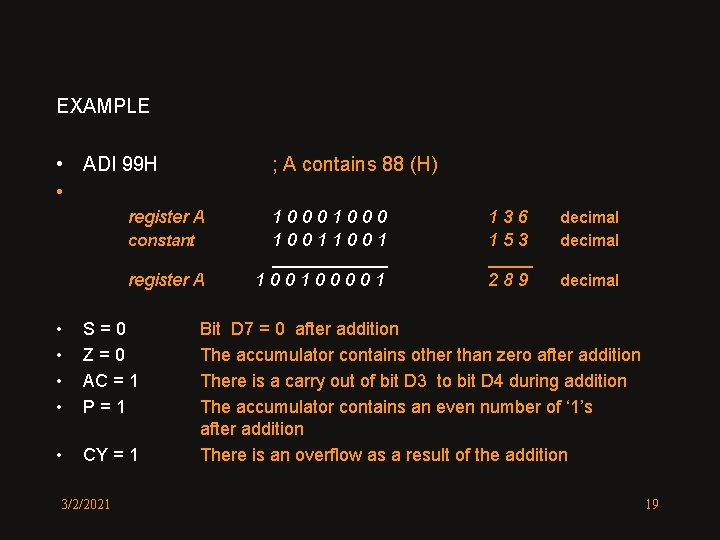

EXAMPLE • ADI 99 H • ; A contains 88 (H) register A constant register A • • S=0 Z=0 AC = 1 P=1 • CY = 1 3/2/2021 1000 1001 136 153 _______ 100100001 289 decimal Bit D 7 = 0 after addition The accumulator contains other than zero after addition There is a carry out of bit D 3 to bit D 4 during addition The accumulator contains an even number of ‘ 1’s after addition There is an overflow as a result of the addition 19

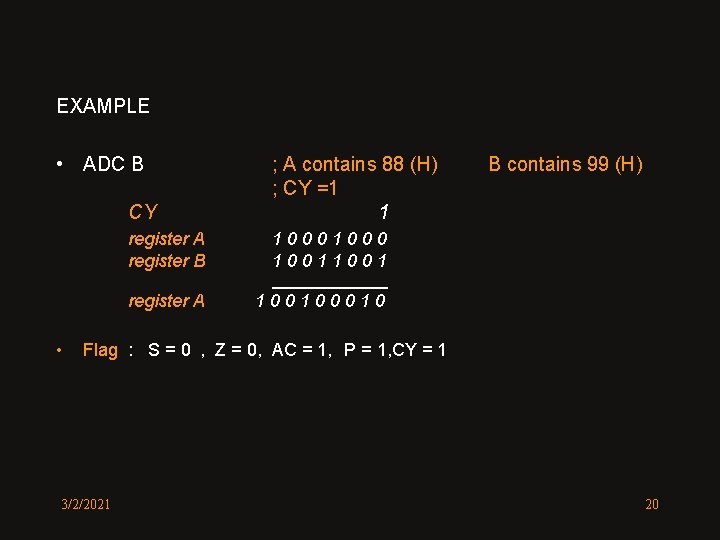

EXAMPLE • ADC B CY ; A contains 88 (H) ; CY =1 1 register A register B 1000 1001 B contains 99 (H) _______ register A • 10010 Flag : S = 0 , Z = 0, AC = 1, P = 1, CY = 1 3/2/2021 20

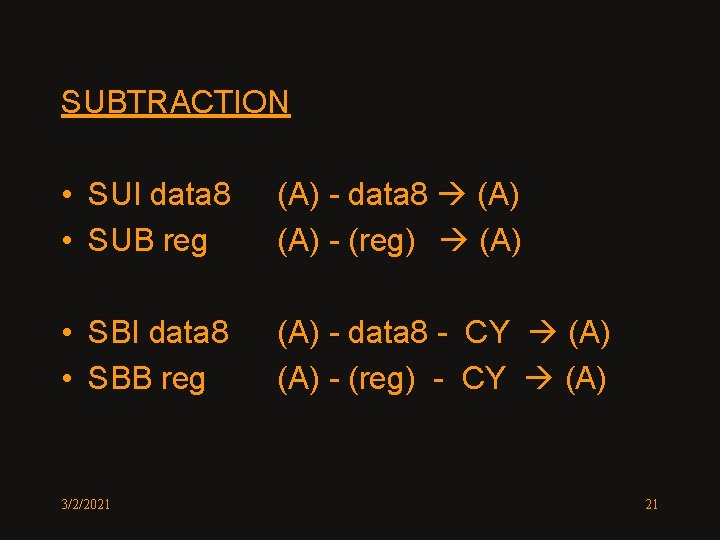

SUBTRACTION • SUI data 8 • SUB reg (A) - data 8 (A) - (reg) (A) • SBI data 8 • SBB reg (A) - data 8 - CY (A) - (reg) - CY (A) 3/2/2021 21

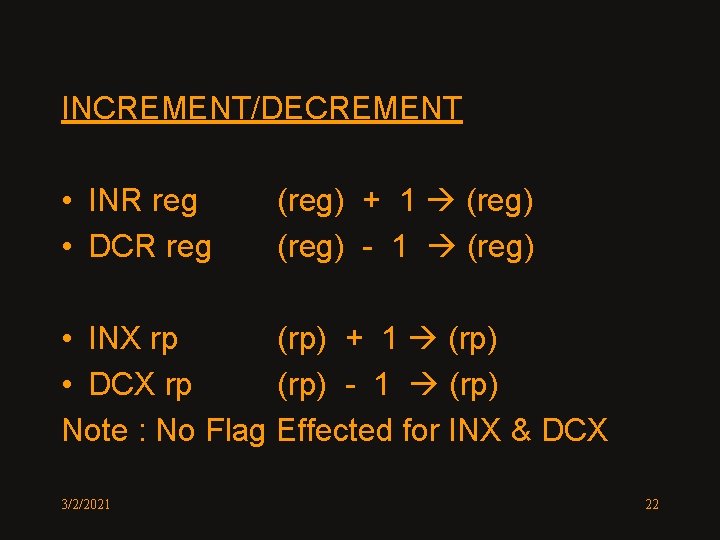

INCREMENT/DECREMENT • INR reg • DCR reg (reg) + 1 (reg) - 1 (reg) • INX rp (rp) + 1 (rp) • DCX rp (rp) - 1 (rp) Note : No Flag Effected for INX & DCX 3/2/2021 22

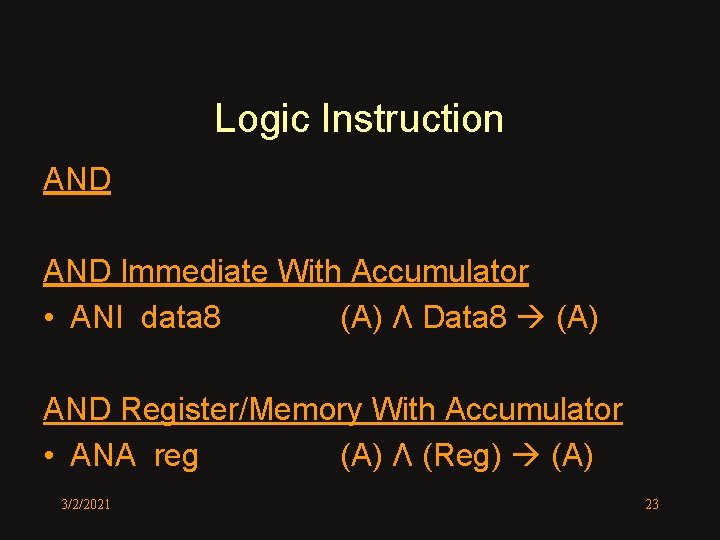

Logic Instruction AND Immediate With Accumulator • ANI data 8 (A) Λ Data 8 (A) AND Register/Memory With Accumulator • ANA reg (A) Λ (Reg) (A) 3/2/2021 23

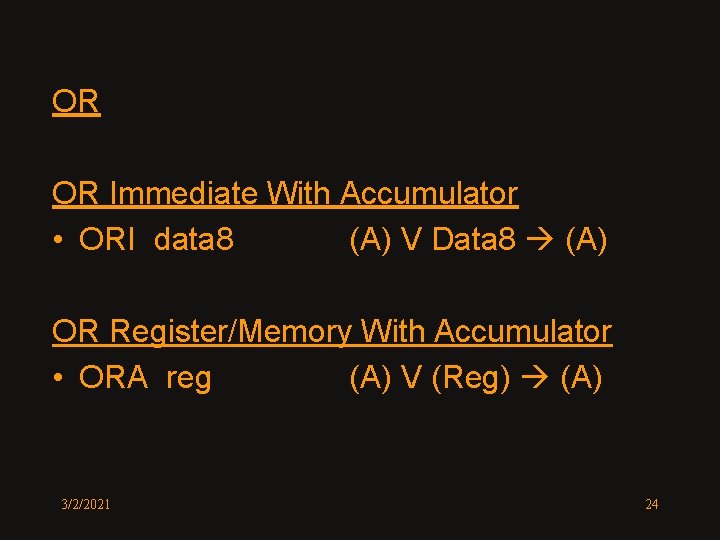

OR OR Immediate With Accumulator • ORI data 8 (A) V Data 8 (A) OR Register/Memory With Accumulator • ORA reg (A) V (Reg) (A) 3/2/2021 24

EXCLUSIVE-OR EX-OR Immediate With Accumulator • XRI data 8 (A) ⊕ Data 8 (A) EX-OR Register/Memory With Accumulator • XRA reg (A) ⊕ (Reg) (A) 3/2/2021 25

COMPLEMENT THE ACCUMULATOR • CMA ( A ) (A) COMPLEMENT THE CARRY STATUS • CMC 3/2/2021 (CY ) (CY) 26

COMPARE Compare Accumulator With Immediate Data • CPI data 8 (A) – data 8 Compare Accumulator With Register/Memory • CMP reg (A) – (reg) Note: Only flag affected 3/2/2021 27

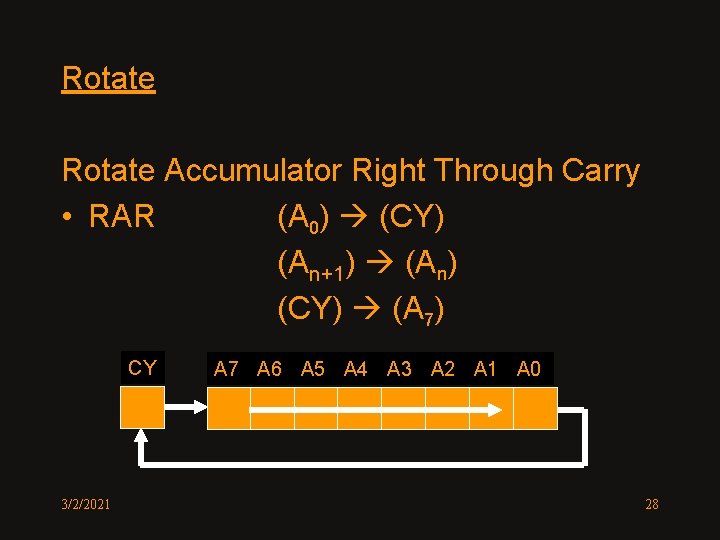

Rotate Accumulator Right Through Carry • RAR (A 0) (CY) (An+1) (An) (CY) (A 7) CY 3/2/2021 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 28

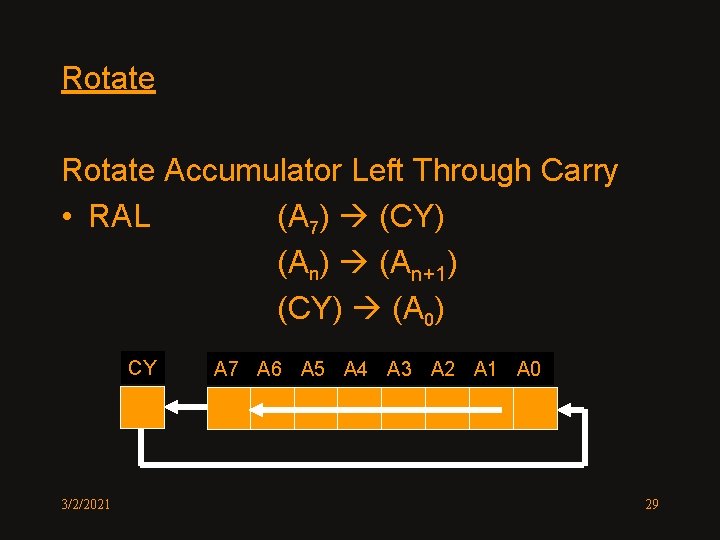

Rotate Accumulator Left Through Carry • RAL (A 7) (CY) (An) (An+1) (CY) (A 0) CY 3/2/2021 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 29

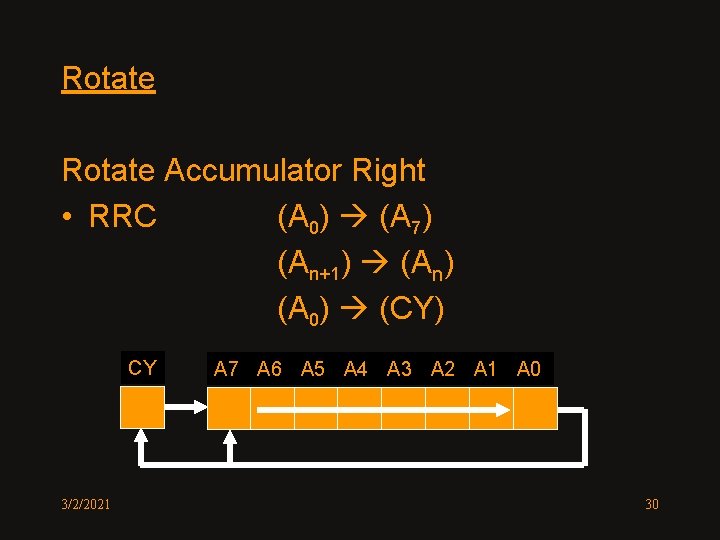

Rotate Accumulator Right • RRC (A 0) (A 7) (An+1) (An) (A 0) (CY) CY 3/2/2021 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 30

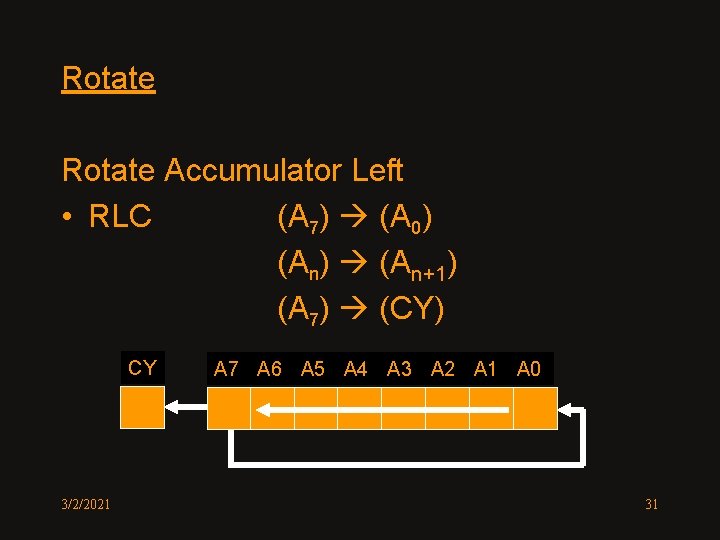

Rotate Accumulator Left • RLC (A 7) (A 0) (An) (An+1) (A 7) (CY) CY 3/2/2021 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 31

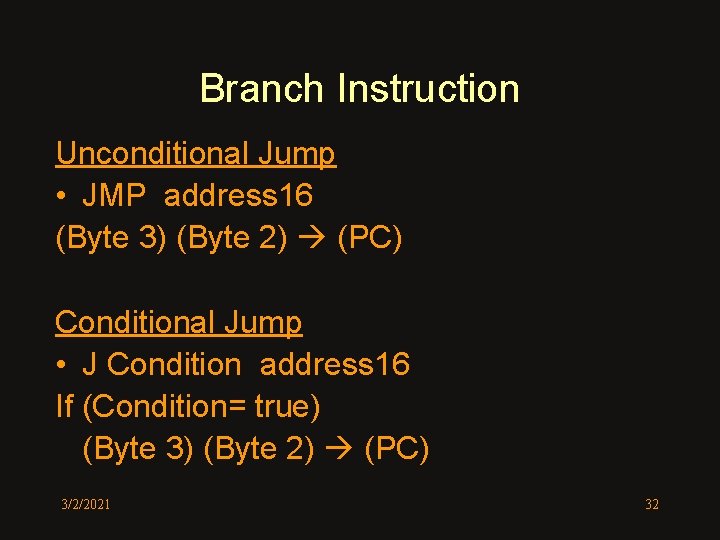

Branch Instruction Unconditional Jump • JMP address 16 (Byte 3) (Byte 2) (PC) Conditional Jump • J Condition address 16 If (Condition= true) (Byte 3) (Byte 2) (PC) 3/2/2021 32

Condition • JZ Z=1 Jump if Zero flag SET • JNZ Z=0 Jump if Zero flag NOT SET • JC CY=1 Jump if Carry flag SET • JNC CY=0 Jump if Carry flag NOT SET • JM S=1 Jump if Sign flag SET • JP S=0 Jump if Sign flag NOT SET • JPE P=1 Jump if Parity flag SET • JPO P=0 Jump if Parity flag NOT SET 3/2/2021 33

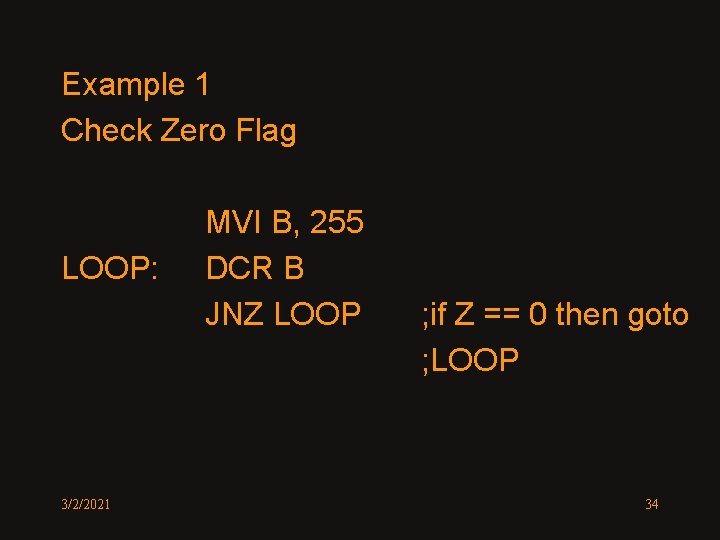

Example 1 Check Zero Flag LOOP: 3/2/2021 MVI B, 255 DCR B JNZ LOOP ; if Z == 0 then goto ; LOOP 34

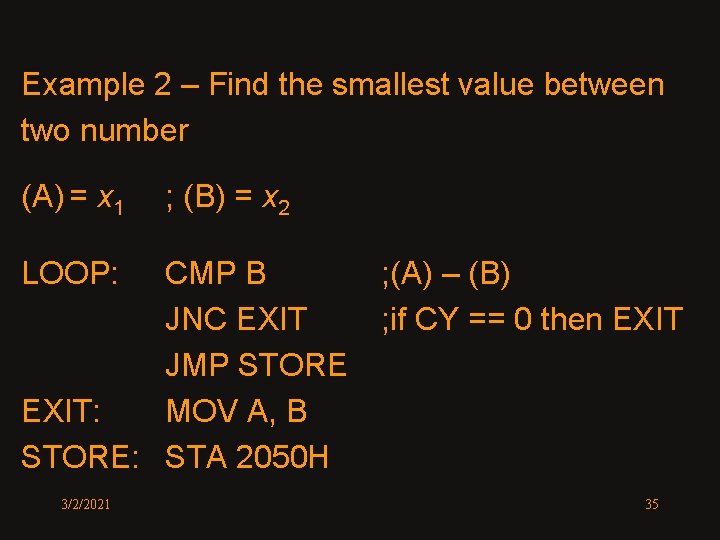

Example 2 – Find the smallest value between two number (A) = x 1 LOOP: ; (B) = x 2 CMP B JNC EXIT JMP STORE EXIT: MOV A, B STORE: STA 2050 H 3/2/2021 ; (A) – (B) ; if CY == 0 then EXIT 35

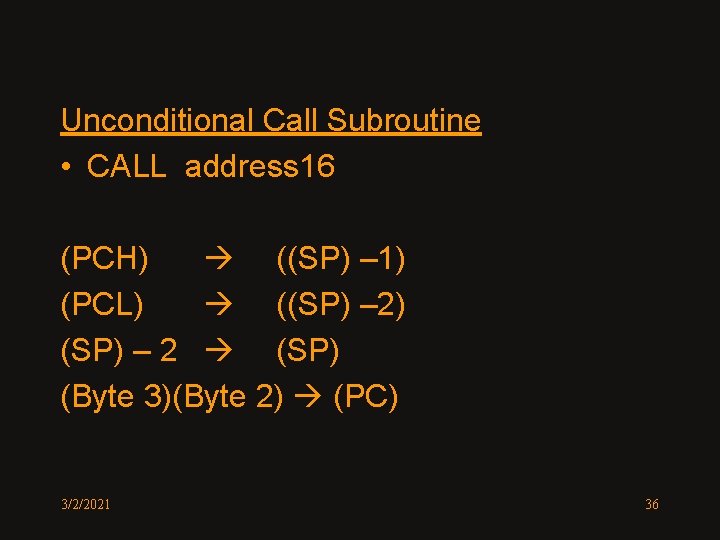

Unconditional Call Subroutine • CALL address 16 (PCH) ((SP) – 1) (PCL) ((SP) – 2) (SP) – 2 (SP) (Byte 3)(Byte 2) (PC) 3/2/2021 36

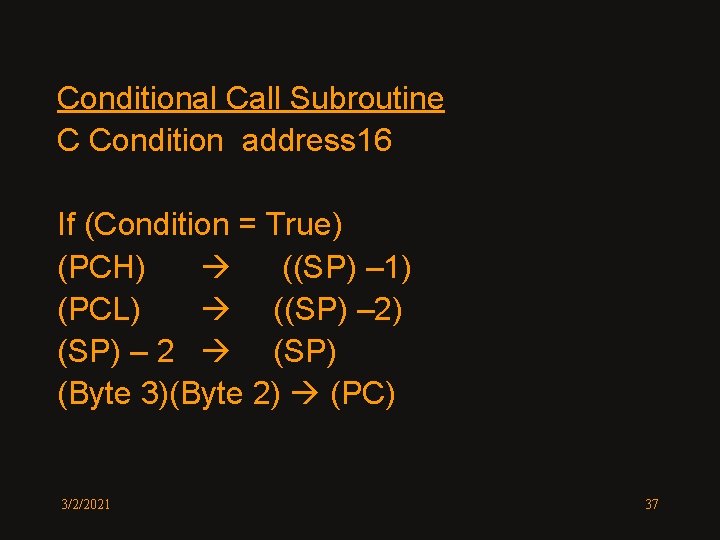

Conditional Call Subroutine C Condition address 16 If (Condition = True) (PCH) ((SP) – 1) (PCL) ((SP) – 2) (SP) – 2 (SP) (Byte 3)(Byte 2) (PC) 3/2/2021 37

• • CZ CNZ CC CNC CM CP CPE CPO 3/2/2021 Z=1 Call if Zero flag SET Z=0 Call if Zero flag NOT SET CY=1 Call if Carry flag SET CY=0 Call if Carry flag NOT SET S=1 Call if Sign flag SET S=0 Call if Sign flag NOT SET P=1 Call if Parity flag SET P=0 Call if Parity flag NOT SET 38

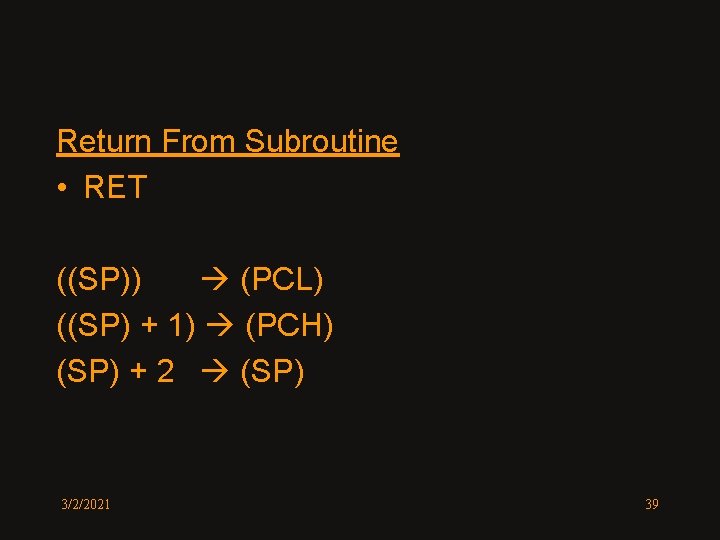

Return From Subroutine • RET ((SP)) (PCL) ((SP) + 1) (PCH) (SP) + 2 (SP) 3/2/2021 39

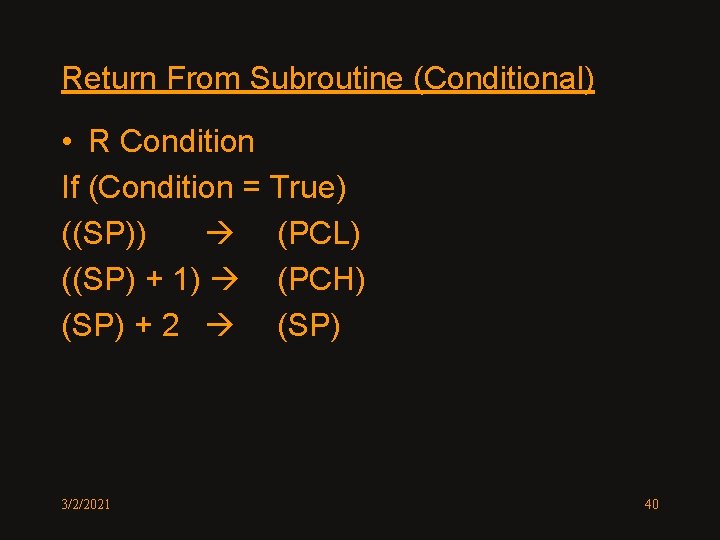

Return From Subroutine (Conditional) • R Condition If (Condition = True) ((SP)) (PCL) ((SP) + 1) (PCH) (SP) + 2 (SP) 3/2/2021 40

• • RZ RNZ RC RNC RM RP RPE RPO 3/2/2021 Z=1 Return if Zero flag SET Z=0 Return if Zero flag NOT SET CY=1 Return if Carry flag SET CY=0 Return if Carry flag NOT SET S=1 Return if Sign flag SET S=0 Return if Sign flag NOT SET P=1 Return if Parity flag SET P=0 Return if Parity flag NOT SET 41

Example REPEAT: DELAY: LOOP: 3/2/2021 LXI SP, 3 FF 0 H MVI A, 80 H OUT 83 H MVI A, 0 OUT 80 H CALL DELAY MVI A, 1 OUT 80 H CALL DELAY JMP REPEAT ; init Stack Pointer MVI B, 0 DCR B JNZ LOOP RET END ; Subroutine ; Init 8255, all port as output ; Call subroutine 42

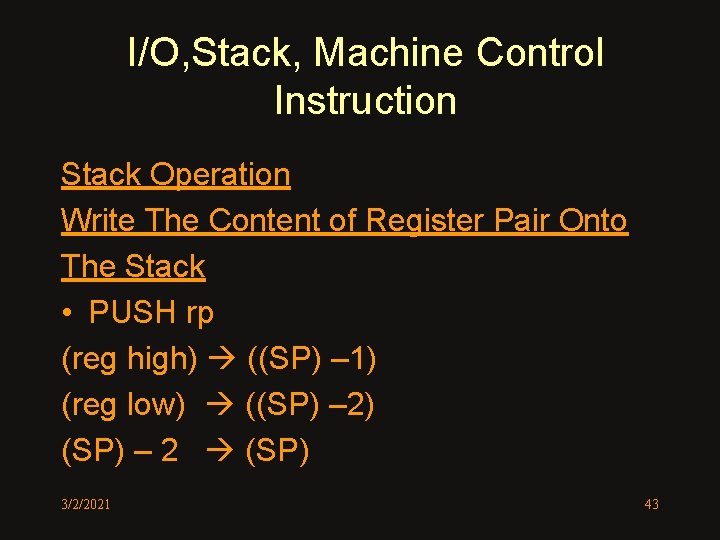

I/O, Stack, Machine Control Instruction Stack Operation Write The Content of Register Pair Onto The Stack • PUSH rp (reg high) ((SP) – 1) (reg low) ((SP) – 2) (SP) – 2 (SP) 3/2/2021 43

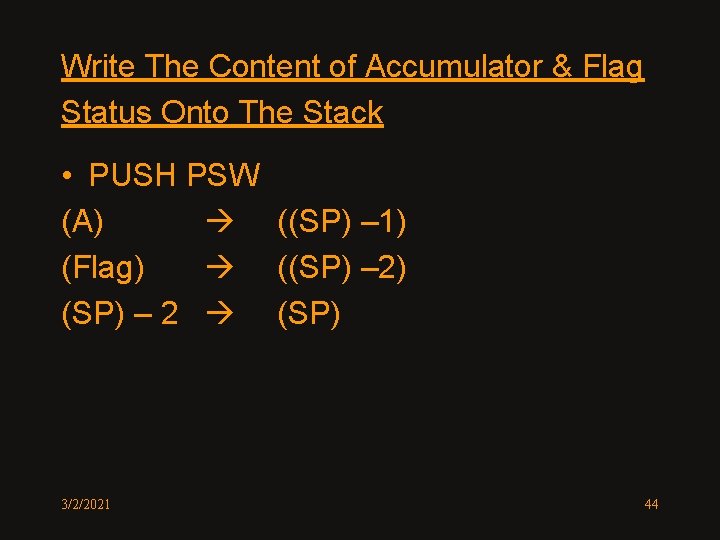

Write The Content of Accumulator & Flag Status Onto The Stack • PUSH PSW (A) ((SP) – 1) (Flag) ((SP) – 2) (SP) – 2 (SP) 3/2/2021 44

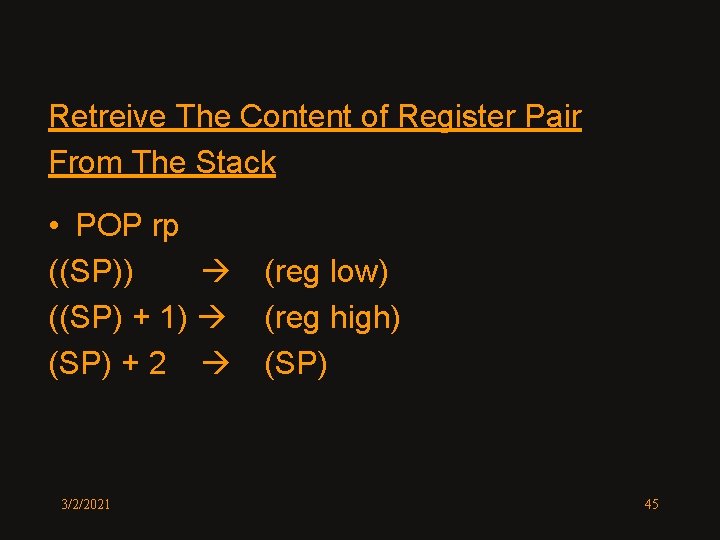

Retreive The Content of Register Pair From The Stack • POP rp ((SP)) (reg low) ((SP) + 1) (reg high) (SP) + 2 (SP) 3/2/2021 45

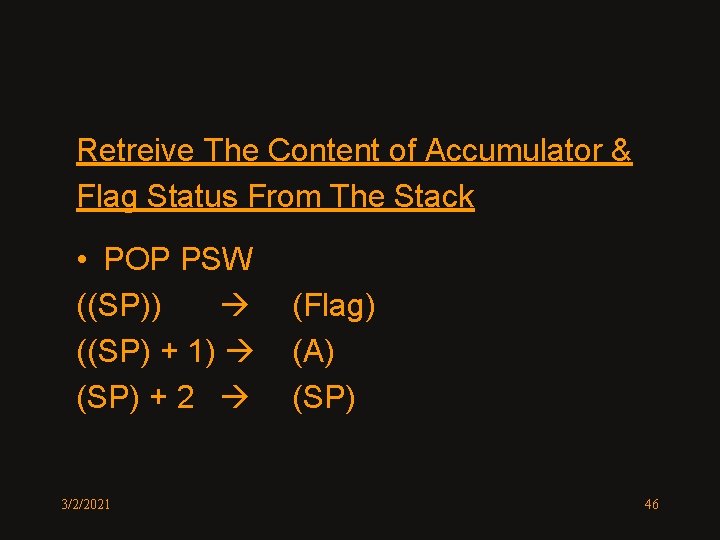

Retreive The Content of Accumulator & Flag Status From The Stack • POP PSW ((SP)) ((SP) + 1) (SP) + 2 3/2/2021 (Flag) (A) (SP) 46

STACK OPERATION Lecture 2 (Revision) 3/2/2021 47

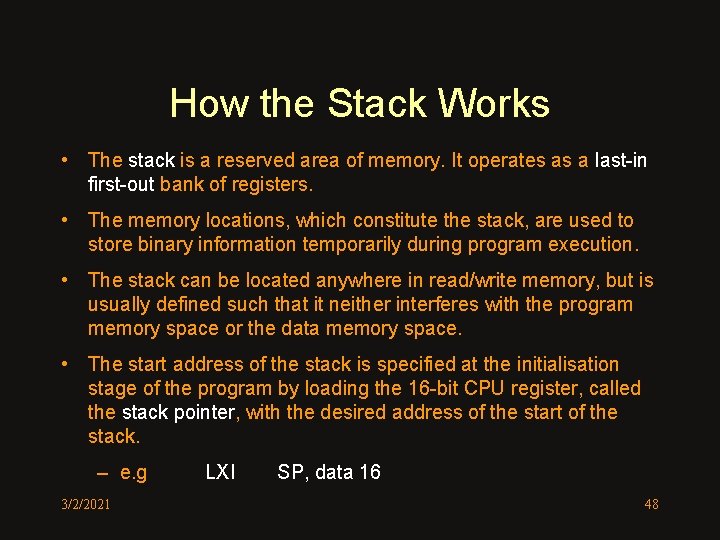

How the Stack Works • The stack is a reserved area of memory. It operates as a last-in first-out bank of registers. • The memory locations, which constitute the stack, are used to store binary information temporarily during program execution. • The stack can be located anywhere in read/write memory, but is usually defined such that it neither interferes with the program memory space or the data memory space. • The start address of the stack is specified at the initialisation stage of the program by loading the 16 -bit CPU register, called the stack pointer, with the desired address of the start of the stack. – e. g 3/2/2021 LXI SP, data 16 48

How the Stack Works • Data from CPU register pairs are stored in the stack area of memory when the processor executes a push rp instruction. • The contents of the program counter is automatically stored in the stack area of memory whenever the processor executes a call or restart (rst n) instruction. • Data stored in the stack area of memory are returned to processor register pairs when the processor executes a pop rp instruction. • Data is automatically transferred from the stack area of memory to the program counter whenever the processor executes a return (ret) instruction. 3/2/2021 49

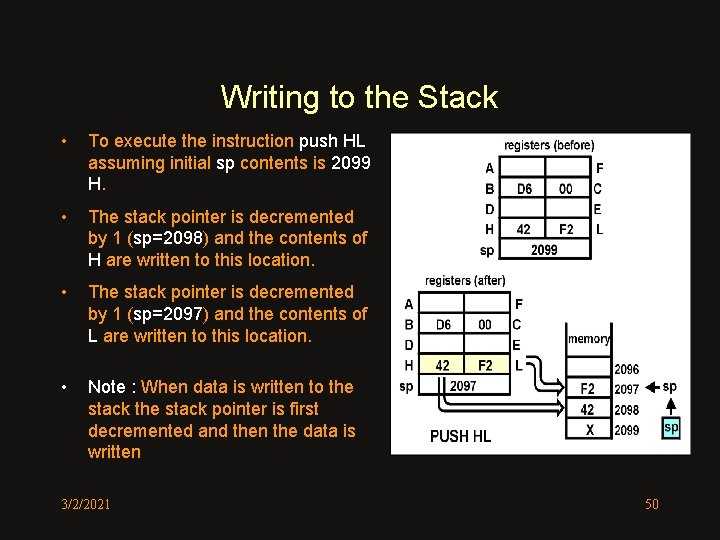

Writing to the Stack • To execute the instruction push HL assuming initial sp contents is 2099 H. • The stack pointer is decremented by 1 (sp=2098) and the contents of H are written to this location. • The stack pointer is decremented by 1 (sp=2097) and the contents of L are written to this location. • Note : When data is written to the stack pointer is first decremented and then the data is written 3/2/2021 50

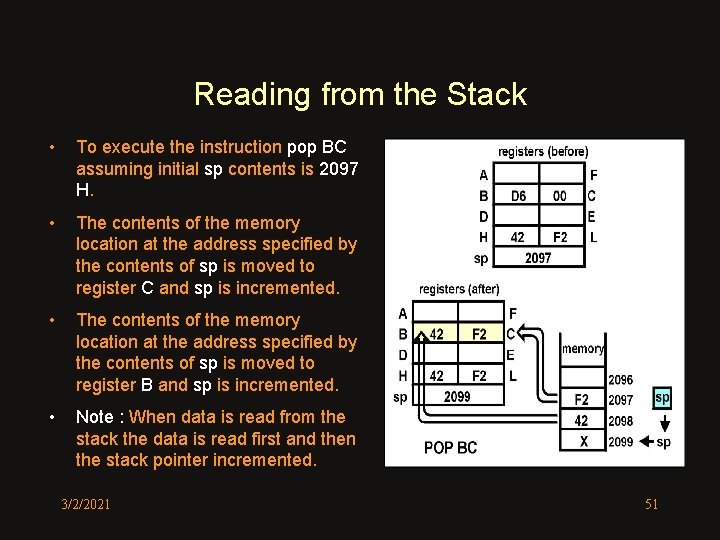

Reading from the Stack • To execute the instruction pop BC assuming initial sp contents is 2097 H. • The contents of the memory location at the address specified by the contents of sp is moved to register C and sp is incremented. • The contents of the memory location at the address specified by the contents of sp is moved to register B and sp is incremented. • Note : When data is read from the stack the data is read first and then the stack pointer incremented. 3/2/2021 51

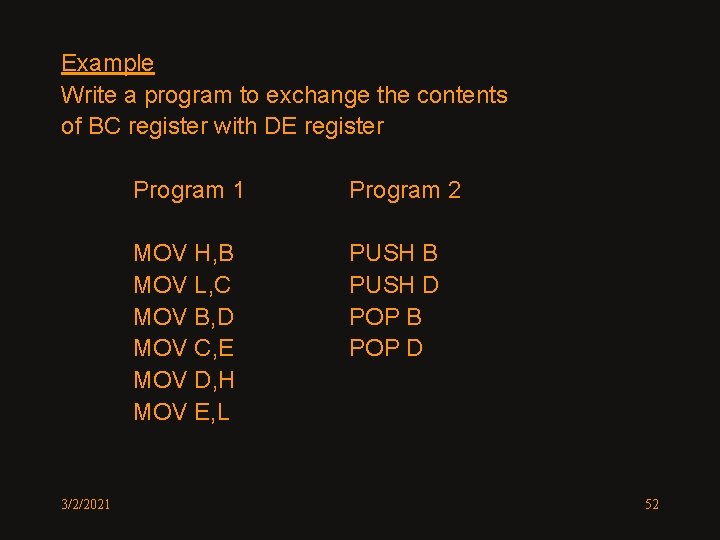

Example Write a program to exchange the contents of BC register with DE register 3/2/2021 Program 2 MOV H, B MOV L, C MOV B, D MOV C, E MOV D, H MOV E, L PUSH B PUSH D POP B POP D 52

Input/Output Operation Input From The Port • IN Port_Address (port) (A) Output To Port • OUT Port_Address (A) (Port) 3/2/2021 53

Example Input From The Port IN 80 H STA 2100 H ; Read from Port 80 H ; Store to Memory Output To Port MVI A, 01 H OUT 81 H 3/2/2021 ; Write 01 H to Port 81 H 54

Interrupt RIM SIM DI EI Read interrupt mask Set Interrupt mask Disable Interrupt Enable Interrupt (Detail discussion in interrupt topic) 3/2/2021 55

NEXT WEEK ASSEMBLY LANGUAGE PROGRAMMING 3/2/2021 56

- Slides: 56