Introduction to Assembly Chapter 2 Sepehr Naimi www

Introduction to Assembly Chapter 2 Sepehr Naimi www. Nicer. Land. com www. Micro. Digital. Ed. com

Topics n AVR’s CPU n n n Its architecture Some simple programs Data Memory access Program memory RISC architecture 2

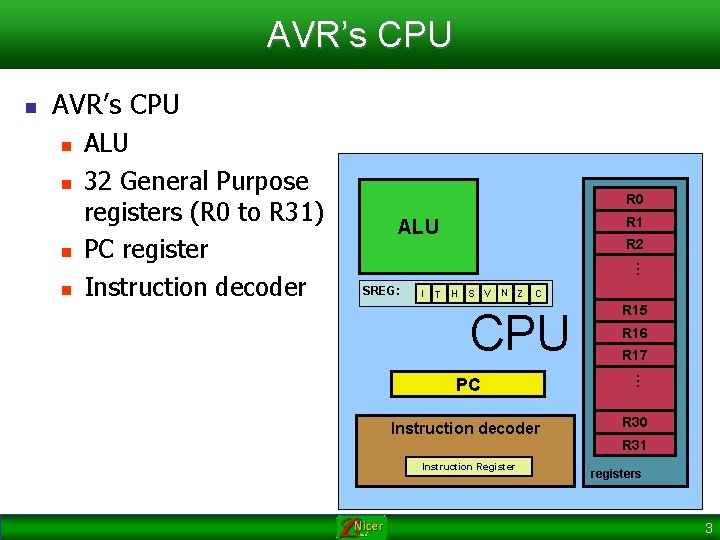

AVR’s CPU n n n R 0 R 1 ALU R 2 … n ALU 32 General Purpose registers (R 0 to R 31) PC register Instruction decoder SREG: I T H S V N Z C CPU Instruction decoder Instruction Register R 16 R 17 … PC R 15 R 30 R 31 registers 3

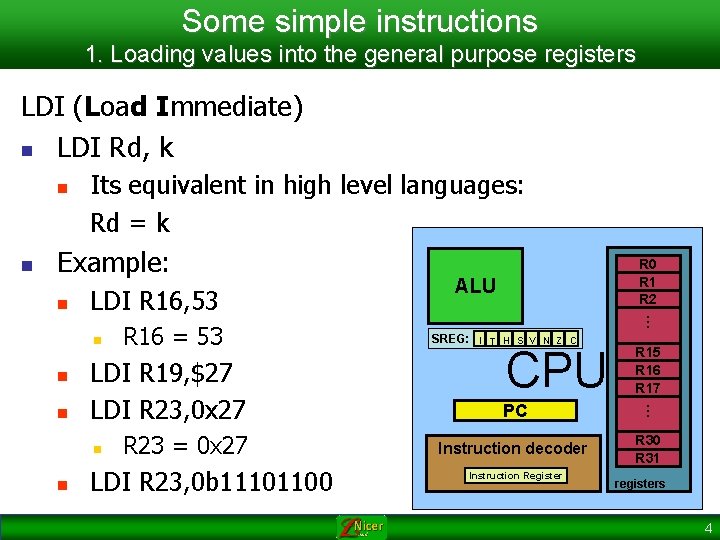

Some simple instructions 1. Loading values into the general purpose registers LDI (Load Immediate) n LDI Rd, k n n Its equivalent in high level languages: Rd = k Example: n LDI R 16, 53 n LDI R 19, $27 LDI R 23, 0 x 27 n n R 23 = 0 x 27 LDI R 23, 0 b 11101100 SREG: I T H S V N Z C CPU R 15 R 16 R 17 PC … n R 16 = 53 ALU … n R 0 R 1 R 2 Instruction decoder R 30 R 31 Instruction Register registers 4

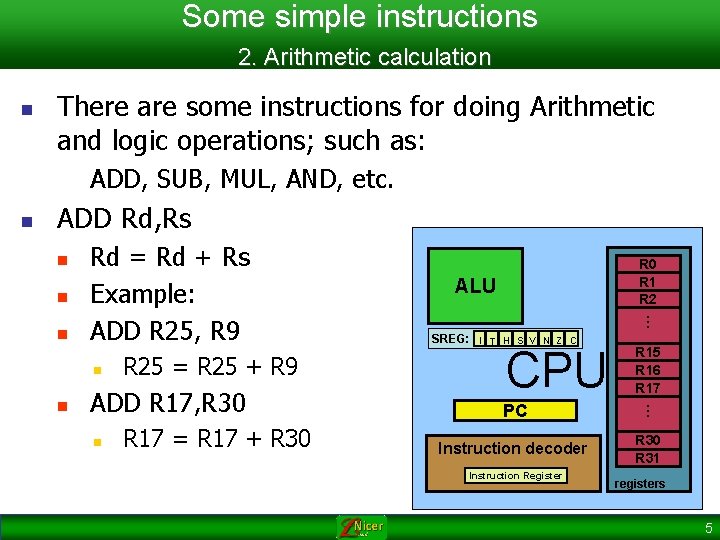

Some simple instructions 2. Arithmetic calculation n There are some instructions for doing Arithmetic and logic operations; such as: ADD, SUB, MUL, AND, etc. n ADD Rd, Rs n n n ADD R 17, R 30 n R 17 = R 17 + R 30 ALU SREG: I T H S V N Z C CPU R 15 R 16 R 17 PC … n R 25 = R 25 + R 9 R 0 R 1 R 2 … n Rd = Rd + Rs Example: ADD R 25, R 9 Instruction decoder R 30 R 31 Instruction Register registers 5

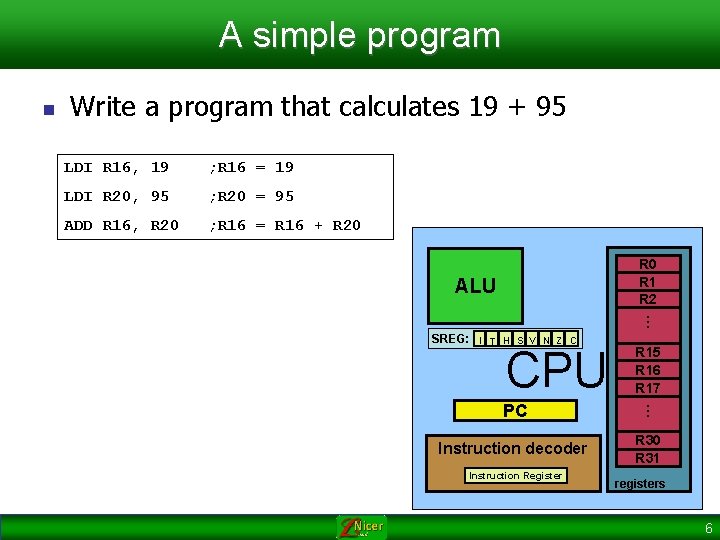

A simple program n Write a program that calculates 19 + 95 LDI R 16, 19 ; R 16 = 19 LDI R 20, 95 ; R 20 = 95 ADD R 16, R 20 ; R 16 = R 16 + R 20 R 1 R 2 ALU … SREG: I T H S V N Z C CPU R 15 R 16 R 17 PC … Instruction decoder R 30 R 31 Instruction Register registers 6

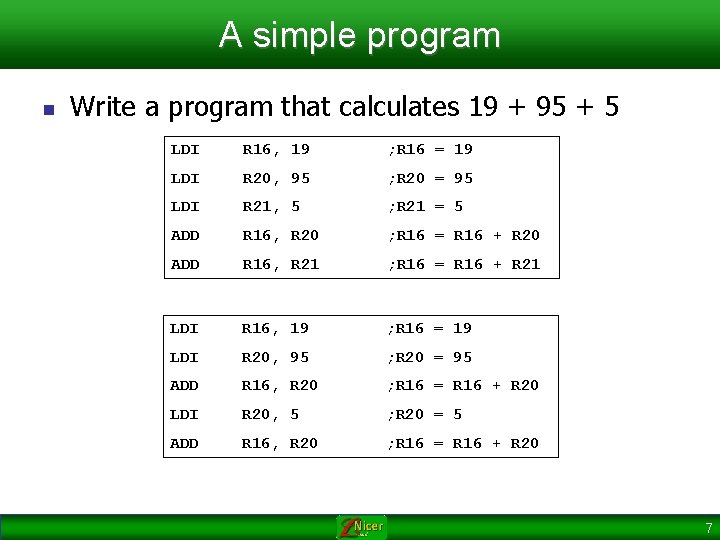

A simple program n Write a program that calculates 19 + 95 + 5 LDI R 16, 19 ; R 16 = 19 LDI R 20, 95 ; R 20 = 95 LDI R 21, 5 ; R 21 = 5 ADD R 16, R 20 ; R 16 = R 16 + R 20 ADD R 16, R 21 ; R 16 = R 16 + R 21 LDI R 16, 19 ; R 16 = 19 LDI R 20, 95 ; R 20 = 95 ADD R 16, R 20 ; R 16 = R 16 + R 20 LDI R 20, 5 ; R 20 = 5 ADD R 16, R 20 ; R 16 = R 16 + R 20 7

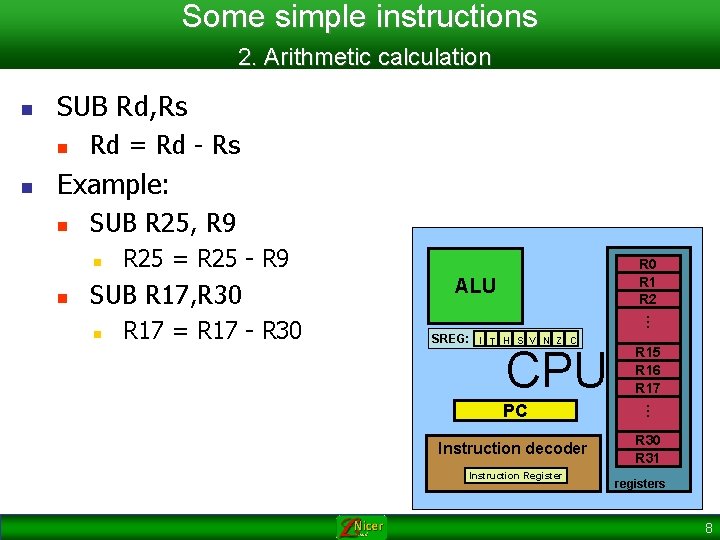

Some simple instructions 2. Arithmetic calculation n SUB Rd, Rs n n Rd = Rd - Rs Example: n SUB R 25, R 9 n n R 25 = R 25 - R 9 SUB R 17, R 30 R 17 = R 17 - R 30 ALU … n R 0 R 1 R 2 SREG: I T H S V N Z C CPU R 15 R 16 R 17 PC … Instruction decoder R 30 R 31 Instruction Register registers 8

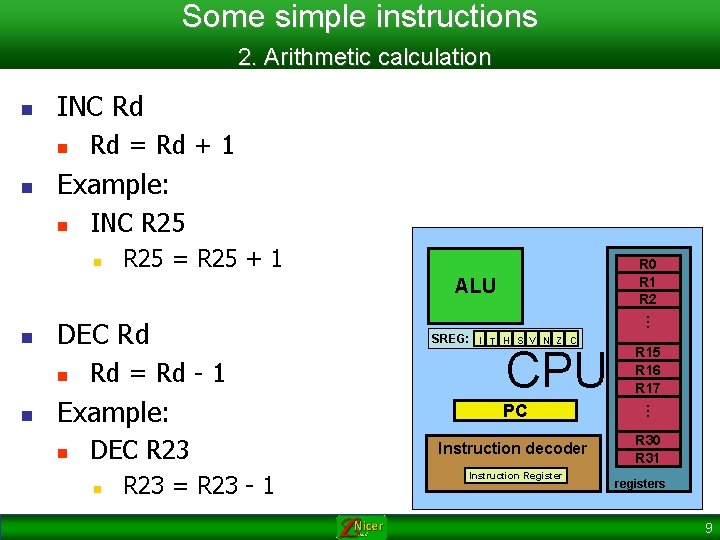

Some simple instructions 2. Arithmetic calculation n INC Rd n n Rd = Rd + 1 Example: n INC R 25 n R 25 = R 25 + 1 R 0 R 1 R 2 ALU DEC Rd n Example: n DEC R 23 n R 23 = R 23 - 1 SREG: I T H S V N Z C CPU R 15 R 16 R 17 PC … n Rd = Rd - 1 … n Instruction decoder R 30 R 31 Instruction Register registers 9

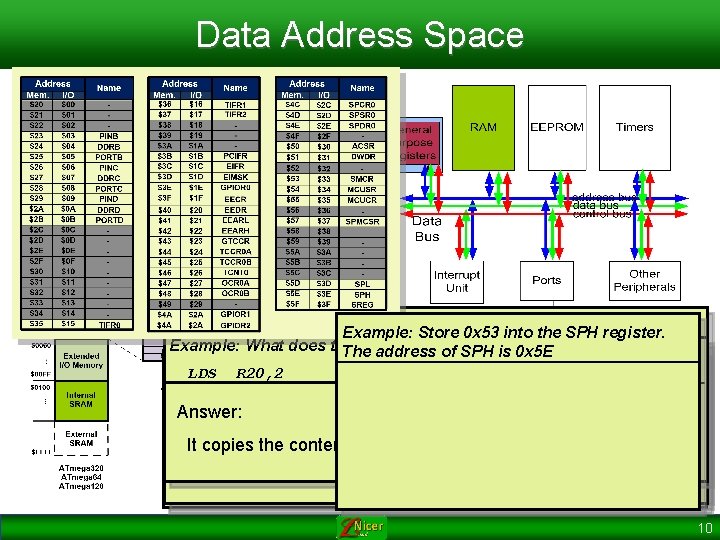

Data Address Space Example: Add contents. Example: of location 0 x 90 to contents of location 0 x 95 Store 0 x 53 into the SPH register. Example: doesinthe following instruction do? space) and store What the result location 0 x 313. LDS (Load direct from data space) STS (Store direct to data The address of SPH is 0 x 5 E Example: Write a program that stores 55 into location 0 x 80 of RAM. Example: Write a program that copies the contents of location 0 x 80 LDS R 20, 2 Solution: of RAM into location 0 x 81. LDS addr ; [addr]=Rd ; Rd = [addr] STS Rd, addr, Rd LDS R 20, 0 x 90 Solution: ; R 20 = [0 x 90] Solution: Answer: LDS R 20, R 21, 55 0 x 95 [0 x 95] LDI =; R 21 R 20, = 0 x 53 ; R 20 = 0 x 53 Example: LDI ; R 20 55 Solution: It copies contents of into R 20; as+ 2 R 21 is the; SPH address ADD the R 20, R 21 = R 20 STSR 2 ; R 20 0 x 5 E, R 20 = R 20 of R 2. STS 0 x 80, R 20 ; [0 x 80] = R 20 = 55 LDS R 20, 0 x 80 LDS ; R 20 = [0 x 80] 0 x 60 STS R 1, 0 x 60, R 15 ; [0 x 60] = R 15 STS 0 x 313, R 20 0 x 81, R 20 ; [0 x 313] = R 20 ; [0 x 81] = R 20 = [0 x 80] 10

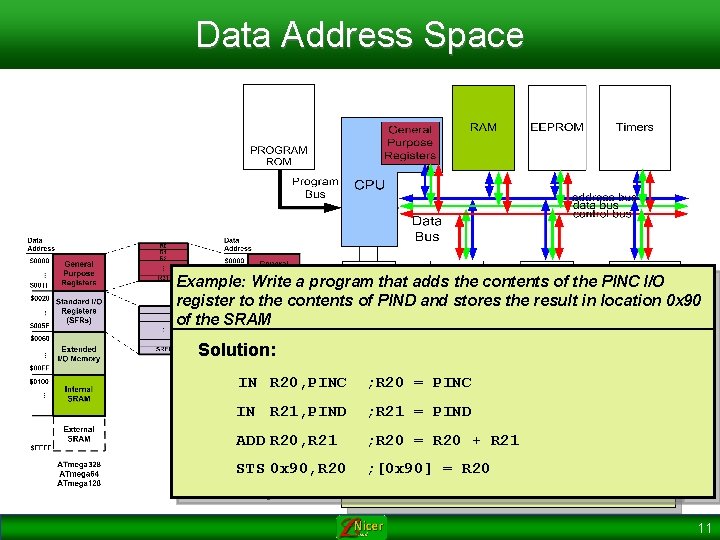

Data Address Space Example: Write a program that adds the contents of the PINC I/O IN (IN fromthe IOI/O location) Using Names of registers register to the contents of PIND and stores in location 0 x 90 OUT (OUT to I/Oresult location) of the SRAM Solution: IN R 20, PINC IN R 21, PIND ADD R 20, R 21 STS 0 x 90, R 20 IN Rd, IOaddress ; Rd = [addr] Example: OUT IOAddr, Rd ; [addr]=Rd OUT =SPH, R 12 ; R 20 PINC Example: IN ; R 21 =R 15, SREG PIND Example: ; OUT 0 x 3 E, R 12 ; IN R 15, 0 x 3 F IN =R 1, 0 x 3 F = SREG ; R 20 + R 21; R 1 OUT 0 x 3 F, R 12 ; SREG = R 12 IN R 17, 0 x 3 E ; [0 x 90] = R 20 ; R 17 = SPH OUT 0 x 3 E, R 15 ; SPH = R 15 11

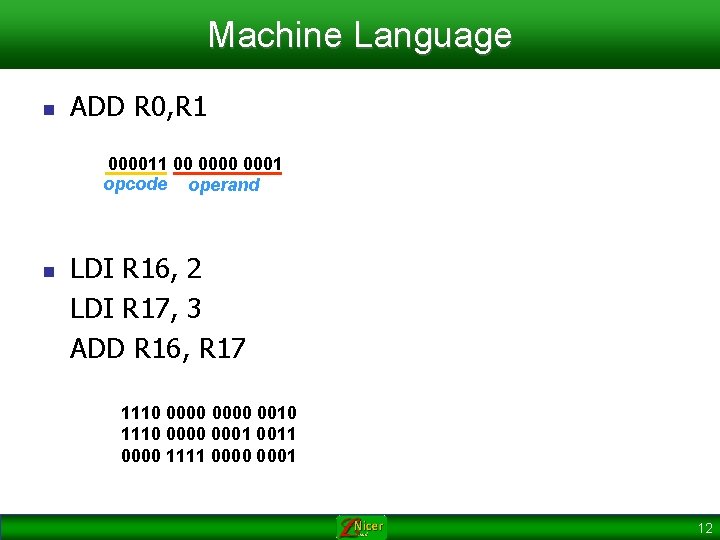

Machine Language n ADD R 0, R 1 000011 00 0001 opcode operand n LDI R 16, 2 LDI R 17, 3 ADD R 16, R 17 1110 0000 0010 1110 0001 0011 0000 1111 0000 0001 12

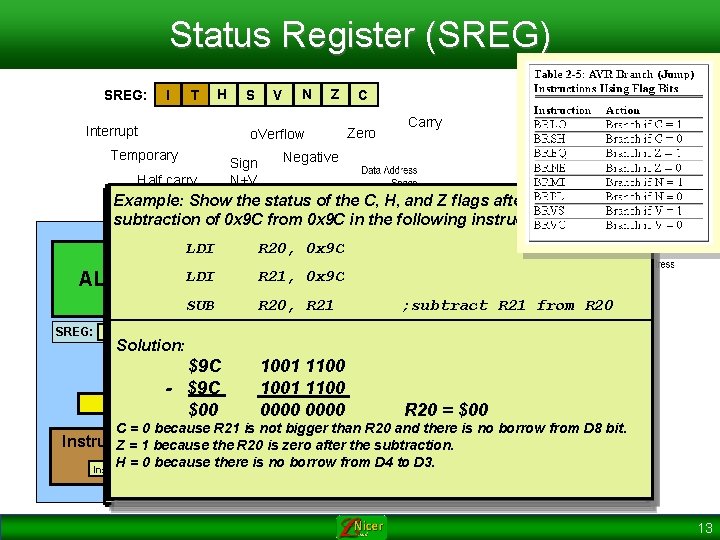

Status Register (SREG) SREG: I T H S Interrupt N V Z o. Verflow Temporary Half carry Sign N+V C Zero Carry Negative Example: Showthe thestatusof ofthe the. C, C, H, H, and. ZZ flagsafterthe theaddition Example: Show the status of the C, H, and flags after the Example: Show the status of the C, H, and ZZflags after the addition subtraction of 0 x 9 C from 0 x 9 C in the following instructions: subtraction of 0 x 23 from 0 x. A 5 in the following instructions: 0 x 73 from 0 x 52 of 0 x 64 in the following instructions: of 0 x 9 C 0 x 38 and 0 x 2 F LDI 0 x 38 R 20, 0 x 9 C LDI R 20, 0 x. A 5 0 x 52 R 20, LDI R 16, ; R 16 = 0 x 38 ALU LDI SUB R 17 R 20, R 21; add R 17; add ; subtract R 21 from R 20 SUB R 20, R 21 ; subtract ADD R 21 to. R 21 R 20 from R 16, to R 16 SREG: I T H S V N Z C Solution: CPU … ADD R 0 R 1 0 x 64 LDI 0 x 2 F R 21, 0 x 9 C LDI R 21, 0 x 23 0 x 73 LDI R 21, R 17, ; R 17 = 0 x 2 F R 2 R 15 11 0101 0010 R 16 1001 1100 1010 0101 0011 1000 1001 R 17 0011 0111 … $52 $9 C $A 5 $38 $9 C $73 $9 C 1001 0100 1100 $23 0010 0011 $2 F 1111 +-- +$64 0110 $DF 1101 1111 R 20 $DF PC $00 0000 R 20 == $00 $82 1000 0010 R 20 == 00 $82 $67 0110 0111 R 16 0 x 67 $100 1 0000 R 20 C = 1 because R 21 is bigger than R 20 and there is a borrow from D 8 bit. C===100 becausethere R 21 is is not bigger than R 20 andbit. there is is no no borrow from D 8 bit. C because R 21 bigger than and there C isnot a carry beyond the D 7 R 30 H = 1 because there is. R 31 a borrow from D 4 D 3 toto D 3. carry from the D 4 bit. H = 0 because there is no borrow from D 4 to D 3. Z = 1 because the R 20 (the result) has a value in it after the addition. Instruction Register Z = 0 because the R 16 (the result) has a value 0 other than 0 after the addition. Z == 00 decoder because the R 20 a value otherthe than after the subtraction. C because there is has no carry beyond D 7 zero Instruction because there the R 20 iscarry zero after the D 3 subtraction. ZZ = == 1 01 because the a value other than 0 bit. after the subtraction. H is ahas from the to the D 4 bit. registers 13

Assembler Assembly assembler Machine Language 14

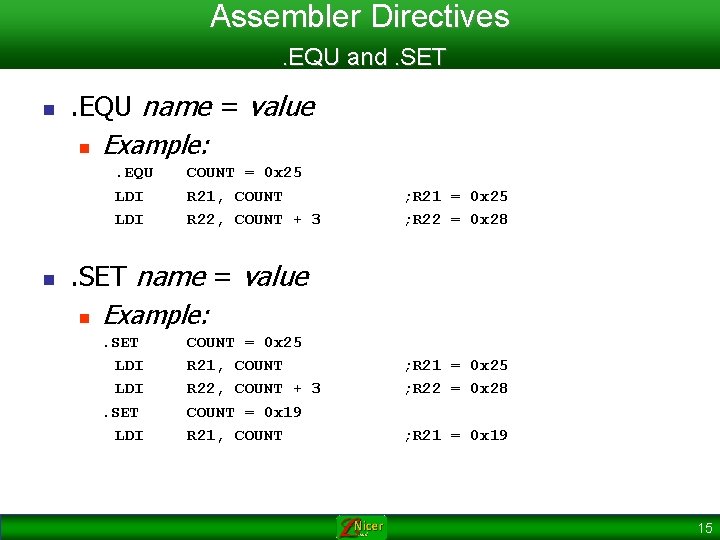

Assembler Directives. EQU and. SET n . EQU name = value n Example: . EQU LDI n COUNT = 0 x 25 R 21, COUNT R 22, COUNT + 3 ; R 21 = 0 x 25 ; R 22 = 0 x 28 . SET name = value n Example: . SET LDI COUNT = 0 x 25 R 21, COUNT R 22, COUNT + 3 COUNT = 0 x 19 R 21, COUNT ; R 21 = 0 x 25 ; R 22 = 0 x 28 ; R 21 = 0 x 19 15

Assembler Directives. ORG n . ORG address Program. asm. ORG 0 LDI R 16, 0 x 25. ORG 0 x 7 LDI R 17, 0 x 34 LDI R 18, 0 x 31 assembler 00 E 205 01 0000 02 0000 03 0000 04 0000 05 0000 06 0000 07 E 314 08 E 321 09 0000 0 A 0000 16

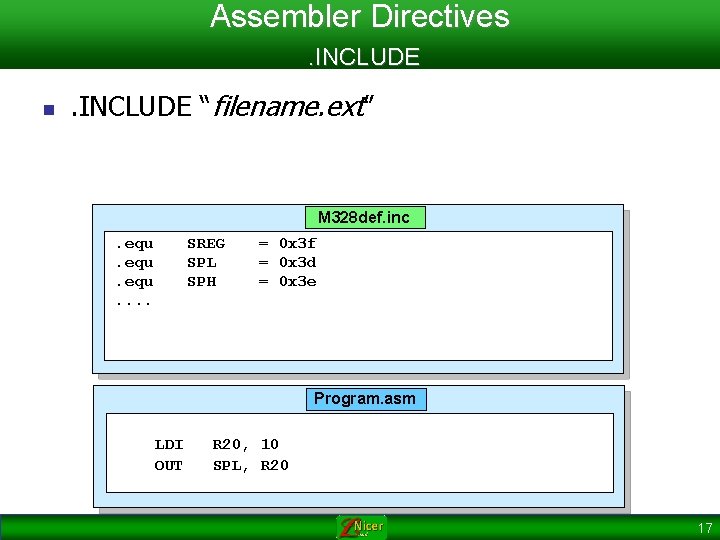

Assembler Directives. INCLUDE n . INCLUDE “filename. ext” M 328 def. inc. equ. . SREG SPL SPH = 0 x 3 f = 0 x 3 d = 0 x 3 e Program. asm LDI OUT R 20, 10 SPL, R 20 17

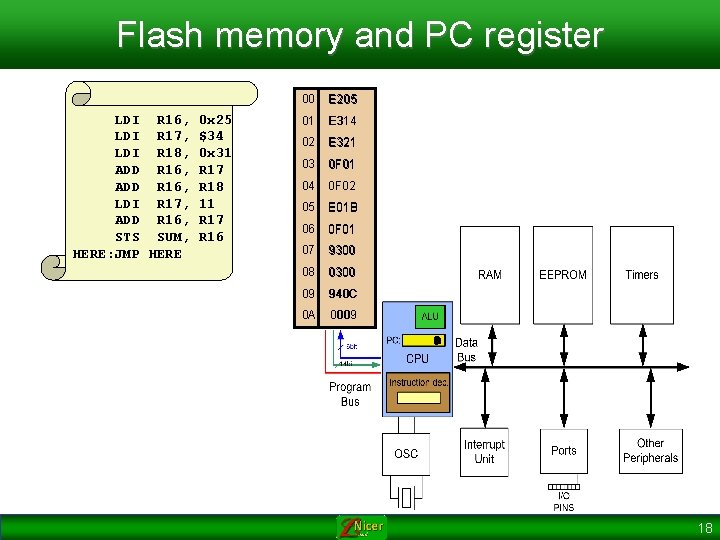

Flash memory and PC register LDI R 16, LDI R 17, LDI R 18, ADD R 16, LDI R 17, ADD R 16, STS SUM, HERE: JMP HERE 0 x 25 $34 0 x 31 R 17 R 18 11 R 17 R 16 00 E 205 01 E 314 02 E 321 03 0 F 01 04 0 F 02 0516 -bit E 01 B 06 0 F 01 07 9300 08 0300 09 940 C 0 A 0009 3 0 9 1 5 2 A 7 4 8 B 6 18

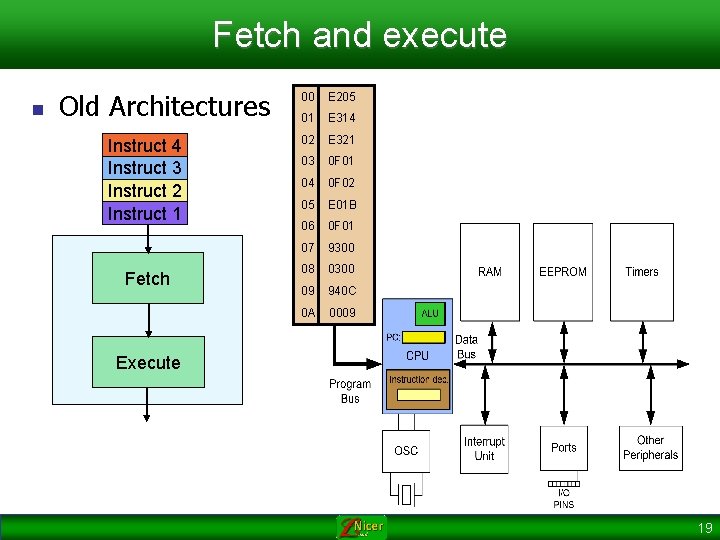

Fetch and execute n Old Architectures Instruct 4 Instruct 3 Instruct 2 Instruct 1 Fetch 00 E 205 01 E 314 02 E 321 03 0 F 01 04 0 F 02 0516 -bit E 01 B 06 0 F 01 07 9300 08 0300 09 940 C 0 A 0009 Execute 19

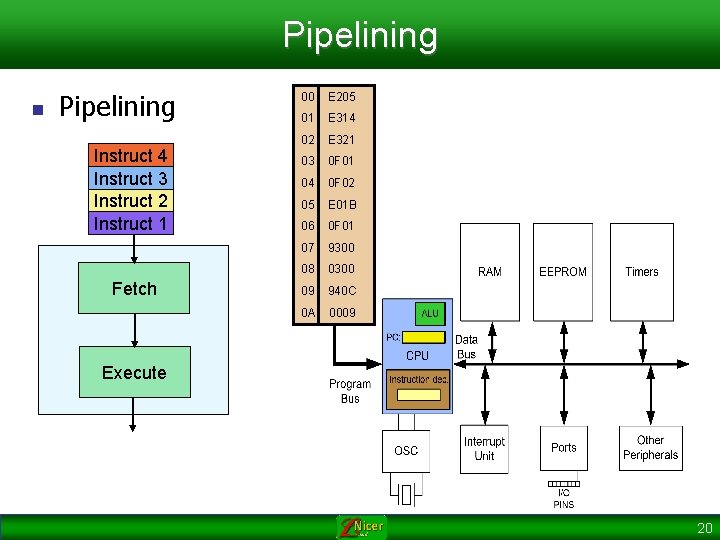

Pipelining n Pipelining Instruct 4 Instruct 3 Instruct 2 Instruct 1 Fetch 00 E 205 01 E 314 02 E 321 03 0 F 01 04 0 F 02 0516 -bit E 01 B 06 0 F 01 07 9300 08 0300 09 940 C 0 A 0009 Execute 20

How to speed up the CPU n Increase the clock frequency n n n More frequency More power consumption & more heat Limitations Change the architecture n n Pipelining RISC 21

Changing the architecture RISC vs. CISC n CISC (Complex Instruction Set Computer) n n Put as many instruction as you can into the CPU RISC (Reduced Instruction Set Computer) n Reduce the number of instructions, and use your facilities in a more proper way. 22

RISC architecture n Feature 1 n RISC processors have a fixed instruction size. It makes the task of instruction decoder easier. n n In AVR the instructions are 2 or 4 bytes. In CISC processors instructions have different lengths n E. g. in 8051 n n n CLR C ADD A, #20 H LJMP HERE ; a 1 -byte instruction ; a 2 -byte instruction ; a 3 -byte instruction 23

RISC architecture n Feature 2: reduce the number of instructions n n Pros: Reduces the number of used transistors Cons: n n Can make the assembly programming more difficult Can lead to using more memory 24

RISC architecture n Feature 3: limit the addressing mode n Advantage n n hardwiring Disadvantage n Can make the assembly programming more difficult 25

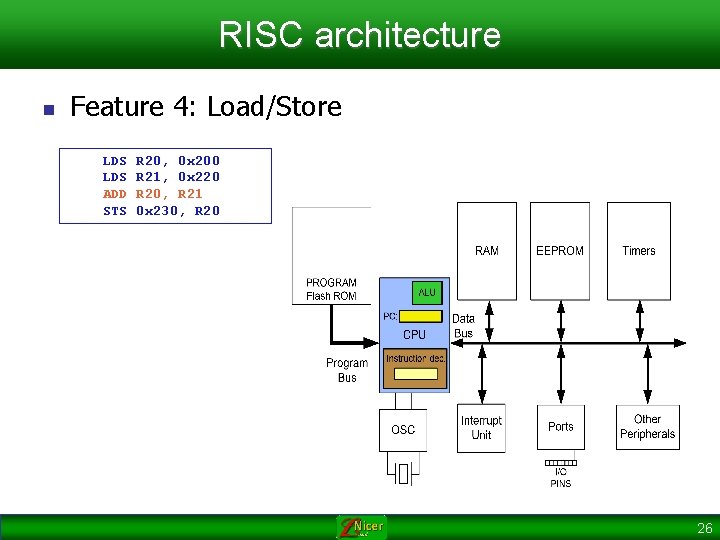

RISC architecture n Feature 4: Load/Store LDS ADD STS R 20, 0 x 200 R 21, 0 x 220 R 20, R 21 0 x 230, R 20 26

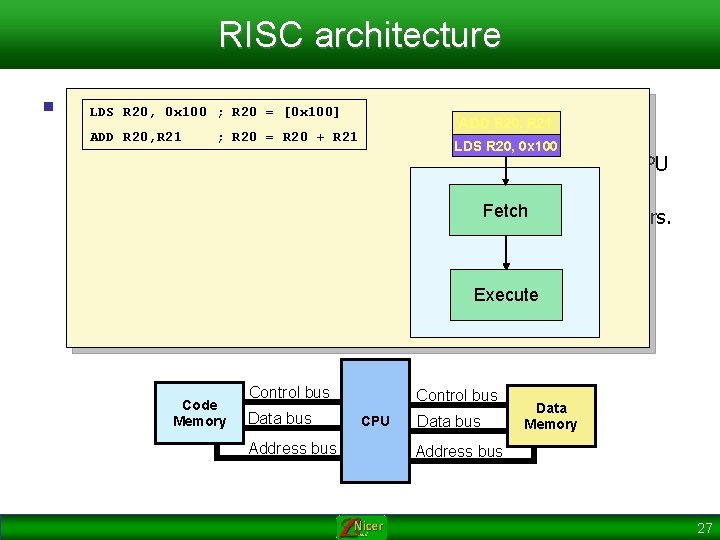

RISC architecture n Feature (Harvard separate buses for LDS R 20, 50 x 100 ; R 20 = architecture): [0 x 100] ADD R 20, R 21 ; R 20 = R 20 + R 21 opcodes and operands LDS R 20, 0 x 100 n n Advantage: opcodes and operands can go in and out of the CPU together. Disadvantage: leads to more cost in general. Fetch purpose computers. Execute Code Memory Control bus Data bus Address bus Control bus CPU Data bus Data Memory Address bus 27

RISC architecture n Feature 6: more than 95% of instructions are executed in 1 machine cycle 28

RISC architecture n Feature 7 n RISC processors have at least 32 registers. Decreases the need for stack and memory usages. n In AVR there are 32 general purpose registers (R 0 to R 31) 29

- Slides: 29