Introduction l Linus Svensson D 4 linsve7student luth

- Slides: 34

Introduction l Linus Svensson D 4, linsve-7@student. luth. se l Åke Östmark D 4, akeost-6@student. luth. se 1

Why we are here l l 2 Project called Design and Implementation of a 32 -bit FPU in VHDL Complete project presentation fpu. varulv. net

Today's topics l l l l l 3 Floating-Point Unit (FPU) Design of our FPU Multiplication, an example of an algorithm Normalisation and rounding Implementation in an HDL Testing of the implementation Final result Life after SMD 082 Questions

Floating-Point Unit (FPU) l l l l 4 A unit providing floating-point processing capabilities Konrad Zuse had a proposal for building a computer in Germany in 1939 First commercial machine with floating-point hardware was the IBM 704 in 1955 Professor W. Kahan -Twenty years ago anarchy threatened floating-point arithmetic. Forming of the IEEE floating-point committee in 1977 The first chip manufactured in complains with the IEEE standard 754 were the Intel 8087 Math Coprocessor The Intel 486 DX processor for the first time integrated the CPU and the FPU architectures on one chip

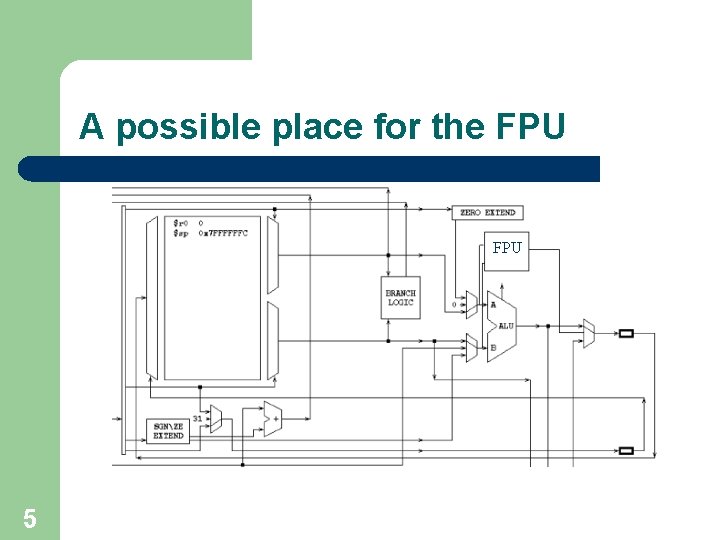

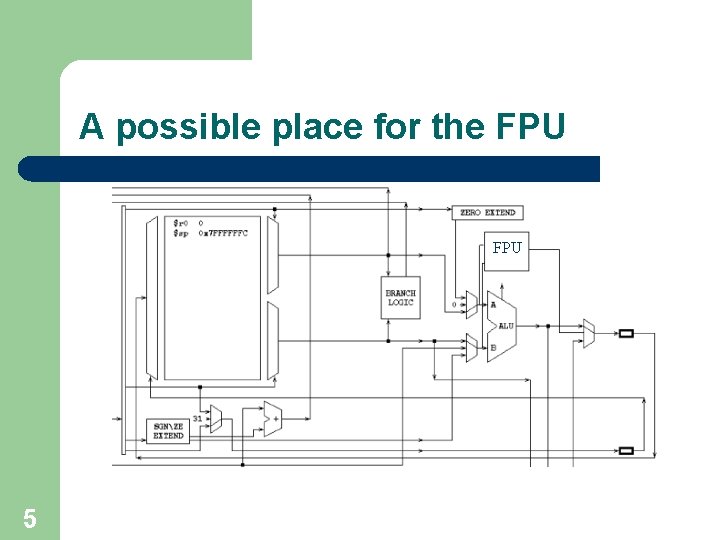

A possible place for the FPU 5

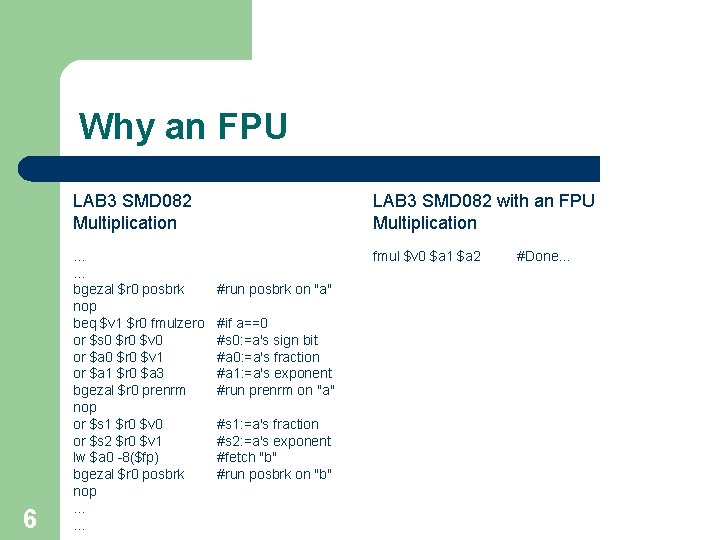

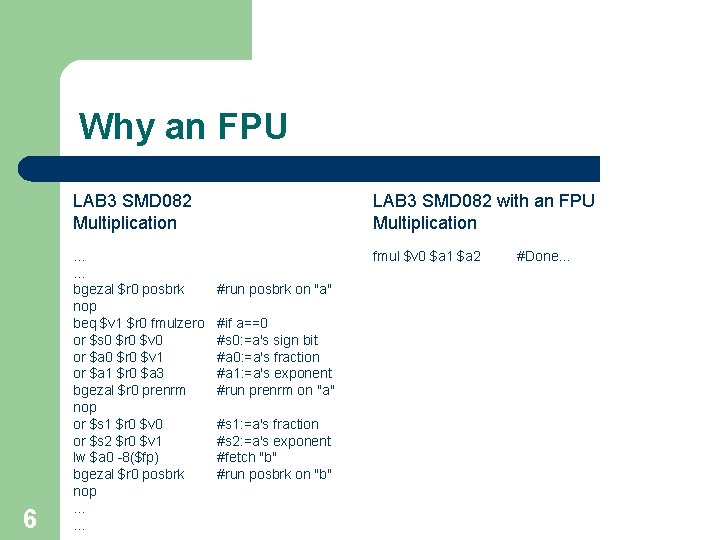

Why an FPU 6 LAB 3 SMD 082 Multiplication LAB 3 SMD 082 with an FPU Multiplication …. . . bgezal $r 0 posbrk nop beq $v 1 $r 0 fmulzero or $s 0 $r 0 $v 0 or $a 0 $r 0 $v 1 or $a 1 $r 0 $a 3 bgezal $r 0 prenrm nop or $s 1 $r 0 $v 0 or $s 2 $r 0 $v 1 lw $a 0 -8($fp) bgezal $r 0 posbrk nop …. . . fmul $v 0 $a 1 $a 2 #run posbrk on "a" #if a==0 #s 0: =a's sign bit #a 0: =a's fraction #a 1: =a's exponent #run prenrm on "a" #s 1: =a's fraction #s 2: =a's exponent #fetch "b" #run posbrk on "b" #Done. . .

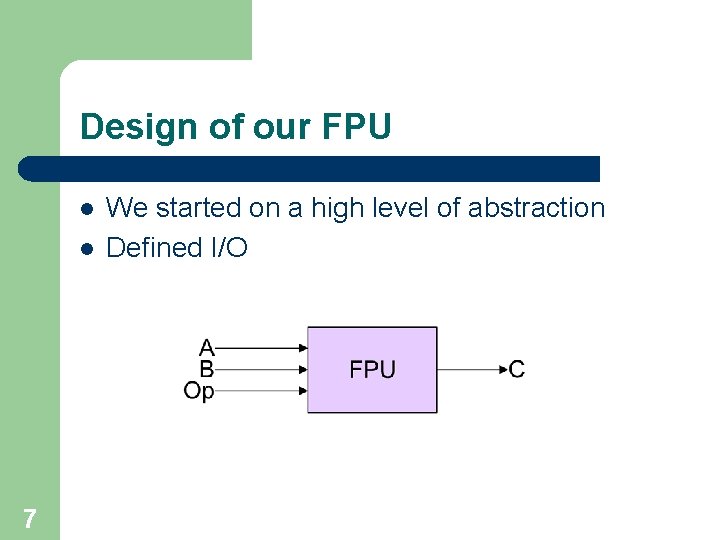

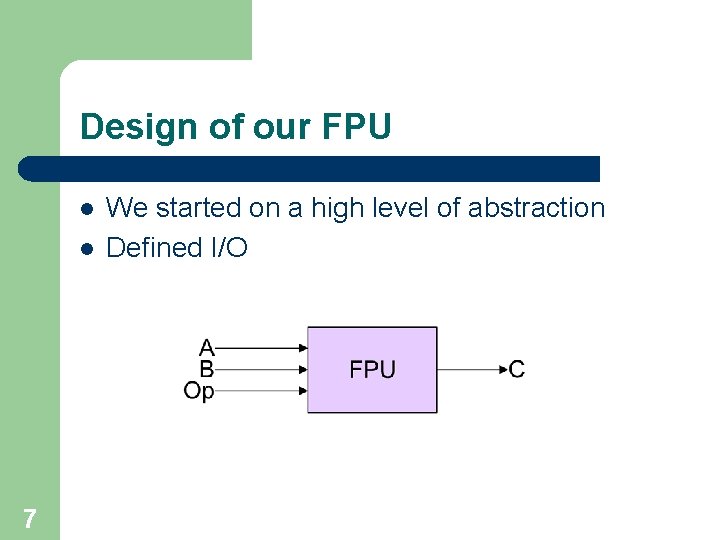

Design of our FPU l l 7 We started on a high level of abstraction Defined I/O

Design of our FPU l 8 We divided the design into smaller blocks …

Design of our FPU l 9 …until we had a low level of abstraction

Design of our FPU l l l 10 Picked an existing algorithm, or modified an existing algorithm, or designed a new algorithm

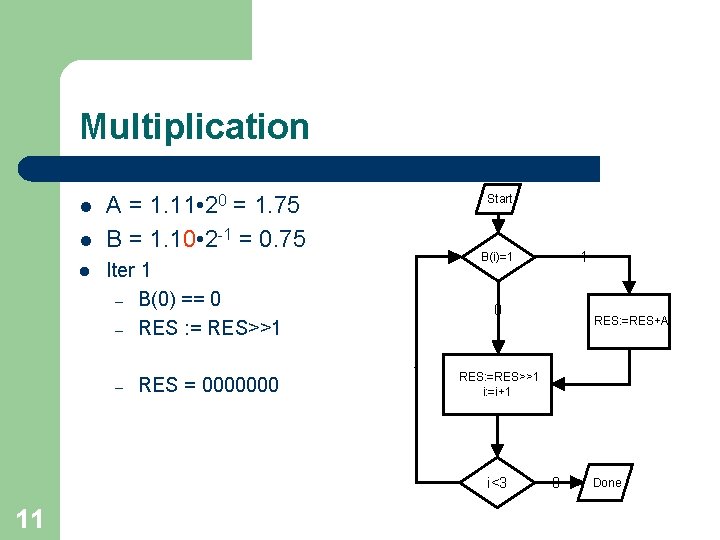

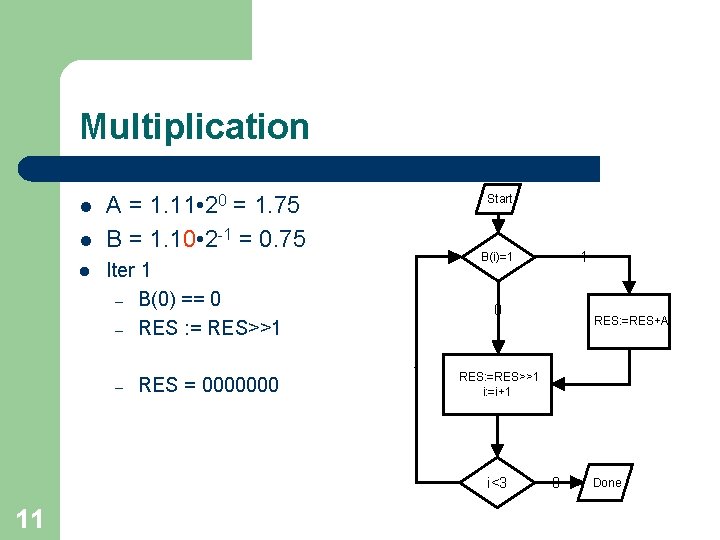

Multiplication l l l A = 1. 11 • 20 = 1. 75 B = 1. 10 • 2 -1 = 0. 75 Start Iter 1 – B(0) == 0 – RES : = RES>>1 – RES = 0000000 0 1 RES: =RES+A RES: =RES>>1 i: =i+1 i<3 11 1 B(i)=1 0 Done

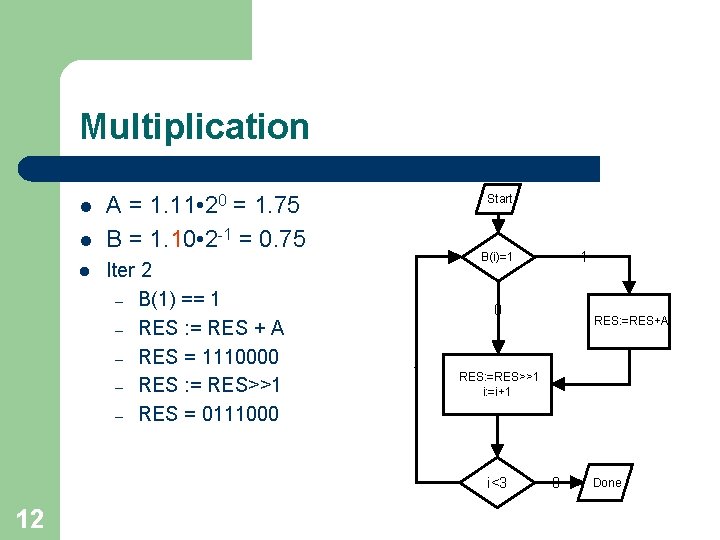

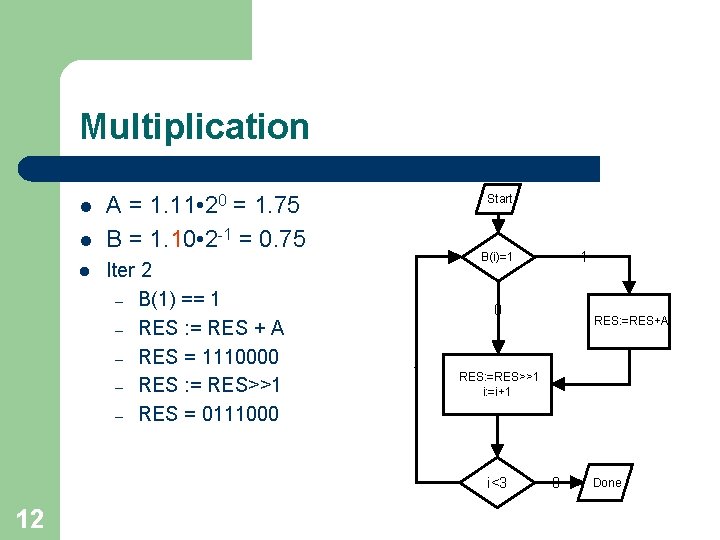

Multiplication l l l A = 1. 11 • 20 = 1. 75 B = 1. 10 • 2 -1 = 0. 75 Iter 2 – B(1) == 1 – RES : = RES + A – RES = 1110000 – RES : = RES>>1 – RES = 0111000 Start 0 1 RES: =RES+A RES: =RES>>1 i: =i+1 i<3 12 1 B(i)=1 0 Done

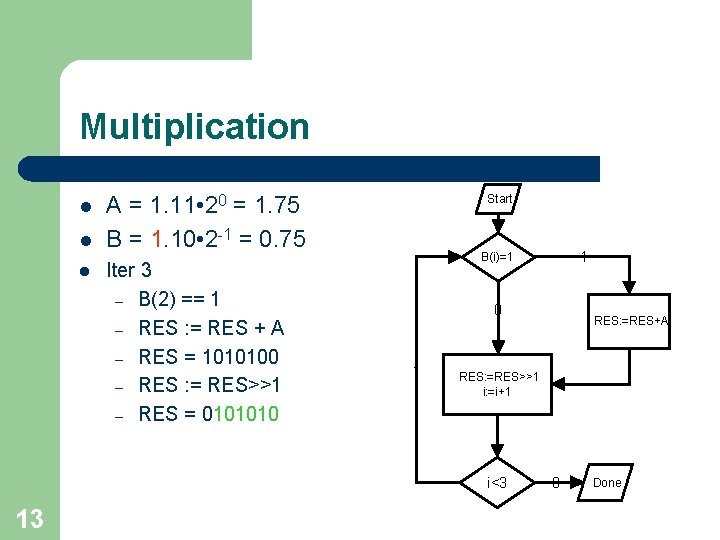

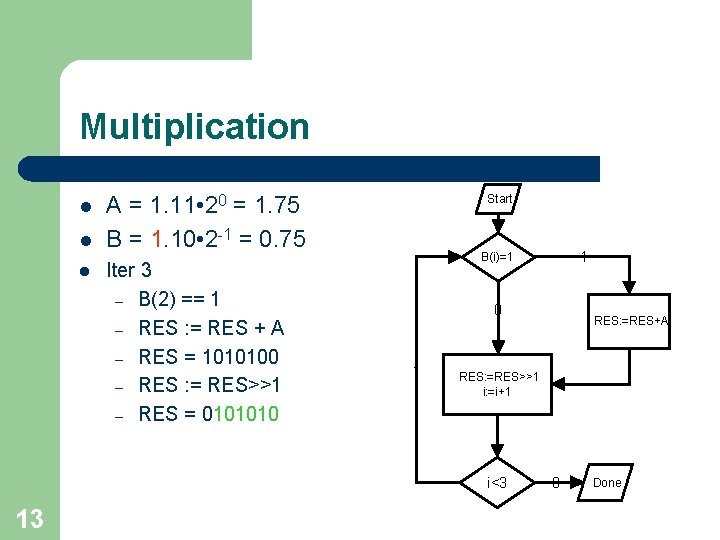

Multiplication l l l A = 1. 11 • 20 = 1. 75 B = 1. 10 • 2 -1 = 0. 75 Iter 3 – B(2) == 1 – RES : = RES + A – RES = 1010100 – RES : = RES>>1 – RES = 0101010 Start 0 1 RES: =RES+A RES: =RES>>1 i: =i+1 i<3 13 1 B(i)=1 0 Done

Multiplication l l l 14 sign. A xor sign. B = 0 exp. A + exp. B = -1 man = 10. 1010

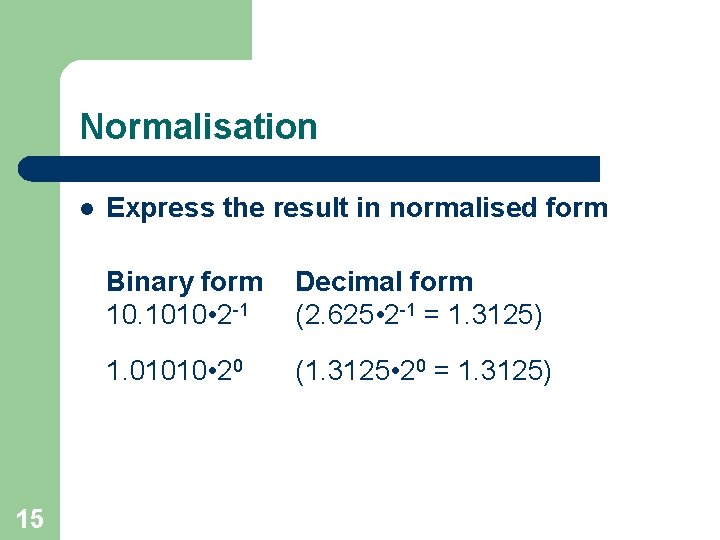

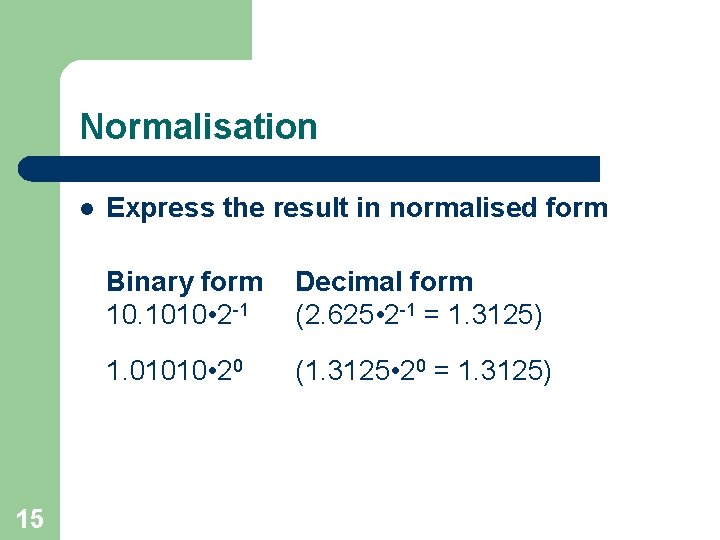

Normalisation l 15 Express the result in normalised form Binary form 10. 1010 • 2 -1 Decimal form (2. 625 • 2 -1 = 1. 3125) 1. 01010 • 20 (1. 3125 • 20 = 1. 3125)

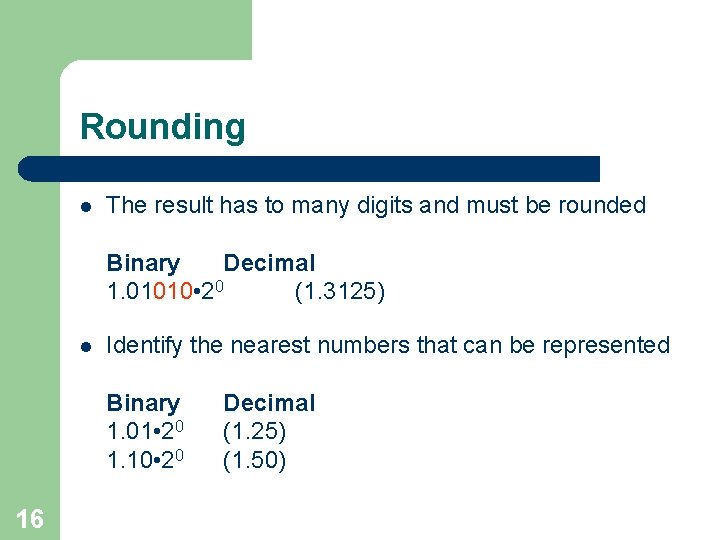

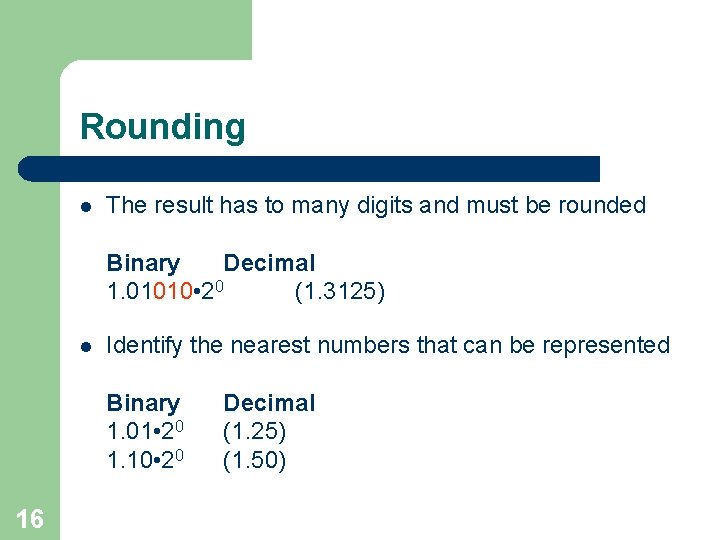

Rounding l The result has to many digits and must be rounded Binary Decimal 1. 01010 • 20 (1. 3125) l Identify the nearest numbers that can be represented Binary 1. 01 • 20 1. 10 • 20 16 Decimal (1. 25) (1. 50)

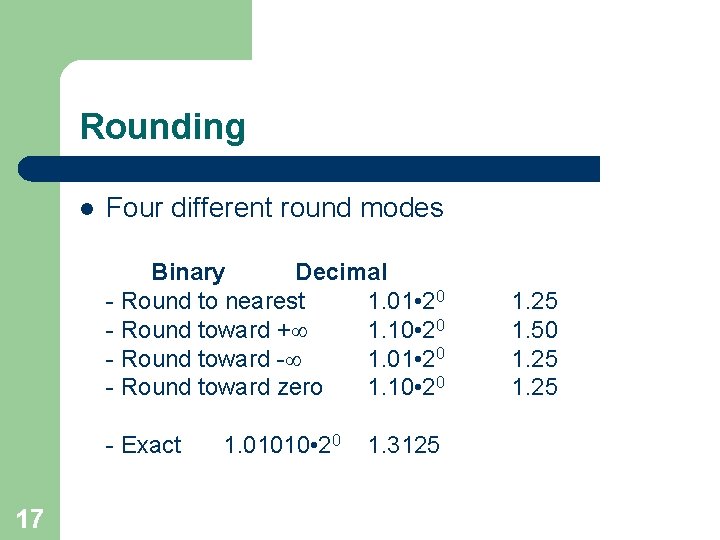

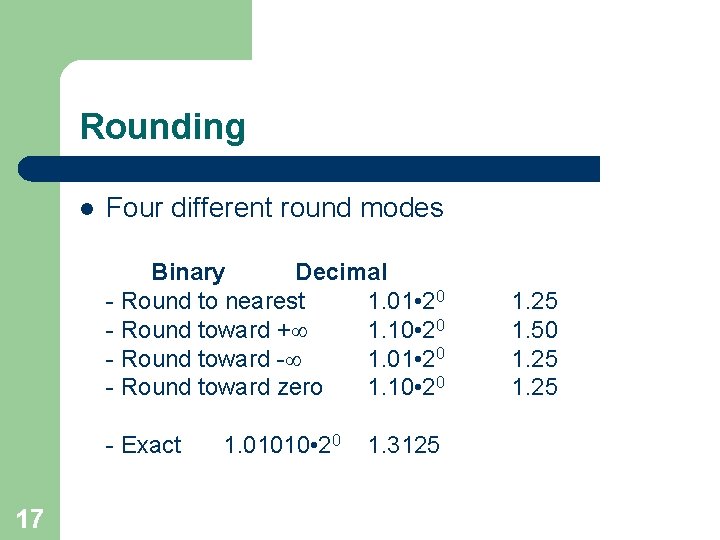

Rounding l Four different round modes Binary Decimal - Round to nearest 1. 01 • 20 - Round toward + 1. 10 • 20 - Round toward - 1. 01 • 20 - Round toward zero 1. 10 • 20 - Exact 17 1. 01010 • 20 1. 3125 1. 50 1. 25

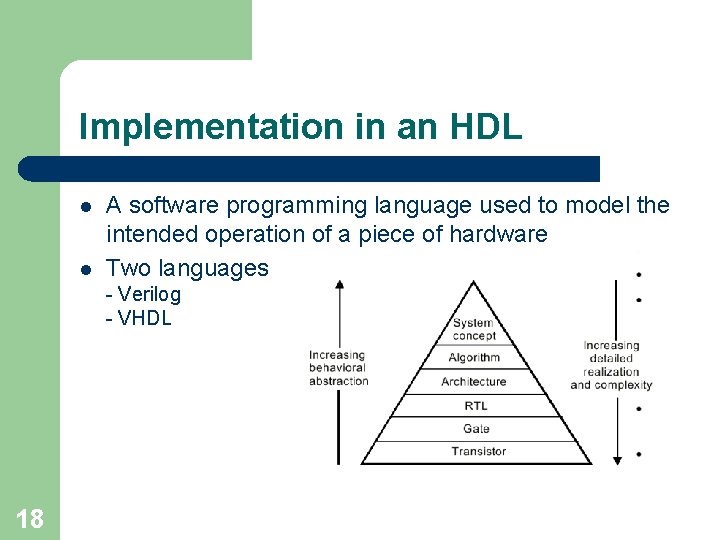

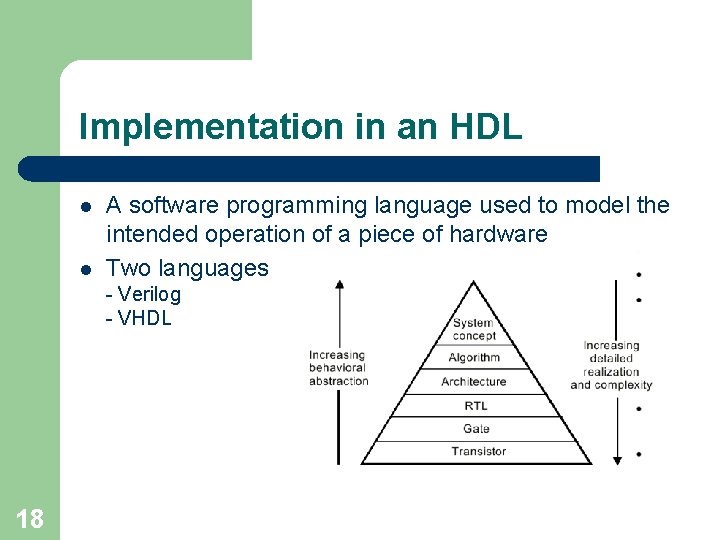

Implementation in an HDL l l A software programming language used to model the intended operation of a piece of hardware Two languages - Verilog - VHDL 18

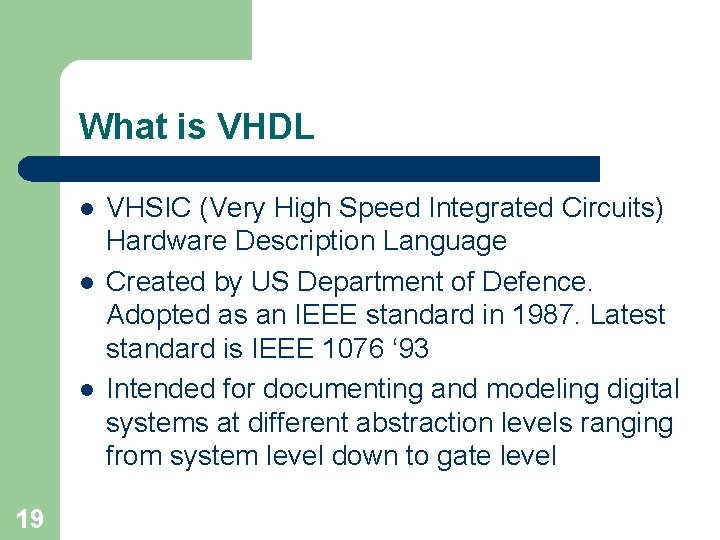

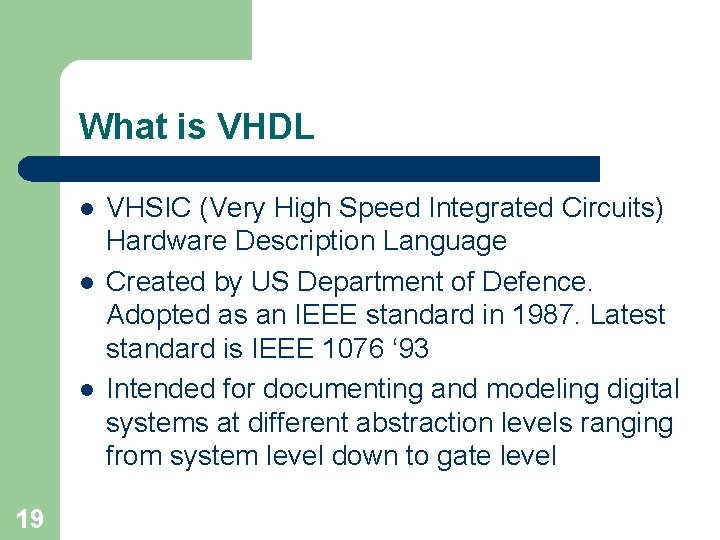

What is VHDL l l l 19 VHSIC (Very High Speed Integrated Circuits) Hardware Description Language Created by US Department of Defence. Adopted as an IEEE standard in 1987. Latest standard is IEEE 1076 ‘ 93 Intended for documenting and modeling digital systems at different abstraction levels ranging from system level down to gate level

Main language concepts l Concurrency – l Structure, hierarchy – l VHDL allows to structure a design in a hierarchical manner Sequential statements – 20 VHDL can describe activities that are happening in parallel VHDL also allows sequential execution of statements. Just like any other programming language

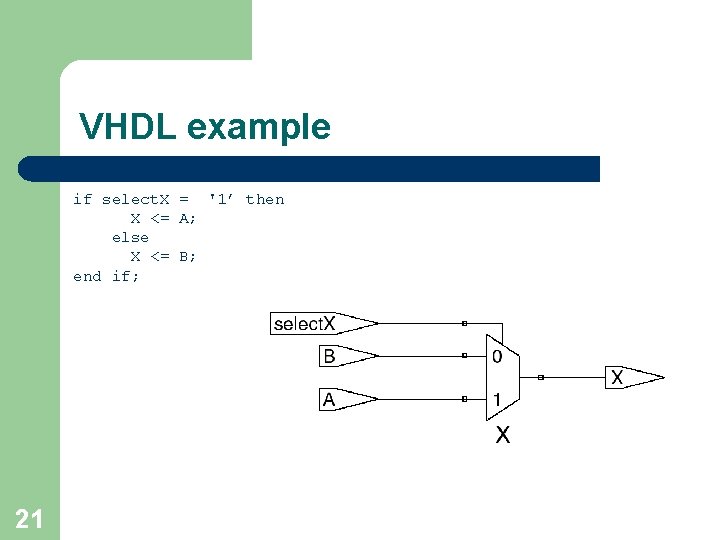

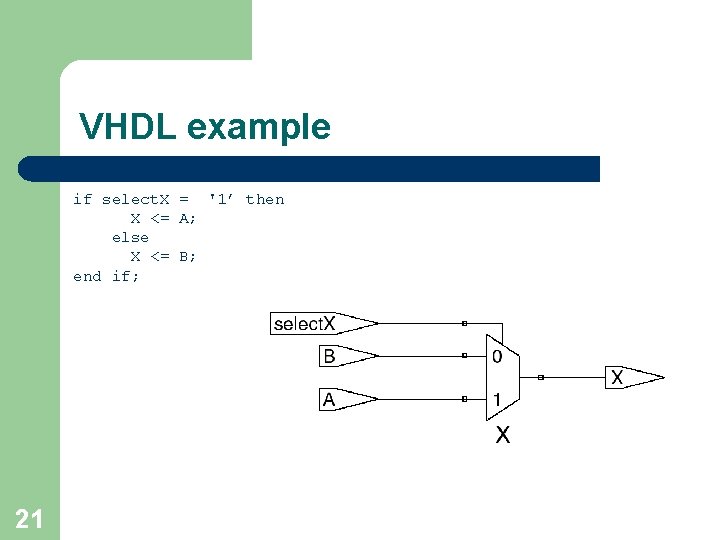

VHDL example if select. X = '1’ then X <= A; else X <= B; end if; 21

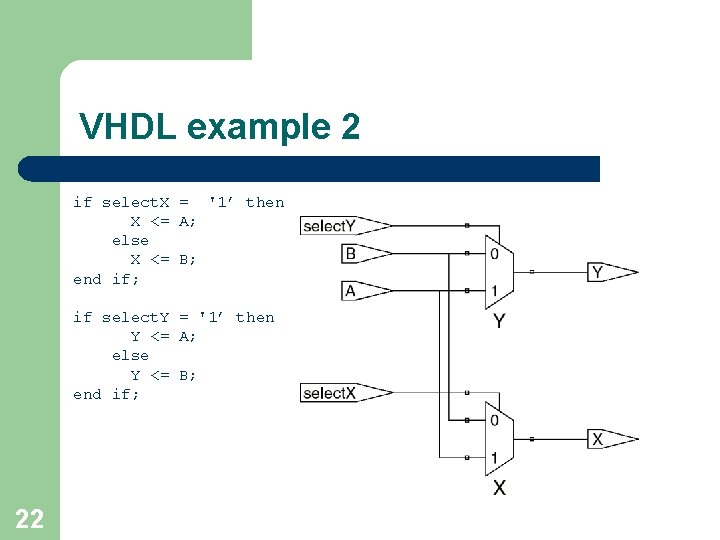

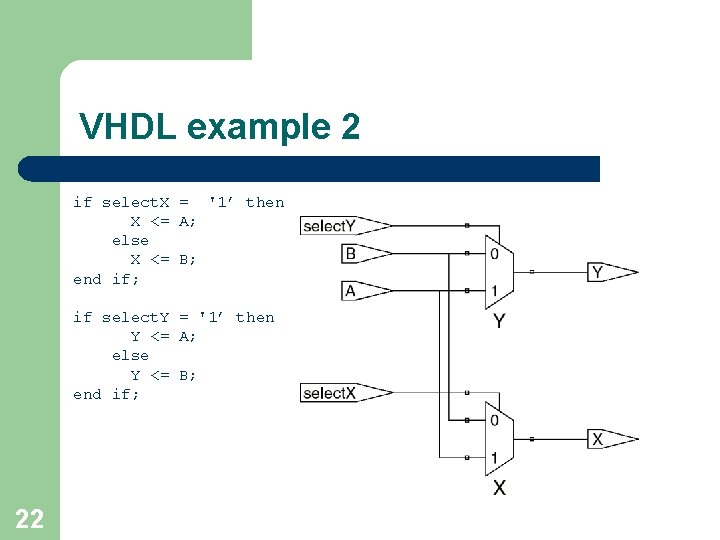

VHDL example 2 if select. X = '1’ then X <= A; else X <= B; end if; if select. Y = '1’ then Y <= A; else Y <= B; end if; 22

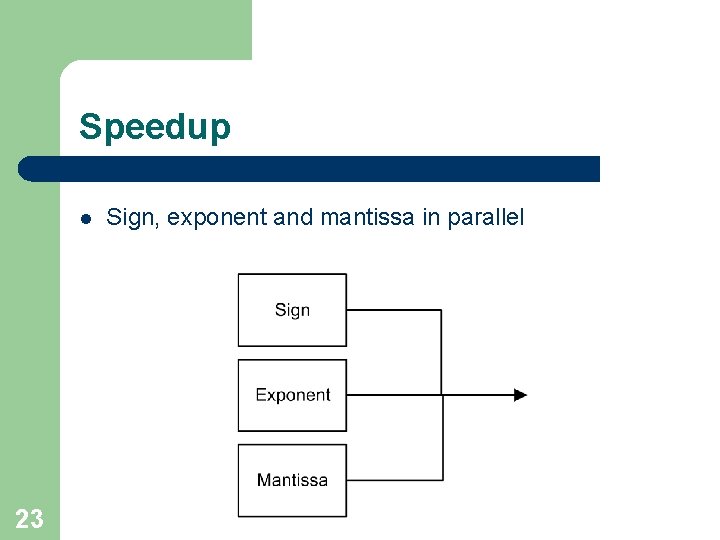

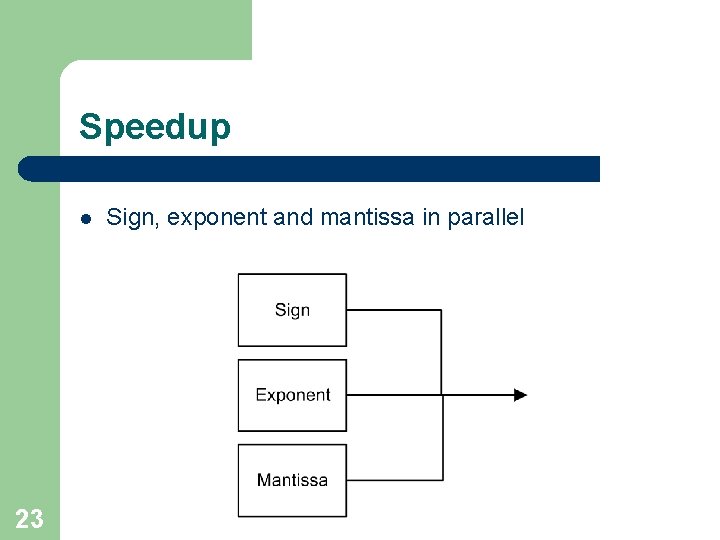

Speedup l 23 Sign, exponent and mantissa in parallel

Testing - Verification l Verification – l l 24 Are we building the product right? Bottom-up integration Testing every module on its own before integrating it into higher level modules

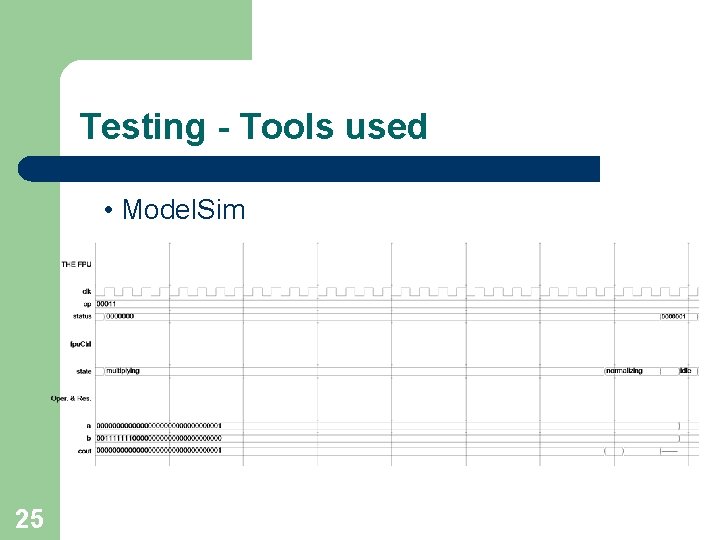

Testing - Tools used • Model. Sim 25

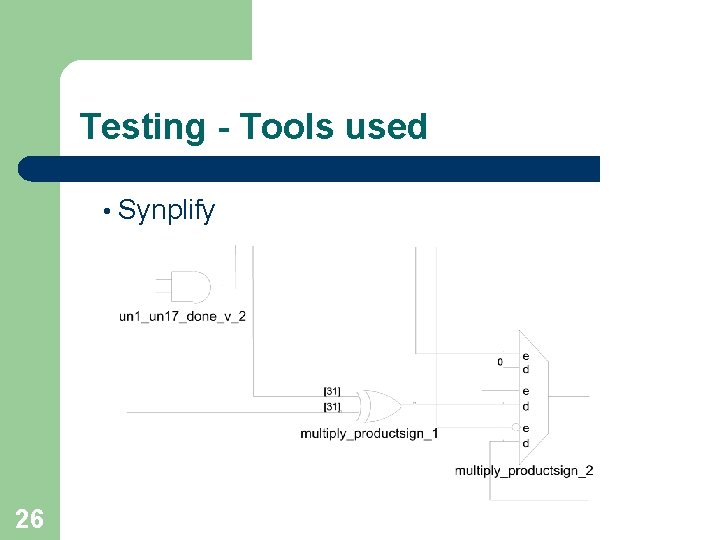

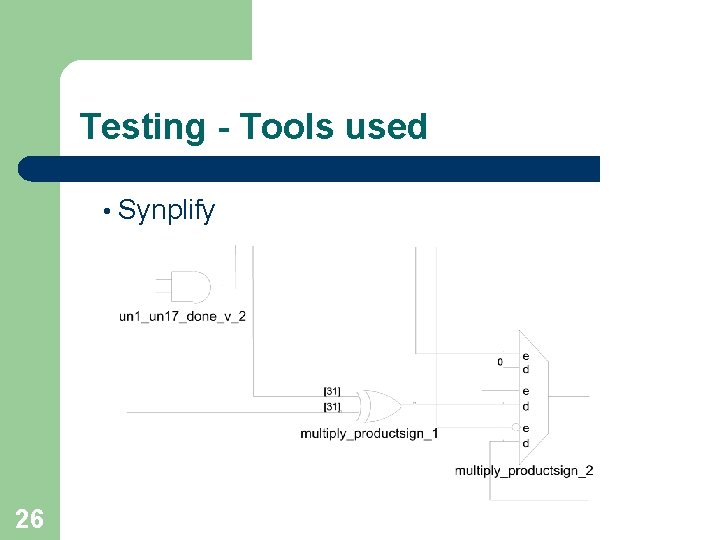

Testing - Tools used • Synplify 26

Testing - Example l Avoid introducing new errors in verified code A : = operand_A B : = operand_B C : = expected_result if result is equal to C test is ok else raise flag to indicate fault in test 27

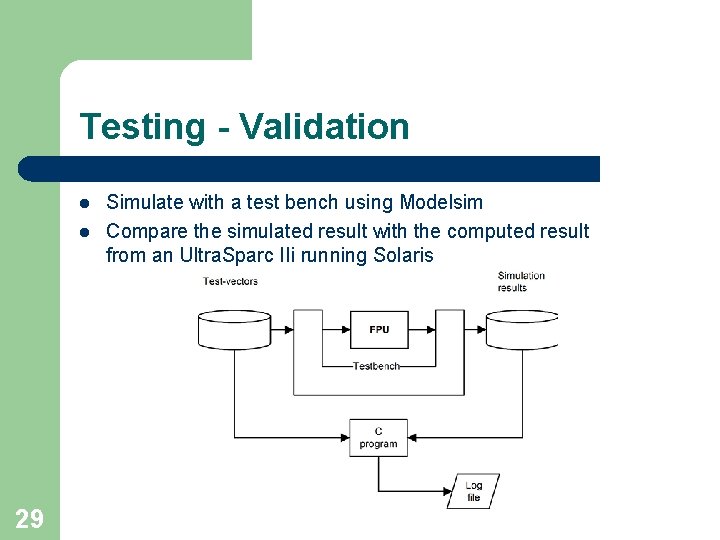

Testing - Validation l Validation – l 28 Are we building the right product? What if we have misinterpreted the IEEE standard 754?

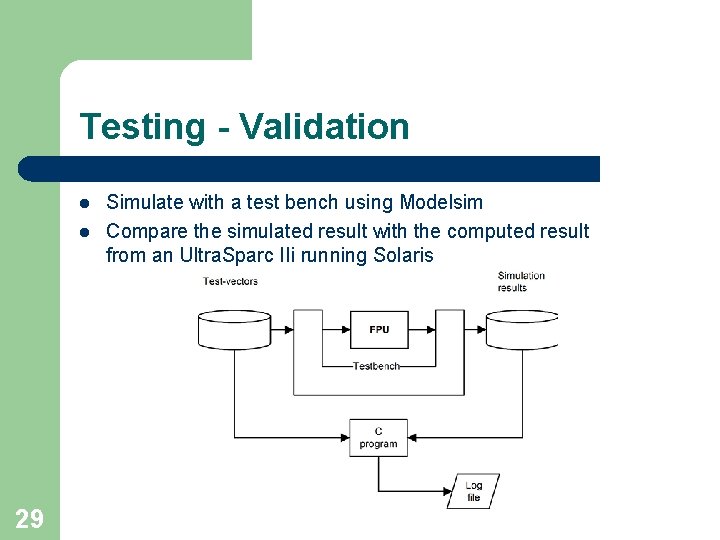

Testing - Validation l l 29 Simulate with a test bench using Modelsim Compare the simulated result with the computed result from an Ultra. Sparc IIi running Solaris

Final result l Operations - addition - subtraction - division - multiplication - square root 30 - ceiling - floor - fraction - float 2 integer - integer 2 float

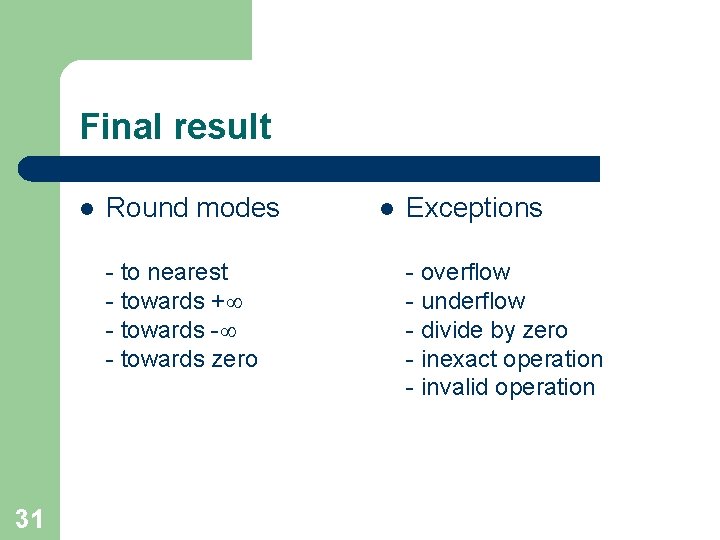

Final result l Round modes - to nearest - towards + - towards - - towards zero 31 l Exceptions - overflow - underflow - divide by zero - inexact operation - invalid operation

Final result 32

Life after SMD 082 l Computer Architecture / Datorarkitektur SMD 077, 4 p, LP 2 l Computation Structures / Beräkningsstrukturer SMD 098, 4 p, LP 2 l Project in Digital Synthesis / Projekt i digital syntes SMD 106, 8 p, LP 3 -4 l Computer Science, Advanced course / Datateknik, fördjupningskurs SMD 061 -3, 2 -4 p, LP 1 -4 33

Questions 34