Introduction CEG 4131 Computer Architecture III Miodrag Bolic

Introduction CEG 4131 Computer Architecture III Miodrag Bolic 1

Four levels of computer description Gate level – Specify operations at the individual bit level – Gates are primitive elements – Very cumbersome to do manually (logic minimization, etc. ) Register level – Specify internal operation of processor-level components at the word level – Primitives: » Registers » Counters » Memories » ALUs » Clocks » Combinational logic 2

Four levels of computer description Processor level – Architectural Features specified » Interfaces » Instruction sets » Data Representation – More detailed individual component specification Global system structure – Overall system structure is defined – Major components identified » Processors » Control modules » Memory modules » Interconnection structure – Mostly a static description -- “black box” approach 3

![Basic parallel techniques [1] • Pipelining (time) – a number of functional units are Basic parallel techniques [1] • Pipelining (time) – a number of functional units are](http://slidetodoc.com/presentation_image_h/cbd0bfb5ffce1050a9c9aac747b7735b/image-4.jpg)

Basic parallel techniques [1] • Pipelining (time) – a number of functional units are employed in sequence to perform a single computation – a number of steps for each computation • Replication (space) – a number of functional units perform computation simultaneously • more processors • more memory • more I/O • Replication at the following levels: – – Processor (multiple functional units) Chip (multiple processors and/or hardware blocks) Board (multiple processors and/or hardware systems) Multiple computers 4

Course Content - Interconnection Networks • Topologies of static networks – – – fully connected, rings, meshes, torii, hypercubes, k-ary n-cubes • Dynamic networks – Buses – Multistage intercon. networks – Crossbar switch networks 5

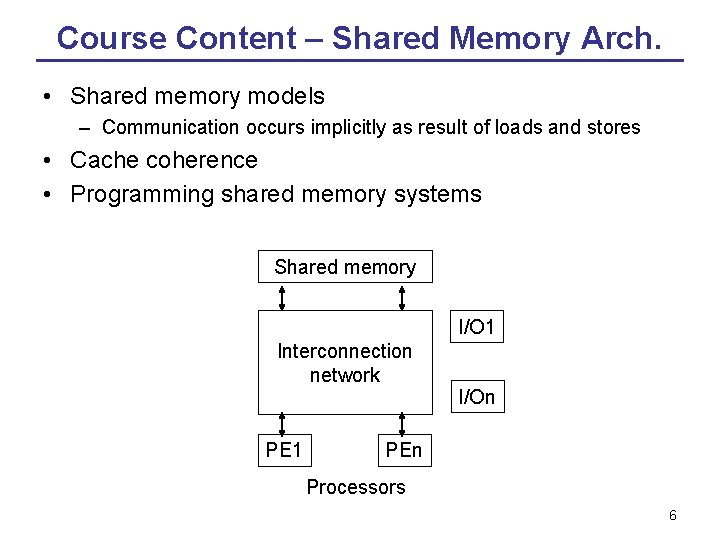

Course Content – Shared Memory Arch. • Shared memory models – Communication occurs implicitly as result of loads and stores • Cache coherence • Programming shared memory systems Shared memory I/O 1 Interconnection network PE 1 I/On PEn Processors 6

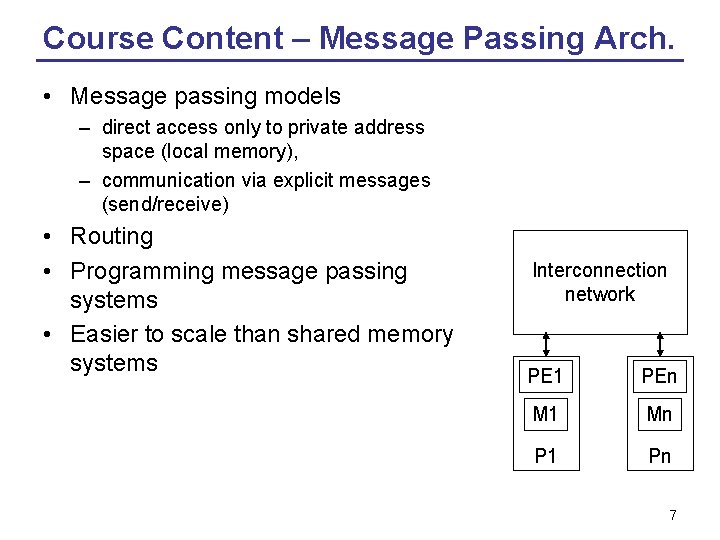

Course Content – Message Passing Arch. • Message passing models – direct access only to private address space (local memory), – communication via explicit messages (send/receive) • Routing • Programming message passing systems • Easier to scale than shared memory systems Interconnection network PE 1 PEn M 1 Mn P 1 Pn 7

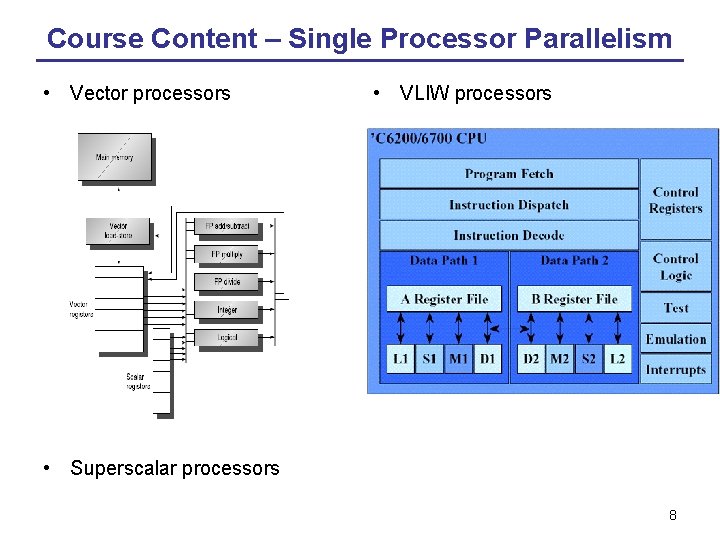

Course Content – Single Processor Parallelism • Vector processors • VLIW processors • Superscalar processors 8

What will you learn from Labs? • New approaches to design from the system level perspective – System-on-chip architectures – Design using IP (Intellectual Property) cores – Configurable instruction set architectures • Altera tools – SOPC builder – NIOS IDE 9

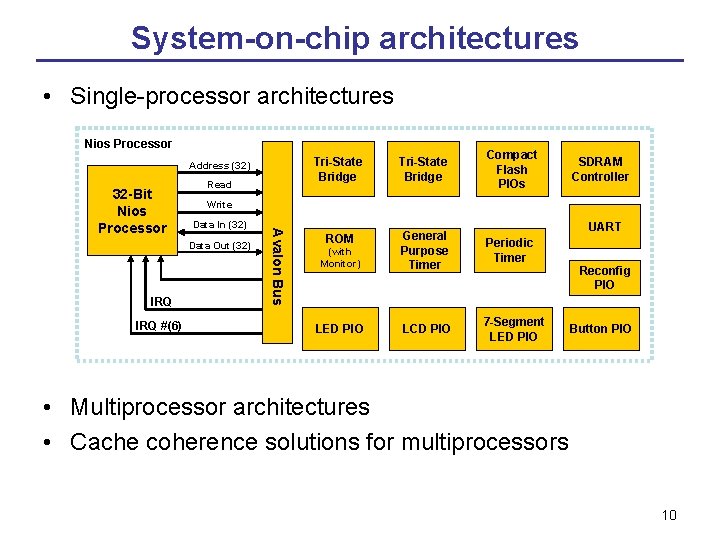

System-on-chip architectures • Single-processor architectures Nios Processor Address (32) Read Data In (32) Data Out (32) IRQ #(6) Tri-State Bridge ROM (with Monitor) General Purpose Timer Periodic Timer LED PIO LCD PIO 7 -Segment LED PIO SDRAM Controller Write Avalon Bus 32 -Bit Nios Processor Compact Flash PIOs Tri-State Bridge UART Reconfig PIO Button PIO • Multiprocessor architectures • Cache coherence solutions for multiprocessors 10

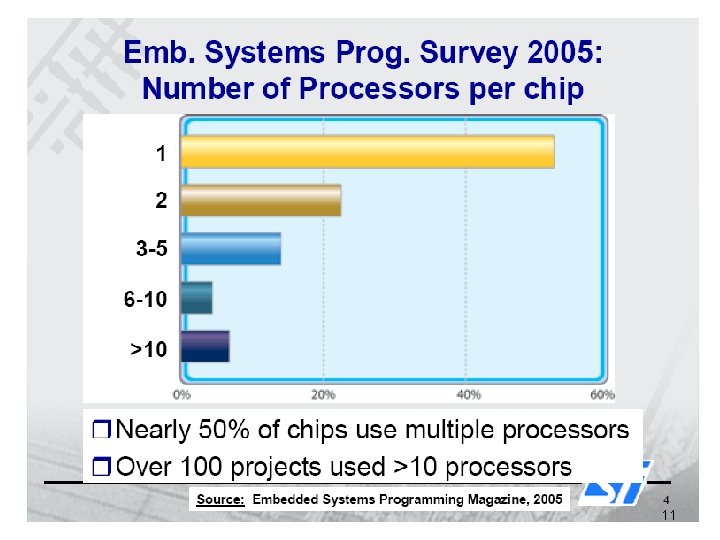

11

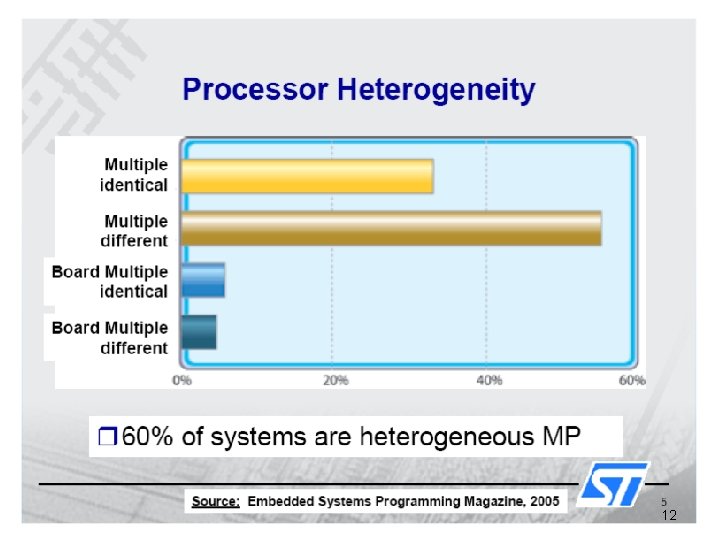

12

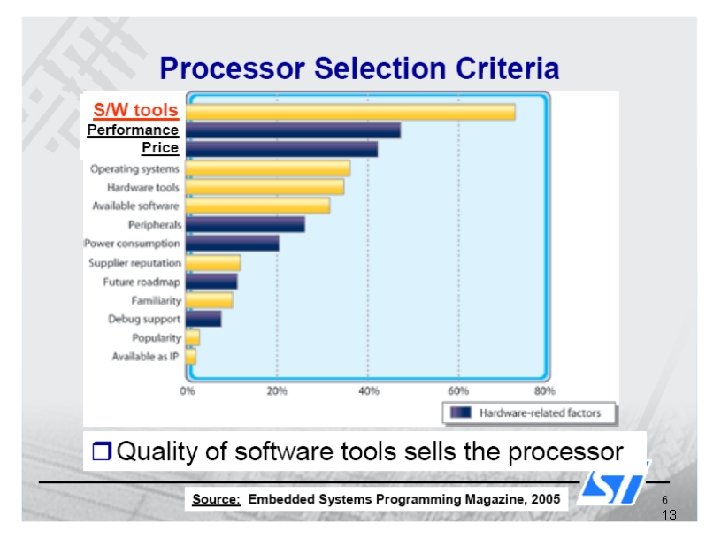

13

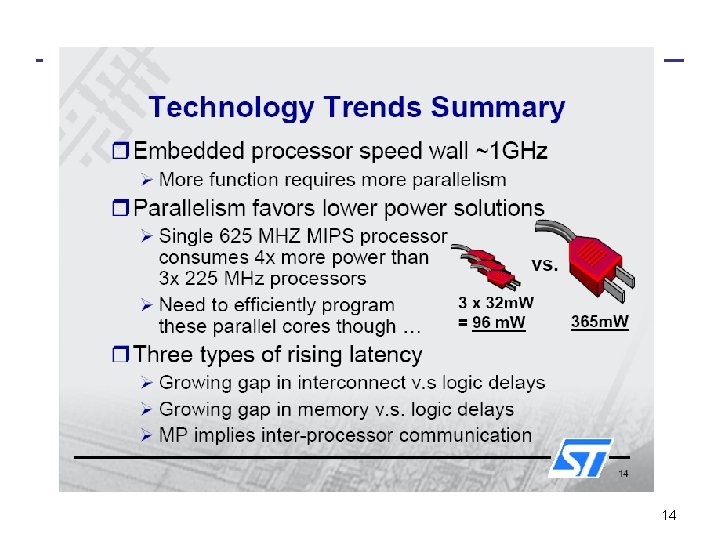

14

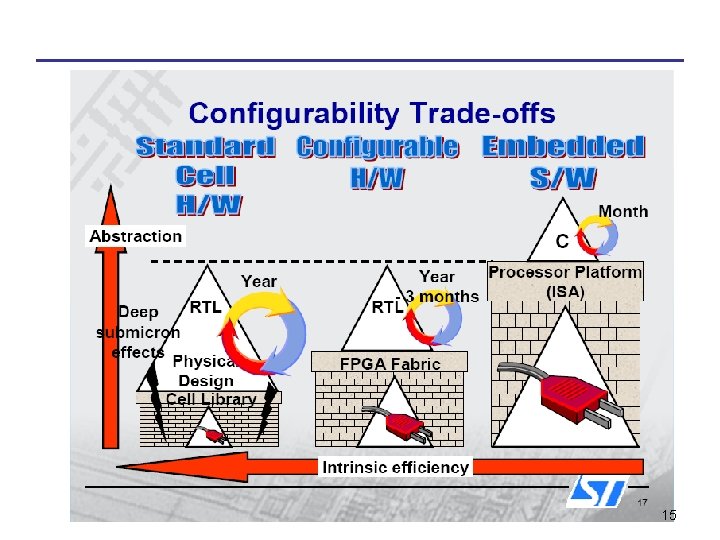

15

References 1. Desco Sima, Terence Fountain and Peter Kascuk, Advanced Computer Architectures – A Design Space Approach, Pearson, 1997. 16

- Slides: 16