Introducing HardwareSoftware Codesign in an Interdisciplinary Curriculum William

- Slides: 18

Introducing Hardware/Software Codesign in an Interdisciplinary Curriculum William B. Gardner & Micaela Serra VLSI Design & Test Group Dept. of Computer Science University of Victoria, BC 25/JUN/98 MR&DCAN '98 1

Computer, June 1998 • “In Pursuit of Hardware-Software Codesign, ” pp. 12 -14 • (blowup of page goes here) 25/JUN/98 MR&DCAN '98 2

Outline of Talk • Background for Course – who / why / what • Codesign snapshot • Course syllabus – tools / projects / response • Future directions 25/JUN/98 MR&DCAN '98 3

Our Research Group • VLSI Design & Test @ Comp. Sci. – Fault Tolerant Systems – Testing: DFT, BIST, Cellular Automata – CAD algorithms: BDDs, FPGA mapping – Multiple Valued Logic Regular course “Topics” courses âCodesign for embedded systems • configware, heterogeneous simulation, interface synthesis 25/JUN/98 MR&DCAN '98 4

Our Educational Concerns • Are our undergrads ready for a systems world? • Comp. Sci. B. Sc. — “Where’s the chips? ” – Digital Logic course (now with FPGA) – Design & Analysis of Real-Time Systems • mobile robots; software for microcontroller – ? ? ? 25/JUN/98 MR&DCAN '98 5

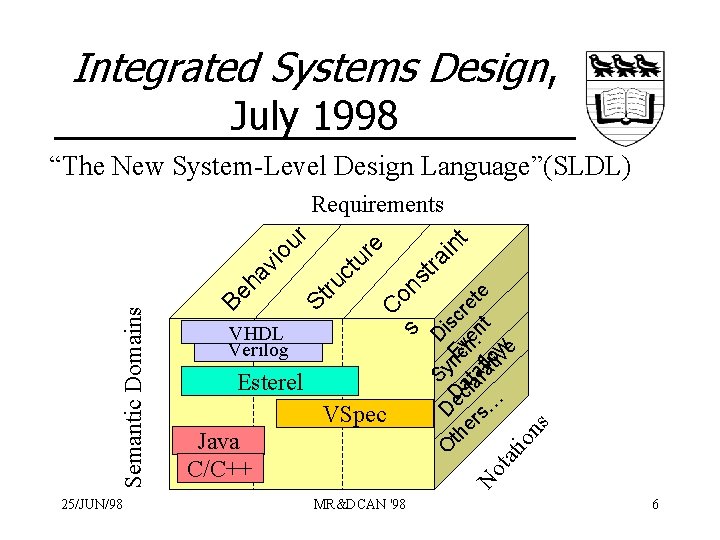

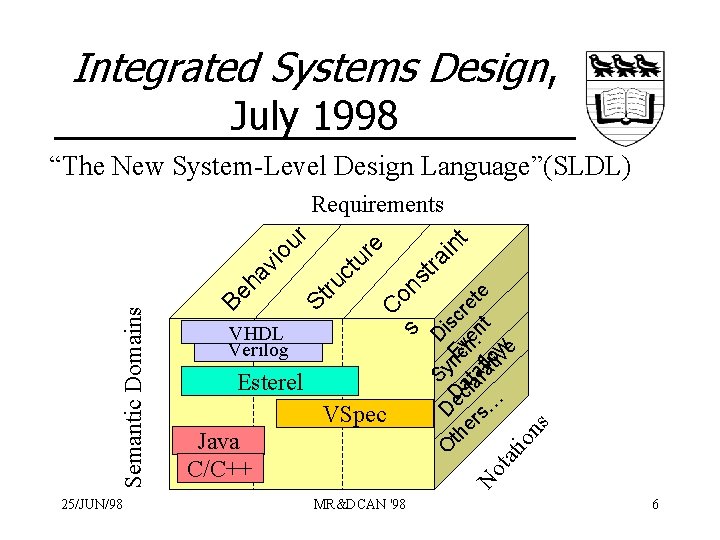

Integrated Systems Design, July 1998 “The New System-Level Design Language”(SLDL) 25/JUN/98 in t e VSpec No O Java C/C++ ns s Esterel tat io on C VHDL Verilog D D Syn. E Dis th ec a c v cr er lata h. e et s… raflo nt e tivw e st ra ur ru St Be Semantic Domains ha ct vi ou r Requirements MR&DCAN '98 6

Our Objectives • Introduce students to world of embedded systems {VLSI / FPGA + µP / DSP} • Introduce our research into teaching • Use “codesign” as theme • Demystify the technology – “comfort level” “empower” 25/JUN/98 MR&DCAN '98 7

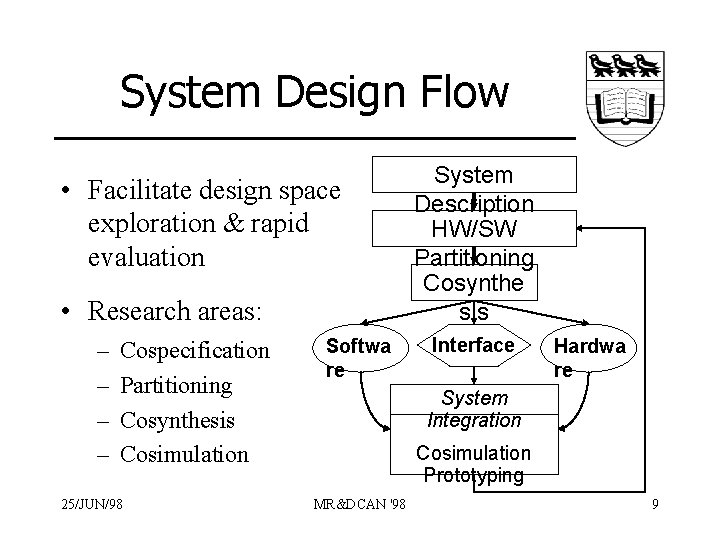

Snapshot of Codesign ê “Utopian” view • Origin in HW synthesis community 25/JUN/98 MR&DCAN '98 8

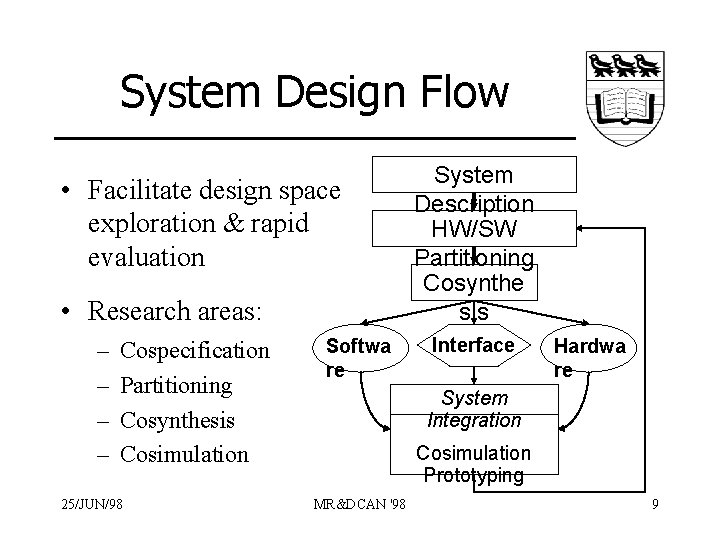

System Design Flow • Facilitate design space exploration & rapid evaluation • Research areas: – – Cospecification Partitioning Cosynthesis Cosimulation 25/JUN/98 Softwa re System Description HW/SW Partitioning Cosynthe sis Interface Hardwa re System Integration Cosimulation Prototyping MR&DCAN '98 9

The Course • CSc 485 a/556 “VLSI Design, CAD and Hardware/Software Codesign” – 4 th year elective, grad-level course • Main texts: – Specification & Design of Embedded Systems, Gajski et al. , PTR Prentice Hall, 1994. – Hardware/Software Co-Design, De Micheli & Sami, eds. , Kluwer, 1996. 25/JUN/98 MR&DCAN '98 10

Syllabus • 13 week course Intro to VLSI fab & design, FPGAs, VHDL & CAD tools Algorithms & unified methods, partitioning & cosimulation 25/JUN/98 Overview & methodologies MR&DCAN '98 11

Codesign Tools • Academic tools: hands-on assignments – Ptolemy (U. C. Berkeley) • build calculator using Synchronous Dataflow – Spec. Syn / Spec. Charts (U. C. Irvine) • design automotive controller (oil pressure, etc. ) 25/JUN/98 MR&DCAN '98 12

Other Tools • Commercial CAD tools: demos • Mentor SDS, • Synopsys VHDL/FPGA Compilers • Xilinx XACT – CMC Rapid-Prototyping Workshop case study • Magic: hands-on • exposure to CMOS layout 25/JUN/98 MR&DCAN '98 13

The Response • Enrolment (2 terms, Fall ‘ 97 & Winter ‘ 98) – 30 students – 28 CSc, 2 ECE – 23 undergrads, 7 grads • Projects, choice of: 1. Literature survey & presentation 2. Original design project 25/JUN/98 MR&DCAN '98 14

Survey Projects • Most with impressive web pages: – MEMS – Chip fabrication – Effects of radiation on VLSI 25/JUN/98 MR&DCAN '98 15

Original Design Projects • Palmtop systems – “Golf Guy” with GPS (Spec. Syn) – “Rowing Coach Assistant” (Ptolemy & VHDL) • Checkers game (Ptolemy) • HW/SW tradeoff re FPGA acceleration – graphics card – Java Virtual Machine 25/JUN/98 MR&DCAN '98 16

Feedback • Enjoyed “from sand to chip” fab technology • Liked interdisciplinary (with CE) & intradisciplinary (within CSc) aspects • Required lots of skills, emphasized breadth • HW related topics good prep for technical jobs in smaller engineering companies • Fun to design whole system, use state-of-the-art tools, see many sides of design process 25/JUN/98 MR&DCAN '98 17

What’s Next? • Uvic Faculty of Engr. , new joint programs – CSc: Software Engineering option (SENG) – ECE: Software Engineering specialization – Mech. E/CE/CSc: Embedded System specialization â Codesign will be regular program course 25/JUN/98 MR&DCAN '98 18