INTRODUCING Enhanced 8 bit MidRange PIC Microcontroller MCU

INTRODUCING: Enhanced 8 -bit Mid-Range PIC® Microcontroller (MCU) Core Short Overview

Enhanced Mid-Range Introduction l l The enhanced mid-range core is a result of Microchip’s commitment to continuous improvement to the 8 -bit market and provides numerous technical enhancements to the existing core. The enhanced mid-range core further drives high-end performance and features into low pin count PIC® microcontrollers, making increased intelligence and control accessible to any design. 2

PIC® MCU Family Roadmap Memory/Performance PIC 32 ds. PIC® DSC PIC 24 PIC 18 (16 -bit instruction word) PIC 12/16 with Enhanced Mid-Range core (14 -bit instruction word) PIC 12/16 (14 -bit instruction word) PIC 10/12 (12 -bit instruction word) Price 3

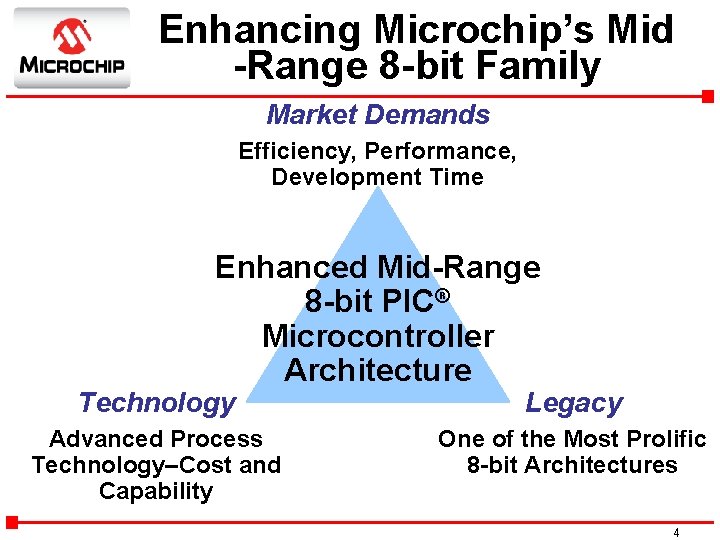

Enhancing Microchip’s Mid -Range 8 -bit Family Market Demands Efficiency, Performance, Development Time Enhanced Mid-Range 8 -bit PIC® Microcontroller Architecture Technology Legacy Advanced Process Technology–Cost and Capability One of the Most Prolific 8 -bit Architectures 4

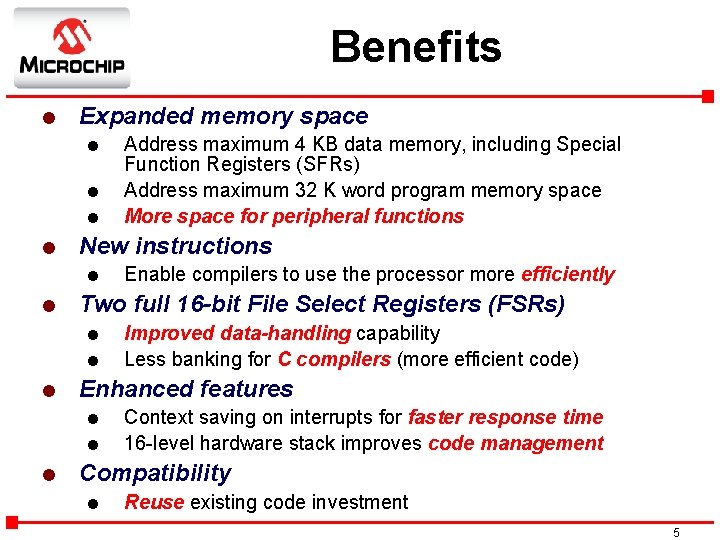

Benefits l Expanded memory space l l New instructions l l l Improved data-handling capability Less banking for C compilers (more efficient code) Enhanced features l l l Enable compilers to use the processor more efficiently Two full 16 -bit File Select Registers (FSRs) l l Address maximum 4 KB data memory, including Special Function Registers (SFRs) Address maximum 32 K word program memory space More space for peripheral functions Context saving on interrupts for faster response time 16 -level hardware stack improves code management Compatibility l Reuse existing code investment 5

Microchip’s Current 8 -bit PIC® Microcontroller Family Instruction Length Addressable Program Memory Max RAM and Register space Instruction Count Hardware Stack Interrupt Handling File Select Registers Baseline Mid-Range PIC 18 F 12 (bits) 2 K (Instructions) 144 (Bytes) 14 (bits) 8 K (Instructions) 446 (Bytes) 16 (bits) 1 M (Instructions) > 4 K (Bytes) 33 35 83 2 8 32 – Software Hardware/ Software 1 x 8 bit 1 x 9 bit 3 x 12 bit 6

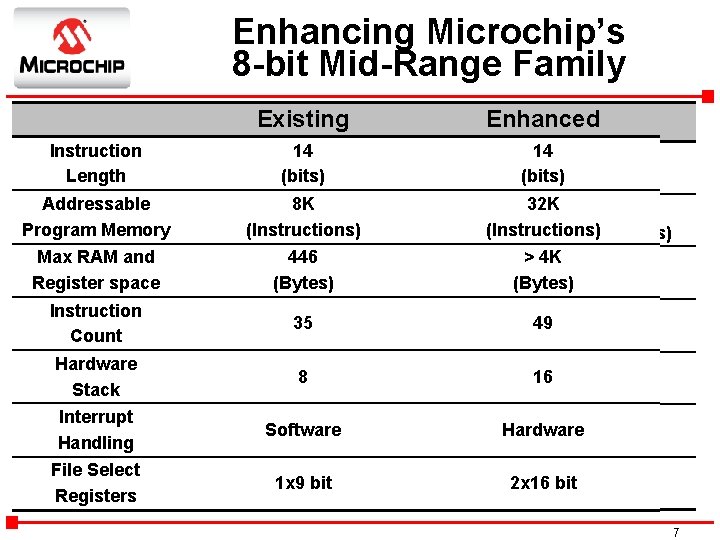

Enhancing Microchip’s 8 -bit Mid-Range Family Existing Baseline Instruction Length Addressable Program. Memory Max. RAMand Registerspace Instruction Count Hardware Stack Interrupt Handling File. Select File Registers 12 14 (bits) 2 K 8 K (Instructions) 144 446 (Bytes) Enhanced Mid-Range PIC 18 F 14 14 16 (bits) 32 K 8 K 1 M (Instructions) > 4 K 446 >4 K (Bytes) 33 35 35 49 83 8 8 16 32 Software - Software Hardware/ Hardware Software 1 x 9 bit 2 x 16 bit 3 x 12 bit 2 1 x 8 1 x 9 bit 7

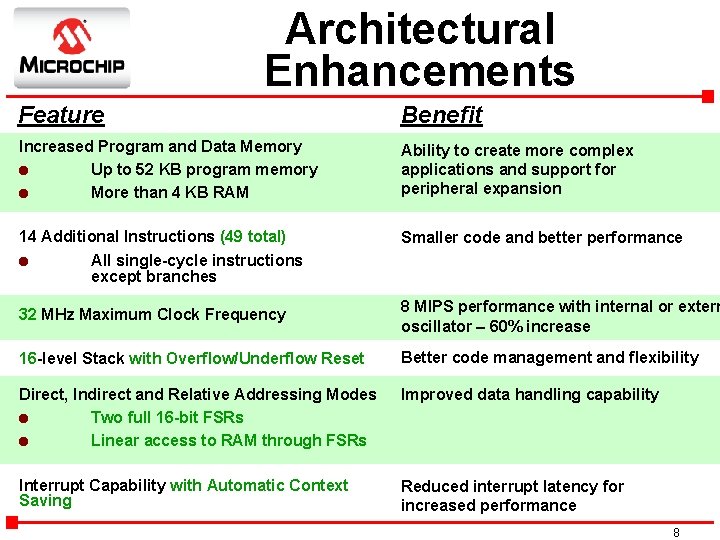

Architectural Enhancements Feature Benefit Increased Program and Data Memory l Up to 52 KB program memory l More than 4 KB RAM Ability to create more complex applications and support for peripheral expansion 14 Additional Instructions (49 total) Smaller code and better performance l All single-cycle instructions except branches 32 MHz Maximum Clock Frequency 8 MIPS performance with internal or extern oscillator – 60% increase 16 -level Stack with Overflow/Underflow Reset Better code management and flexibility Direct, Indirect and Relative Addressing Modes l Two full 16 -bit FSRs l Linear access to RAM through FSRs Improved data handling capability Interrupt Capability with Automatic Context Saving Reduced interrupt latency for increased performance 8

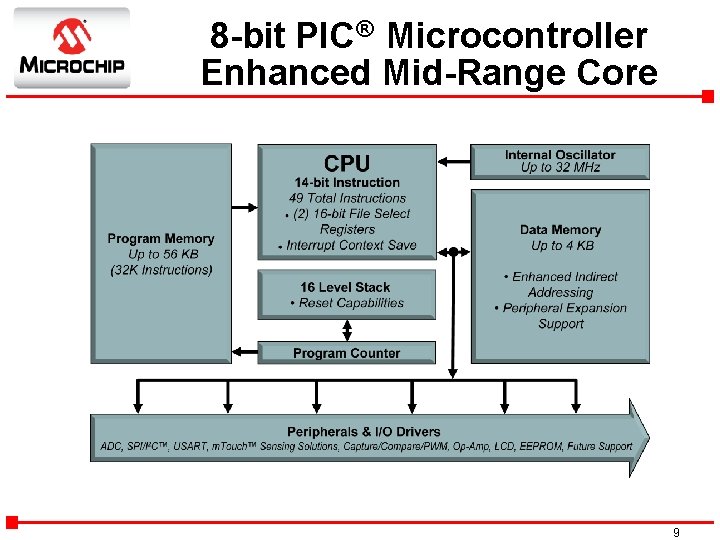

8 -bit PIC® Microcontroller Enhanced Mid-Range Core 9

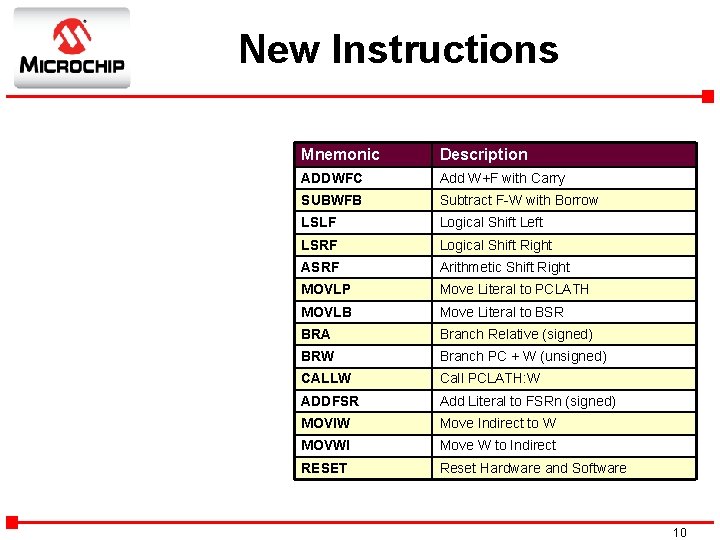

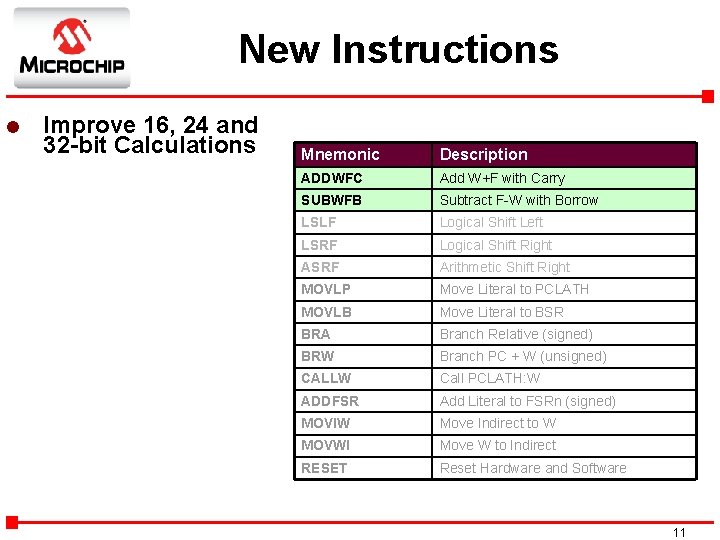

New Instructions Mnemonic Description ADDWFC Add W+F with Carry SUBWFB Subtract F-W with Borrow LSLF Logical Shift Left LSRF Logical Shift Right ASRF Arithmetic Shift Right MOVLP Move Literal to PCLATH MOVLB Move Literal to BSR BRA Branch Relative (signed) BRW Branch PC + W (unsigned) CALLW Call PCLATH: W ADDFSR Add Literal to FSRn (signed) MOVIW Move Indirect to W MOVWI Move W to Indirect RESET Reset Hardware and Software 10

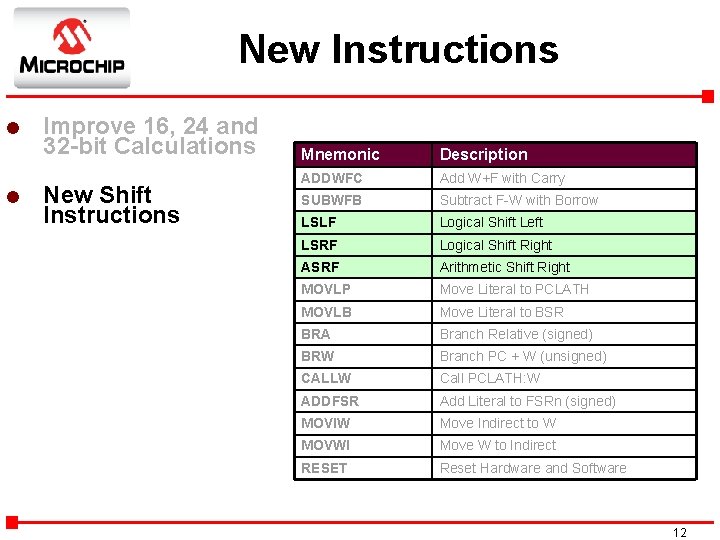

New Instructions l Improve 16, 24 and 32 -bit Calculations Mnemonic Description ADDWFC Add W+F with Carry SUBWFB Subtract F-W with Borrow LSLF Logical Shift Left LSRF Logical Shift Right ASRF Arithmetic Shift Right MOVLP Move Literal to PCLATH MOVLB Move Literal to BSR BRA Branch Relative (signed) BRW Branch PC + W (unsigned) CALLW Call PCLATH: W ADDFSR Add Literal to FSRn (signed) MOVIW Move Indirect to W MOVWI Move W to Indirect RESET Reset Hardware and Software 11

New Instructions l l Improve 16, 24 and 32 -bit Calculations New Shift Instructions Mnemonic Description ADDWFC Add W+F with Carry SUBWFB Subtract F-W with Borrow LSLF Logical Shift Left LSRF Logical Shift Right ASRF Arithmetic Shift Right MOVLP Move Literal to PCLATH MOVLB Move Literal to BSR BRA Branch Relative (signed) BRW Branch PC + W (unsigned) CALLW Call PCLATH: W ADDFSR Add Literal to FSRn (signed) MOVIW Move Indirect to W MOVWI Move W to Indirect RESET Reset Hardware and Software 12

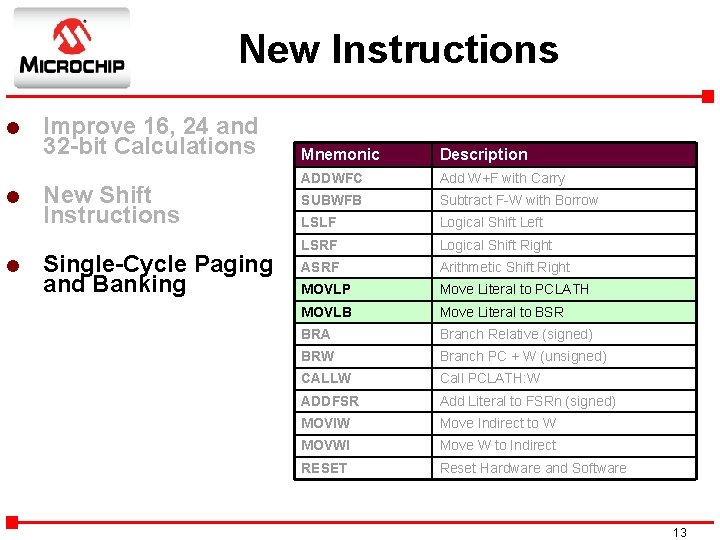

New Instructions l l l Improve 16, 24 and 32 -bit Calculations New Shift Instructions Single-Cycle Paging and Banking Mnemonic Description ADDWFC Add W+F with Carry SUBWFB Subtract F-W with Borrow LSLF Logical Shift Left LSRF Logical Shift Right ASRF Arithmetic Shift Right MOVLP Move Literal to PCLATH MOVLB Move Literal to BSR BRA Branch Relative (signed) BRW Branch PC + W (unsigned) CALLW Call PCLATH: W ADDFSR Add Literal to FSRn (signed) MOVIW Move Indirect to W MOVWI Move W to Indirect RESET Reset Hardware and Software 13

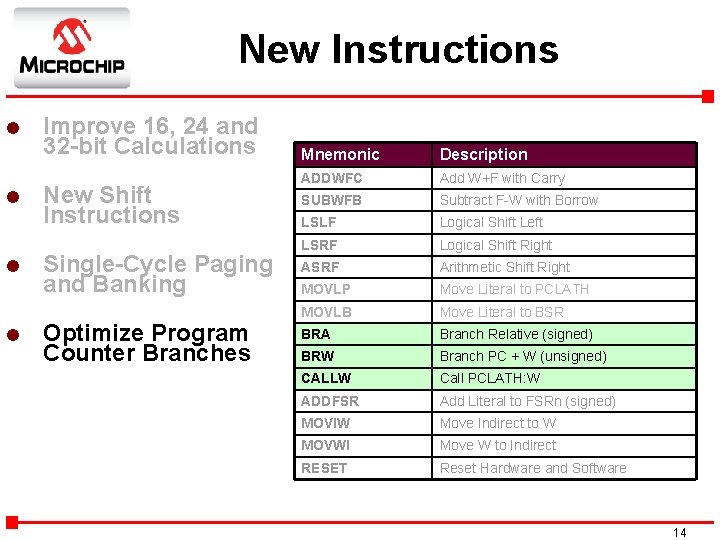

New Instructions l l Improve 16, 24 and 32 -bit Calculations New Shift Instructions Single-Cycle Paging and Banking Optimize Program Counter Branches Mnemonic Description ADDWFC Add W+F with Carry SUBWFB Subtract F-W with Borrow LSLF Logical Shift Left LSRF Logical Shift Right ASRF Arithmetic Shift Right MOVLP Move Literal to PCLATH MOVLB Move Literal to BSR BRA Branch Relative (signed) BRW Branch PC + W (unsigned) CALLW Call PCLATH: W ADDFSR Add Literal to FSRn (signed) MOVIW Move Indirect to W MOVWI Move W to Indirect RESET Reset Hardware and Software 14

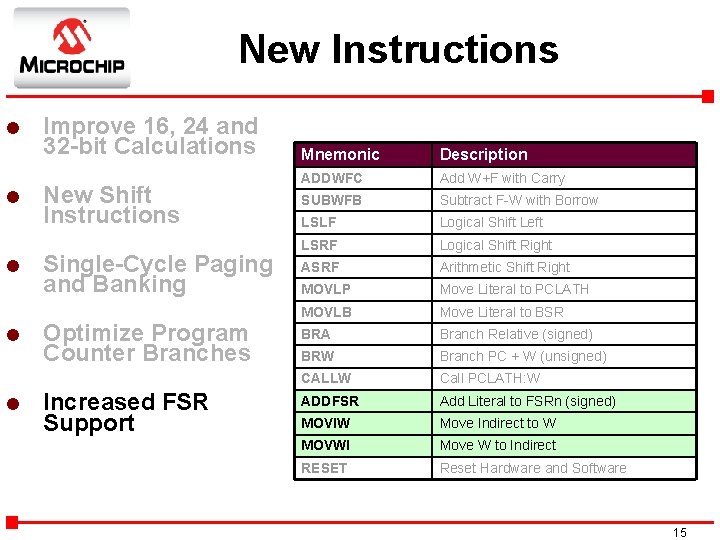

New Instructions l l l Improve 16, 24 and 32 -bit Calculations New Shift Instructions Single-Cycle Paging and Banking Optimize Program Counter Branches Increased FSR Support Mnemonic Description ADDWFC Add W+F with Carry SUBWFB Subtract F-W with Borrow LSLF Logical Shift Left LSRF Logical Shift Right ASRF Arithmetic Shift Right MOVLP Move Literal to PCLATH MOVLB Move Literal to BSR BRA Branch Relative (signed) BRW Branch PC + W (unsigned) CALLW Call PCLATH: W ADDFSR Add Literal to FSRn (signed) MOVIW Move Indirect to W MOVWI Move W to Indirect RESET Reset Hardware and Software 15

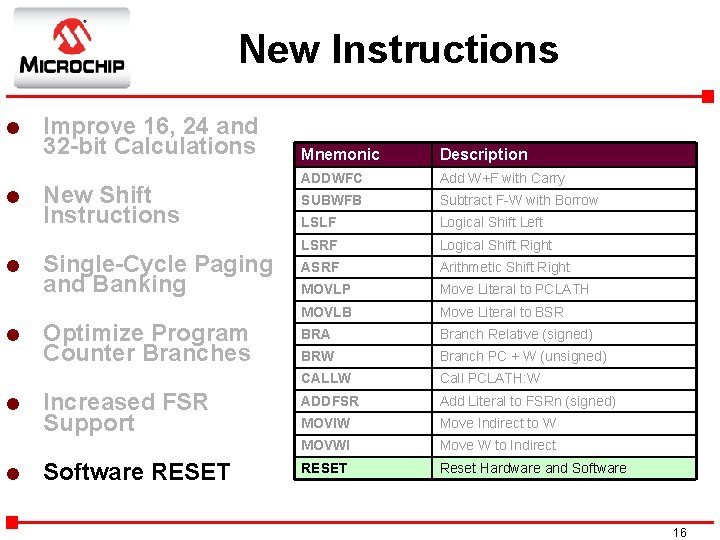

New Instructions l l l Improve 16, 24 and 32 -bit Calculations New Shift Instructions Single-Cycle Paging and Banking Optimize Program Counter Branches Increased FSR Support Software RESET Mnemonic Description ADDWFC Add W+F with Carry SUBWFB Subtract F-W with Borrow LSLF Logical Shift Left LSRF Logical Shift Right ASRF Arithmetic Shift Right MOVLP Move Literal to PCLATH MOVLB Move Literal to BSR BRA Branch Relative (signed) BRW Branch PC + W (unsigned) CALLW Call PCLATH: W ADDFSR Add Literal to FSRn (signed) MOVIW Move Indirect to W MOVWI Move W to Indirect RESET Reset Hardware and Software 16

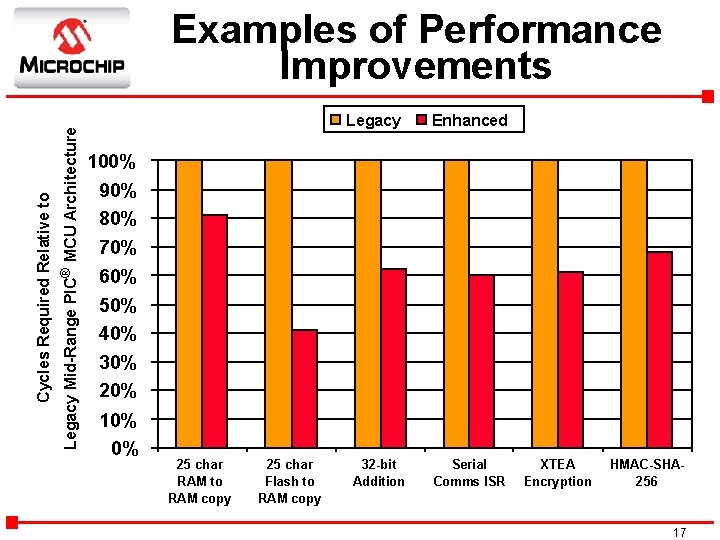

Legacy Mid-Range PIC® MCU Architecture Cycles Required Relative to Examples of Performance Improvements Legacy Enhanced 100% 90% 80% 70% 60% 50% 40% 30% 20% 10% 0% 25 char RAM to RAM copy 25 char Flash to RAM copy 32 -bit Addition Serial Comms ISR XTEA Encryption HMAC-SHA 256 17

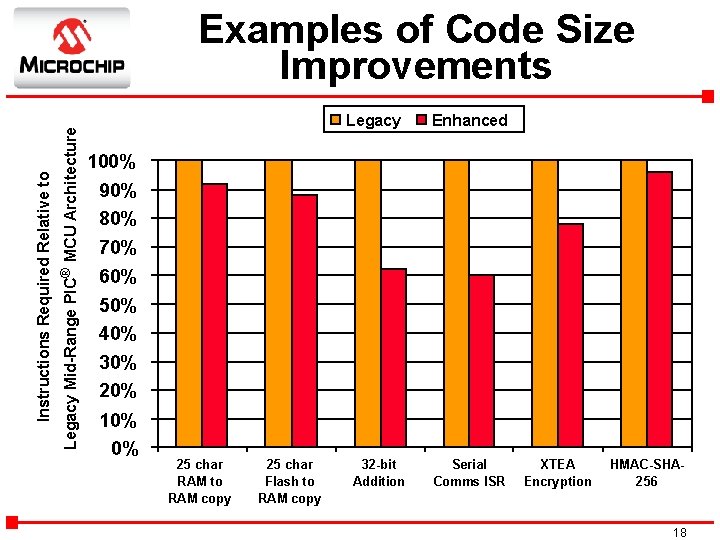

Legacy Mid-Range PIC® MCU Architecture Instructions Required Relative to Examples of Code Size Improvements Legacy Enhanced 100% 90% 80% 70% 60% 50% 40% 30% 20% 10% 0% 25 char RAM to RAM copy 25 char Flash to RAM copy 32 -bit Addition Serial Comms ISR XTEA Encryption HMAC-SHA 256 18

Availability and Tool Support l PIC® MCUs with the enhanced Mid-Range 8 -bit core and tool support expected to be available early 2009 28 -/40 -/64 -pin PIC MCU family coming first l Additional products ranging from 8 -pin up to 64 -pin thereafter Assembly code development and debug to be supported by the free MPLAB® IDE Integrated Development Environment, available as a download from Microchip’s Web site www. microchip. com/MPLAB Third-party C-compiler support for 8 -bit PIC MCUs utilizing the enhanced core provided by: HI-TECH Software, CCS, micro. Engineering Labs, and Byte Craft Limited l l l 19

Summary l l The enhanced mid-range core expands on the best elements of the existing mid-range core by providing additional performance and peripherals Numerous technical improvements Compatibility with existing mid-range products for true product migration Allows 8 -bit PIC® MCUs to continue their wide market acceptance 20

Thank You!

Trademarks l l l The Microchip name and logo, the Microchip logo, Accuron, ds. PIC, Kee. Loq logo, MPLAB, PICmicro, PICSTART, rf. PIC, Smart. Shunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U. S. A. and other countries. Filter. Lab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, Smart. Sensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U. S. A. Analog-for-the-Digital Age, Application Maestro, Code. Guard, ds. PICDEM. net, ds. PICworks, ds. SPEAK, ECAN, ECONOMONITOR, Fan. Sense, In‑Circuit Serial Programming, ICSP, ICEPIC, Mindi, Mi. Wi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, m. Touch, PICkit, PICDEM. net, PICtail, PIC 32 logo, Power. Cal, Power. Info, Power. Mate, Power. Tool, REAL ICE, rf. LAB, Select Mode, Total Endurance, Wiper. Lock and ZENA are trademarks of Microchip Technology Incorporated in the U. S. A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U. S. A. All other trademarks mentioned herein are property of their respective companies. © 2008, Microchip Technology Incorporated, All Rights Reserved. 22

- Slides: 22