Interrupts of X 86 Microprocessor Course Outcome Recognize

- Slides: 13

Interrupts of X 86 Microprocessor Course Outcome Recognize the need for recent Bus standards like PCI Express, USB etc.

Types of interrupts of X-86 processor Maskable Interrupts • These are the most common way used by the X 86 processor to respond to asynchronous external hardware events. Hardware interrupts occurs when the INTR is pulled high and the Interrupt flag bit is enabled. • The processor only responds to interrupts between instructions. • When an interrupt occurs the processor reads the 8 bit vector code of interrupt supplied by hardware which identifies the source of interrupt (one of the 224 user defined interrupts. ) • The IF bit in the flag register is reset when as interrupt is being serviced. This effectively disables servicing additional interrupts during an Interrupt service routine. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

Types of interrupts of X-86 processor Non Maskable Interrupts • Non maskable interrupts provide a method of servicing very high priority interrupts. NMI is an example of non maskable interrupt. It is an external pin to the microprocessor. • A common example of the use of non maskable interrupt (NMI) would be to activate a power failure routine. • When a NMI is pulled high it causes an interrupt with an internally supplied vector value of 2. No interrupt acknowledgement cycle is performed by the processor when NMI occurs. • While executing NMI, no further NMI is serviced until the next IRET instruction is executed or the processor is reset. • If NMI occurs at the time of servicing a NMI, its occurrence will be saved and it will be processed when the servicing of the first will be over. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

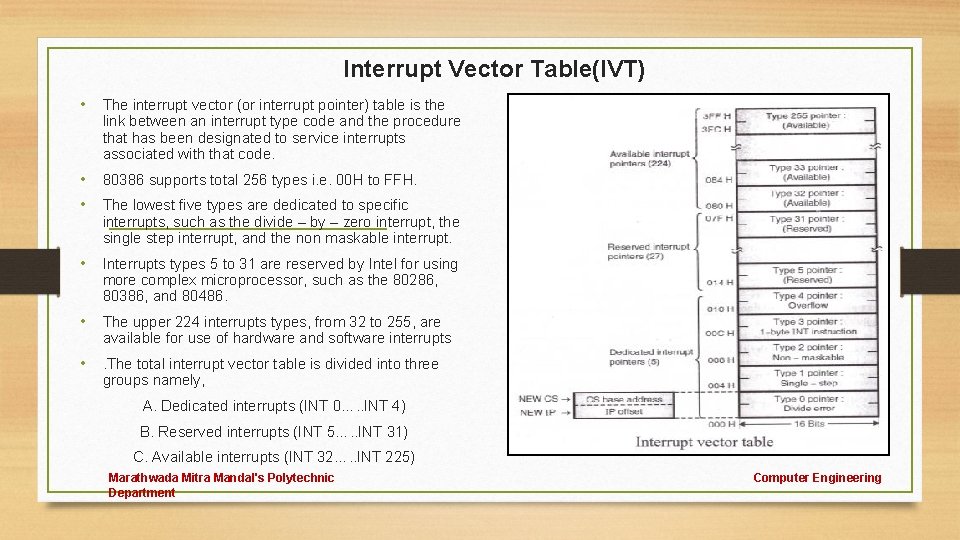

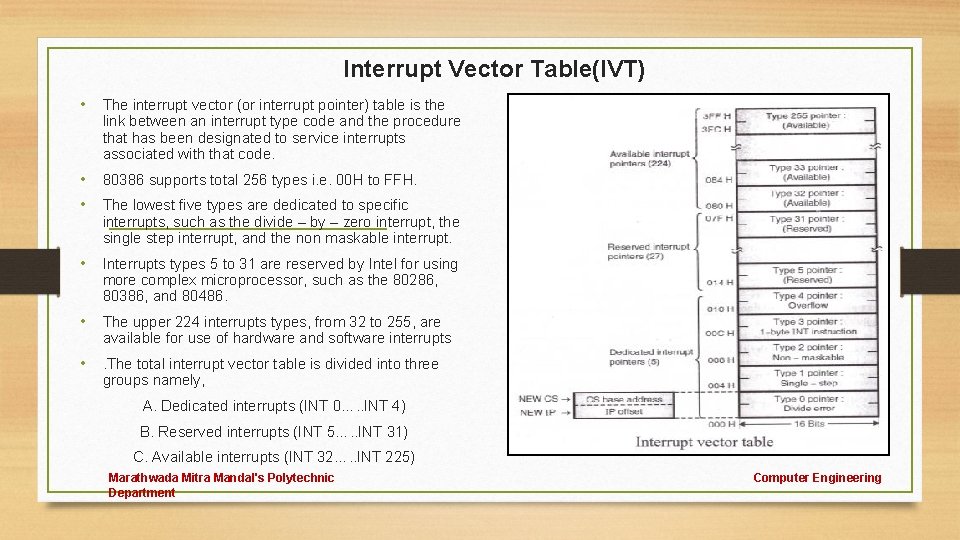

Interrupt Vector Table(IVT) • The interrupt vector (or interrupt pointer) table is the link between an interrupt type code and the procedure that has been designated to service interrupts associated with that code. • 80386 supports total 256 types i. e. 00 H to FFH. • The lowest five types are dedicated to specific interrupts, such as the divide – by – zero interrupt, the single step interrupt, and the non maskable interrupt. • Interrupts types 5 to 31 are reserved by Intel for using more complex microprocessor, such as the 80286, 80386, and 80486. • The upper 224 interrupts types, from 32 to 255, are available for use of hardware and software interrupts • . The total interrupt vector table is divided into three groups namely, A. Dedicated interrupts (INT 0…. . INT 4) B. Reserved interrupts (INT 5…. . INT 31) C. Available interrupts (INT 32…. . INT 225) Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

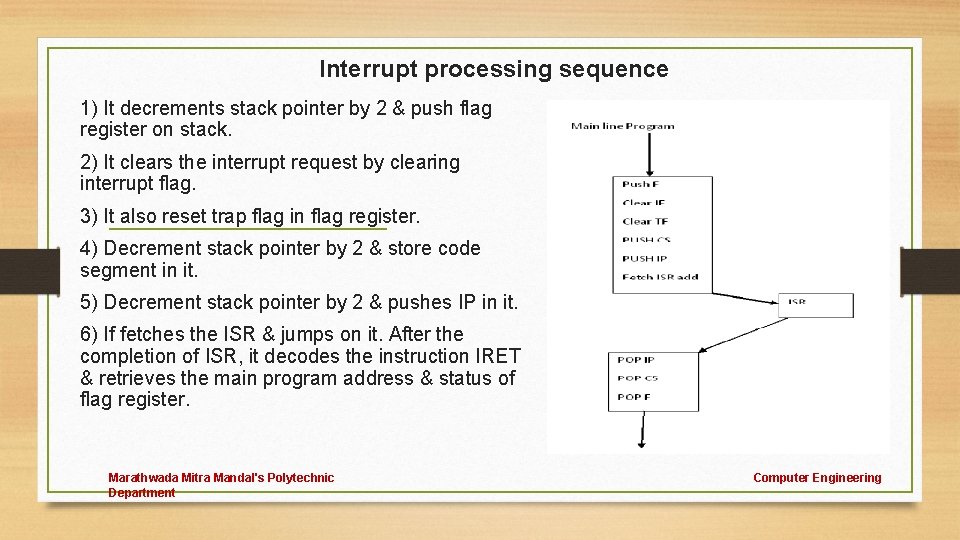

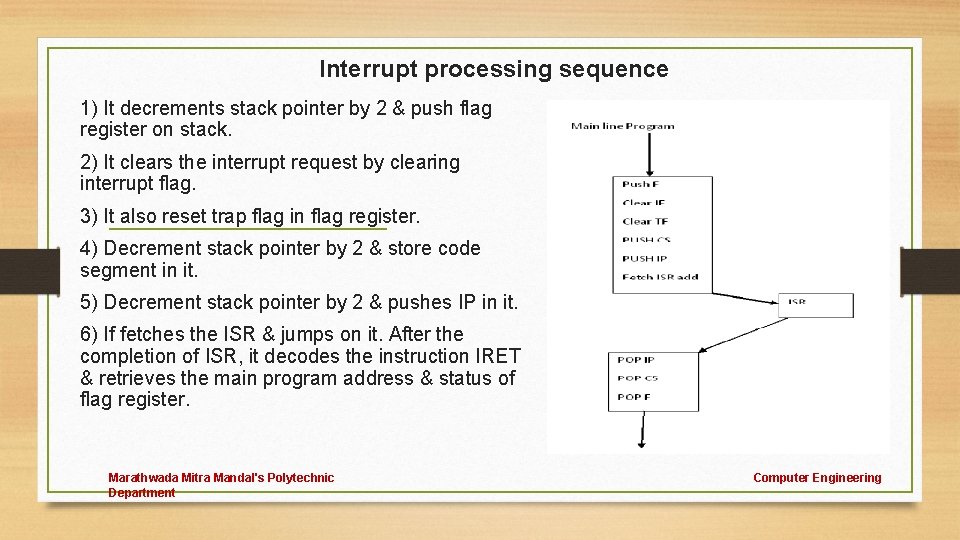

Interrupt processing sequence 1) It decrements stack pointer by 2 & push flag register on stack. 2) It clears the interrupt request by clearing interrupt flag. 3) It also reset trap flag in flag register. 4) Decrement stack pointer by 2 & store code segment in it. 5) Decrement stack pointer by 2 & pushes IP in it. 6) If fetches the ISR & jumps on it. After the completion of ISR, it decodes the instruction IRET & retrieves the main program address & status of flag register. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

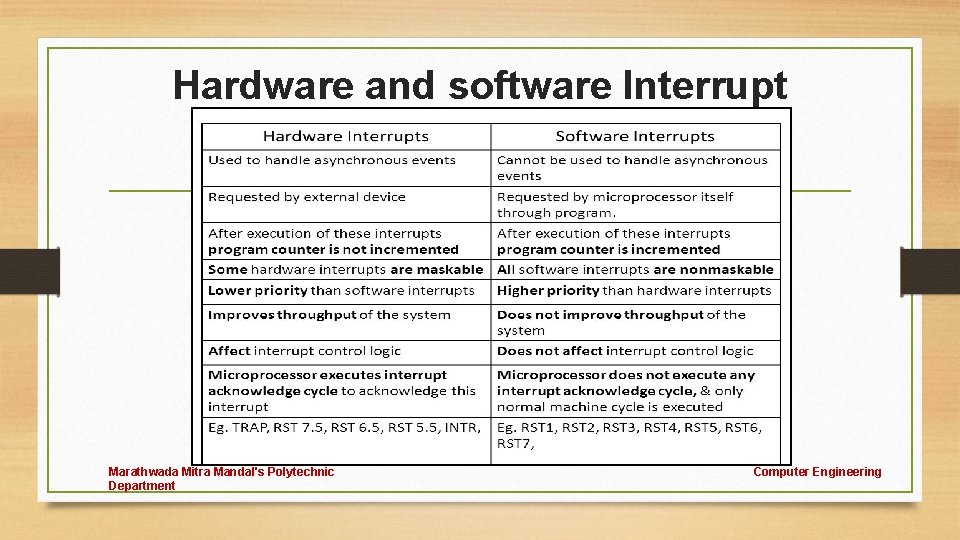

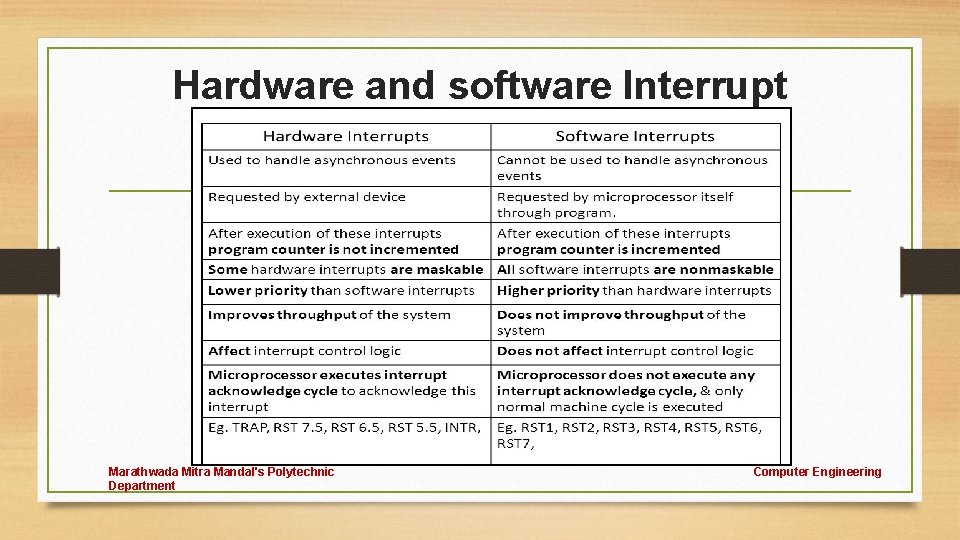

Hardware and software Interrupt Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

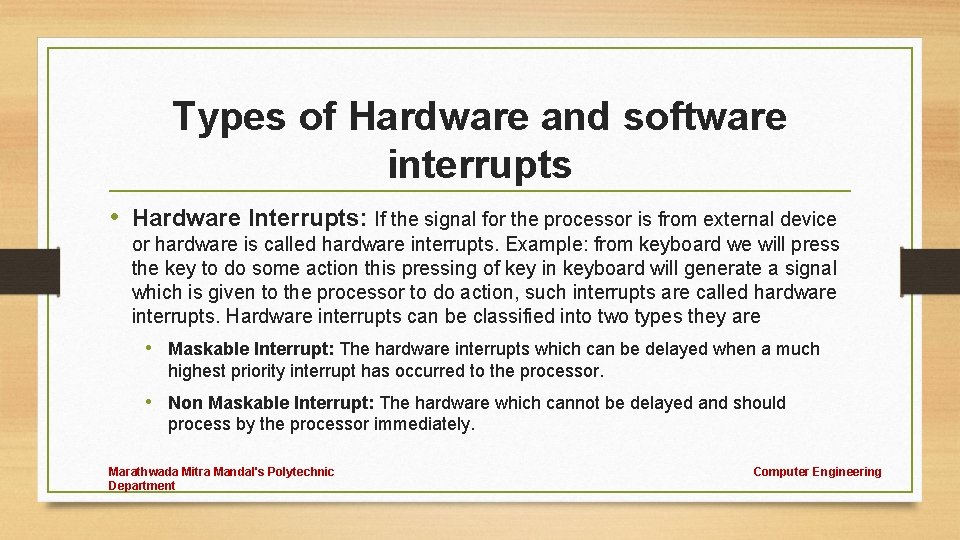

Types of Hardware and software interrupts • Hardware Interrupts: If the signal for the processor is from external device or hardware is called hardware interrupts. Example: from keyboard we will press the key to do some action this pressing of key in keyboard will generate a signal which is given to the processor to do action, such interrupts are called hardware interrupts. Hardware interrupts can be classified into two types they are • Maskable Interrupt: The hardware interrupts which can be delayed when a much highest priority interrupt has occurred to the processor. • Non Maskable Interrupt: The hardware which cannot be delayed and should process by the processor immediately. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

Types of Hardware and software interrupts • Software Interrupts: Software interrupt can also divided in to two types. They are • Normal Interrupts: the interrupts which are caused by the software instructions are called software instructions. • Exception: unplanned interrupts while executing a program is called Exception. For example: while executing a program if we got a value which should be divided by zero is called a exception. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

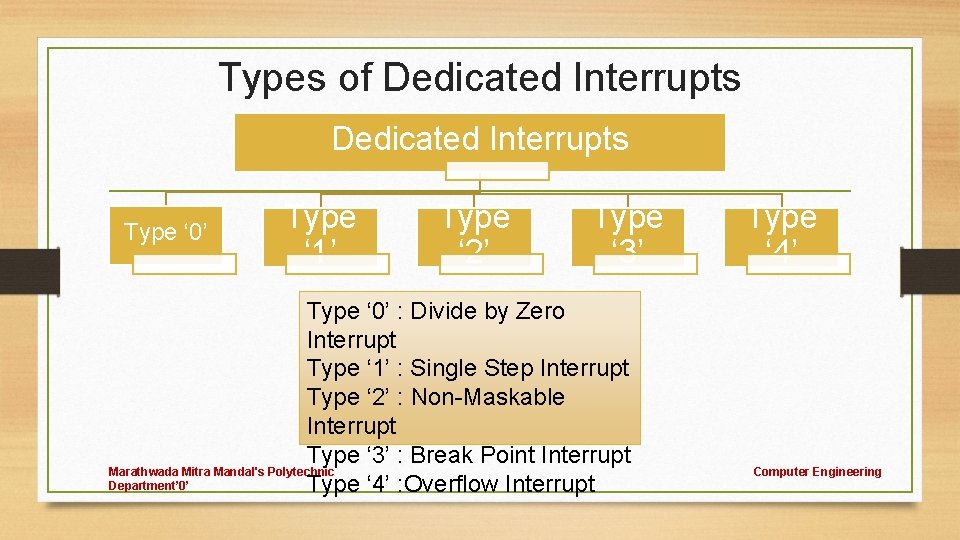

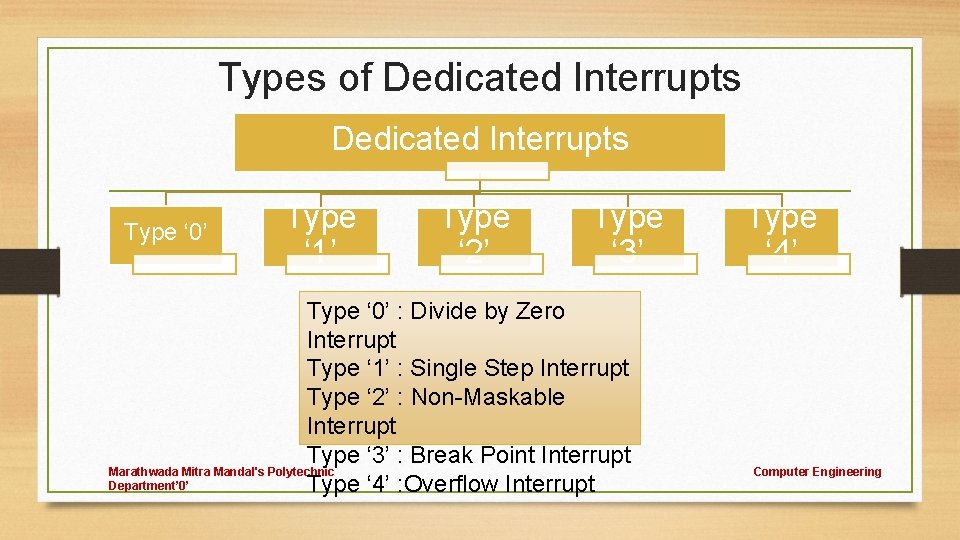

Types of Dedicated Interrupts Type ‘ 0’ Type ‘ 1’ Type ‘ 2’ Type ‘ 3’ Type ‘ 0’ : Divide by Zero Interrupt Type ‘ 1’ : Single Step Interrupt Type ‘ 2’ : Non-Maskable Interrupt Type ‘ 3’ : Break Point Interrupt Marathwada Mitra Mandal's Polytechnic Department’ 0’ Type ‘ 4’ : Overflow Interrupt Type ‘ 4’ Computer Engineering

INT 0(Divide by zero error) The interrupt with type number 0 is dedicated to the divide by zero error. This interrupt is an ‘error generated’ interrupt (also called an ‘exception’. Dedicating type 0 for this case means that the corresponding interrupt vector in the interrupt vector table is available at 0000: 0000 INT 1 (single stepping) This type number is dedicated for single stepping or trace. Single stepping is an important idea in debugging during logical debugging of our programs. We would like to stop after the execution of each instruction and check the contents of register, memory and so on. The ISR for viewing the register and memory content will be pointed by the vector of interrupt type 1. INT 2 (Non Maskable Interrupt) This interrupt corresponds to the vector (pointer) of the hardware interrupt NMI. When an interrupt is received on the pin NMI (Non Maskable Interrupt) of the processor, a type 2 interrupt occur- this means that the ISR for NMI must be written in the address pointed by the corresponding IVT content. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

INT 3 (Breakpoint Interrupt) This is the breakpoint interrupt, which is useful for de-bugging. We will need to set breakpoints (stop after executing a group of instruction) and check the content of registers and memory after executing instructions up to the breakpoint. INT 4 (Overflow Interrupt) This interrupts corresponding to the overflow flag. If the overflow flag is set, this interrupt occurs but not automatically. An instruction INTO (interrupt on overflow) must be written after the program segment which is likely to cause the overflow flag (OF) to be set. Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

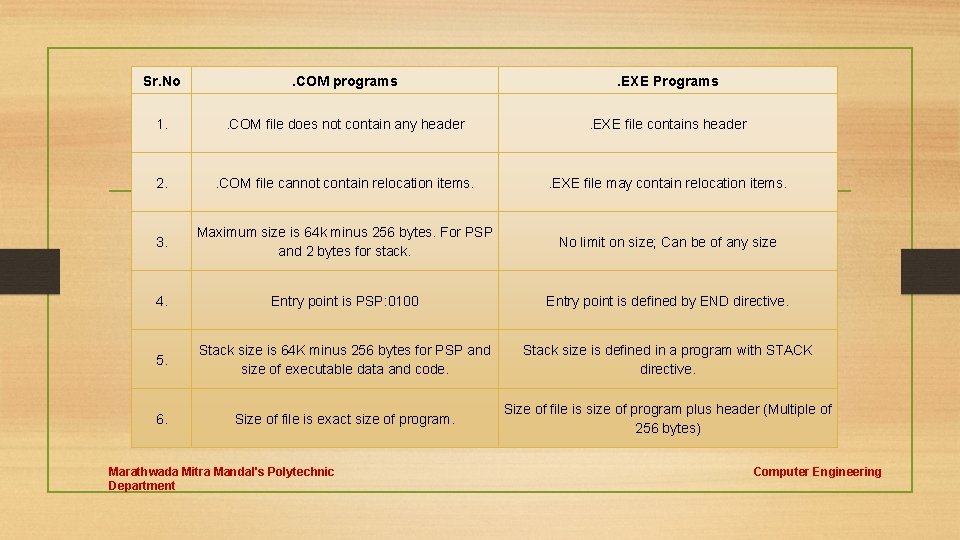

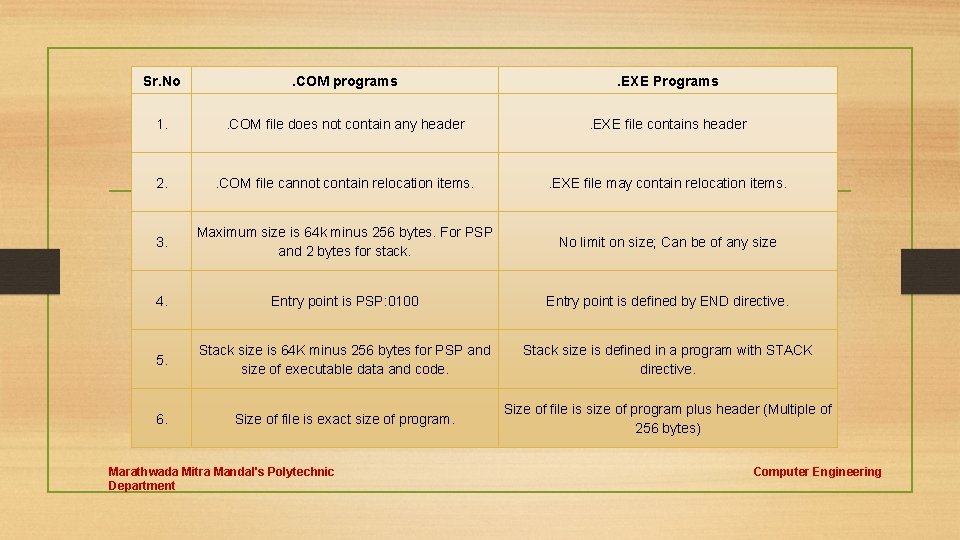

Sr. No 1. 2. 3. 4. 5. 6. . COM programs . EXE Programs . COM file does not contain any header . EXE file contains header . COM file cannot contain relocation items. . EXE file may contain relocation items. Maximum size is 64 k minus 256 bytes. For PSP and 2 bytes for stack. No limit on size; Can be of any size Entry point is PSP: 0100 Entry point is defined by END directive. Stack size is 64 K minus 256 bytes for PSP and size of executable data and code. Stack size is defined in a program with STACK directive. Size of file is exact size of program. Size of file is size of program plus header (Multiple of 256 bytes) Marathwada Mitra Mandal's Polytechnic Department Computer Engineering

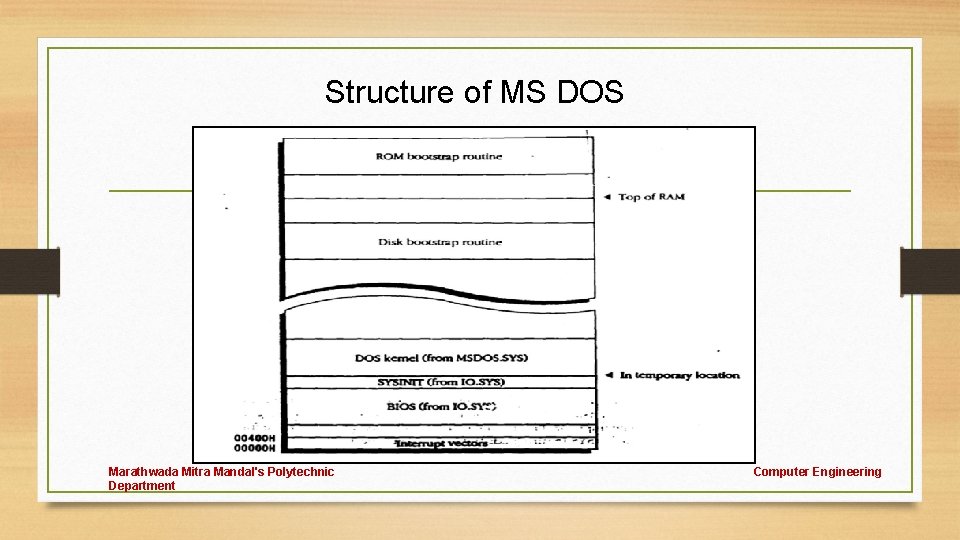

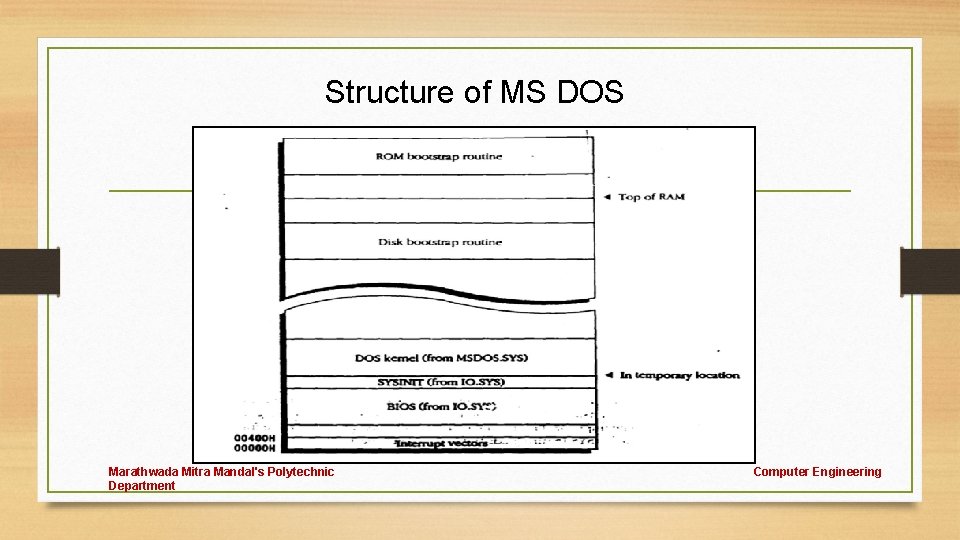

Structure of MS DOS Marathwada Mitra Mandal's Polytechnic Department Computer Engineering